ufl in htl + Ii2hn 5

ua« hn + ijfbn

U,j

13 2

It1hlt+ llthtt+ lnhlf + + I2,hu;

Ua, - 1г1Ь,;

Ul iu11

1nhu+ 1агьг 5

игг 1i«hl4.

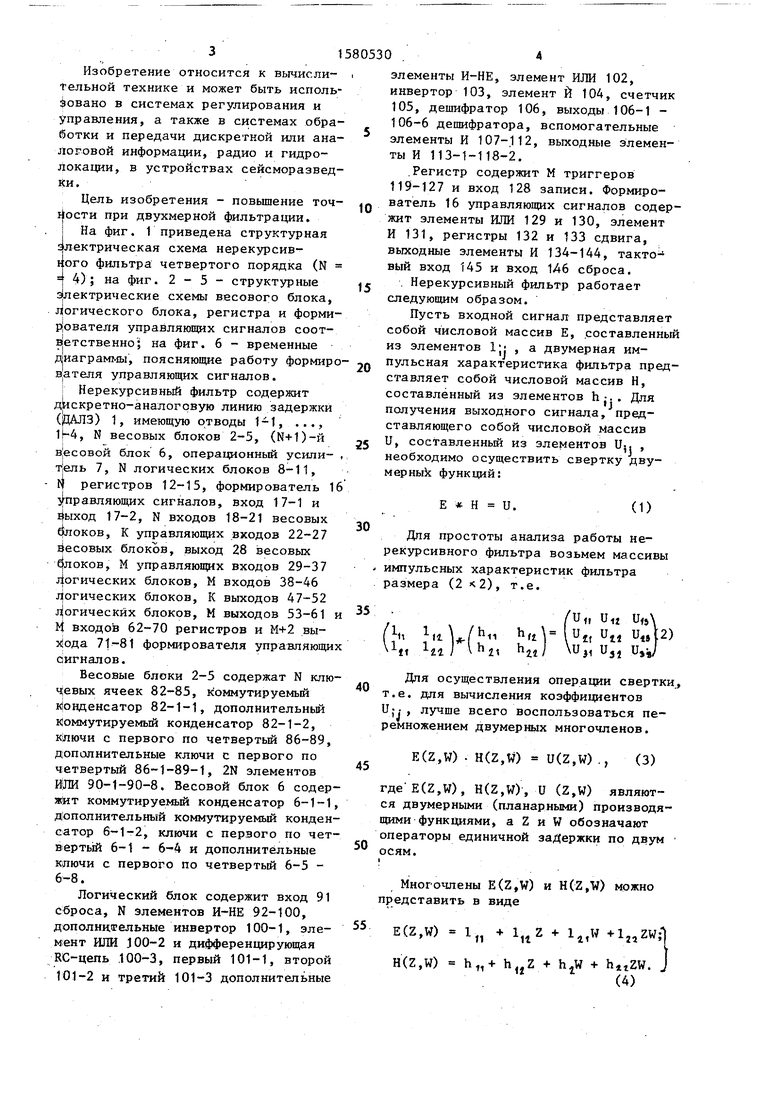

Проведя упорядочение относительно порядка следования коэффициентов Ij: и , вектор-столбец из U;, можно представить в виде

U,

11

Jf

Z1

1Ь

и

U

и2а

31 игъ

и.

38J

0 + 0 + О

fi Ml fh Ь„141+ 0 + Ьг11„ + О

О + Ь141П+ 0 + 0

hH 1li+h«t1li+ht 1l4-fhii О + 0 + Ь411г1+ О

О + Ь-Л--+ 0 + h-Д

iltilt

11L и

О + 0 + ht,ltl+ hltllf 0 + 0 + 0 + hltl14

5

0

О + 0 + О i +Inh«+ ° + °

I41hrt +I14hn+l

11 ufi

и,

U4

э

U4 Uj

Ч

. U7J иО + 0 + 0 +

h,, + О

+1г1Ь,2+1пЬг

О + l«hn+ It1h21+ lnhtl| О + 0 + ltthw+ I71htt

(7)

но

)

35

Сравнивая выражения для результирующих коэффициентов, полученных по (6) и по (7), видно, что количество выходных коэффициентов, определяющих

40 выходной двумерный массив, больше, чем количество выходных коэффициентов, определяющих выходной одномерный массив. Количество слагаемых, определяющих сооответствующий коэффициент

45 выходного Массива в одномерном случае, определяется по линейному закону и строго возрастает от одного слагаемого до п слагаемых, где п - количество слагаемых входного многочлена

50 E(Z) и H(Z) соответственно. Количество слагаемых, определяющих соответствующий коэффициент выходного массива в двумерном случае, определяется по нелинейному закону и зависит

,-с от принятой последовательности следования коэффициентов U-: , представлен- ных в виде вектора-столбца и ,-. .

Выражение (7) можно переписать в виде

Из выражения (8) видно, что коэффициенты . одномерной последовательности, стоящие в соответствующих столбцах, строго следуют один за другом. Из выражения (9) видно, что в двумерном случае, коэффициенты не следуют строго один за другим, а зависят от порядка следования коэффициентов U,-j и размера двумерного массива входного сигнала, поэтому для оптимального нахождения выходных коэффициентов U-: необходимо прежде всего знать информацию о соответствующих вектор-столбцах связей, состоящих из единиц или нулей.

Количество вектор-столбцов связей определяется по размеру массива входных сигналов Е и массива чисел импульсной переходной характеристики фильтра Н. Так, если размер указанных массивов N х N, то количество вектор-столбцов N2.

Размеры вектор-столбцов связей определяются размерами выходного массива CU ;s . Так, если размеры входных массивов чисел N N, то размеры выходного массива (2п-2)+1 (2ц-2)+13 , а следовательно, размер вектора-столбца равен Ј(2п-2)+1 .

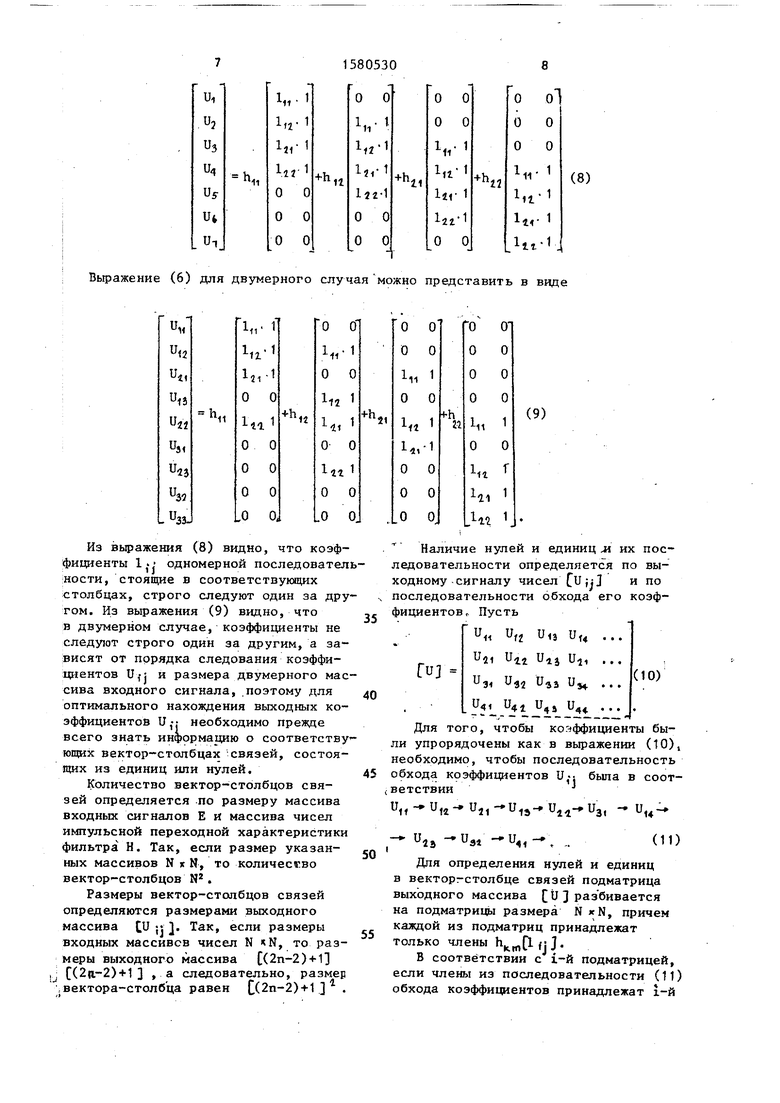

Наличие нулей и единиц м их последовательности определяется по выходному сигналу чисел CUijJ и по последовательности обхода его коэффициентов , Пусть

u« ufz и и uf4 ... и41 игг u4S иц ... иэ УЗ и« и. ...

FfL.u« ,

Для того, чтобы коэффициенты были упрорядочены как в выражении (10), необходимо, чтобы последовательность обхода коэффициентов U,- была в соответствии

Cuj(10)

ulf-u12

и

21

( - U14

u«8 u3

(11)

Для определения нулей и единиц в векторгстолбце связей подматрица выходного массива U 1 разбивается на подматрицы размера N «N, причем каждой из подматриц принадлежат только члены .

В соответствии с i-й подматрицей, если члены из последовательности (11) обхода коэффициентов принадлежат 1-й

подматрице, то в вектор-столбце связей будет 1, если члены из последовательности (11) не принадлежат i-й подматрице, то в вектор-столбце связей будет О.

Таким образом, определив по размерам входных массивов размеры выходного массива, определяют вектор- столбцы связей. Наличие вектор-столб- д цов связей позволяет достаточно просто реализовать алгоритм двумерной нерекурсивной фильтрации.#

Рассмотрим принцип работы нерекурсивного фильтра.

I

Пусть массив входных сигналов и массив импульсных переходных характеристик фильтра имеет размер (), как показано в выражении (2). Необхо- 20 димо реализовать нерекурсивную фильт- радию, т.е. получить на входе отфильтрованный двумерный массив чисел U;:. Здесь N 2, следовательно, размер выходного массива C2N-2)+1 (2N-2)+ 25 + 3 «3.

Следовательно, выходной массив можно представить в виде

5

30

«

и,г

«31

и

13

и«

Ua-ь

Последовательность обхода коэффициентов выходного массива, в соответствии с (11) имеет вид

и - Чс -

вая подматрица

1

U

1S

U

гг

и

51

1,-;3 -h

11

11

4i

и

11

11

U« U12

вторая подматрица

hfiCV.J - h

ft

J«

LII

Jll

подматрица

Г1 - hn

L ц

11

12

У

J41

U

31

четвертая подматрица

г

fi. jJ

h

г г

- it

1.

L-21

31

;

J3SJ

В соответствии с последовательностью обхода коэффициентов Ql JjJ и в соответствии с i-й подматрицей,. первый вектор-столбец имеет вид

F1 11 101 0000 3 Т ,

5 второй вектор-столбец

F 010110100 7 ,

третий вектор-столбец связен

FJ 001011010 т , четвертый вектор-столбец связей

F. 000010111 JT.

Определив все вектор-столбцы свяв

зей F

4.

необходимо занес ре30

ффитвет35

1

40

« 12

45

50

1 a l 3

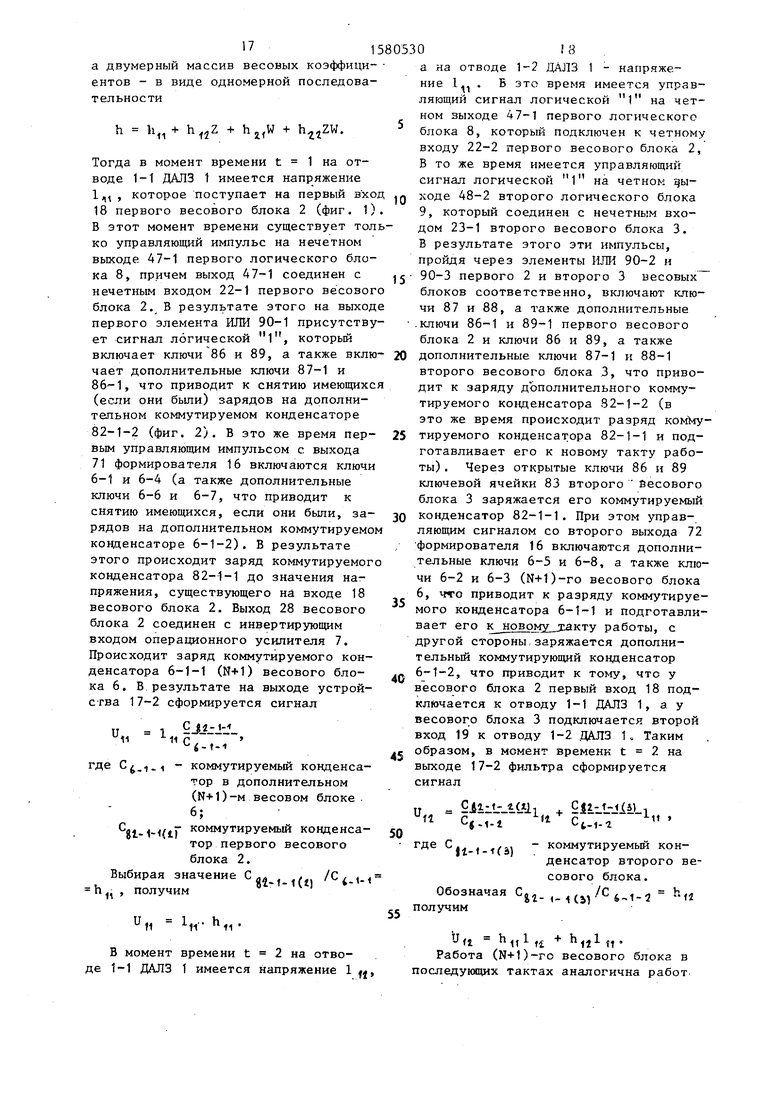

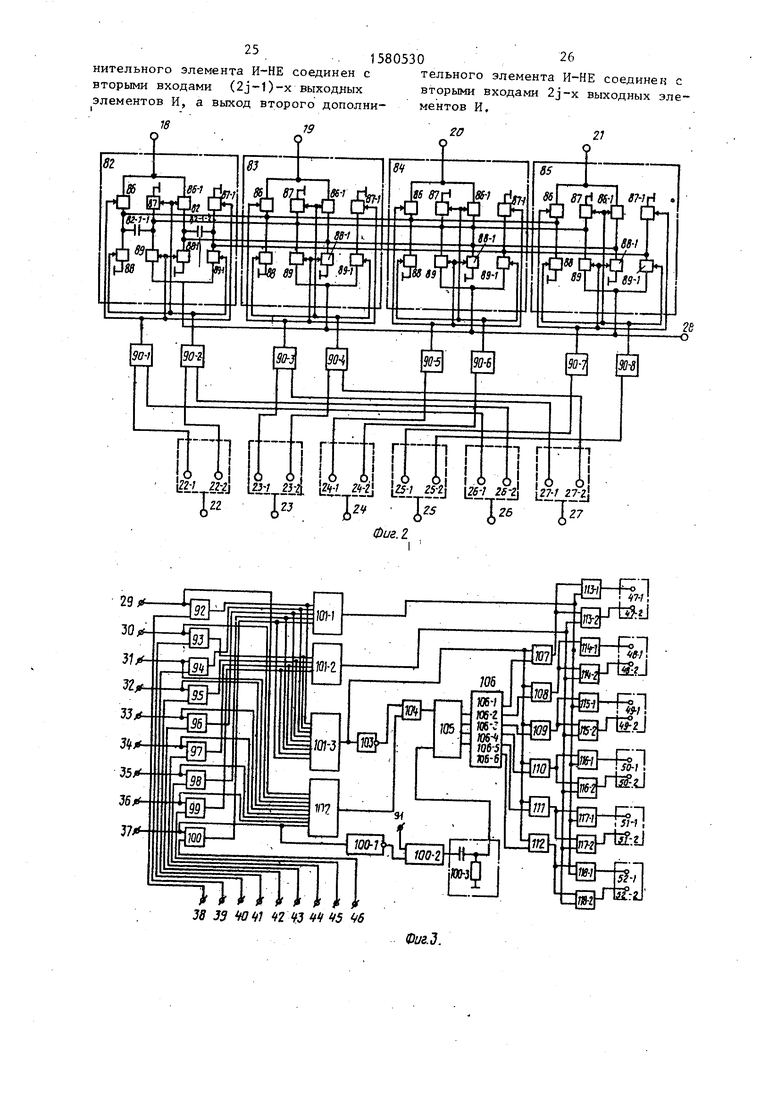

ти их значение в соответствующие гиатры 12-15 (фиг. 1). Каждый из регистра памяти содержит по девять триггеров 119-127 (фиг. 4). В качестве триггеров могут быть использованы таксируемые потенциалом D-триг- геры. Ввод кодовой комбинации, содержащейся в каждом вектор-столбце связей, в соответствующий регистр осуществляется через информационные входы 62-70 D каждого триггера (фиг. 4). При этом на вход 128 записи подается сигнал высокого потенциала, что осуществляется от внешнего источника одиночного импульса Пуск, а для хранения информации в регистрах необходимо, чтобы на входе 129 записи был всегда потенциал О.

В результате проведенной записи информации о содержимом каждого вектор-столбца связей F1 , F

2

3

4

55

ill

t.

в соответствующие регистры 12-15 на их выходах 53-61 (фиг. 4) будет кодовая комбинация, соответствующая коде вой комбинации 1-го вектор-столбца связей. После записи кодовой комбинации в регистрах 12-15 нерекурсивный фильтр готов к работе.

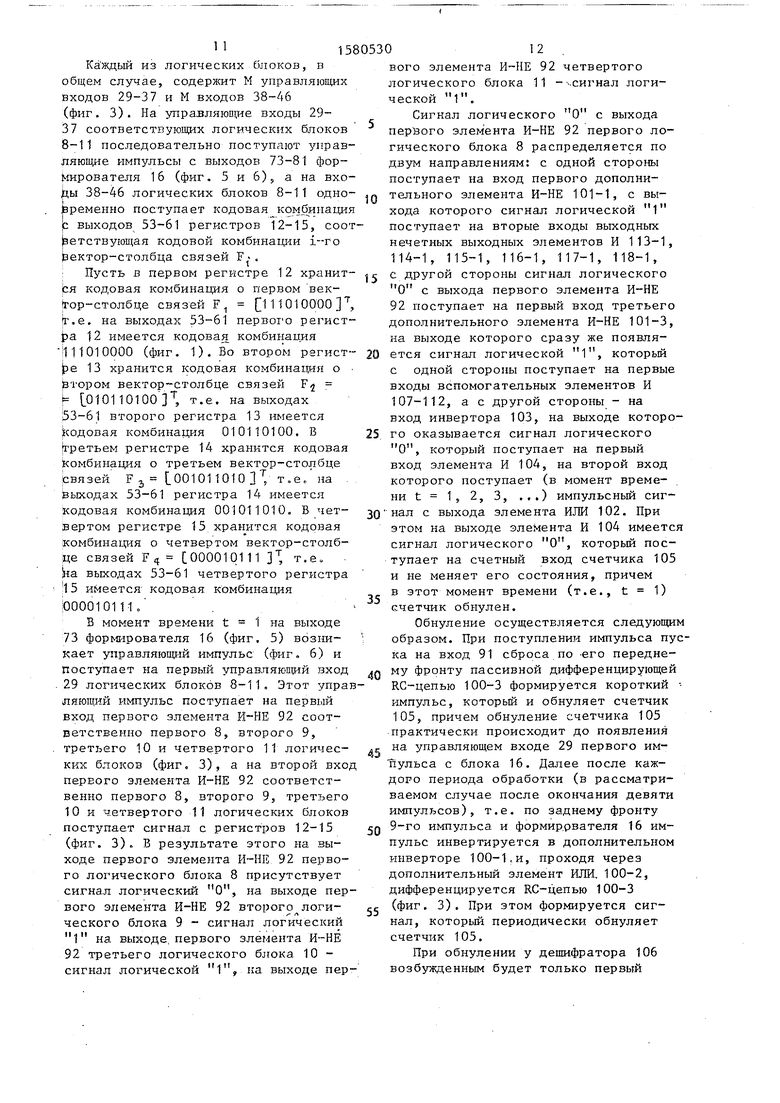

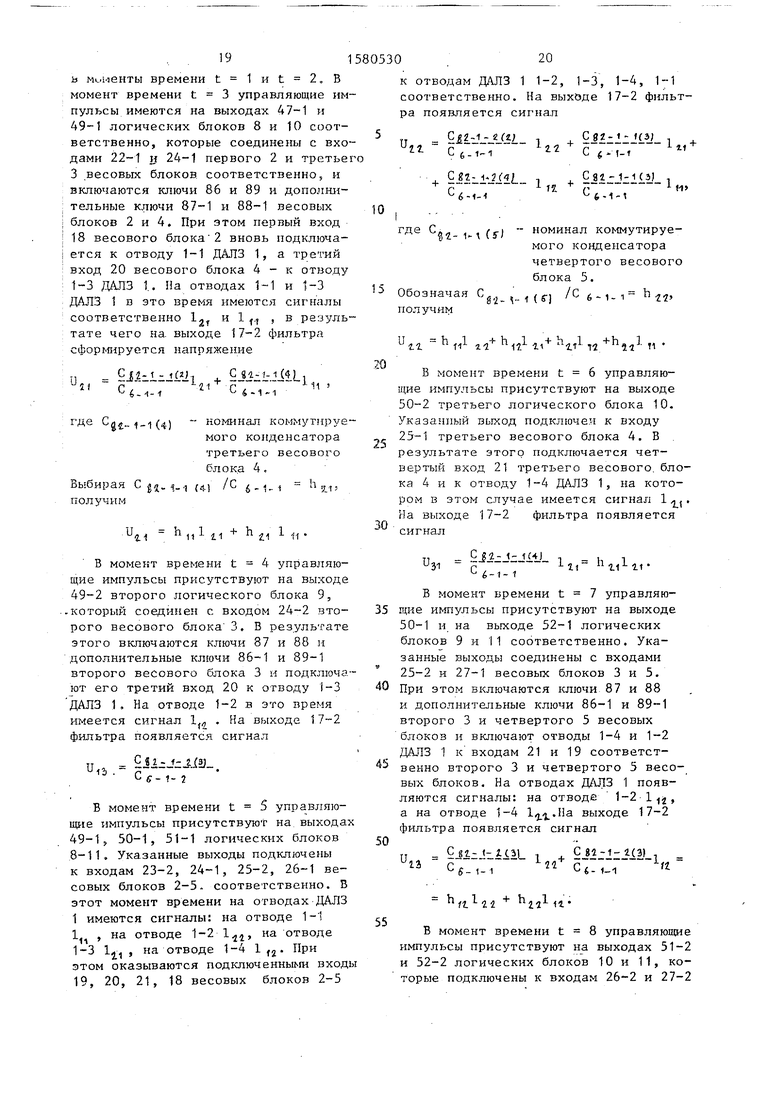

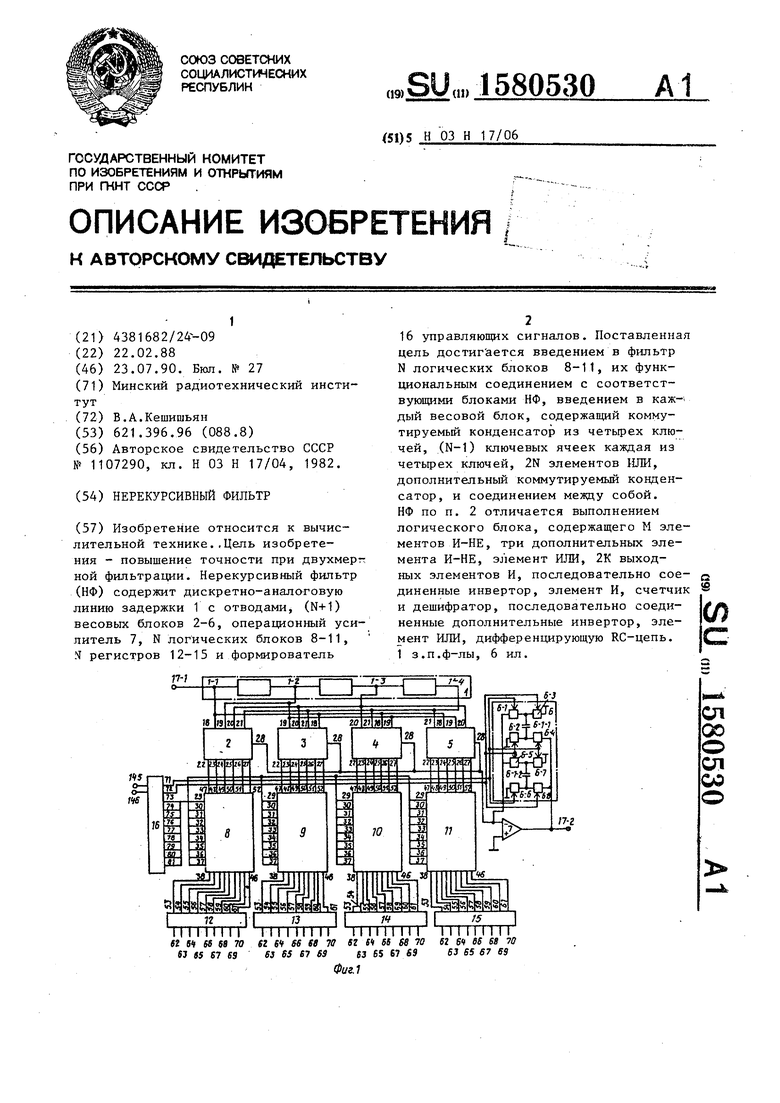

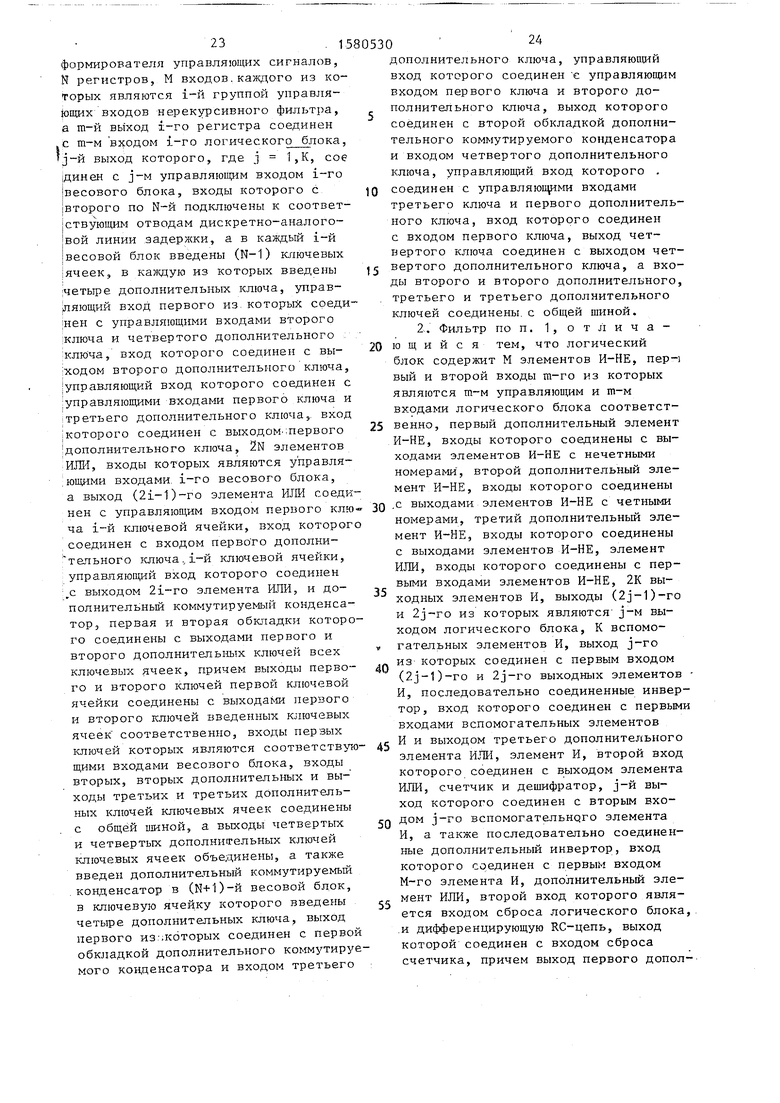

Рассмотрим принцип действия логических блоков 8-11 (фиг. 3)

10

11

Каждый из логических блоков, в общем случае, содержит М управляющих входов 29-37 и М входов 38-46 (фиг. 3). На управляющие входы 29- 37 соответствующих логических блоков 8-11 последовательно поступают управляющие импульсы с выходов 73-81 формирователя 16 (фиг. 5 и 6)5 а на входы 38-46 логических блоков 8-11 одно- рременно поступает кодовая комбинация с выходов 53-61 регистров 12-15, соответствующая кодовой комбинации 1-го Вектор-столбца связей F.

Пусть в первом регистре 12 хранит- «г ся кодовая комбинация о первом вектор-столбце связей F1 J 11010000 7, т.е. на выходах 53-61 первого регистра 12 имеется кодовая комбинация 111010000 (фиг. 1). Во втором регистре 13 хранится кодовая комбинация о втором вектор-столбце связей F2 t 0101 10100 т, т.е. на выходах 53-61 второго регистра 13 имеется Кодовая комбинация 010110100. В Третьем регистре 14 хранится кодовая

20

25

Комбинация о третьем вектор-столбце связей F 3 00101 1010 Т, т.е. на выходах 53-61 регистра 14 имеется Кодовая комбинация 001011010. В четвертом регистре 15 хранится кодовая комбинация о четвертом вектор-столбце связей F ч 0000101 11 т, т.е. |на выходах 53-61 четвертого регистра 15 имеется кодовая комбинация 000010111.

Б момент времени t 1 на выходе 73 формирователя 16 (фиг. 5) возникает управляющий импульс (фиг. 6) и Поступает на первый управляющий вход 29 логических блоков 8-11. Этот управляющий импульс поступает на первый вход первого элемента И-НЕ 92 соответственно первого 8, второго 9, третьего 10 и четвертого 11 логических блоков (фиг. 3), а на второй вход первого элемента И-НЕ 92 соответственно первого 8, второго 9, третьего 10 и четвертого 11 логических блоков поступает сигнал с регистров 12-15 (фиг. 3). В результате этого на выходе первого элемента И-НЕ 92 первого логического блока 8 присутствует сигнал логический О, на выходе первого элемента И-НЕ 92 второго логического блока 9 - сигнал логический 1 на выходе первого элемента И-НЕ 92 третьего логического блока 10 - сигнал логической 1, на выходе пер58053012

вого элемента И-НЕ 92 четвертого логического блока 11 - сигнал логиu 1 t . 11

ческой 1 „

Сигнал логического О с выхода первого элемента И-НЕ 92 первого логического блока 8 распределяется по двум направлениям: с одной стороны поступает на вход первого дополнительного элемента И-НЕ 101-1, с выхода которого сигнал логической 1 поступает на вторые входы выходных нечетных выходных элементов И 113-1, 114-1, 115-1, 116-1, 117-1, 118-1, с другой стороны сигнал логического О с выхода первого элемента И-НЕ 92 поступает на первый вход третьего дополнительного элемента И-НЕ 101-3, на выходе которого сразу же появляется сигнал логической 1, который с одной стороны поступает на первые входы вспомогательных элементов И 107-112, а с другой стороны - на вход инвертора 103, на выходе которого оказывается сигнал логического О, который поступает на первый вход элемента И 104, на второй вход которого поступает (в момент времени t 1, 2, 3, .,.) импульсный сигнал с выхода элемента ИЛИ 102. При этом на выходе элемента И 104 имеется сигнал логического О, который поступает на счетный вход счетчика 105 и не меняет его состояния, причем в этот момент времени (т.е., t 1) счетчик обнулен.

Обнуление осуществляется следующим образом. При поступлении импульса пуска на вход 91 сброса по его переднему фронту пассивной дифференцирующей КС-цепью 100-3 формируется короткий - импульс, который и обнуляет счетчик 105, причем обнуление счетчика 105 практически происходит до появления на управляющем входе 29 первого им- ггульса с блока 16. Далее после каждого периода обработки (в рассматриваемом случае после окончания девяти импульсов), т.е. по заднему фронту 9-го импульса и формиррвателя 16 импульс инвертируется в дополнительном инверторе 100-1,и, проходя через дополнительный элемент ИЛИ. 100-2, дифференцируется RC-цепью 100-3 (фиг. 3). При этом формируется сигнал, который периодически обнуляет счетчик 105.

При обнулении у дешифратора 106 возбужденным будет только первый

30

35

40

45

50

55

выход 106-1 (фиг. 3), остальные выходы находятся в состоянии О. Сигнал логической 1 с первого выхода 106-1 дешифратора 106 поступает на второй вход первого вспомогательного элемента И 107, в результате чего на его выходе будет сигнал логической 1, который поступает на первые входы нечетного и четного выходных эле- ментов И 113-1 и 113-2. Но так как сигнал логической 1 подан на второ вход только нечетного выходного элемента И 113-1, то на его выходе (нечетный выход) 47-1 будет управляющий сигнал логической 1.

В этот же момент времени (t 1) на выходе первых элементов И-НЕ 92 второго 9, третьего 10 и четвертого 11 логических блоков имеются импульсные сигналы логической 1, которые поступают на первый вход первого дополнительного элемента И-НЕ 101-1, на выходе которого оказывается импульсный сигнал логического О, ко- торый, поступая на вторые входы нечетных выходных элементов И 113-1, 114-1, 115-1, 116-1, 117-1, 118-1, запрещает появление управляющего импульса на соответствующих выходах логических блоков 9-11. Однако с другой стороны сигнал логической 1 с выхода первого элемента И-НЕ 92 поступает на первый вход третьего дополнительного элемента И-НЕ 101-3, на выходе которого имеется импульсный сигнал логического О, который с одной стороны оказывается на первых входах вспомогательных элементов И 107-112 и запрещает появление сигналов логической 1 на выходах последних, а с другой стороны импульсный сигнал логического О поступает на инвертор 103, на выходе которого возникает импульсный сигнал логи- ческой 1, который, поступая на первый вход элемента И 104 (на второй вход которого всегда поступает разрешающий импульсный сигнал), формирует импульсный сигнал, который поступает на счетный вход счетчика 105 и по переднему фронту переводит его в новое состояние, в результате (чего возбуждается второй выход 106-2 дешифратора 106 (фиг. 3).

Таким образом, при поступлении на m-й вход логических блоков 8-11 сигнала логической 1 на соответствующем выходе соответствующего логичес

5

0

Q

5 0 5

5

0

кого блока всегда имеется управляющий импульс логической 1, а при поступлении на m-й вход логических блоков 8-11 сигнала логического О, на выходе соответструющего логического блока отсутствует управляющий сигнал, причем подача на его m-й вход сигнала логического О всегда приводит к возбуждению следующего по счету выхода дешифратора 106, а поступление на m-й информационный вход логической 1 не приводит к возбуждению следующего по счету выхода дешифратора 106, а оставляет возбужденным выход, который задействован в предшествующие моменты.

Рассмотрим формирование управляющих импульсов на выходах логических блоков 8-11 в различные моменты времени о

В момент времени t 1 у первого логического блока 8 на нечетном выходе 47-1 присутствует управляющий сигнал логической 1, При этом возбужден первый выход 106-1 дешифратора 106 (фиг. 3). У логических блоков 9-11 управляющий сигнал логической 1 на выходах отсутствует. При этом возбуждается второй выход 106-2 дешифратора 106.

В момент времени t 2 на четном выходе 47-2 первого логического блока 8 присутствует сигнал логической 1. При этом возбужденным остается первый выход 106-1 дешифратора 106. У второго логического блока 9 имеется сигнал логической 1 на четном выходе 48-2. При этом возбужден второй выход 106-2 дешифратора 106 (фиг. 3). У логических блоков 10 и 11 на их выходах управляющие сигналы логической 1 отсутствуют. При этом происходит возбуждение третьего выхода 106-3 дешифратора 106 обоих логических блоков.

В момент времени t 3 появляется управляющий сигнал логической 1

на нечетном выходе 47-1 первого логического блока 8. При этом вновь оказывается возбужденным только первый выход 106-1 дешифратора 106. У второго логического блока 9 управляющий сигнал на выходе отсутствует. При этом происходит возбуждение третьего

выхода 106-3 дешифратора 106. У третьего логического блока 10 присутствует управляющий сигнал логической 1 на нечетном выходе 49-1. При этом возбужденным остается третий

15

1580530

выход 106-3 дешифратора 106. У чет- вертого логического блока 11 на вы- ходе отсутствует управляющий сигнал. При этом происходит возбуждение четвертого выхода 106-4 дешифратора 106.

В момент времени t 4 у первого логического блока 8 на выходе отсутствует управляющий сигнал. При этом происходит возбуждение второго вы- |кода 106-2 дешифратора 106. У второ- ho логического блока 9 появляется управляющий сигнал логической 1 На четном выходе 49-2. При этом возбужденным остается третий выход 106-3 дешифратора 106. У третьего логического блока 10 управляющий сигнал на выходе отсутствует. При этом Происходит возбуждение четвертого выхода 106-4 дешифратора 106. У четвертого логического блока 11 на выходе управляющий сигнал также отсутствует. При этом происходит возбуждение пятого выхода 106-5 дешифратора 106.

В момент времени t 5 у первого логического блока 8 управляющий сигнал логической 1 имеется на нечетном выходе 48-1. При этом остается возбужденным второй выход 106-2 дешифратора 106. У второго логического блока 9 на выходе присутствует управляющий сигнал логической 1 на нечетном выходе 49-1, При этом возбужденным остается третий выход 106-3 дешифратора 106. У третьего логического блока 10 управляющий сигнал логической 1 присутствует на нечетном выходе 50-1. При этом возбуждена ным остается четвертый выход 106-4 дешифратора 106. У четвертого логического блока 11 управляющий сигнал логической 1 имеется на нечетном выходе 51-1. При.этом возбужденным остается пятый выход 106-5 дешифратора 106.

В момент времени t 6 оставшиеся кодовые комбинации, хранящиеся в первом регистре Т 2 и которые поступают на входы первого логического блока 8, представляют собой сигналы логического О, и очевидно, что в оставшемся,цикле работы (состоящем из 9 тактов) логический блок 8 участвовать не будет. У второго логического блока 9 управляющий сигнал на выходе отсутствует. При этом возбуждается четвертый выход 106-4 дешифратора 106. У третьего логического бло30

5

0

5

0

5

0

5

16

ка 10 сигнал логической 1 имеется на четном выходе 50-2. Нри этом возбужденным остается четвертый выход 106-4 дешифратора 106. У четвертого логического блока 11 на выходе сигнал отсутствует. При этом происходит возбуждение шестого выхода 106-6 дешифратора 106.

В момент времени t 7 у второго логического блока 9 имеется сигнал логической 1 на нечетном выходе 50-1. При этом остается возбужденным третий выход 106-3 дешифратора 106. У третьего логического блока 10 отсутствует управляющий сигнал логической 1 на выходе. При этом возбуждается пятый выход 106-5 дешифратора 106. У четвертого логического блока 11 управляющий сигнал логической 1 присутствует на нечетном выходе 52-1. При этом остается возбужденным шестой выход 106-6 дешифратора. 106.

В момент времени t 9 второй логический: блок 9 в оставшихся тактах цикла уже не участвует. У третьего логического блока 10 имеется сигнал логической 1 на четном выходе 51-2. При этом остается возбужденным шестой выход 106-6 дешифратора 106. У четвертого логического блока 11 присутствует сигнал логической 1 на четном выходе 52-2.

В момент времени t - 9 участвует в работе только четвертый логический блок 11. На его нечетном выходе 52-1 имеется управляющий сигнал логической 1. Момент времени t 9 является последним тактом в цикле работы нерекурсивного фильтра.

Рассмотрим работу непосредственно нерекурсивного фильтра. Пусть входной массив сигналов lj: представлен матрицей размера (2 х 2), а весовые коэффициенты также представлены матрицей размера (2 х2). Тогда выходной обработанный массив сигналов можно представить в виде

L11

4l

11

11

21 Ml

№и h«

55

Представим двумерный массив входных сигналов в виде одномерной последовательности

1ц+ xtl

Z +

i4tw

+ 4azw

а двумерный массив весовых коэффици- ентов - в виде одномерной последовательности

- hn +

h,fW

h4tZW.

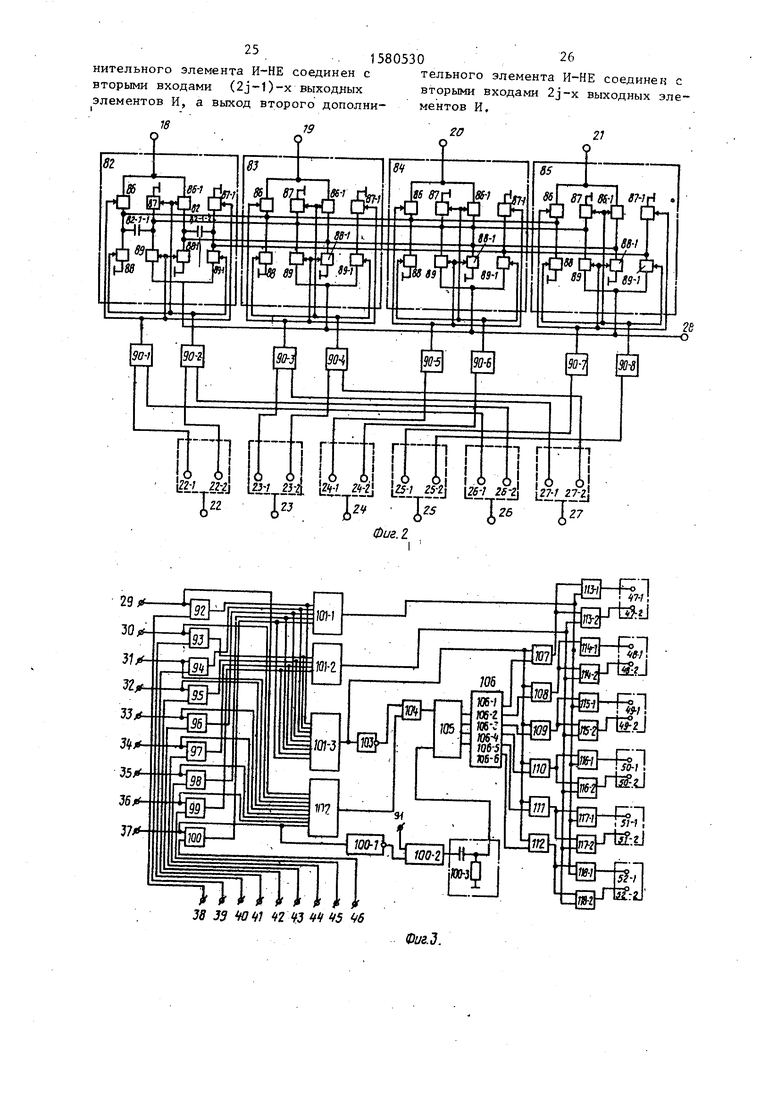

Тогда в момент времени t 1 на отводе 1-1 ДАЛЗ 1 имеется напряжение 1м , которое поступает на первый вход 18 первого весового блока 2 (фиг. 1). В этот момент времени существует только управляющий импульс на нечетном выходе 47-1 первого логического блока 8, причем выход 47-1 соединен с нечетным входом 22-1 первого весового блока 2. В результате этого на выходе первого элемента ИЛИ 90-1 присутствует сигнал логической 1, который включает ключи 86 и 89, а также включает дополнительные ключи 87-1 и 86-1, что приводит к снятию имеющихся (если они были) зарядов на дополнительном коммутируемом конденсаторе

82-1-2 (фиг. 2). В это же время первым управляющим импульсом с выхода 71 формирователя 16 включаются ключи 6-1 и 6-4 (а также дополнительные ключи 6-6 и 6-7, что приводит к снятию имеющихся, если они были, зарядов на дополнительном коммутируемом конденсаторе 6-1-2). В результате этого происходит заряд коммутируемого конденсатора 82-1-1 до значения напряжения, существующего на входе 18 весового блока 2. Выход 28 весового блока 2 соединен с инвертирующим входом операционного усилителя 7. Происходит заряд коммутируемого конденсатора 6-1-1 (N+1) весового блока 6 . В результате на выходе устройства 17-2 сформируется сигнал

U

11

1 М-1: 1«С

де С

6-1-1

Jgl-1-(l)

-t-i

коммутируемый конденсатор в дополнительном (N+O-M весовом блоке.

6;

коммутируемый конденсатор первого весового блока 2.

Выбирая значение С

11

получим

81-f-f(i

U

И

111- hn

В момент 1-1 ДАЛЗ

времени t 1 имеется

2 на отво- напряжение 1

а на отводе 1-2 ДАЛЗ 1 - напряже0

5

0

5

0

5

0

5

ние

I

11

Б это

время имеется управляющий сигнал логической 1 на четном выходе 47-1 первого логического блока 8, который подключен к четному входу 22-2 первого весового блока 2, В то же время имеется управляющий сигнал логической 1 на четном цы- ходе 48-2 второго логического блока 9, который соединен с нечетным входом 23-1 второго весового блока 3. В результате этого эти импульсы, пройдя через элементы ИЛИ 90-2 и 90-3 первого 2 и второго 3 весовых блоков соответственно, включают ключи 87 и 88, а также дополнительные .ключи 86-1 и 89-1 первого весового блока 2 и ключи 86 и 89, а также дополнительные ключи 87-1 и 88-1 второго весового блока 3, что приводит к заряду дополнительного коммутируемого конденсатора 82-1-2 (в это же время происходит разряд коммутируемого конденсатора 82-1-1 и подготавливает его к новому такту работы) . Через открытые ключи 86 и 89 ключевой ячейки 83 второго весового блока 3 заряжается его коммутируемый конденсатор 82-1-1. При этом управляющим сигналом со второго выхода 72 формирователя 16 включаются дополнительные ключи 6-5 и 6-8, а также ключи 6-2 и 6-3 (N+1)-ro весового блока 6, что приводит к разряду коммутируемого конденсатора 6-1-1 и подготавливает его к новому 1акту работы, с другой стороны заряжается дополнительный коммутирующий конденсатор 6-1-2, что приводит к тому, что у весового блока 2 первый вход 18 подключается к отводу 1-1 ДАЛЗ 1, а у весового блока 3 подключается второй вход 19 к отводу 1-2 ДАЛЗ 1 Таким образом, в момент времени t 2 на выходе 17-2 фильтра сформируется сигнал

0

5

U

11

где С

$№-1--ИЛ1 + Јlt:.t--JiiLi CS-1-1

Ml

11

li-t-tfa)

ct-i-i

- коммутируемый конденсатор второго весового блока.

Ь

Обозначая Cgl. , /С . получим

42

и,

h 11l f

h«l

fi 11 ft T и-1- п

Работа (N+1)-rc весового блока в последующих тактах аналогична работ

191

t 1 и t 2. В управляющие им5

ь моменты времени момент времени t 3 пульсы имеются на выходах 47-1 и 49-1 логических блоков 8 и 10 соответственно, которые соединены с входами 22-1 и 24-1 первого 2 и третьег 3 весовых блоков соответственно, и включаются ключи 86 и 89 и дополнительные ключи 87-1 и 88-1 весовых блоков 2 и 4. При этом первый вход 18 весового блока 2 вновь подключается к отводу 1-1 ДАЛЗ 1, а третий вход 20 весового блока 4 - к отводу 1-3 ДАЛЗ 1. На отводах Ы и 1-3 ДАЛЗ 1 в это время имеются сигналы

соответственно и 1

ft

тате чего на выходе 17-2 сформируется напряжение

580530

20

к отводам ДАЛЗ 1 1-2, 1-3, 1-4, 1-1 соответственно. На выходе 17-2 фильтра появляется сигнал

11

- P..JL(2 т .

,, 1 л л „

6-1-1

Јtiz..

б-1-

2.2

п.

С ЈM-f

Cai-1-кэ)

с

t-1-t

U,+

и

где си-1мЫ

Обозначая С

получим

«4- -i «Ч

номинал коммутируемого конденсатора четвертого весового блока 5.

/С б 1- т h -г

uit h

г Ь141г1+Ь1Т1

w+hn

Т1

| название | год | авторы | номер документа |

|---|---|---|---|

| Нерекурсивный фильтр | 1982 |

|

SU1107290A1 |

| Формирователь матричных команд | 2018 |

|

RU2707913C1 |

| Дискретно-аналоговый анализатор ортогональных составляющих спектра электрических сигналов | 1975 |

|

SU553547A1 |

| Устройство параллельной обработки видеоинформации | 1989 |

|

SU1651299A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| РАДИОИНТРОСКОП | 1995 |

|

RU2067759C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| ВЫСОКОПАРАЛЛЕЛЬНЫЙ СПЕЦПРОЦЕССОР ДЛЯ РЕШЕНИЯ ЗАДАЧ О ВЫПОЛНИМОСТИ БУЛЕВЫХ ФОРМУЛ | 1993 |

|

RU2074415C1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 2002 |

|

RU2234147C2 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение точности при двухмерной фильтрации. Нерекурсивный фильтр (НФ) содержит дискретно-аналоговую линию задержки 1 с отводами, (N+1) весовых блоков 2-6, операционный усилитель 7, N логических блоков 8-11, N регистров 12-15 и формирователь 16 управляющих сигналов. Поставленная цель достигается введением в фильтр N логических блоков 8-11, их функциональным соединением с соответствующими блоками НФ, введением в каждый весовой блок, содержащий коммутируемый конденсатор из четырех ключей, (N-1) ключевых ячеек каждая из четырех ключей, 2N элементов ИЛИ, дополнительный коммутируемый конденсатор, и соединением между собой. НФ по п.2 отличается выполнением логического блока, содержащего М элементов И - НЕ, три дополнительных элемента И - НЕ, элемент ИЛИ, 2К выходных элементов И, последовательно соединенные инвертор, элемент И, счетчик и дешифратор, последовательно соединенные дополнительные инвертор, элемент ИЛИ, дифференцирующую RC-цепь. 1 з.п. ф-лы, 6 ил.

GJ2-f - i(b , с () 1 -„.+ - J

6-i-f

21

c 4-1-1

M

Cge., 1(4)

номинал коммутируемого конденсатора третьего весового блока 4.

Выбирая С j j,. i , (4.j /С

б-1-i

h г

У 15

получим

- h 11111

+ h

21

1

В момент времени t 4 управляющие импульсы присутствуют на выходе 49-2 второго логического блока 9, -который соединен с входом 24-2 второго весового блока 3, В результате этого включаются ключи 87 и 88 и дополнительные ключи 86-1 и 89-1 второго весового блока 3 и подключают его третий вход 20 к отводу I-3 ДАЛЗ 1. На отводе 1-2 в это время

имеется сигнал 1

fl

На выходе 17-2

фильтра появляется сигнал

О

ЈiI-J-J.l2J.

Ce-tt- 1

В момент времени t S управляющие импульсы присутствуют на выхода 49-1, 50-1, 51-1 логических блоков 8-11. Указанные выходы подключены к входам 23-2, 24-1, 25-2, 26-1 весовых блоков 2-5. соответственно. В этот момент времени на отводах ДАЛЗ 1 имеются сигналы: на отводе 11-3 1

на отводе 1-2 114, на отводе

И

на отводе

1-4 1

f 2

При

этом оказываются подключенными вход 19, 20, 21, 18 весовых блоков 2-5

В момент времени t 6 управляющие импульсы присутствуют на выходе 50-2 третьего логического блока 10. Указанный выход подключен к входу 25-1 третьего весового блока 4. В результате этого подключается четвертый вход 21 третьего весового блока 4 и к отводу 1-4 ДАЛЗ 1, на котором в этом случае имеется сигнал 1 (. На выходе 17-2 фильтра появляется сигнал

5

0

5

0

U

С«2- 1- U4J 31 с

ii пгЛи

6-1- 1

В момент времени t 7 управляющие импульсы присутствуют на выходе 50-1 и на выходе 52-1 логических блоков 9 и И соответственно. Указанные выходы соединены с входами 25-2 и 27-1 весовых блоков 3 и 5. При этом включаются ключи 87 и 88 и дополнительные ключи 86-1 и 89-1 второго 3 и четвертого 5 весовых блоков и включают отводы 1-4 и 1-2 ДАЛЗ 1 к входам 21 и 19 соответственно второго 3 и четвертого 5 весовых блоков. На отводах ДАЛЗ 1 появляются сигналы: на отводе 1-2 1-и , а на отводе 1-4 l.Ha выходе 17-2 фильтра появляется сигнал

U

13

Cji-JziilL

5-1-1

1„+

(.l) с (.- 1-1

1к- h 1 г 1 г г

,

В момент времени t 8 управляющие импульсы присутствуют на выходах 51-2 и 52-2 логических блоков 10 и 11, которые подключены к входам 26-2 и 27-2

соответственно третьего 4 и четвертого 5 весовых блоков. При этом включаются ключи 87 и 88 и дополнительные ключи 86-1 и 89-1, а также ключи 86 и 89 и дополнительные ключи 87-1 и 88-1 соответственно весовых блоков 4 и 5, в результате чего подключаются первый t8 и второй 19 входы соответственно третьего 4 и четвертого 5 весовых блоко в к отводам 1-2 и 1-1 ДАЛЗ 1. В это время на этих отводах имеются сигналы: на отводе 1-2 121 , на отводе 1-1 На выходе 17-2 фильтра появляется сигнал

U , СJi-Jt JiL 1 + ClbL-jjJ2

V,2 - г с - - - 1

-1-2

- Ь211 гг+ ,

В момент времени t 9 присутствует управляющий импульс на выходе 52-1 четвертого логического блока 11, который соединен с входом 27-1 четвертого весового блока 5. При этом включаются ключи 87 и 88 и дополнительные ключи 86-1 и 89-1 и подключают вход 19 четвертого весового блока 5 к отводу 1-2 ДАЛЗ 1. На отводе 1-2 в это время имеется сигнал 144. Тогда на выходе 17-2 фильтра появляется сигнал

С H.I-1(2 , ъ -i- 1,„- п

С t-f-1

и

Таким образом, за девять тактов управляющих импульсов с выхода формирователя 16 формируется полный массив обработанных двумерных выходных сигналов размера (3 «3). Далее процесс обработки повторяется.

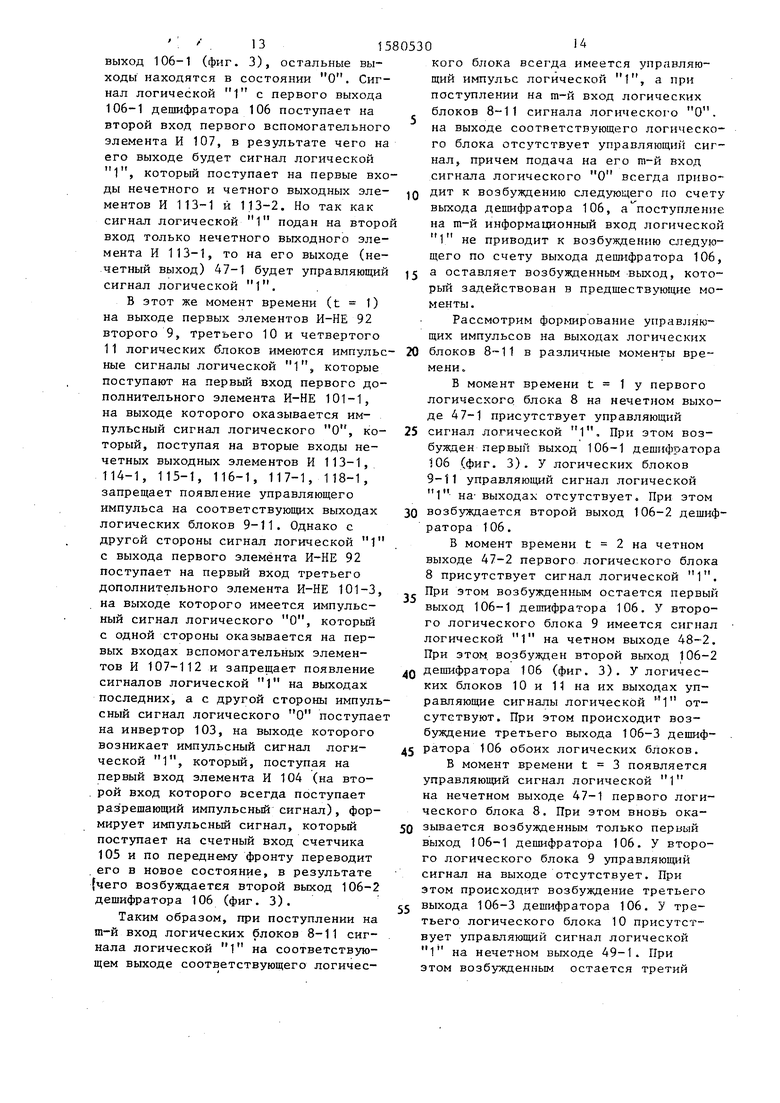

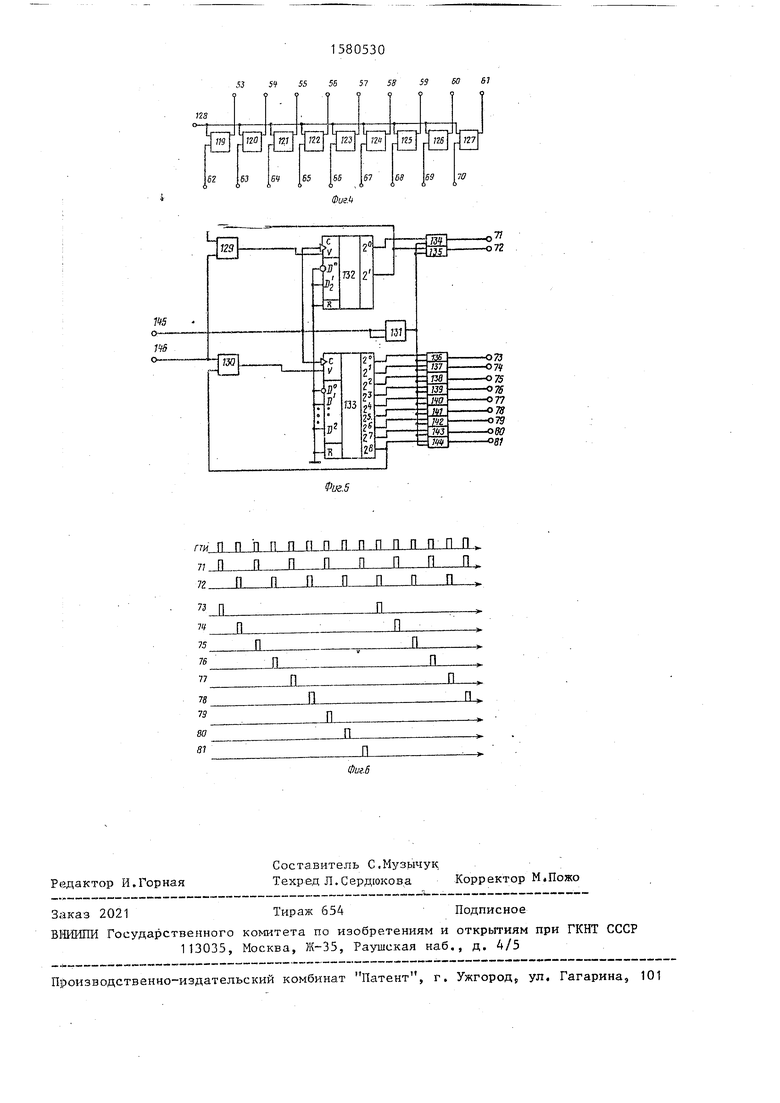

Формирователь 16 управляющих сиг- налов работает следующим образом.

Тактовые импульсы от внешнего генератора тактовых импульсов поступают на вход 145, а также на входы С регистров 132 и 133 и через элемент И 131 на вторые входы выходных элементов И 134-144.

Внешний источник одиночного импульса Пуск подключается к входу 146 формирователя 16 (фиг. 5) для определения начала работы фильтра, по которому на выходах элементов ИЛИ 129 и 130 формируются сигналы подгоовки приема информации в регистры 132 и 133. По переднему фронту тактового импульса попавшего в строб сигнала подготовки приема информа0

5

0

5

0

5

0

5

0

5

ции осуществляется запись кода 1,0 в регистр 132 и кода 1,0, ..., О в регистр 133, т.е. происходит запись логической 1 в первые разряды регистров, в результате чего на выходах 71 и 73 формируются управляющие сигналы. Далее принцип работы форми- рователя 16 очевиден. Временная диаграмма работы формирователя 16 приведена на фиг. 6.

Формула изобретения

К Нерекурсивный фильтр, содержащий операционный усилитель, выход которого является выходом нерекурсив- ного фильтра, N весовых бтоков, дискретно-аналоговую линию задержки, вход которой является входом нерекурсивного фильтра, а ее i-й отвод, где i 1,N, соединен через i-й весовой блок с инвертирующим входом операционного усилителя, неинвертирующий вход которого соединен с общей шиной, а также (N+O-й весовой блок, вход и выход которого соединен с входом и выходом операционного усилителя соответственно, и формирователь управляющих сигналов, первый и второй выходы которого соединены с первым и вторым управляющими входами (N+1)-го весового блока соответственно, а каждый весовой блок содержит коммутируемый конденсатор и ключевую ячейку, содержащую четыре ключа, выход первого из которых соединен с входом третьего ключа, управляющий вход которого соединен с управляющим входом второго ключа, выход которого соединен с входом четвертого ключа, управляющий вход которого соединен с управляющим входом первого ключа, причем первая и вторая обкладки коммутируемого конденсатора соединены с выходами первого и третьего ключей соответственно, вход первого и выход четвертого ключа являются входом и выходом весового блока соответственно, а первым и вторым управляющими входами (N-H)-ro весового блока являются управляющие входы первого и второго ключей соответственно, отличающийся тем, что, с целью повышения точности при двухмерной фильтрации, введены N логических блоков, т-и управляющий вход каждого из которых, где m « 1,М соединен с (т+2)-м выходом

формирователя управляющих сигналов, N регистров, М входов каждого из которых являются i-й группой управляющих входов нерекурсивного фильтра, а m-й выход 1-го регистра соединен ,с m-м входом 1-го логического блока, j-й выход которого, где j 1,K, сое динен с j-м управляющим входом 1-го весового блока, входы которого с второго по N-и подключены к соответствующим отводам дискретно-аналоговой линии задержки, а в каждый i-й весовой блок введены (N-1) ключевых ячеек, в каждую из которых введены четыре дополнительных ключа, управляющий вход первого из которых соединен с управляющими входами второго ключа и четвертого дополнительного ключа, вход которого соединен с выходом второго дополнительного ключа, управляющий вход которого соединен с управляющими входами первого ключа и третьего дополнительного ключа, вход которого соединен с выходом первого дополнительного ключа, 2N элементов ИЛИ, входы которых являются управляющими входами 1-го весового блока, а выход (21-1)го элемента ИЛИ соединен с управляющим входом первого клю ча i-й ключевой ячейки, вход которог соединен с входом первого дополнительного ключа i-й ключевой ячейки, управляющий вход которого соединен „с выходом 21-го элемента ИЛИ, и до- полнительный коммутируемый конденсатор, первая и вторая обкладки которого соединены с выходами первого и второго дополнительных ключей всех ключевых ячеек, причем выходы перво- го и второго ключей первой ключевой ячейки соединены с выходами первого и второго ключей введенных ключевых ячеек соответственно, входы первых ключей которых являются соответствую щими входами весового блока, входы вторых, вторых дополнительных и выходы третьих и третьих дополнительных ключей ключевых ячеек соединены с общей шиной, а выходы четвертых и четвертых дополнительных ключей ключевых ячеек объединены, а также введен дополнительный коммутируемый конденсатор в (Н+1)-й весовой блок, в ключевую ячейку которого введены четыре дополнительных ключа, выход первого из .которых соединен с первой обкладкой дополнительного коммутируемого конденсатора и входом третьего

0

5

. 0 5 0 5 0 5

дополнительного ключа, управляющий вход которого соединен с управляющим входом первого ключа и второго дополнительного ключа, выход которого соединен с второй обкладкой дополнительного коммутируемого конденсатора и входом четвертого дополнительного ключа, управляющий вход которого . соединен с управляющими входами третьего ключа и первого дополнительного ключа, вход которого соединен с входом первого ключа, выход четвертого ключа соединен с выходом четвертого дополнительного ключа, а входы второго и второго дополнительного, третьего и третьего дополнительного ключей соединены с общей шиной.

О О О

К-Л 97.t 7-7

I

27

Э-fi,

jrted

B-fi7

::&™d

53 54 55 56 57 53 53 50 57

| Нерекурсивный фильтр | 1982 |

|

SU1107290A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-23—Публикация

1988-02-22—Подача