ел

оо

Јъ

NU

00

ров зашунтировагы обрап-ъ ми диодами 24, 25, обеспечивает такой алгоритм коммутации транзисторов 1, 2л 16,

при котором уыхид не н пряжения всех 2М каналов стааипизиртнтск на заданном уоовне. 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты | 1984 |

|

SU1205240A1 |

| Преобразователь частоты | 1982 |

|

SU1150711A1 |

| Преобразователь частоты | 1986 |

|

SU1403287A2 |

| Однофазный преобразователь частоты | 1987 |

|

SU1800569A1 |

| Устройство для контроля правильности электрического монтажа | 1984 |

|

SU1216782A1 |

| Импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1337887A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| СПОСОБ ДВУХТАКТНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕГРИРУЮЩЕГО ТИПА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2564909C1 |

| Устройство контроля сопротивления изоляции | 1988 |

|

SU1597770A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

Изобретение относится к электронике, в частности к бестрансформаторным понижающим источникам вторичного электропитания. Целью изобретения является расширение функциональных возможностей путем получения 2M источников двухполярного напряжения различной амплитуды. Многоканальный стабилизированный конвертор содержит два последовательно соединенных разрядных транзистора 1, 2, зарядный транзистор 16. Введение 2M-1 зарядно-разрядных блока, каждый из которых содержит несколько последовательно соединенных цепочек, образованных последовательно соединенными накопительным конденсатором 6 и зарядным диодом 7, точки соединения которых связаны через первые разрядные диоды 15 с первым входом соответствующего выходного фильтра 11, 12, подключенного выходом к выходным выводам, а точки соединения упомянутых цепочек через вторые разрядные диоды 8 связаны с силовым электродом соответствующего разрядного транзистора, входы выходных фильтров зашунтированы обратными диодами 24, 25, обеспечивает такой алгоритм коммутации транзисторов 1, 2 и 16, при котором выходные напряжения всех 2M каналов стабилизируются на заданном уровне. 4 ил.

Изобретенье относится к зпехтро

технике, в частности к бестрансформа- торньвч понижающим источникам вторичного электропитания,

Цель изобретения - расширение функциональных возможностей путем получения 2М источников двухполярного на- гтояжения различной амплитуды.

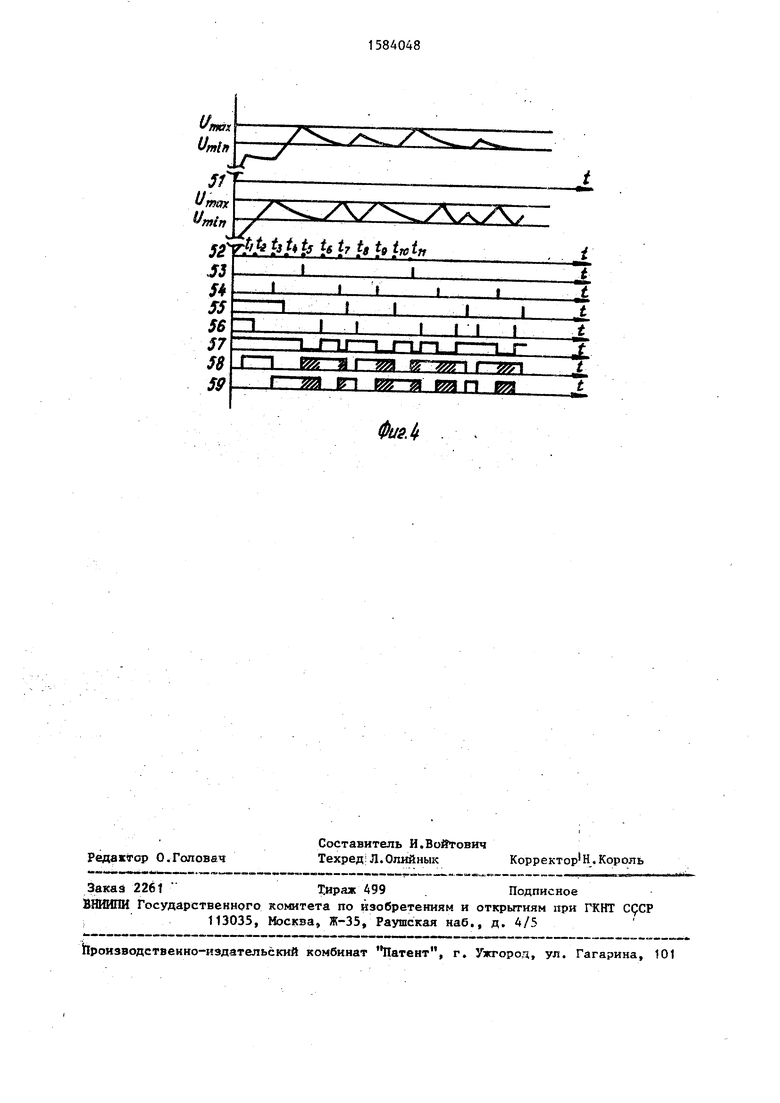

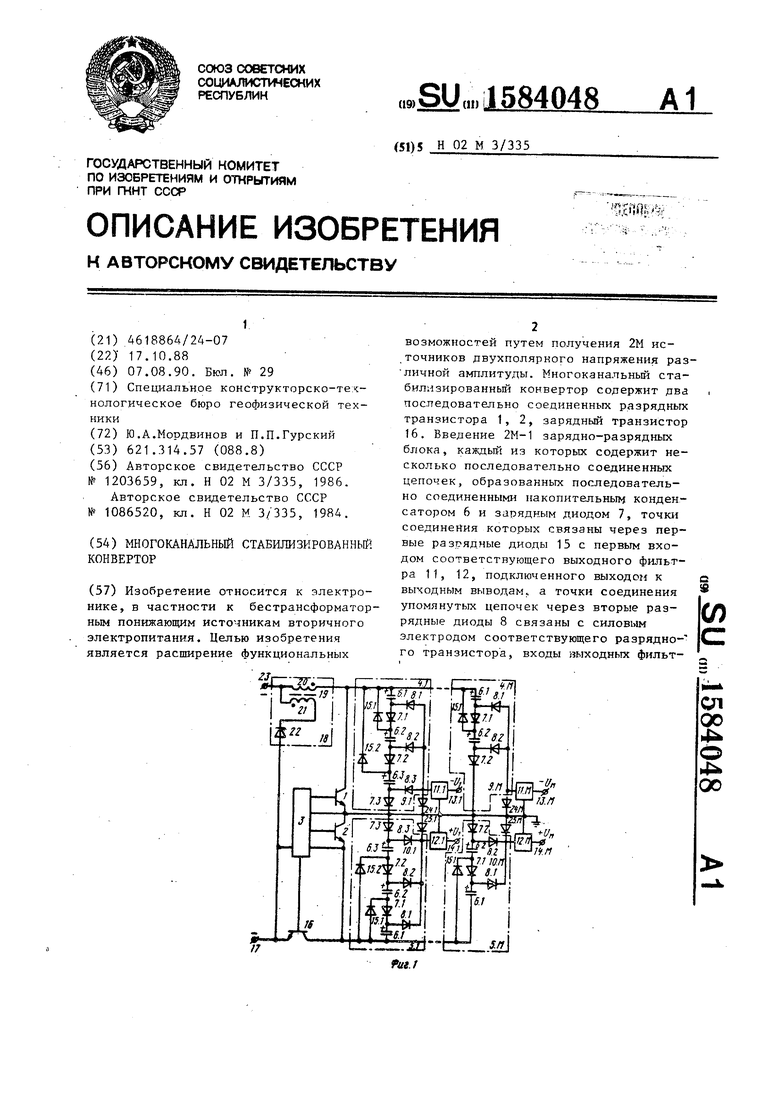

Ка фиг„ 1 представлена схема кон- вертора| на фиг. 2 - схема подключения датчиков напряжения не фиг. 3 - схема блока управления; на фиг. 4 - вргпенные диаграммы, поясняющие работу конвертора,

, Многоканальный стабилиъчрованный IxoHtspTop (фиг. 1} содержит два m ч- ледовательно соединенных разрядник транзистора 1 и 2, упраг.гечп«- которых СВЯЗЭЫУ с блоком 3 уггчар.

зарядно-рачЈ;якные бло. -. ; - .М} каждый и-:, которых сос Ь И э

4Л,

деужит несколько последовательно цнненньгк цепочек, образованных пс--л - довательно соединенными накопительным конденсатором 6.1 (6.2, .„.) и заряц- лым диодом 7.1 { «2, .,, ,) s точки сое

.Шипения которык связаны через первые разрядные диоды 8.1 (8,/. . ,) с первым 9 .1, 1Q.t:(9u2,..., J.0n2,,..) входом соответствующего пштсцного йда-it-ipa 11 Л, 12,1 (11.2, ..., 12„29 ..., 12.М), подключенного выходом к ыходным выводам 13 Л, 14 Л (13,2- ,М, 14.2-1&.М), а точки соединения указанных цапочек через втсч-ые раэ- рп, диодч 15.1 ( ...) еьяза- с. силовь:м электродом СООТВР.ТСТЗУКЗ- maro разрядного транзистора 1, 2), а гядный траг.зястор 16, силовые электроды которого соедчнгни с первым 1/ вхс, выводом и свободным СЯЛОРЫМ электродом транзистора в связанного с конденсаторами 6.1 зарйдно-рэзряд кык блоков 5.1-5.М, тоюограничияаюj щий элемент 18Р включзюащйч например j дроссель 19 с обмотками 20 к 21 s чьи ч. к,(ды подкпючену и отсекай- ещ диод t,9 к второ.чу входнок; эыьодт; 23 и свойодноку силовому электроду транзистора 19 соединенному с.

0

0

5

0

5

0

конденсаторами 6.1 зарядно-раэряд- нь ч блоков 4.1-4.М, другэй силовой эпе -трэд транзистора связан с обратными /йодами 24 Л-24.М, 25 Л-25.М, обеспечивающими работу фильтра, например, структуры LC.

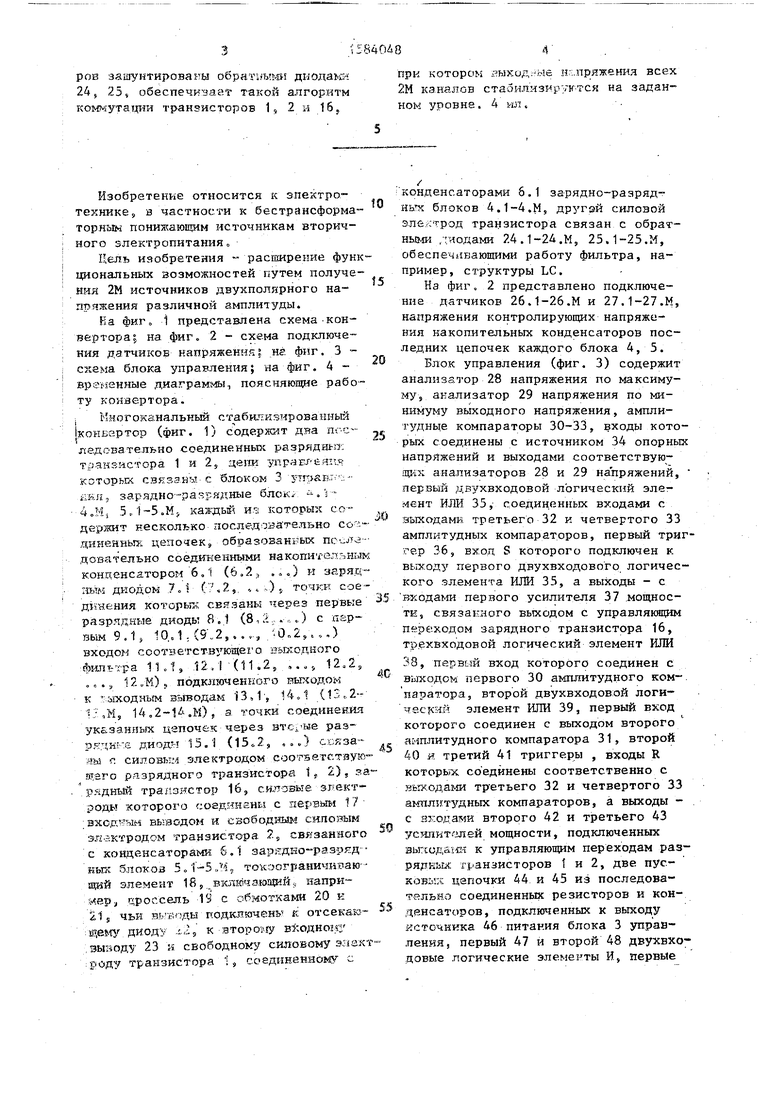

На фиг, 2 представлено подключение датчиков 26 Л-26.М и 27 Л-27.М, напряжения контролирующих напряжения накопительных конденсаторов последних цепочек каждого блока 4, 5.

Блок управления (фиг. 3) содержит анализатор 28 напряжения по максимуму, анализатор 29 напряжения по минимуму выходного напряжения, амплитудные компараторы 30-33, входы которых соединены с источником 34 опорных напряжений и выходами соответствующих анализаторов 28 и 29 напряжений, первый двухвходовой логический элемент ИЛИ 35, соединенных входами с выходами третьего 32 и четвертого 33 амплитудных компараторов, первый триггер 36, вход S которого подключен к выходу первого двухвходового логического элемента ИЛИ 35, а выходы - с входами первого усилителя 37 мощности, связагного выходом с управляющим переходом зарядного транзистора 16, трехвходовой логический элемент ИЛИ

38, первий вход которого соединен с выходом первого 30 амплитудного компаратора, второй двухвходовой логи- vecfctf элемент ИЛИ 39, первый вход

L

которого соединен с выходом второго амплитудного компаратора 31, второй 40 и третий 41 триггеры , входы R которых соединены соответственно с ВЕГХодами третьего 32 и четвертого 33 амплитудных компараторов, а выходы - с алодами второго 42 и третьего 43 усилителей мощности, подключенных вычо&йни к управляющим переходам раз- рярьых, транзисторов 1 и 2, две пусковая цепочки 44 и 45 из последовательно соединенных резисторов и конденсаторов, подключенных к выходу источника 46 питания блока 3 управления, первый 47 и второй 48 двухвхо- цовые логические элементы И, первые

5Г

входы которых подключены к выходу первой пусковой цепочки 44, вторые входы - соответственно к выходу четвертого амплитудного компаратора и Инверсному выходу третьего триггера 41, а их выходы - к второму и третьему входам трехвходового логического элемента ИЛИ 38, третий двухвходовой логический элемент И 49, входы которого подключены к выходу третьего амплитудного компаратора и выходу второй пусковой цепочки 45, а выход к второму входу второго логического элемента ИЛИ 39, четвертый двухвхо- довой логический элемент И 50, входы которого соединен с прямыми выходам второго 40 и третьего 41 триггеров, а ЕЫУОД - с R-входом первого триггера 36, при этом входы S второго 40 и третьего 41 триггеров связаны соответственно с выходами трехвходового 38 и второго двухвходового 39 логических элементов ИЛИ.

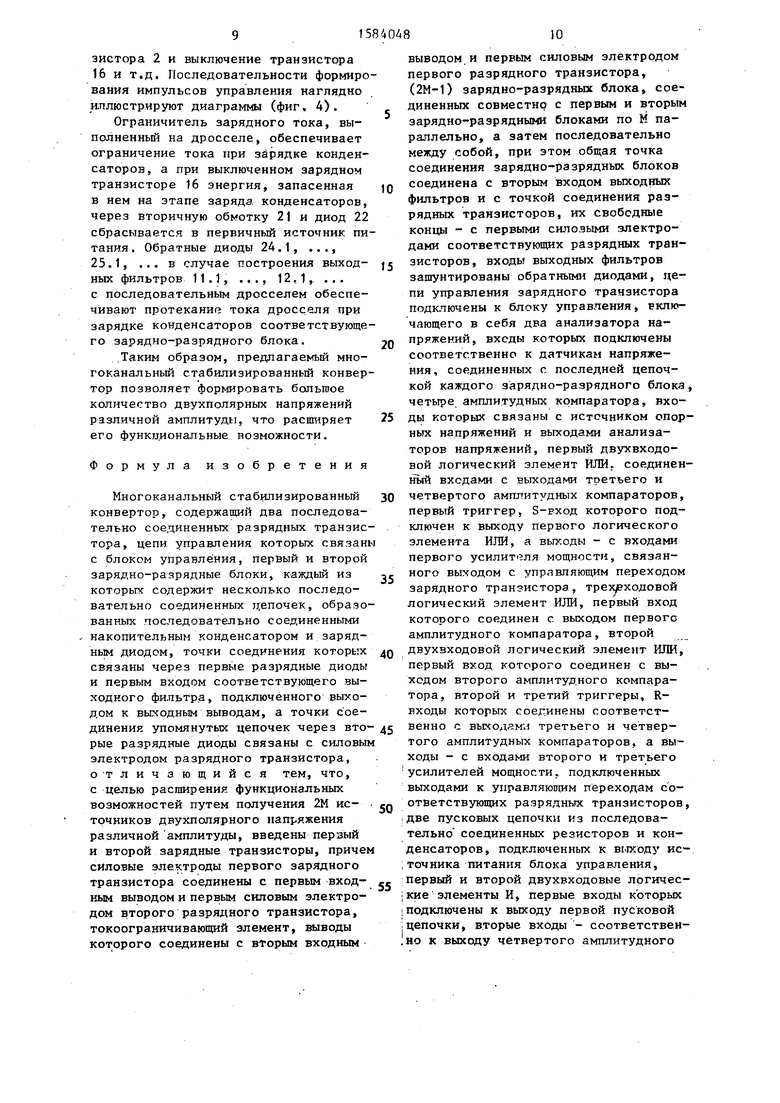

На фиг. 4 представлена переменная составляющая одного из напряжений -U 51 и +U 52, импульсы 53-56 наполнения на выходах соответственно первого 30, второго 31, третьего 32 и четвертого 33 амплитудных ком- паратоуов, импульсы 57-59 напряжения соответственно на прямых выходах триггеров 36, 40, 41 (импульсы напряжения, обеспечивающие включение транзчсторов 16, 1 и 2).

Многоканальный стабилизированный конвертор работает следующим образом.

При подаче питающего напряжения на блок управления (конденсаторы 6.1, ... всех зарядно-вазрядных блоков 4.1, ..., 5.1, ... разряжены) анализаторы 28 и 29 напряжения формируют нз выходах нулевой сигнал. Анализатор 28 напряжения по чаксиму- му обеспечивает подключение к выходу того входного напряжения, амплитуда которого больше всех. При этом к правому выходу анализатора 29 и верхне- му выходу анализатора 28 подключаются напряжения с датчиков 27.1-27.М, а к леному нижнему выходу - с датчиков 26.1-26.М. Анализатор 29 напряжения по минимуму подклютает к -чоему РЫ- ходу наименьшее напряжение. Схемотехническая реализация таких аьаляэато- ров относительно проста и может быть выполнена на основе диодов и операционных усилителей. Источник 34

Р6

опорных напряжений обеспечивает подачу на входы амплитудных компараторов опорных напряжелий. Поэтому при включении на выходе амплитудных компараторов 32 и 33 появляются логические I, что приводит к установке на пряном выходе триггера 36 логической1 1, которая обеспечивает насыщение

транзистора 16. Одновременно логическая 1 с выходов амплитудных компараторов 32 и 33 поступает на входы R триггеров 40 и 41, что приводит к установке на х прямых выходах логичетких О и нахождению транзисторов 1 и 2 в области отсечки. Начинается процесс зарядки всех конденсаторов зарядно-разрядных блоков. Огоаниче- ние зарядного тока осуществляет

ограничитель 18 тока, выполненный, например, на основе дросселя 19, В момент времени t, (фиг. 4) на выходе пусковой цепочки 44 формируется логическая 1 и на вых&че логического

элемента И 48 формируется логическая 1, что приводит к формированию логической 1 па выходе логического ттемента ИЛИ 38, прямом вьтсоде триг- ера 40 и включению транзистора 1.

К :м,нсаторы всех зарядно-раэрядных блЈ ов 4.1-4.М подключаются к выход- нк Фильтрам 11.1-11,М и начинают рзэпяжатыя (фиг. 4, 51). Включение транзистора 1 приводит ч увеличению капг р ения, подаваемого на зарядно- рачрядкые блоки 5.1-5.М. R момент времени t г на выхоце амплитудного компаратора 33 формируется логический Г (напряжение всех конденсаторов зэрядно-раэрядчых блоков 5,1- 5,М не ниже минимального значения), а в момент времени t3 одно из напряжений указанных блоков достигает максимальной величины и на выходе амплитудного компаратора 31 (фиг. 4, 54) формируется логическая 1, что приводит к подаче логической 1 на вход S триггера 41 и включению транзистора 2. В свою очередь, логический

О на инверсном выходе триггера 41 приводит к снятию логической 1 с входа S триггера 40 и формированию на прямом выходе триггера 40 логического О, что приводит к выключению транзистора 1 (на вход R логическая 1 поступает с (выхода амплитудного конпаратора 32, который контролирует минимальное напряжение на конденсаторах всех заоядно-разрядных

блоков 4.1-4.М). Амплитудный компаратор 33 контролирует минимальное напряжение на конденсаторах всех заряд- но-разрядных блоков 5.1-5.М. Амплитудные компараторы 30 и 31 контролируют максимальное напряжение на конденсаторах всех зарядно-разрядных блоков 4.1-4.М и 5.1-5.М. С момента времени tj конденсторы всех зарядно-разряд™ ных блоков подключаются к выходным фильтрам 12.1-12.М, а конденсаторы зарядно-разрядных блоков 4.1-4.М подключаются к входным выводам 23, 17 и начинают заряжаться. В момент вре- мени t напряжения на всех конденсаторах (фиг. 2) зарярно-разрядных блоков 4.1-4.М достигают минимально допустимой величины и на выходе амплитудного компаратора 32 (55) формирует ся логический О, что приводит к снятию логической 1 с входа R триггера 40 (логической 1 не и на входе R триггера 41) . В момедт времени tf одно ич контролируемых напряжений (фиг. 2 и 4) достигает максимально допустимой величины и на выходе амплитудного компаратора 30 (. 4, 53) формируется логическая 1, которая поступает через логический эле- мент ИЛИ 38 на вход S триггера 40, что приводит к формированию на его прямом выходе логической 1, включению транзистора 1, подключению конденсаторов зарядно-разрядных блоков 4.1-4.М к выходным фильтрам 11.1- 11.М и снятию управляющего напряжения с зарядного транзистора 16 (фиг. 4, 57). В момент времени te на конденсаторах одного из заряд- но-разрядных блоков 5.1-5.М напряжение достигает минимально допусти- мой величины II

мин

и поэтому на выходе амплитудного компаратора 33 (фиг. 4, 56) формируется логическая 1, которая поступает на вход R ,триггера 41, обеспечивает установку на его прямом выходе логического О, выключение разрядного транзистора 2 и включение разрядного транзистора 16, так как логическая 1 поступает на вход S триггера 36 (с входа R поступает при этом логический О). Конденсаторы зарядно-разрядных блоков 5.1-5 .М начинают зарякатся от первично- го источника через ограничитель 18 зарядного тока и включенный транзистор 1 . При зарядке конденсаторов зарчдно- рэзрядных нагрузки получают

питание от конденсаторов (Ьильтров 12.1, ... в момент времени t7 напряжение на одном из конденсаторов зарядно-разрядных блоков 5.1-5.М достигает максимально допустимой величины и на выходе амплитудного компаратора 31 (фиг. 4, 54) формируется логическая 1, которая поступает на вход S триггера 41, обеспечивает включение разрядного транзистора 2 и выключение зарядного транзистора 16. В момент времени tj на одном из конденсаторов зарядно-разрядных бло- ков 4.1-4.М напряжение достигает ми- нимально допустимой величины и на выходе амплитудного компаратора 32 формируется логическая 1 (фиг. 4. 55) которая поступает на вход R триггера 42, обеспечивает выключение разрядного транзистора 1, заряд конденсаторов зарядчо-разпядных блоков 4.1- 4.М и подтверждение логической 1 на прямом выходе триггера 41. Однако в момент времени t (конденсаторы зарядно-разрядных блоков 4.1-4.М еще не зарядились до максимально допустимой величины напряжения U„„ , ) на

улике

одном из конденсаторов зарядно-разрядных блоков 5. 1-5.М напряжение достигает минимально допустимой величины, что приводит к формированию на выходе амплитудного компаратора 33 (фиг. 4, 56) логической 1, которая подается на вход R триггера 41, устанавливается логический О на его прямом выходе, выключается разрядный триггер 2 и начиняют разряжаться конденсаторы зарядно-разрядных блоков 5.1,.... Одновременно логическая 1 с инверсного выхода триггера 41 через логические элементы И 48 и ИЛИ 38 поступает на вход S. триггера 40, устанавливает на его прямом выходе логическую 1 и обеспечивает включение разрядного транзистора 1, который обеспечивает заряд конденсаторов зарядно-разрядных блоков 5.1-5.М и подключение конденсаторов зарядно- разрядных блоков 4.1-4.М к выходным фильтрам 11.1-11.М. В момент времени t10 одно из напряжений зарядно-раэ- рядных блоков 5.1-5.М достигает максимально допустимой величины и на выходе амплитудного компаратора 31 (фиг. 4, 54) формируется логическая 1, которая через логический элемен ИЛИ 39 поступает на вход S триггера 41, что обеспечивает включение транэистора 2 и выключение транзистора 16 и т.д. Последовательности формирования импульсов управления наглядно иллюстрируют диаграммы (фиг. 4).

Ограничитель зарядного тока, выполненный на дросселе, обеспечивает ограничение тока при зарядке конденсаторов, а при выключенном зарядном транзисторе 16 энергия, запасенная в нем на этапе заряда конденсаторов, через вторичную обмотку 21 и диод 22 сбрасывается в первичный источник питания . Обратные диоды 24.1, ..., 25.1, ... в случае построения выход- ных фильтров 11.1, ..., 12.1, ... с последовательным дросселем обеспечивают протекание тока дросселя при зарядке конденсаторов соответствующего зарядно-разрядного блока.

Таким образом, предлагаемый многоканальный стабилизированный конвертор позволяет формировать большое количество двухполярных напряжений различной амплитуды, что расширяет его функциональные возможности.

Формула изобретения

Многоканальный стабилизированный конвертор, содержащий два последовательно соединенных разрядных транзистора, цепи управления которых связаны с блоком управления, первый и второй зарядно-разрядные блоки, каждый из которых содержит несколько последовательно соединенных цепочек, образованных последовательно соединенными накопительным конденсатором и зарядным диодом, точки соединения которых связаны через первые разрядные диоды и первым входом соответствующего выходного фильтра, подключенного выходом к выходным выводам, а точки соединения упомянутых цепочек через вто- рые разрядные диоды связаны с силовым электродом разрядного транзистора, отличающийся тем, что, с целью расширения функциональных возможностей путем получения 2М ис- точников двухполярного напряжения различной амплитуды, введены перзый и второй зарядные транзисторы, причем силовые электроды первого зарядного транзистора соединены с первым вход- ным выводом и первым силовым электродом второго разрядного транзистора, токоограничивающий элемент, выводы которого соединены с вторым входным

выводом и первым силовым электродом первого разрядного транзистора, (2М-1) зарядно-разрядных блока, соединенных совместно с первым и вторым зарядно-разрядными блоками по М параллельно, а затем последовательно между собой, при этом общая точка соединения зарядно-разрядных блоков соединена с вторым входом выходных фильтров и с точкой соединения разрядных транзисторов, их свободные концы - с первыми сило дыми электродами соответствующих разрядных транзисторов, входы выходных фильтров зашунтированы обратными диодами, цепи управления зарядного транзистора подключены к блоку управления, включающего в себя два анализатора напряжений, входы которых подключены соответственно к датчикам напряжения, соединенных с последней цепочкой каждого зарядно-разрядного блока, четыре амплитудных компаратора, входы которых связаны с источником опорных напряжений и выходами анализаторов напряжений, первый двухвходо- вой логический элемент ИЛИ. соединенный входами с выходами тпетьего и четвертого амплитудных компараторов, первый триггер, S-РХОД которого подключен к выходу первого логического элемента ИЛИ, а выходы - с входами первого усилителя мощности, связанного выходом с управляющим переходом зарядного транзистора, трехузходовой логический элемент ИЛИ, первый вход которого соединен с выходом первого амплитудного компаратора, второй двухвходовой логический элемент ИЛИ, первый вход которого соединен с выходом второго амплитудного компаратора, второй и третий триггеры, R- входы которых соегинены соответственно с выходямл третьего и четвертого амплитудных компараторов, а выходы - с входами второго и третьего усилителей мощности, подключенных выходами к управляющим переходам соответствующих разрядных транзисторов, ве пусковых цепочки из последовательно соединенных резисторов и коненсаторов, подключенных к выходу источника питания блока управления, ервый и второй двухвходовые логичес- ие элементы И, первые входы которых одключены к выходу первой пусковой епочки, вторые входы - соответствен- о к выходу четвертого амплитудного

компаратора и инверсному выходу третьего триггера, а их выходы - к второму и третьму входу трехвходового логического элемента ИЛИ, третий двухвходовой логический элемент И, входы которого подключены к выходу третьего амплитудного компаратора и выходу второй пусковой цепочки, а выход - к второму входу второго двух- вХодового логического элемента ИЛИ,

Ы

м «ъ

п1

четвертый двухводовой логический элемент И, входп которого соединены с прямыми выходами второго ч третьего триггеров, а выход - с R-входом первого триггера, при этом S-вхоаы второго и третьего триггеро.-1 связаны соответственно с выходами трехвходо-- вого и второго двухв.содовсго логических элементов ИЛИ.

МП

Фиг А

| Стабилизированный преобразователь постоянного разнополярного напряжения | 1984 |

|

SU1203659A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Инвертирующий бестрансформаторный понижающий преобразователь постоянного напряжения | 1980 |

|

SU1086520A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1990-08-07—Публикация

1988-10-17—Подача