Изобретение относится к радиотехнике, а именно к многоканальным цифрвым устройствам обработки информации в полосе частот, и может использоваться для согласованной обработки сигналов в полосе частот, а также в качестве спектроанализатора.

Цель изобретения - повышение быстродействия цифрового согласованного фильтра.

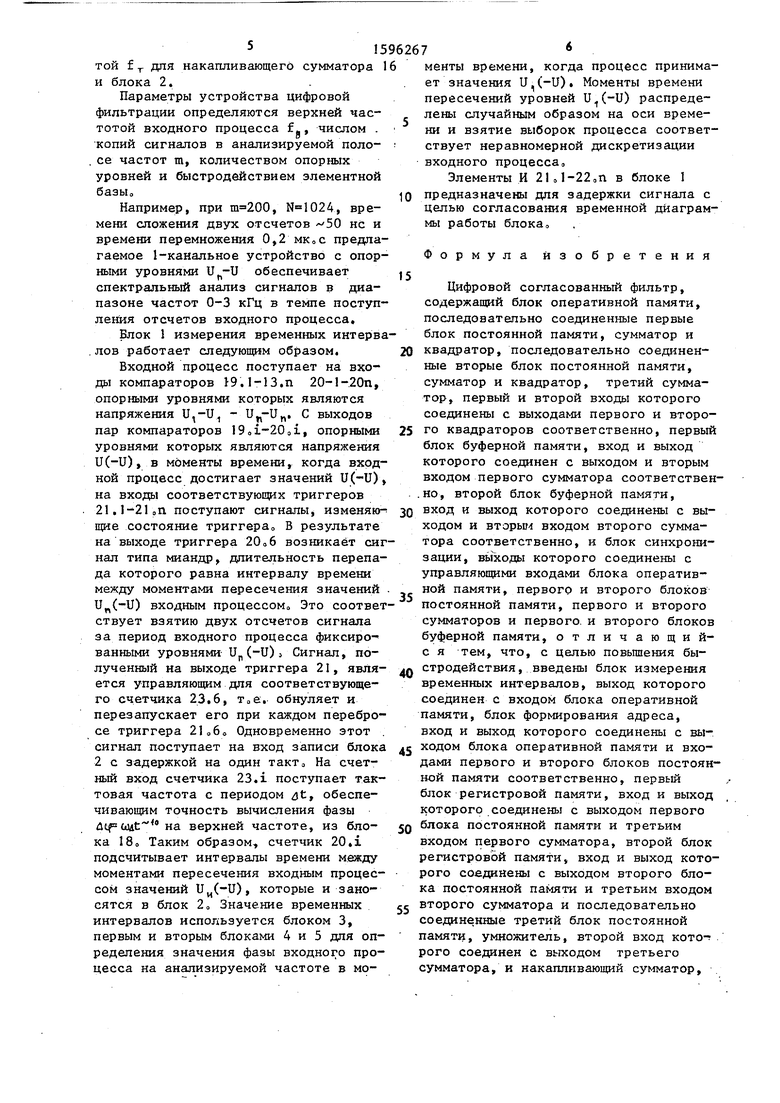

На фиг. 1 приведена электрическая структурная схема цифрового согласованного фильтра; на фиг, 2 - пример выполнения блока измерения временных интервалов

Цифровой согласованный фильтр содержит блок 1 измерения временных

интервалов, блок 2 оперативной памяти, блок 3 формирования адреса, первый и второй блоки 4 и 5 постоянной памяти, первый и второй сумматоры 6

и 7, первый и второй квадраторы 8 и I 9, первый и второй блоки 10 и 1 Г ре-.

гистровой памяти, первый и второй блоки 12 и 13 буферной памяти, третий сумматор 14, умножитель 15, накап ливающий сумматор 16, третий блок I7 постоянной памяти и блок 18 синхронизации о Блок 1 измерения временных интервалов содержит компараторы 19о1-19оП и 20«1-20,п, триггеры ,п, элементы И 22.1-22оП, счетчики 23в1-23оП Предлагаемый цифровой согласованный фильтр реализует скользящее вычис ление свертки входного процесса в тем пе поступления входных отсчетов на т-частотах в заданной полосе анализа по следующей формуле: и,-, {Cco8(cd,.)+Pi(c O-cosCco tf. )+Csin()+q.(aj)-8in(.. )3) 4-. . .+U {fC08(,. ) + +Pj (jO)-cos( )f (. ) + +q. (а)-з1п((л)б€;. )l , где Z , - отсчет спектра мощности в i-й момент на та-й частоUn - значение опорных уровней; значение частоты т-ой копии сигнала; NN Р. I COS u)at . q.- . sinu; flt N - число тактов на интервале време ни, равном длительности анализируемого сигнала; 4tj - временные интервалы входного процесса в i-й момент времени. Отсчет спектра мощности Z. на фиксированной частоте m вычисляется следуюпщм образом, Входной процесс в блоке I преобра зуется в последовательность временных интервалов dt (,.,N), для каждой.пары опорных уровней U (где п - количество опорных уровней), которые записываются в блок 2 и затем поступают в блок 3 формирования адре са, в котором происходит определение значения фазы на т,-ой частоте сигна ла Значение фазы , поступающее с частотой f (где п - количеств частот) на блоки 4 и 5, является адр сом для считывания квадратурных значений копий сигнала coscUrt t;, sino),, t., которые с этой же частотой подступают на вторые входы первого и второго сумматоров 6 и 7 и на входы первого.и второго блоков 10 и П соответственно, где записывается текущее значение квадраторных копий сигнала Формирование значения cosuJ At + +P.J ((ci)-cosc ; dt . осуществляется следующим образом Квадр.атурная копия сигнала costtiy /Jt; поступает на первый вход первого сумматора 6,.на первый блок 10 и, проходя без изменений первый сумматор 6, поступает на первый блок 12о В момент времени N+1 квахфатурная копия сигнала - поступает на первый вход первого сумматора 6 и на первьй блок 10, где сдвигает значение coscJ Jt, На второй вход первого сумматора 6 поступает значение с выхода первого блока 12, результат суммирования поступает в первый блок 12, затирая значение .. Так в течение первых тактов подсчитывается значенкие Р- (W,) 2 со8и)„ 4t., Затем на jet f, -т N+1 такте на первый вход первого сумматора 6 поступает значение СО8(0„ ijt. , на первый вход значение Р. ((л),) с выхода первого блока 12, а на третий вход - проинвертиррванное значение cosuj,,at N, , Формирование значения 8inc«/ dt, +q, (tJ,)-sinu)flt , осуществляется аналогично на вторых сумматоре 7,блоке 11 и блоке 13о Вычислен1-1ые значения поступают на первый и второй квадраторы 8 и 9, выходные коды которьпс суммируются на третьем сумматоре 14 и поступают на умножитель 15, На первый вход змножителя 15 с третьего блока 17 поступает последовательность значений квадратов опорных уровней U. Результат вычислений последовательно суммируется в накапливающем сумматоре Вычисление откликов на остальных частотах производится аналогичным способом на интервала между двумя соседними выборками сигнала Для синхрош1зации работы устройства цифровой фильтрации блок 18 выдает синхроимпульс с частотой следования f, определяемой верхней частотой входного процесса f g для блока 1 измерения временных интервалов, с частотой f-r.n для третьего блрка 17, с частотой f п. блока 3 формирования адреса первого и второго блоков 10 и 11j первого и второго блоков 12 и 13, с частотой 2 для первого и второго сумматоров 6 и 7 и с частотой f т- для накапливающего сумматора и блока 2. Параметры устройства цифровой фильтрации определяются верхней частотой входного процесса f,, числом . копий сигналов в анализируемой полосе частот т, количеством опорных уровней и быстродействием элементной баэЫо Например, при , , времени сложения двух отсчетов -50 не и времени перемножения 0,2 предлагаемое 1-канальное устройство с опорными уровнями обеспечивает спектральный анализ сигналов в диапазоне частот 0-3 кГц в темпе поступления отсчетов входного процесса. Блок 1 измерения временных интерва .лов работает следующим образом. Входной процесс поступает на входы компараторов }9.}-13,п 20-1-.20п, опорными уровнями которых являются напряжения U,-U, - , С выходов пар компараторов 19oi-20oi, опорными уровнями которых являются напряжения и(-и), в моменты времени, когда входной процесс достигает значений U(-U) на входы соответствующих триггеров 21.1-21 оП поступают сигналы, изменяющие состояние триггера В результате на выходе триггера 20о6 возникает сиг нал типа миандр, длительность перепада которого равна интервалу времени между моментами пересечения значений и(-и) входным процессом Это соответ ствует взятию двух отсчетов сигнала за период входного процесса фиксиро- ванными уровнями Up(-U)з Сигнал, полученный на выходе триггера 21, является управляющим для соответствующего счетчика 23.6, Тов. обнуляет и перезапускает его при каждом перебросе триггера 2U6o Одновременно этот сигнал поступает на вход записи блока 2 с задержкой на один такт На счетный вход счетчика 23.1 поступает тактовая частота с периодом t, обеспечивающим точность вычисления фазы utpojif на верхней частоте, из блока 18 Таким образом, счетчик 20,1 подсчитывает интервалы времени м.ежду моментами пересечения входным процессом значений U,(-U), которые и заносятся в блок 2 о Значение временных интервалов используется блоком 3, первым и вторым блоками 4 и 5 для определения значения фазы входного процесса на анализируемой частоте в мовход и выход которого соединены с выной памяти соответственно, первый блок регистровой памяти, вход и выход которого соединены с выходом первого

блока постоянной памяти и третьим

входом первого сумматора, второй блок регистровой памяти, вход и выход которого соединены с выходом второго блока постоянной памяти и третьим входом

второго сумматора и последовательно соединенные третий блок постоянной памяти, умножитель, второй вход которого соединен с выходом третьего сумматора, и накапливающий сумматор. менты времени, когда процесс принимает значения U, (-U) Моменты времени пересечений уровней U(-U) распределены случайным образом на оси времени и взятие выборок процесса соответствует неравномерной дискретизации входного процессао Элементы И 21о1-22оП в блоке 1 предназначены для задержки сигнала с целью согласования временной диаграммы работы блока. Формула изобретения Цифровой согласованньШ фильтр, содержащий блок оперативной памяти, последовательно соединенные первые блок постоянной памяти, сумматор и квадратор, последовательно соединенные вторые блок постоянной памяти, сумматор и квадратор, третий сумматор, первый и второй входы которого соединены с выходами первого и второго квадраторов соответственно, первый блок буферной памяти, вход и выход которого соединен с выходом и вторым входом первого сумматора соответственно, второй блок буферной памяти. ОД выход которого соединены с выходом и вторым входом второго сумматора соответственно, и блок синхронизации, выходы которого соединены с управляющими входами блока оперативной памяти, первого и второго блоков постоянной памяти, первого и второго сумматоров и первого, и второго блоков буферной памяти, отличающийс я тем, что, с целью повьшения бы Р Я ствия, введены блок измерения временных интервалов, выход которого соединен с входом блока оперативной памяти, блок формирования адреса. 45 °Дом блока оперативной памяти и входами первого и второго блоков постоянпричем управляющие входы блока изменения временных интервалов, блока формирования адреса, первого и второго блоков регистровой памяти, третьего блока постоянной памяти и накапливающего сумматора подключены к соответствующим выходам блока синхронизации,

| название | год | авторы | номер документа |

|---|---|---|---|

| Фурье-коррелятор | 1983 |

|

SU1164731A1 |

| Устройство для быстродействующей токовой защиты электроустановки переменного тока | 1983 |

|

SU1111220A1 |

| Цифровой панорамный измеритель частоты | 1986 |

|

SU1413547A1 |

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

| Цифровой анализатор сигнала | 1988 |

|

SU1619297A1 |

| СПОСОБ ОБНАРУЖЕНИЯ ШИРОКОПОЛОСНОГО СИГНАЛА С НЕИЗВЕСТНОЙ ЧАСТОТОЙ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 1998 |

|

RU2141730C1 |

| Цифровой панорамный измеритель частоты | 1977 |

|

SU737857A1 |

| Анализатор сигнала тактовой синхронизации | 1988 |

|

SU1587656A1 |

| Устройство для вычисления дискретного спектра действительного временного ряда | 1974 |

|

SU525960A1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2003 |

|

RU2255421C2 |

Изобретение относится к многоканальным цифровым устройствам обработки информации в полосе частот и может использоваться для согласованной обработки сигналов, а также в качестве спектроанализатора. Цель изобретения - повышение быстродействия. Поставленная цель достигается за счет того, что в цифровой согласованный фильтр, содержащий блок 2 оперативной памяти, первый и второй блоки 4, 5 постоянной памяти, первый, второй и третий сумматоры 6, 7 и 14, первый и второй блоки 12 и 13 буферной памяти, первый и второй квадраторы 8 и 9 и блок 18 синхронизации, введены блок 1 измерения временных интервалов, блок 3 формирования адреса, первый и второй блоки 10 и 11 регистровой памяти, третий блок 17 постоянной памяти, умножитель 15 и накапливающий сумматор 16. Предлагаемый цифровой согласованный фильтр позволяет реализовать нерегулярную дискретизацию сигналов и рекурентное вычисление суммы отсчетов копии сигнала, что позволяет при скользящем вычислении свертки входного процесса в темпе поступления входных отсчетов на M частотах в заданной полосе анализа резко сократить число операций умножения и сложения и повысить быстродействие устройства. 2 ил.

Фиг.1

224

fif8.2

| Авторское свидетельство СССР № 1289212, кл, G 01 R 23/16, 1984 |

Авторы

Даты

1990-09-30—Публикация

1988-02-10—Подача