(21)4403772/24

(22)05.04.88

(46) 07.01.91. Бнш. Я 1

(72) М.В.Куприянова, В.А.Смирнова

и С.И.Хазанович

(53)681.32(088.8)

(56) Авторское свидетельство СССР 1107134, кп. G 06 F 15/332, 1982. лренкс Л. Теория сигналов. - М., 1974, с.63, рис.36.

(54)ЦИФРОВОЙ АНАЛИЗАТОР СИГНАЛА (57) Изобретение относится к средствам вычислительной техники и может

найти применение в системах обработки информации различного назначения. Целью изобретения является повышение точности анализа сигналов. Сущность изобретения состоит в том, что устройство содержит с первого по четвертый блоки 3, 7, 14, 11 памяти, четыре блока 2,6, 15, 10 микропрограммного управления, делитель 12, четыре сумматора 5, 9, 13, 17 и два умножителя 4, 8, блок 19 извлечения квадратного корня, схему 19 сравнения, квадратор 16 и синхронизатор 20.3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор сигнала | 1990 |

|

SU1836689A3 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Цифровой измеритель показателей качества электрической энергии трехфазной сети | 1988 |

|

SU1633368A1 |

| Устройство для вычисления коэффициентов нерекурсивных полосовых фильтров | 1988 |

|

SU1647587A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ГАРМОНИКИ НАПРЯЖЕНИЯ | 1990 |

|

RU2030753C1 |

| Анализатор обобщенного энергетического спектра | 1983 |

|

SU1257543A1 |

| Устройство для обработки изображений | 1990 |

|

SU1751784A2 |

| Адаптивный цифровой фильтр | 1987 |

|

SU1494212A1 |

(Я

СЭ

я я к

Шиг.1

( - ЈK(t) К-1

i

:KiCf;(t),

К

«i

ft

fK(tp)(tp)

- fn(t) П-А

1

П1

(t)

N

С

П

(t,)(tp)

(3)

31619297

Изобретение относится к вычислительной технике и средствам обработки сигналов и может найти применение в цифровых системах обработки информации различного назначения.

Цель изобретения - повышение точности.

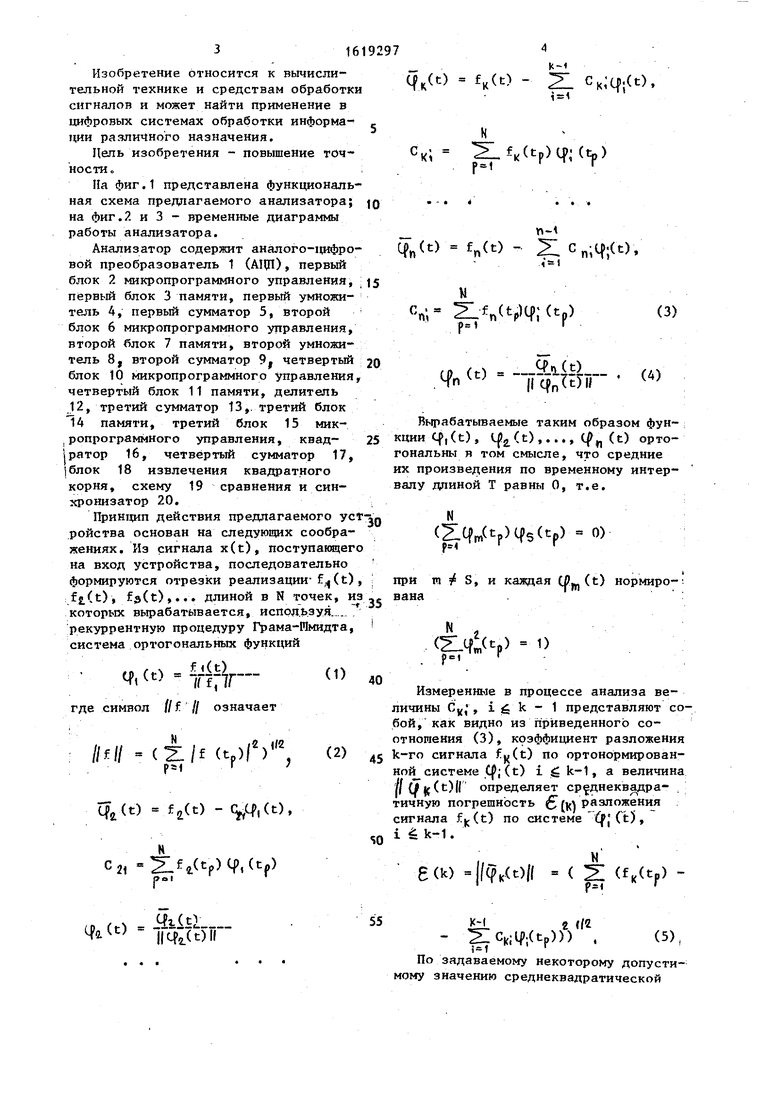

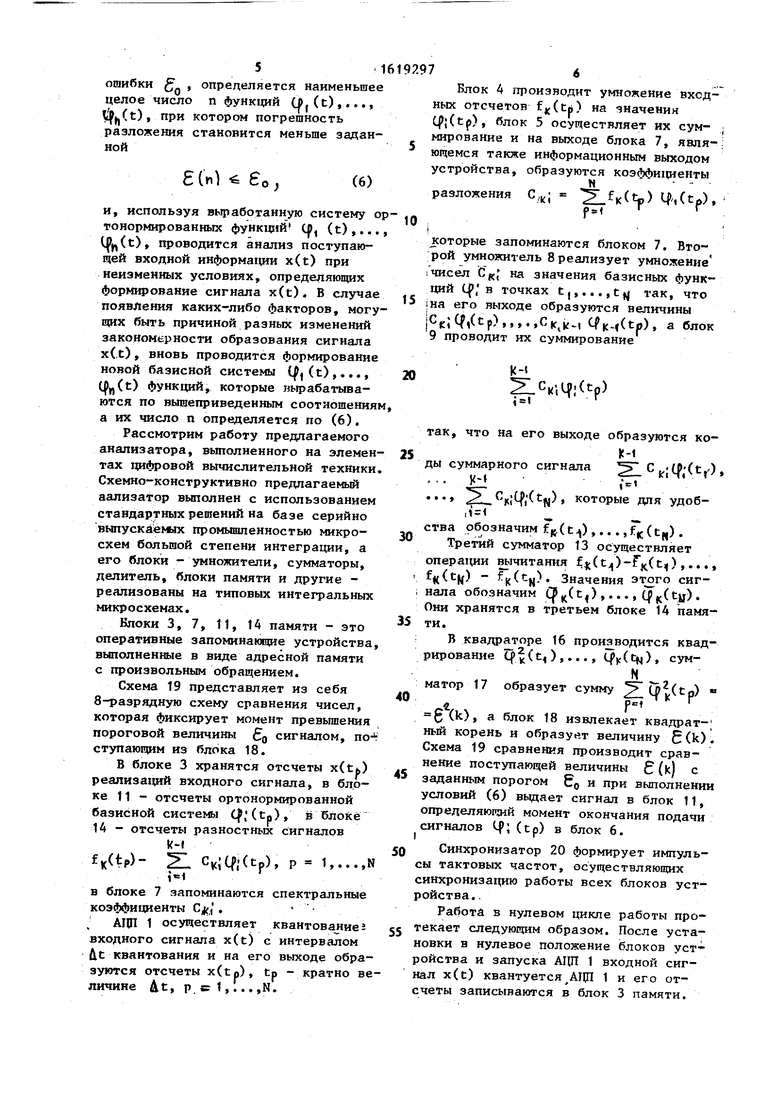

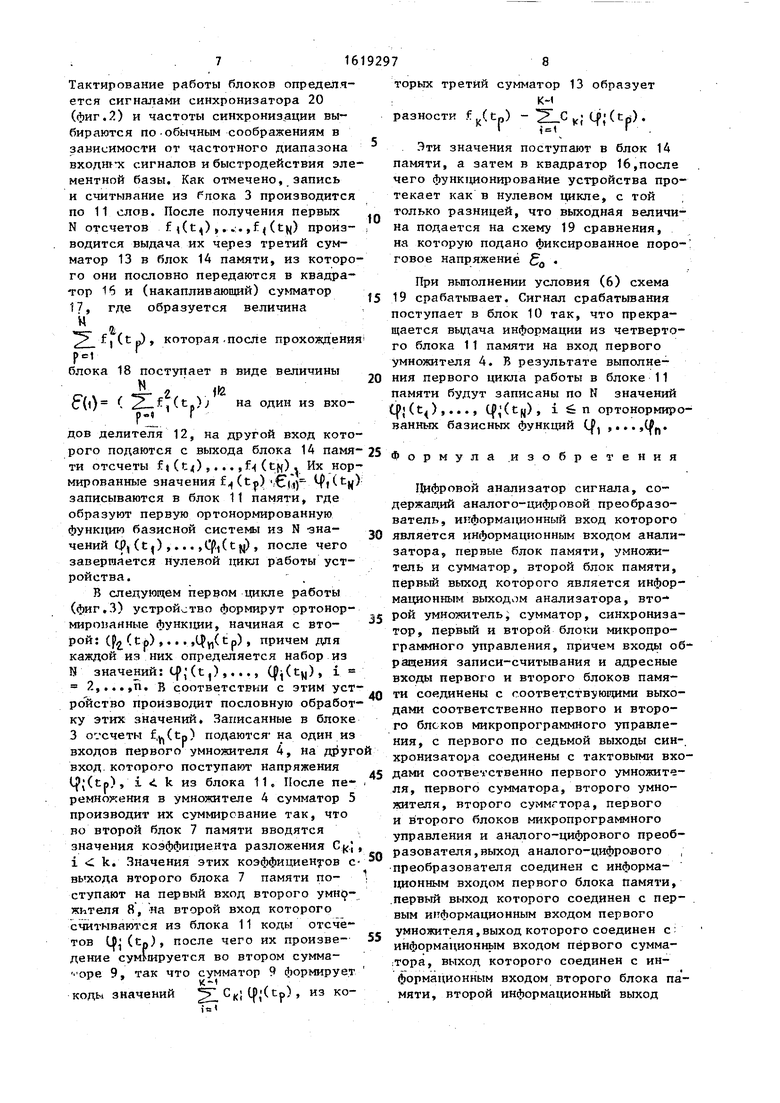

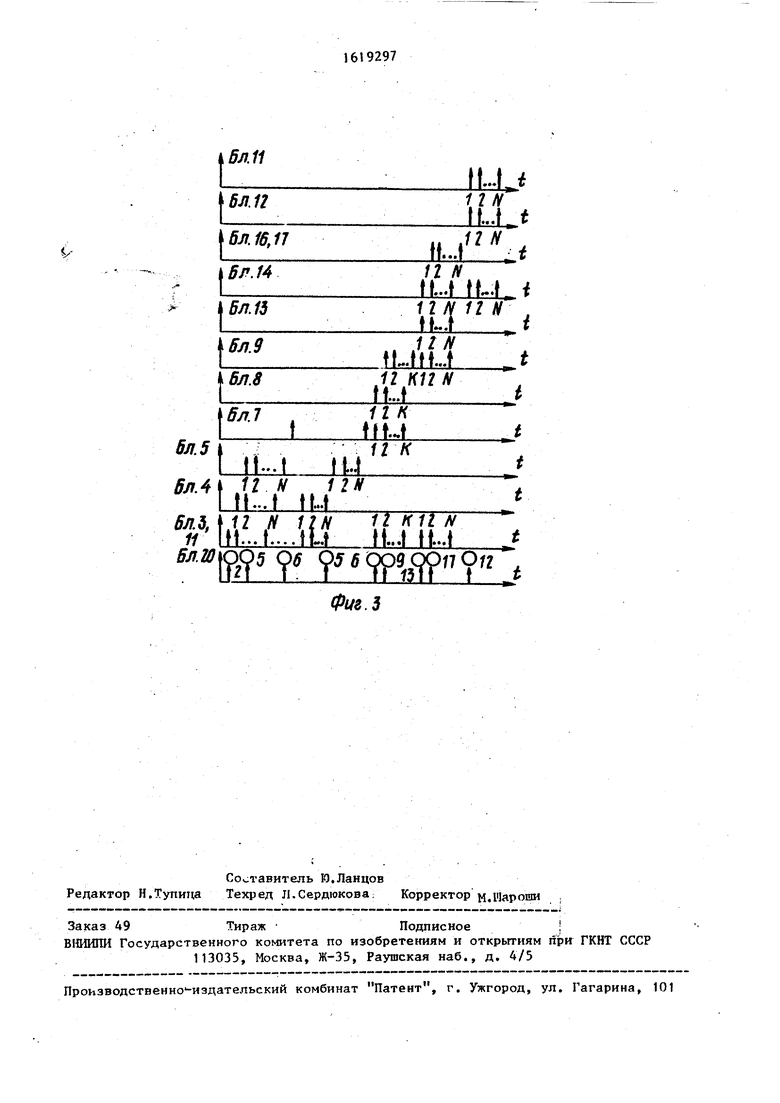

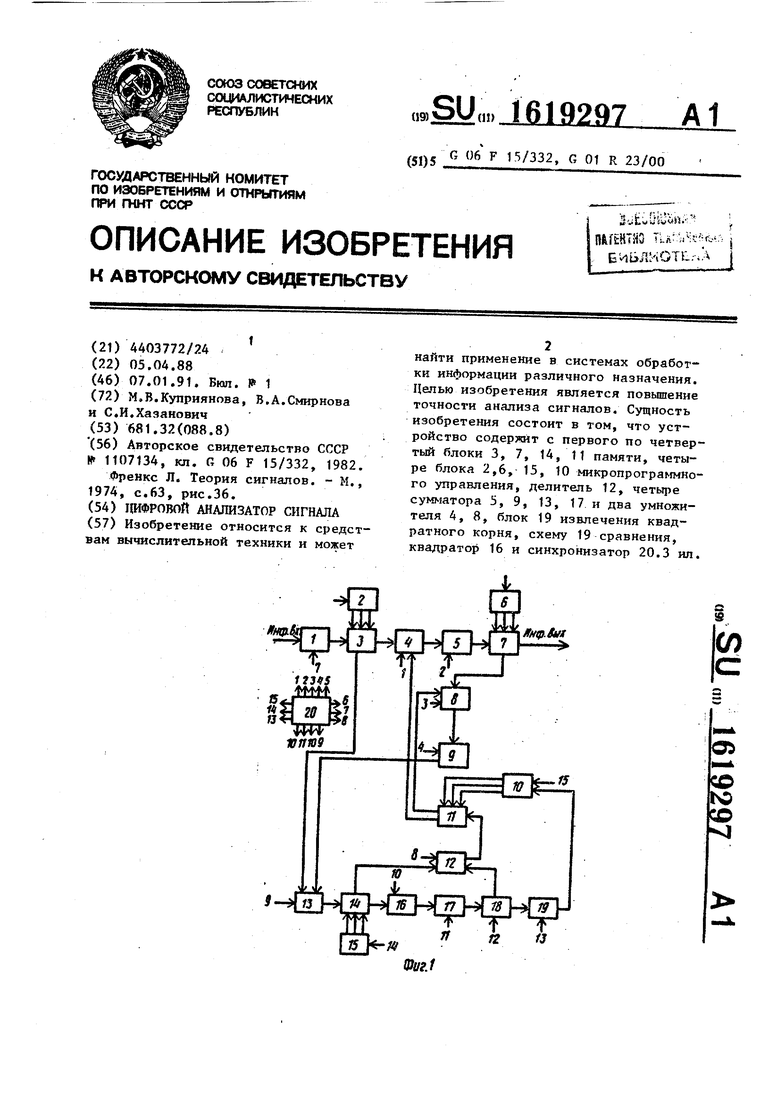

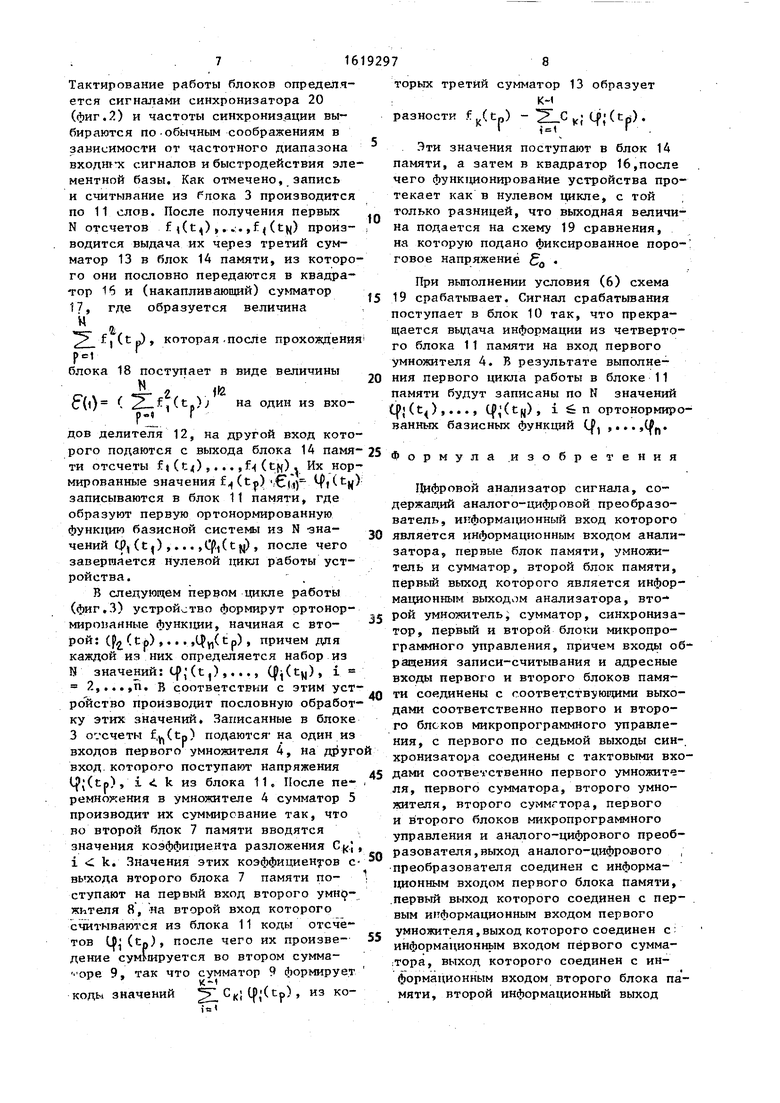

На фиг.1 представлена функциональная схема предлагаемого анализатора; Q на фиг.2 и 3 - временные диаграммы работы анализатора.

Анализатор содержит аналого-цифровой преобразователь 1 (АЦП), первый блок 2 микропрограммного управления, 15 первый блок 3 памяти, первый умножитель 4, первый сумматор 5, второй блок 6 микропрограммного управления, второй блок 7 памяти второй умножитель 8, второй сумматор 9f четвертый 20 блок 10 микропрограммного управления, четвертый блок 11 памяти, делитель 12, третий сумматор 13, третий блок 14 памяти, третий блок 15 микропрограммного управления, квад- |ратор 16, четвертый сумматор 17, (блок 18 извлечения квадратного корня, схему 19 сравнения и синхронизатор 20.

Принцип действия предлагаемого ройства основан на следующих соображениях. Из сигнала x(t), поступающего на вход устройства, последовательно

формируются отрезки реализации-f,(t) , при tn S, и каждая (0 (t) нормиро- fЈ.(t) fs(t),... длиной в N точек, из., вана которых вырабатывается, используя. . рекуррентную процедуру Грама-Шмидта, система ортогональных функций

г. (t) . -SЈa. n|iq nlt)u

(4)

Вырабатываемые таким образом фун- 25 кцииСр,(с), (t),..., (fn (t) ортогональны в том смысле, что средние их произведения по временному интервалу длиной Т равны 0, т.е.

N )tb(tp) °

fst

N

- 1)

w -rfir(1)

где символ

llf И

означает

2,1/2

И tit - (21/f (tp)/ ) ,(2)

tpt(t) - f2(t) - (Cf,(t),

С2 5.)(tf

(t)

.

|| cpt( t) I

( - ЈK(t) К-1

i

:KiCf;(t),

К

«i

ft

fK(tp)(tp)

- fn(t) П-А

1

П1

(t)

N

(t,)(tp)

(3)

г. (t) . -SЈa. n|iq nlt)u

(4)

Вырабатываемые таким образом фун- кцииСр,(с), (t),..., (fn (t) ортогональны в том смысле, что средние их произведения по временному интервалу длиной Т равны 0, т.е.

N )tb(tp) °

fst

N

n S, и каждая

- 1)

р«н

F

Измеренные в процессе анализа величины Cv;, i k 1 представляют собой, как видно из приведенного соотношения (3), коэффициент разложения k-ro сигнала fj((t) по ортонормирован- ной системе С|); (t) i k-1, а величина (t)|| определяет ср днеква цра- тичную погрешность м разложения сигнала j;(t) по системе (р| (t), i k-1.

-|/(рк(0/|

(

N

(fK(tf)

K-l

(5)

- ..-2 f/2

- .(tp))) ,

По задаваемому некоторому допустимому значению среднеквадратической

51619297

ошибки f , определяется наименьшее целое число п функций П.(с),..., 0h(t), при котором погрешность разложения становится меньше заданной

еы « е

°)

и, используя выработанную систему о

тонормированных функций Ср, (t)

l$,(t), проводится анализ поступающей входной информации x(t) при неизменных условиях, определяющих формирование сигнала x(t). В случае появления каких-либо факторов, могущих быть причиной разных изменений закономерности образования сигнала x(t), вновь проводится формирование новой базисной системы ( (t) ,..., n(t) функций, которые нырабатыва- ются по вышеприведенным соотношения а их число п определяется по (6).

Рассмотрим работу предлагаемого анализатора, выполненного на элементах цифровой вычислительной техники Схемно-конструктивно предлагаемый аалязатор выполнен с использованием стандартных решений на базе серийно выпускаемых промышленностью микросхем большой степени интеграции, а его блоки - умножители, сумматоры, делитель, блоки памяти и другие - реализованы на типовых интегральных микросхемах.

Блоки 3, 7, 11, 14 памяти - это оперативные запоминающие устройства выполненные в виде адресной памяти с произвольным обращением.

Схема 19 представляет из себя 8-разрядную схему сравнения чисел, которая фиксирует момент превышения пороговой величины Ј0 сигналом, поступающим из блока 18.

В блоке 3 хранятся отсчеты x(tk) реализаций входного сигнала, в блоке 1 1 - отсчеты ортонормированной базисной системы Cf. Ctp) в блоке 14 - отсчеты разностных сигналов

k-l fK(tl)- Zl ), p- 1,...,N

i«1

в блоке 7 запоминаются спектральные коэффициенты С,.

АДП 1 осуществляет квантование се текает следующим образом. После уставходного сигнала x(t) с интервалом ut квантования и на его выходе образуются отсчеты x(tp), tp - кратно ве личине At, pc1,...,N.

новки в нулевое положение блоков устройства и запуска А1Щ 1 входной сигнал x(t) квантуется АЩ 1 и его отсчеты записываются в блок 3 памяти.

Блок 4 производит умножение входных отсчетов fj((tp) на значения tft(tp), блок 5 осуществляет их сум- ( мирование и на выходе блока 7, являющемся также информационным выходом устройства, образуются коэффициенты

N разложения C,KJ

- ,

Z-Mtp if,(t,.

г

Которые запоминаются блоком 7. Второй умножитель 8 реализует умножение Гчисел Ск, на значения базисных функций Ц, в точках t,ttf так, что

|на его выходе образуются величины

}ск;( cfK-«(tp)t а блок 9 проводит их суммирование

20

K-t

(tp)

0

так, что на его выходе образуются ко5 м

ды суммарного сигнала Г С ,,(P(t.),

KJ,i

..., P CyiCftCtfl), которые для удоб) ства обозначим f ( t ) ,..., fк (tN) .

Третий сумматор 13 осуществляет операции вычитания Ј(с)-Г(с),...,

f«(ck) Значения этого сигнала обозначим СР j((t|) ,..., tp j((tjj) . Они хранятся в третьем блоке 14 памяти.

В квадраторе 16 производится квад- рирование ),..., ) сумN

матор 17 образует сумму

t

5

0

«P

6(10 а блок 18 извлекает квадратный корень и образует величину Ј(k). Схема 19 сравнения производит сравнение поступающей величины Ј (k) с 5 заданным порогом Ј0 и при выполнении условий (6) выдает сигнал в блок 11, определяющий момент окончания подачи сигналов (tp) в блок 6.

0 Синхронизатор 20 формирует импульсы тактовых частот, осуществляющих синхронизацию работы всех блоков устройства.

Работа в нулевом цикле работы проновки в нулевое положение блоков устройства и запуска А1Щ 1 входной сигнал x(t) квантуется АЩ 1 и его отсчеты записываются в блок 3 памяти.

Тактирование работы блоков определяется сигналами синхронизатора 20 (фиг,2) и частоты синхронизации выбираются по обычным соображениям в зависимости от частотного диапазона входт х сигналов и быстродействия элементной базы. Как отмечено, запись и считывание из блока 3 производится по 11 слов. После получения первых N отсчетов f(t),...,f(t) производится выдача их через третий сумматор 13 в блок 14 памяти, из которого они пословно передаются в квадратор 1 и (накапливающий) сумматор 17, где образуется величина Н .

f,(tp), которая-после прохождения

pel

блока 18 поступает в виде величины

N

Л, &

Ј() ( (О- на °ДИН из вхо- р««

дов делителя 12, на другой вход которого подаются с выхода блока 14 памя- ти отсчеты ft(t{),...,f4(tty). Их нормированные значения f (t«) Cii) записываются в блок 11 памяти, где образуют первую ортонормированную функцию базисной системы из N -зна- чений Ср, (t|) ,... {(tty), после чего завершается нулевой цикл работы устройства.

В следующем первом цикле работы (фиг.З) устройство формирут ортонор- миро)аянне функции, начиная с вто- рой: (p(tp) ,... ,tfM(tp), причем для каждой из них определяется набор из Я значений: cp;(t,),..., ((), i .,...,п. в соответствии с этим устройство производит пословную обработку этих значений. Записанные в блоке 3 обсчеты f,(tp) подаются- на один из входов первого умножителя 4, на друго вход которого поступают напряжения lf((tp), i «i. k из блока 11. После пе- ремнохения в умножителе 4 сумматор 5 производит их суммирование так, что во второй блок 7 памяти вводятся значения коэффициента разложения С«;, i «i k. Значения этих коэффициентов с- выхода второго блока 7 памяти поступают на первый вход второго умнф- жителя 8, на второй вход которого считываются из блока 11 коды отсчётов ф (tp), после чего их произве- дение суммируется во втором сумма оре 9. так что сумматор 9 формирует

к- коды значений Г CKj (fjttp- из ко

0

5

0

5 Q

5

0

5

торых третий сумматор 13 образует

К-1

разности fK(tp) - Cp,(tp). i 1 Г

Эти значения поступают в блок 14 памяти, а затем в квадратор 16,после чего функционирование устройства протекает как в нулевом цикле, с той только разницей, что выходная величина подается на схему 19 сравнения, на которую подано фиксированное пороговое напряжение Ј .

При выполнении условия (6) схема 19 срабатывает. Сигнал срабатывания поступает в блок 10 так, что прекращается выдача информации из четвертого блока 11 памяти на вход первого умножителя 4. В результате выполнения первого цикла работы в блоке 11 памяти будут записаны по N значений tPj(t|),..., ((tfj), i n ортонормиро- ванных базисных функций t ,...,(JL.

Формула изобретения

цифровой анализатор сигнала, содержащий аналого-цифровой преобразователь, информационный вход которого является информационным входом анализатора, первые блок памяти, умножитель и сумматор, второй блок памяти, первый выход которого является информационным выходом анализатора, вто- рой умножитель, сумматор, синхронизатор, первый и второй блоки микропрограммного управления, причем входы обращения записи-считывания и адресные входы первого и второго блоков памяти соединены с соответствующими выходами соответственно первого и второго блсков микропрограммного управления, с первого по седьмой выходы синхронизатора соединены с тактовыми входами соотвеч ственно первого умножителя, первого сумматора, второго умножителя, второго суммгтора, первого и второго блоков микропрограммного управления и аналого-цифрового преобразователя, выход аналого-цифрового , преобразователя соединен с информационным входом первого блока памяти, первый выход которого соединен с первым информационным входом первого умножителя, выход которого соединен с информационным входом первого сумматора, выход которого соединен с информационным входом второго блока памяти, второй информационный выход

второго блока памяти соединен с первым информационным входом второго умножителя, выход которого соединен с информационным входом второго сумма- тора, отличающийся тем, что, с целью повышения точности, в анализатор введены третьи и четвертые блоки памяти,блоки микропрограммного управления, сумматоры, делитель и квадратор, блок извлечения квадратного корня и пороговый элемент, причем входы обращения записи-считывания и адресные входы третьего и четвертого блоков памяти соединены с соответствующими выходами соответственно третьего и четвертого блоков мик- ропроцессорногд,,управления, выход второго сумматора и второй выход первого блока памяти подключены соответственно к первому и второму входам третьего сумматора, первый выход третьего блока памяти соединен с первым информационным входом делителя, второй информационный вход которого соединен с первым выходом блока извлечения квадратного корня, выход делителя соединен с информационным входом

четвертого блока памяти, первый и второй выходы которого соединены с вторыми информационными входами соответ- ственно первого и второго умножителей, выход третьего сумматора соединен с информационным входом третьего блока памяти, второй выход которого соединен с информационным входом квадратора,выход которого соединен с информационным входом третьего сумматора, выход которого соединен с информационным входом блока извлечения квадратного корня, выход которого соединен с информационным входом порогового элемента, выход которого соединен с входом логических условий третьего блока микропрограммного управления, с восьмого по пятнадцатый выходы синхронизатора соединены с тактовыми входами соответственно делителя, третьего сумматора, квадратора, четвертого сумматора, блока извлечения квадратного корня, порого- 5 вого элемента и третьего и четвертого блоков микропрограммного управления.

5

0

Фиг.З

Авторы

Даты

1991-01-07—Публикация

1988-04-05—Подача