Изобретение относится к области электросвязи, преимущественно к дуплексной передаче сигналов связи.

Известно устройство для разделения сигналов двух направлений /1/, состоящее из передающего устройства, адаптивного фильтра, приемного устройства и вычитателя. Принцип действия таких устройств основан на искусственном вырабатывании сигналов эха в адаптивном фильтре и впоследствии компенсации эхо-сигналов в вычитателе.

Недостатком подобных устройств является низкая помехоустойчивость принимаемых сообщений, большой уровень некомпенсированного эхо-сигнала, большая критичность к корреляционным связям сигналов передачи и приема, даже при частичной коррелированности сигналов двух направлений устройство начинает компенсировать принимаемый сигнал, делая дуплексный обмен сигналов невозможным.

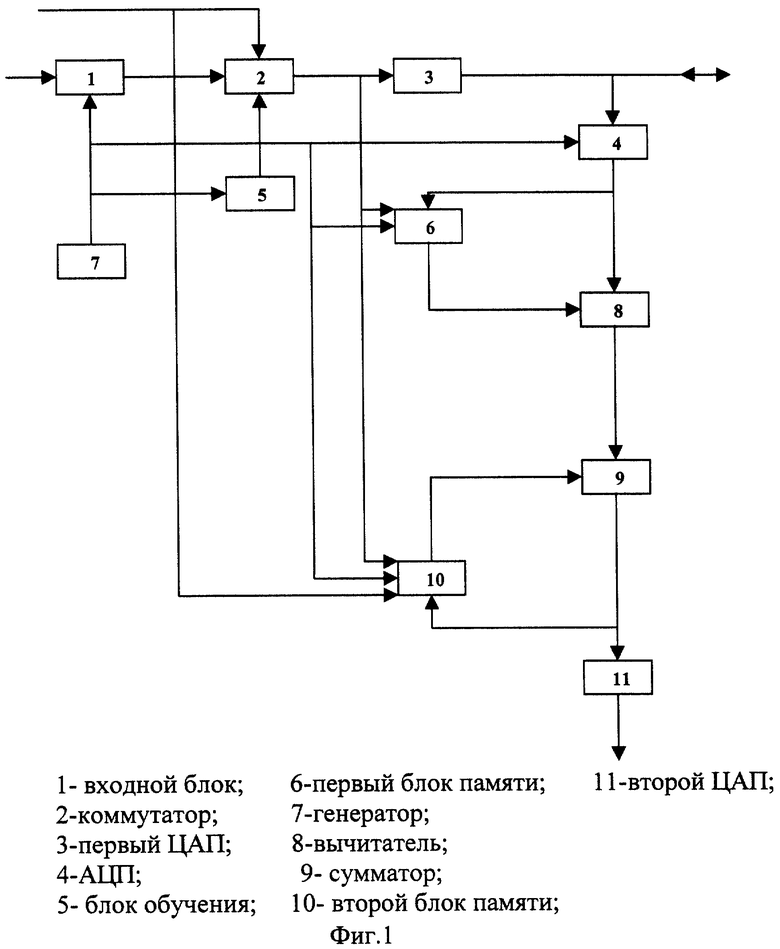

Этот недостаток устранен в прототипе /2/, содержащем последовательно соединенные (Фиг.1) входной 1 блок, коммутатор 2, первый 3 ЦАП, аналого-цифровой преобразователь 4, первый 6 блок памяти, вычитатель 8, вторым входом соединенный с выходом АЦП 4, сумматор 9, второй 10 блок памяти, выход которого соединен со вторым входом сумматора 9 и вторым 11 ЦАП, а также последовательно соединенные генератор 7 и формирователь, 5 обучающих сигналов, выходом соединенный со вторым входом коммутатора 2, управляющий вход которого объединен со входом обнуления второго 10 блока памяти, при этом выход генератора 7 соединен со вторыми входами соответственно входного 1 блока, АЦП 4, первого 6 и второго 10 блоков памяти, а выход коммутатора соединен с третьими входами первого 6 и второго 10 блоков памяти.

Работа прототипа состоит из двух частей: предварительного обучения и дуплексного обмена сигналами.

При предварительном обучении устройства под параметры канала связи блок обучения 5 выдает в цифровой форме все используемые цифровые комбинации, отклики от которых записываются в первом блоке памяти. На период адаптации второй 10 блок памяти обнуляется. При обучении принимаемые сигналы с домина отсутствуют.

По окончании предварительного обучения начинается дуплексный обмен сигналами. Включаются оба блока памяти. Используемая структура нерекурсивной и рекурсивной частей компенсатора зеркально симметричны. В нерекурсивной части производится компенсация сигналов передачи и модуляция сигналов приема. Рекурсивная часть компенсатора полностью восстанавливает форму принимаемых сигналов.

Однако прототип может работать только на каналах с постоянными параметрами. При переходе параметров каналов связи из одного состояния в другое во втором 10 блоке памяти накапливается сигнал недокомпенсации, который дополнительно не компенсируется. Это явление может привести к срыву дуплексного обмена и потребует нового переобучения. Если параметры канала связи изменяются с большей скоростью, то в таких условиях работа прототипа будет невозможной. При этом помехоустойчивость принимаемых сообщений будет низкой.

Целью настоящего изобретения является повышение помехоустойчивости принимаемых сообщений.

Поставленная цель достигается тем, что в устройство для разделения сигнала передачи и приема в дуплексных системах связи, содержащее последовательно соединенные генератор, входной блок, второй вход которого является входом сигналов передачи, коммутатор, первый цифроаналоговый преобразователь, выходом соединенный с двухпроводным каналом связи, аналого-цифровой преобразователь, первый блок памяти, вычитатель, первый сумматор, второй блок памяти, а также блок обучения и второй цифроаналоговый преобразователь, при этом выход генератора соединен со вторыми входами соответственно входного блока, аналого-цифрового преобразователя, первого и второго блоков памяти, а также со входом блока обучения выход которого соединен со вторым входом коммутатора, третий вход которого является управляющим и соединен с третьими входами первого и второго блоков памяти, выход коммутатора соединен с четвертыми входами первого и второго блоков памяти, а выход первого сумматора соединен со вторым входом цифроаналогового преобразователя, выход которого является выходом устройства, а выход аналого-цифрового преобразователя соединен со вторым входом вычитателя, введены последовательно соединенные второй сумматор, второе реестровое запоминающее устройство, делитель, второй вычитатель и умножитель, а также одновибратор и первое реестровое запоминающее устройство, выход которого соединен со вторым входом второго сумматора, первый вход которого объединен со входом второго цифроаналогового преобразователя, при этом выход одновибратора соединен со вторыми входами первого и второго реестровых запоминающих устройств, выход второго сумматора соединен с первым входом первого реестрового запоминающего устройства, третий вход которого соединен со вторым входом одновибратора и объединен с выходом генератора, на второй вход делителя подключено максимально возможное значение управляющего сигнала, а на второй вход второго вычитателя подключено максимально возможное значение коэффициента передачи, при этом вход второго блока памяти соединен со вторым входом умножителя, выход которого соединен со вторым входом первого сумматора.

Докажем соответствие предлагаемого решения критерию "существенные отличия".

1. Отличительным конструктивным признаком предлагаемого решения является введение сумматора, двух регистровых запоминающих устройств, делителя, вычитателя, умножителя и одновибратора. При этом вновь введенные блоки представляют собой единую совокупность конструктивных признаков, так как элементы предложенной конструкции взаимосвязаны, соединены в единую систему, действие одного из них непосредственно влияет на другие, замена какого-либо блока на другие нарушает работу всего устройства в целом. Такая новая совокупность конструктивных признаков обеспечивает положительный эффект (повышение помехоустойчивости принимаемых сообщений), который соответствует всему устройству, а не отдельным ее элементом.

2. Заявителем просмотрена техническая документация по классификации МКИ H 04 L 27/14 и YDK 621.393.3, относящихся ко всему устройству в целом. В результате анализа вышеуказанной литературы, которая изложена в тексте описания, заявителем не обнаружено технических решений, аналогичных предлагаемому.

3. Также можно доказать появление у объекта новых свойств, не присущих его частям. Каждый из введенных блоков выполняет в отдельности те же функции, что и в известных устройствах, например блоки памяти считывают и записывают сигналы, сумматоры суммируют и т.д. Однако, введение новых блоков и связей между ними, а также новые электрические связи между введенными узлами и узлами прототипа создают новый механизм взаимодействие, который обеспечивает разделение сигналов двух направлений при изменении параметров канала связи и позволяют автоматически вести подстройку устройства.

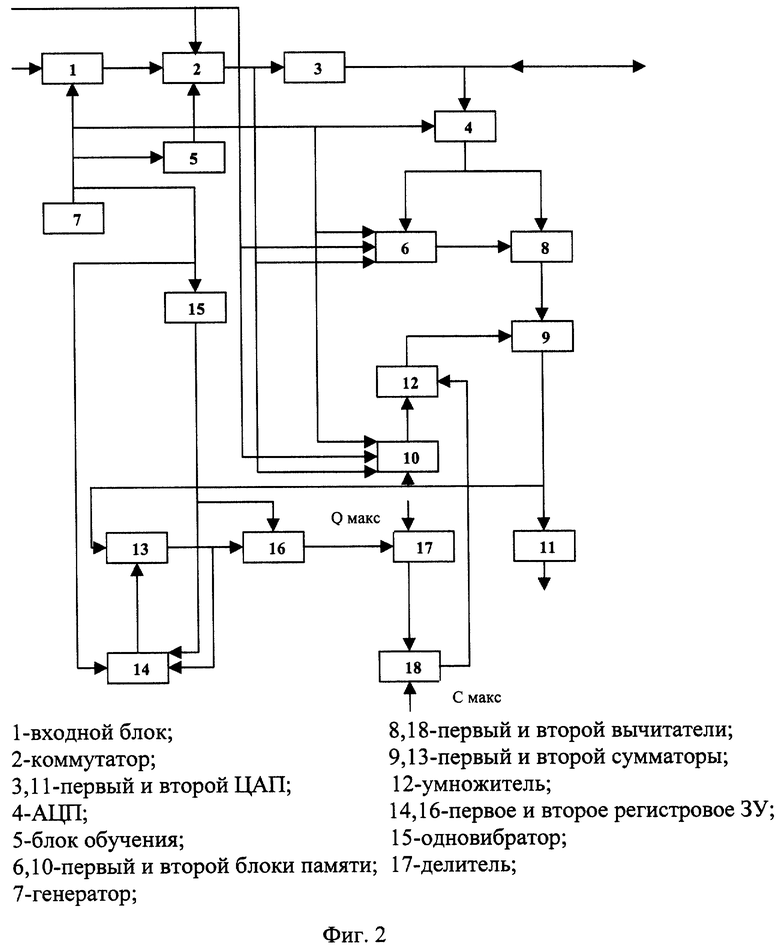

Устройство (см. фиг.2) содержит:

1. входной блок;

2. коммутатор;

3. первый ЦАП;

4. АЦП;

5. блок обучения;

6. первый блок памяти;

7. генератор;

8. первый вычитатель;

9. первый сумматор;

10. второй блок памяти;

11. второй ЦАП;

12. умножитель;

13. второй сумматор;

14. первое регистровое ЗУ;

15. одновибратор;

16. второе регистровое ЗУ;

17. делитель;

18. второй вычитатель.

Конструктивное выполнение сумматоров и вычитателей (блоки 8, 9, 13, 18) известно. Это м/схемы 155ИМ1, 555ИМ1 и т.д./3/.

Конструктивное выполнение блоков памяти (блоки 6 и 10) известно. Это ОЗУ с произвольной выборкой /3/.

Блок 5 обучения можно построить на цифровых счетчиках, к примеру 155ИЕ5.

Умножитель (блок 12) и делитель (блок 17) выполняются либо на основе ПЗУ, либо на сумматорах, к примеру 555ИМ1 /3.4/.

АЦП и ЦАП (блоки 1, 3, 4, 11) стандартные узлы, реализованные в виде готовых микросхем.

Конструктивное выполнение регистровых запоминающих устройств известно. Это, к примеру, 555ТМ8 /3/.

Конструктивное выполнение остальных блоков также известно /3, 4/.

Принципы работы устройства заключаются в следующем. Сразу после включения устройства по сигналу выхода оконечного оборудования данных ООД (на Фиг.2 не показан) производится кратковременное обнуление первого 6 и второго 10 блоков памяти и подключение выхода блока обучения 5 через коммутатор 2 ко входу первого 3 цифроаналогового преобразователя. Блок обучения 5 выдает в цифровом форме все используемые цифровые комбинации Ui(nT).

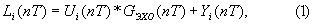

Эти цифровые комбинации Ui(nT) с помощью первого 3 ЦАП превращаются в аналоговое напряжение и поступают в сторону противоположной станции Б. Одновременно сигнал передачи совместно с сигналом приема станции Б поступает на вход АЦП 4. На входе АЦП 4 наблюдаем суммарный процесс в виде

где Li(nT) - сигнал на входе АЦП 4;

Ui(nT) - сигнал передачи станции А (обучающий сигнал);

GЭХО(nT) - импульсная реакция эхо-тракта;

Yi(nT) - сигнал приема;

n - текущий номер временного отсчета;

Т - интервал дискретизации;

* - символ линейной свертки.

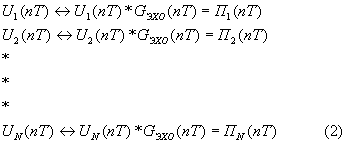

Подстрочный индекс означает номер разрешенной передаваемой комбинации. В силу линейности операции свертки наблюдается жесткая связь между сигналом обучения Ui(nT) и величиной эхо-сигнала, равное Ui(nТ)*GЭХО(nT).Тогда первой разрешенной цифровой комбинацией сигнала обучения U0(nT) соответствует эхо-сигнал, равный

U0(nT)*GЭХО(nT)=П0(nT)

Аналогично можно сказать и про остальные разрешенные цифровые комбинации. Таким образом:

В выражении (2) величиной Пi(nТ) обозначено значение эхо-сигнала.

В силу жесткой связи между передаваемым сигналом и эхо-сигналом производится запись информационного сигнала в первый 6 и второй 10 блоки памяти. Адресом для первого 6 и второго 10 блоков памяти служит информационный сигнал передачи Ui(nT) с выхода коммутатора 2. Рассмотрим процесс записи и считывания информационного сигнала в первый 6 и второй 10 блоки памяти более подробно.

Порядок работы этих блоков памяти следующий:

вначале по заданному адресу производится считывание информационного сигнала, а затем по этому же адресу производится запись. В первый 6 блок памяти производится запись сигнала с АЦП 4, а во второй 10 блок памяти записывается сигнал с выхода первого 9 сумматора.

Для понимания сути происходящих процессов будем полагать, что блок 5 обучения выдает М раз подряд первую разрешенную цифровую комбинацию (сигнал обучения) в виде

[U0(0Т); U0(1T);...U0(MT)]

Так как разрешенная комбинация неизменна, то в этом случае адрес для первого 6 и второго 10 блоков памяти будет неизменным.

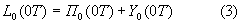

На выходе АЦП 4 в момент времени, равный (0Т), наблюдаем сумму двух сигналов: эхо-сигнала и сигнала приема.

где П0(0T) - отсчет эхо-сигнала в начальный момент времени.

Y0(0Т) - отсчет сигнала приема.

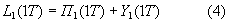

В силу того, что первый 6 и второй 10 блоки памяти при первом включении устройства были обнулены, то по адресу U0(nT) из указанных выше блоков памяти считываются нули. В начальный момент времени на выходе вычитателя 8 и первого сумматора 9 сигнал будет равен значению L0(0T), описываемому выражением (3), которое записывается в первый 6 и второй 10 блоки памяти. Рассмотрим, каким образом производится обработка сигнала на последующих временных интервалах в момент времени, равный (1T). На выходе АЦП 4 наблюдаем сигнал, равный

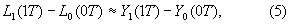

На выходе первого вычитателя 8 сигнал будет равен

Справедливость выражения (5) можно объяснить следующим образом. Значения эхо-сигнала П0(0T) и П0(1T) отличаются друг от друга на малую величину из-за того, что параметры эхо-тракта на соседних временных интервалах изменяются незначительно.

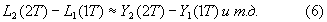

На втором (2Т) временном интервале сигнал на выходе вычитателя 8 будет равен

Рассмотрим процесс, происходящий в сумматоре 9, втором 10 блоке памяти и умножителе 12. Заметим, что такая совокупность блоков, указанных выше, представляет собой рекурсивный цифровой фильтр. В течение всего периода обучения на второй вход умножителя 12 подано значение коэффициента передачи, близкого к единице, но меньше единицы на малую величину. Обозначим через "С" - коэффициент, на значение которого производится умножение содержимого второго 10 блока памяти в умножителе 12.

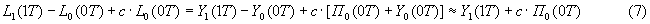

Напомним, что после временного интервала, равного (0Т) во втором 10 блоке памяти по адресу U0(0T) хранится значение сигнала, равное L0(0T). На первом (1T) временном интервале с помощью второго 10 блока памяти, умножителя 12 и сумматора 9 выходной сигнал сумматора 9 будет равен

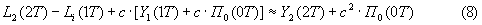

Эта величина записывается во второй 10 блок памяти по адресу U0(1T), на втором временном интервале (2Т), результат суммирования на выходе сумматора 9 будет равен

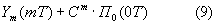

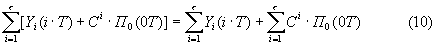

Спустя М временных интервалов на выходе сумматора 9, результат будет равен

Так как величина С<1, то второе слагаемое постоянно уменьшается, стремясь в пределе к величине шумов недокомпенсации. Скорость сходимости процесса настройки всего устройства определяется величиной "С". Чем меньше величина "С", тем скорость сходимости больше. Величина коэффициента "С" определяется вторым 13 сумматором; первым 14 и вторым 16 регистровыми запоминающими устройствами, делителем 17, вторым вычитателем 18 и одновибратором 15.

Рассмотрим процесс формирования управляющего коэффициента "С".

С началом обучения устройства помимо обнуления первого 6 и второго 10 блоков памяти производится обнуление первого 14 и второго 16 регистровых ЗУ. После обнуления указанных выше регистровых ЗУ с помощью второго 16 и первого 14 регистровых ЗУ производится суммирование всех отсчетов сигнала, полученного с выхода сумматора 9.

В /5/ приведены коэффициенты корреляции отсчетов сигнала приема для речевого сигнала и сигналов передачи данных. Спустя 2,5 мс отсчеты принимаемого сигнала независимо от природы возникновения становятся некореллированными. Величина отсчетов эхо-сигнала Пi(nT), считанное из второго 10 блока памяти, многократно повторяется. Отсчеты эхо-сигнала корреллируют друг с другом на интервале, превышающем 2,5 мс. Данный факт положен в основу расчета управляющего коэффициента "С". Выходной сигнал второго 13 сумматора определяется выражением

где τ - это интервал суммирования.

Первое слагаемое (10) определяет величину помехи в системе формирования коэффициента "С".

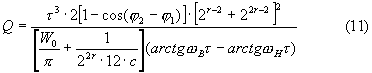

Второе слагаемое (10) определяет величину сигнала управления. Отношение сигнал/помеха управляющего значения на выходе второго 13 сумматора определяется выражением /6/.

где r - разрядность обработки;

ϕ2, ϕ1 - фазовые сдвиги, вносимые эхо-трактом на интервале анализа;

W0 - спектральная плотность мощности сигнала приема;

ωн, ωв - соответственно нижняя и верхняя частота пропускания эхо-тракта;

τ - интервал суммирования.

Интервал суммирования τ задается с помощью одновибратора 15. По окончании этого интервала результат суммирования с выхода второго 13 сумматора переписывается во второе 16 регистровое ЗУ, а первое 14 регистровое ЗУ обнуляется. С помощью второго 13 сумматора и первого 14 регистрового ЗУ производится расчет нового значения Qi на следующем интервале анализа τ и т. д.

Таким образом, во втором 16 регистровом ЗУ хранятся величины сигнала управления Qi, которые используются в дальнейшем для формирования коэффициента "С".

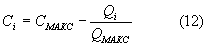

Текущее значение Qi, хранящееся во втором регистровом ЗУ, поступает на вход делителя 17. Указанный выше блок производит деление текущего значения Qi на максимально возможное значение QМАКС, которое рассчитывается по формуле (10). В вычитателе 18 производится вычитание из значения CМАКС величины  которое получено с выхода делителя 17.

которое получено с выхода делителя 17.

Тогда текущее значение коэффициента передачи будет определяться следующим выражением

Из выражения (12) видно следующее. Чем меньше значение Qi, тем больше величина Сi. Это свидетельствует о том, что процесс компенсации П0(0T) во втором 10 блоке памяти завершен.

Данная структура является адаптивной при любых изменениях параметров эхо-тракта. Действительно, на каком-то временном интервале работы устройства параметры эхо-тракта изменились таким образом, что во втором 10 блоке памяти появилась величина эхо-сигнала Пi(iT).

Значение эхо-сигнала Пi(iT) во втором 13 сумматоре и первом 14 регистровом ЗУ пересчитывается в управляющий сигнал Qi в соответствии с выражением (10). Окончательно с помощью выражения (12) производится расчет величины "Сi"; так как по нашему условию появился сигнал недокомпенсации, то тогда будет выполнятся условие Сi<Ci-1, и система вновь подстроится под новые передачи.

В силу того, что текущее значение коэффициента Сi всегда меньше единицы, то это позволяет подстраиваться под новые условия, даже если Сi=CМАКС. При других значениях передаваемого сигнала процессы будут аналогичными.

Оценим преимущества заявленного устройства по сравнению с прототипом, взятым за базовый объект. Как указано в материалах заявки, прототип при обучении требует отсутствия сигналов приема и специального алгоритма вхождения в рабочий режим.

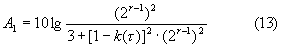

Величина защищенности у прототипа при переходе эхо-тракта в другое состояние будет равна

где r - разрядность обработки;

к(τ) - коэффициент корреляции отсчетов эхо-сигналов.

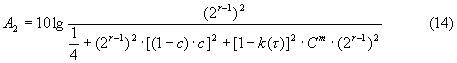

Величина защищенности в заявленном устройстве определяется в виде

где М - число циклов.

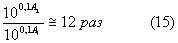

При заданных значениях r и k(τ), а также С<1 всегда А2>А1. Величина выигрыша будет равна

Таким образом величина положительного эффекта поясняется вышеизложенным текстом, формулами (13-15) и результатами эксперимента, полностью подтвердившими теоретические выкладки.

Литература

1. Адаптивные фильтры. Под ред. К.Ф.Коуэна и П.М.Гранта. М.: Мир, 1988, - 298 с. (аналог).

2. А.С.№1133675. Устройство для разделения сигналов передачи и приема в дуплексных системах связи (прототип), опублик. в БИ №1, 07.01.1985.

3. В.Г.Тарабрин. Справочник по микросхемам. М., 1986.

4. Б.А.Калабеков. Микропроцессоры и их применение в системах передачи и обработки сигналов. М.: Радио и Связь, 1988.

5. Величкин А.И. Теория дискретной передачи непрерывных сообщений. - М.: Сов. Радио, 1970, с.242-251.

6. Малинкин В.Б. Разработка и исследование относительных компенсационных методов в одновременных двусторонних системах связи. Докторская диссертация.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2001 |

|

RU2223599C2 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2001 |

|

RU2233553C2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1987 |

|

SU1483647A2 |

| Устройство для разделения сигналов двух направлений | 1989 |

|

SU1658393A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

| Эхокомпенсатор | 1990 |

|

SU1707766A1 |

| Адаптивное дуплексное устройство для передачи и приема фазоманипулированных сигналов | 1985 |

|

SU1256238A2 |

Изобретение относится к области электросвязи и к дуплексной передаче сигналов по каналам связи. Технический результат заключается в повышении помехоустойчивости. Для этого в устройство разделения сигналов передачи и приема дополнительно введено устройство управления коэффициентом передачи в цепи обратной связи второго блока памяти, вход которого подключен к выходу сумматора, состоящее из интегратора, регистрового запоминающего устройства, делителя, вычитателя, соединенных последовательно, причем на вторые входы делителя и вычитателя постоянно подается максимально возможное на интеграторе значение, а одновибратор задает время работы интегратора. 2 ил.

Устройство для разделения сигналов передачи и приема в дуплексных системах связи, содержащее последовательно соединенные генератор, входной блок, второй вход которого является входом сигналов передачи, коммутатор, первый цифроаналоговый преобразователь, выходом соединенный с двухпроводным каналом связи, аналогоцифровой преобразователь, первый блок памяти, первый вычитатель, первый сумматор, второй блок памяти, а также блок обучения и второй цифроаналоговый преобразователь, при этом выход генератора соединен со вторыми входами соответственно аналого-цифрового преобразователя, первого и второго блоков памяти, а также с входом блока обучения, выход которого соединен со вторым входом коммутатора, третий вход которого является управляющим и соединен с третьими входами первого и второго блоков памяти, выход коммутатора соединен с четвертыми входами первого и второго блоков памяти, выход первого сумматора соединен со входом второго цифроаналогового преобразователя, выход которого является выходом устройства, а выход аналого-цифрового преобразователя соединен со вторым входом первого вычитателя, отличающееся тем, что введены последовательно соединенные второй сумматор, второе регистровое запоминающее устройство, делитель, второй вычитатель и умножитель, а также одновибратор и первое регистровое запоминающее устройство, выход которого соединен со вторым входом второго сумматора, первый вход которого объединен с входом второго цифроаналогового преобразователя, при этом выход одновибратора соединен со вторыми входами первого и второго регистровых запоминающих устройств, являющихся соответственно обнуляющим входом R и входом тактирования, выход второго сумматора соединен с первым информационным входом первого регистрового запоминающего устройства, третий вход которого является тактирующим входом, соединен со входом одновибратора и объединен с выходом генератора, на второй вход делителя подключено максимально возможное значение управляющего сигнала Qмакс, а на второй вход второго вычитателя подключено максимальное значение коэффициента передачи Смакс, при этом выход второго блока памяти соединен со вторым входом умножителя, выход которого соединен со вторым входом первого сумматора.

| Устройство для разделения направлений передачи в дуплексных системах связи | 1983 |

|

SU1133675A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1987 |

|

SU1483647A2 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1993 |

|

RU2039415C1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1992 |

|

RU2038702C1 |

Авторы

Даты

2005-06-27—Публикация

2003-03-20—Подача