СП

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейрный сумматор | 1990 |

|

SU1795454A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Конвейерный сумматор | 1982 |

|

SU1067499A1 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 2001 |

|

RU2199774C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для сложения @ чисел | 1980 |

|

SU1012243A1 |

| Арифметическое устройство | 1985 |

|

SU1305662A2 |

| Логическое запоминающее устройство | 1974 |

|

SU507899A1 |

Изобретение относится к вычислительной технике и предназначено для использования в мультиконвейерных системах цифровой обработки сигналов. Цель изобретения - расширение функциональных возможностей устройства за счет суммирования групп операндов. Конвейерный N-входовый сумматор содержит входы 1 1, ..., 1 N, суммирующие ячейки 2, выходы 3, выходы 4 ячеек, шину 5 синхронизации и шину 6 установки в "О". Ячейка 2 содержит тревходовый комбинационный сумматор и триггер. 2 ил., 1 табл.

I .

ел ю

0s 00 N5 О

Изобретение относится к вычислительной технике и предназначено для использования в мультиконвейериых системах цифровой обработки сигналов.

Цель изобретения - расширение функциональных возможностей устройства за счет реализации суммирования групп операндов.

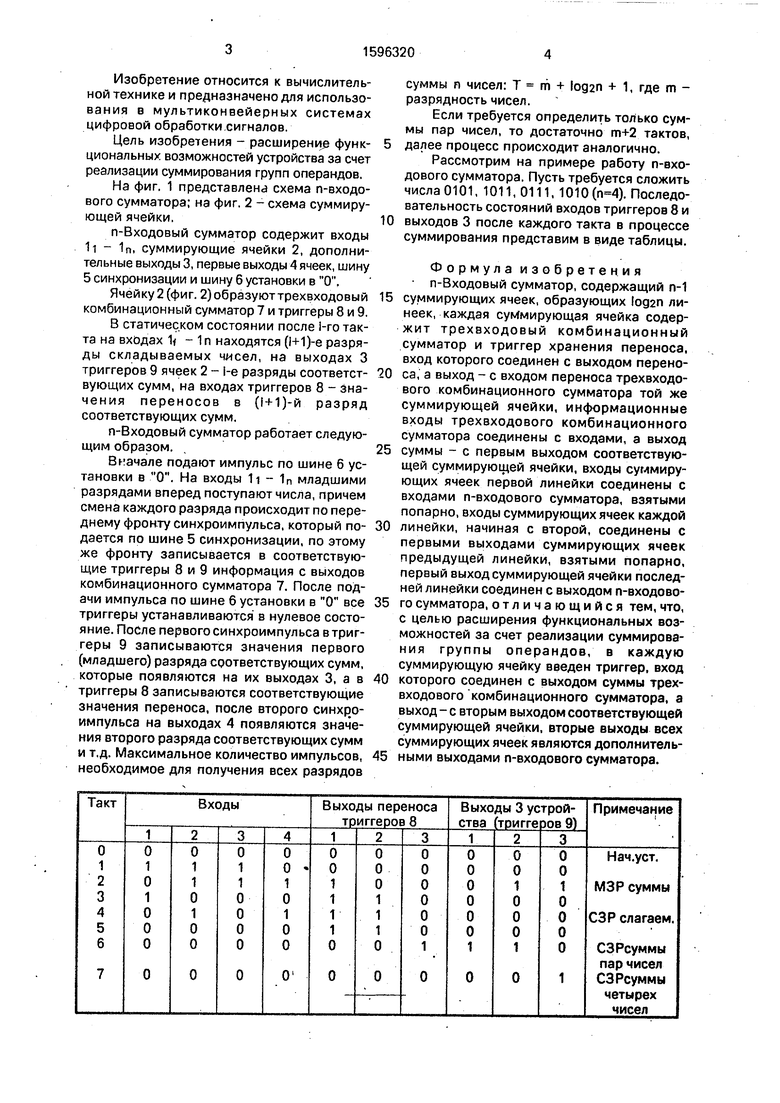

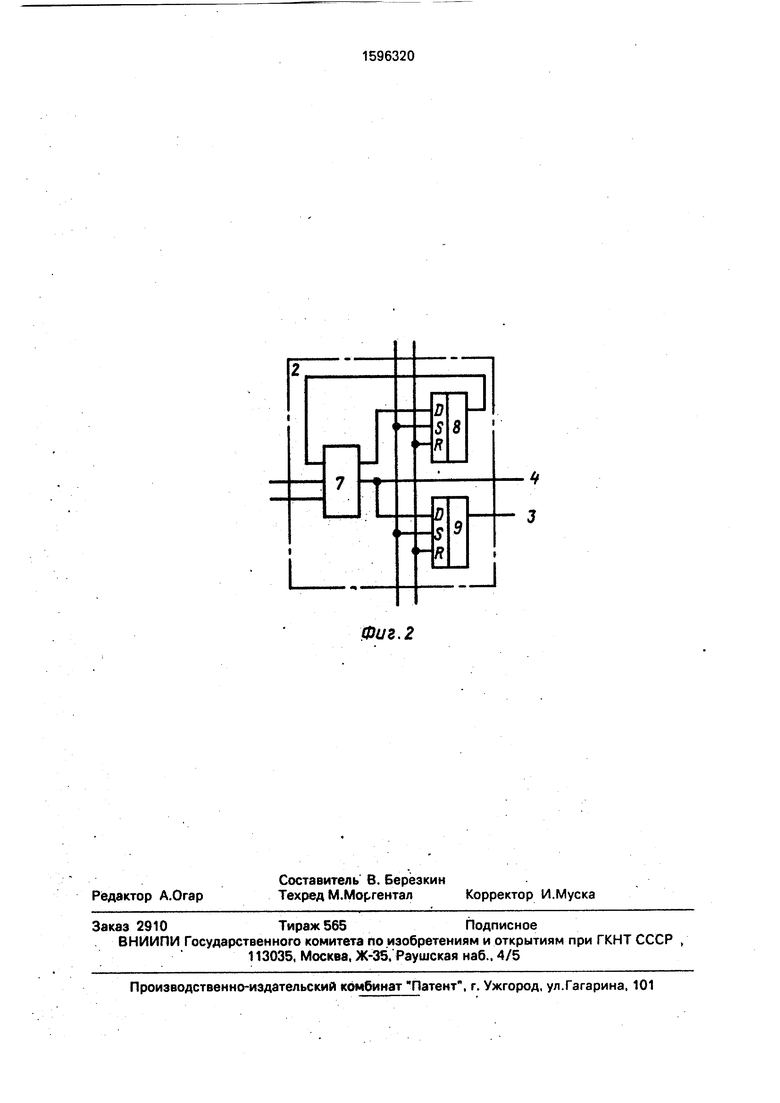

На фиг. 1 представлена схема п-входового сумматора; на фиг. 2 - схема суммирующей ячейки.

п-Входовый сумматор содержит входы 1i - In, суммирующие ячейки 2, дополнительные выходы 3, первые выходы 4 ячеек, шину 5 синхронизации и шину 6 установки в О,

Ячейку 2 (фиг. 2) образуют трехвходовый комбинационный сумматор 7 и триггеры 8 и 9.

В статическом состоянии после 1-го такта на входах 1 - 1п находятся (1+1)-е разряды складываемых чисел, на выходах 3 триггеров 9 ячеек 2 - i-e разряды соответствующих сумм, на входах триггеров 8 - значения переносов в (1+1)-й разряд соответствующих сумм.

п-Входовый сумматор работает следующим образом.

Вначале подают импульс по шине 6 установки в О. На входы 1i - In младшими разрядами вперед поступают числа, причем смена каждого разряда происходит по переднему фронту синхроимпульса, который подается по шине 5 синхронизации, по этому же фронту записывается в соответствующие триггеры 8 и 9 информация с выходов комбинационного сумматора 7. После поДачи импульса по шине 6 установки в О все триггеры устанавливаются в нулевое состояние. После первого синхроимпульса в триггеры 9 записываются значения первого (младшего) разряда соответствующих сумм, которые появляются на их выходах 3, а в триггеры 8 записываются соответствующие значения переноса, после второго синхроимпульса на выходах 4 появляются значения второго разряда соответствующих сумм и т.д. Максимальное количество импульсов, необходимое для получения всех разрядов

суммы п чисел: Т m + 1од2П + 1, где m разрядность чисел.

Если требуется определить только суммы пар чисел, то достаточно т+2 тактов, далее процесс происходит аналогично.

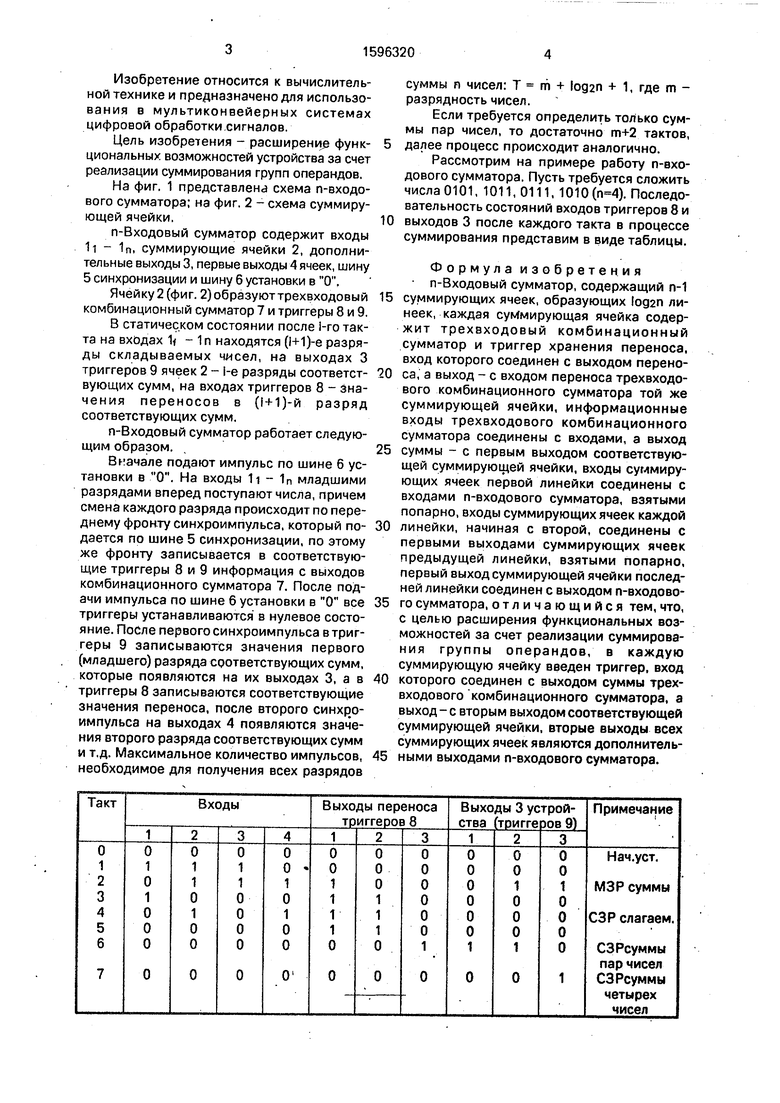

Рассмотрим на примере работу п-входового сумматора. Пусть требуется сложить числа 0101, 1011, 0111, 1010 (). Последовательность состояний входов триггеров 8 и выходов 3 после каждого такта в процессе суммирования представим в виде таблицы.

Формула изобретения п-Входовый сумматор, содержащий п-1

суммирующих ячеек, образующих logan линеек, каждая суммирующая ячейка содержит трехвходовый комбинационный сумматор и триггер хранения переноса, вход которого соединен с выходом переноса, а выход - с входом переноса трехвходового комбинационного сумматора той же суммирующей ячейки, информационные входы трехвходового комбинационного сумматора соединены с входами, а выход

суммы - с первым выходом соответствующей суммирующей ячейки, входы суммирующих ячеек первой линейки соединены с входами п-входового сумматора, взятыми попарно, входы суммирующих ячеек каждой

линейки, начиная с второй, соединены с первыми выходами суммирующих ячеек предыдущей линейки, взятыми попарно, первый выход суммирующей ячейки последней линейки соединен с выходом п-входового сумматора, отличающийся тем, что, с целью расширения функциональных возможностей за счет реализации суммирования группы операндов, в каждую суммирующую ячейку введен триггер, вход

которого соединен с выходом суммы трехвходового комбинационного сумматора, а выход - с вторым выходом соответствующей суммирующей ячейки, вторые выходы всех суммирующих ячеек являются дополнительными выходами п-входового сумматора.

4- J

Фиг. 2

| Конвейерный сумматор | 1982 |

|

SU1067499A1 |

| Обработка физической информации/Под ред | |||

| Б.Н.Малиновского | |||

| Киев: Наукова думка | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| с | |||

| Способ получения бензидиновых оснований | 1921 |

|

SU116A1 |

Авторы

Даты

1990-09-30—Публикация

1988-03-31—Подача