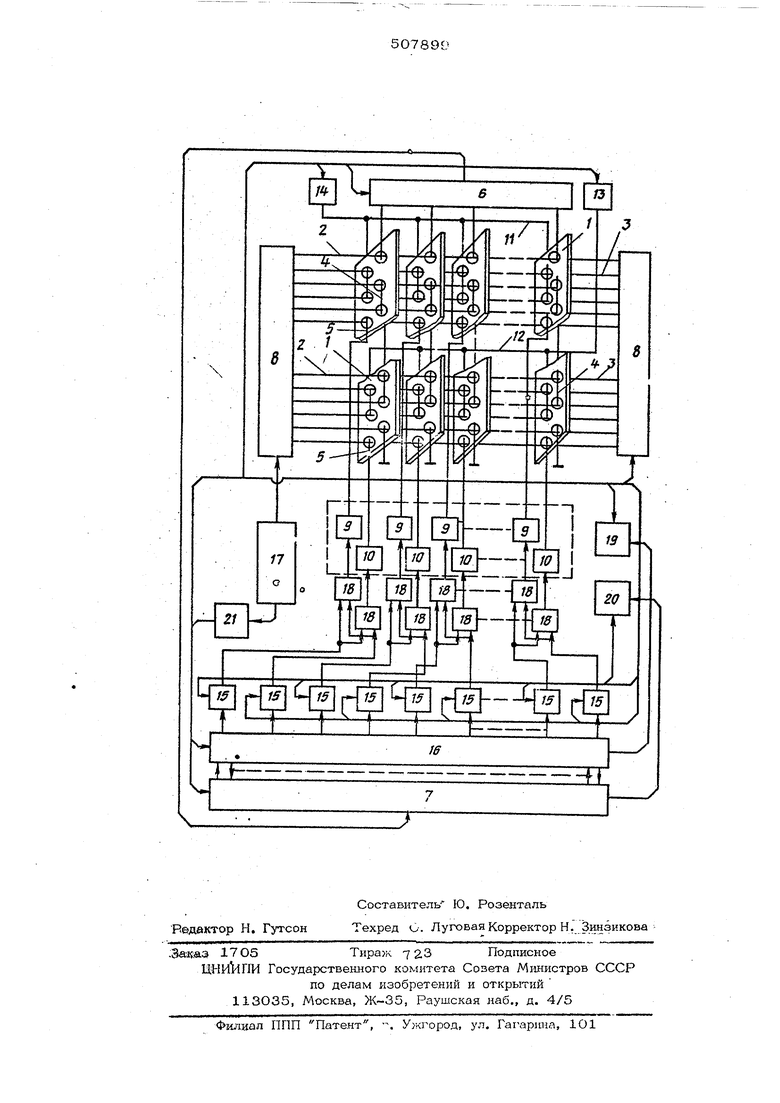

(54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО Оло содер / 1Т накспш-ель, вьЕПояненкый на шггегральлых числовых лш1ейках 1 с адjjeciibiMH шшгами опроса 2, записи 3 и ршзряд.и.1ми обмотками считывания 4, запрета 5, Выходы блока усилиггелей воспроизведения 6 соед1шены с соответствующими разрядными обмотками считывания 4, а выходы с блоком вентилей сдвига 7. Блоки выборки адресов 8 подключены к соответ- ствуюшим адресным шинам опроса 2 и записи 3, Формирователи разрядного тока запрета первых операндов 9 и вторых операндов 10 соедшюны с соответствующими обмотками запрета по каждому разряду в отдельности, выходы которых объединены в группы первых операндов 11 и вторых операндов 12 и подключены к одноименным генераторам тока 13 и 14, Разрядные элементы И 15, выходы которых соединены с/ соответств тощими выходами разрядного регистра 16 и блока синхронизации 17, соедшгены с разрядными элементами ИЛИ 18. Узел анализа знака 19 подключен к разрядному регистру 16, а узел гшализа переполления 2О к блоку вентилей сдвига 7, Узел дополнительных элементов И подключен к блоку вентилей сдвига 7 и разрядному регистру 16. Устройство работает следующим образом: В исходном состоянии в AJ - ой ячейке накопителя, пргшадлежащей к группе яче ек первых операндов, хранится операнд У ( У-. ......,Уу), а второй операнд X ( Х ,,, ...., Xj) хранится в Ai -ой ячейке, принадлежащей к группе ячеек вторых операндов. Рассмотрим реализацию операции суммирования, на которой основаны другие ари метические операции: сложение, вычитание, у-множение, деление. Алгоритм суммирования сводится к формированию п разрядн9го слова суммы SL .rio mod 2 и слова переносов , Pi + I , сдви нутому на один разряд влево. После получения первого слова суммы по rriDd 2 и слдрд переносов проводится анализ слова I7i3pp}}aeGfi, Если Pi-tl , то цикл Суммираваияя повторяется, причем, операция поразрядного суммирования по mod 2 выполняется меходу словом суммы по mod 2 и словом переносов, сдвинутому на один ра ряд в сторону старших разрядов. При Р О процесс суммирования заканчивается, Пикл суммирования реализуется за 16 робочих тактов, что на 5 тактов меньше, jex-f в приведенном прототипе. D 1-ом такте, как обычно перед началом работы, производится уста 1овка в состояние О всех триггеров разрядного регистра, узла анализа злака и блока синхронизации. Во 2-ом такте производится считывалие Aj ячейки, содержимое которой поступает через блок усилителей воспроизведения и вентилей сдвига в разрядный регистр В 3-ем такте содержимое разрядного регистра (У) записывается обратно в яче&.ку Aj , при этом срабатывает генератор тока первого операнда 13 и соответствую- щйе формирователи разрядного тока запрета первых операндов. в 4-ом такте значение операнда У, хранящегося в разрядном регистре, сдвигаетсяна один разряд влево. В 5-ом такте содержимое разрядного ре- гистра (У) инвертируется и записывается в ячейку Aj + 1 аналогично 3-му такту. В 6-ом такте разрядный регистр уста- , навливается в состоадие О. В 7-ом считывается ячейка Ai и содержимое её запоминается в разрядном регистре,о В 8-ом такте производится запись прямого кода содержимого разрядаого регистра (X) в ячейку Ai , при этом срабатывает генератор тока второго операнда 14. В 9-ом такте 1швертированный код (X) защ1сывается в ячейку Aj - 1. В 10-ом такте разрядный регистр устанавливается в состояние О. В 11-ом такте считываются ячейки Aj и At и, в результате встречного включения обмоток считывания (усилители воспроизведения 2-х полярные), в разрядный регистр записывается первая сумма по mod 2, которая в следующем 12 такте заносится в ячейку Aj . Б 13-ом такте обнуляется разрядный регистр. В 14-ом считывается ячейка Aj + 1 и проивводится сдвиг содержимого на один разряд влево. В результате того в разрядном регистре будем иметь ( . у V X ). В 15-ом такте записывается в инвертированном виде содержимое из разрядного регистра в ячейку Al и производится анализ переноса. Если Р (у V Х ) 0, то суммирование заканчивается, если Р ч О, то Ш1КЛ суммирования повторяется. В 16-ом такте проводится анализ переполнения узлом 20. Операций сложения отличается от операции сумм1фования только тем, что производится преобразование прямых кодов операндов в обратные и результат операции записывается со свопм знаком, т.е. преобразование из обратного кода в П шмой. Выполнение операции вычитания отличав ется от операшш сложения тем, что у ; читаемо го необходимо инвертировать знак. Операшш умножения выполняется в со« ;ответствии с алгоритмом умноженя5 начи,ная с младших разрядов со сдвигом частичного произведенЕя вправо. В каждом цикле умножения множимое либо сумми руётся 6 частичным произведением, если в соответI ствуюшем разряде множителя была едини- на, либо не суммируется, если в соответ; ствующем разряде множителя был нуль. При этом знак полученнохч) произведения опре- деляется1, как сумма по кйэдулю 2 знаков множимого и множителя, а затем присвай- вается произведению. Значение младшего разряда множителя и окончание операции умножения определяется посредством соответствующего узла дополнительных :элёмен- TOBVai. Формула иа обретен Логическое запоминающее устройство, содержащее накопитель на интегральных чи еловых ферритовых линейках, прошитых адреснымн шинами опроса и записи и разрядными обмотками считывания н запрета, блоки усилителей воспроизведения, входы которь1х соединены с юоответству1(зи1лми разрядныйй Обмотками считывания, а ьыходы - с вентилей сдвига, блоки выборки aj ресов, подключенные к соответствующим ад- ресным шинам опроса и записи, формировате- ли разрядного тока запрета первых и вторых операндов соединенные с соответствующими обмотками запрета в каждом разряде, разрядные элементы И , входы которых соединены с соответствующими выходами разрядного регистра и блока синхронизации, а выходы - с разрядными элементами ИЛИ, узел анализа знака, подключенный к разрядному регистру, и узел анализа переполнения, соединенный с блоком вентилей сдвига, о т л Й1ч а кГ щ е ее я тем, что, с повышения быстродействия устройства, оно содержит генераторы тока первого и второго операндов, подключенные к соответствующим обмоткам запрета каждого операнда, а обмотки считывания первых И .вторых операндов включены в каждом раз;раде встречно.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Логическое запоминающее устройство | 1980 |

|

SU942152A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Процессорный элемент | 1980 |

|

SU881757A1 |

| АССОЦИАТИВНОЕ ПАРАЛЛЕЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕУСТРОЙСТВО | 1970 |

|

SU288414A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

Авторы

Даты

1976-03-25—Публикация

1974-05-24—Подача