Устройство относится к средствам управления и может применятся при автоматизации в технологических процессах и в производстве.

Известно устройство, содержащее входной и выходной блоки, блок оперативной памяти, блок синхронизации, адресные и командные шины, генератор импульсов, программный блок, блок коммутации и вычисления, содержащий трехвходовой дешифратор, три двухвходовых элемента И, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и управляемую ячейку памяти с соответствующими связями [1].

К недостаткам этого устройства можно отнести относительно низкое быстродействие при обработке двоичной кодовой информации.

Наиболее близким по технической сущности является устройство, содержащее входной и выходной блоки, блок оперативной памяти, блок синхронизации, программный блок, командные и адресные шины, блок прерывания, коммутационно-вычислительный блок, состоящий из трехвходового дешифратора, элемента 2-2И-2ИЛИ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четырех элементов И, ячейки памяти с прямым и инверсным выходами, элемента ИЛИ и элемента НЕ с соответствующими связями [2].

К недостаткам этого устройства можно отнести относительно низкое быстродействие, большой объем ячеек памяти в программном блоке, трудоемкое программирование, что связано с большим количеством тактов, необходимых при организации сложения двоичных чисел.

Целью предлагаемого изобретения является повышение быстродействия устройства, упрощение процесса программирования и уменьшение числа ячеек памяти в программном блоке.

Для этого в программируемое устройство для управления электроприводами, электронными ключами и сигнализацией, содержащее входной блок, блок оперативной памяти, блок синхронизации, блок программ, блок прерывания, коммутационно-вычислительный блок, содержащий дешифратор, логический элемент И-ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй, третий и четвертый элементы И, элемент ИЛИ, элемент НЕ и первую ячейку памяти, причем первые входы логического элемента И-ИЛИ соединены соответственно с первым и вторыми выходами дешифратора, а вторые входы подключены соответственно к выходу входного блока, соединенного первой и второй группами входов соответственно с группой информационных выходов объекта управления и с адресными шинами блока программ, и к выходу блока оперативной памяти, выход логического элемента И-ИЛИ подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с соответствующим выходом блока программ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом первого элемента И, подключенного вторым входом к первому выходу блока синхронизации, соединенного вторым выходом с блоком прерывания, с первыми управляющими входами блока оперативной памяти и выходного блока, группа входов которых соединена с группой адресных шин блока программ, а информационные входы объединены и связаны с прямым выходом первой ячейки памяти, третий выход блока синхронизации соединен со счетным входом блока программ, третий и четвертый выходы дешифратора связаны соответственно со вторыми управляющими входами блока оперативной памяти и выходного блока, управляющий вход первой ячейки памяти соединен с выходом первого элемента И, ее информационный вход связан с выходом элемента ИЛИ, первый вход которого соединен с выходом второго элемента И, входы которого связаны с выходом элемента НЕ и с выходом программного блока, вход элемента НЕ подключен к выходу блока прерывания, второму входу третьего элемента И и первому входу четвертого элемента И, второй вход которого соединен с инверсным выходом ячейки памяти, а выход - со вторым входом элемента ИЛИ, прямой выход первой ячейки памяти связан с третьим входом третьего элемента И, выходы выходного блока соединены с электроприводами, электронными ключами и сигнализацией, четвертый вход третьего элемента И подключен к третьему выходу блока синхронизации, а выход третьего элемента И соединен с соответствующим входом блока прерывания, соединенного входами с определенными выходами блока программ, входы дешифратора соединены с выходами блока прерывания определенным образом, в коммутационно-вычислительный блок введены счетный триггер, вторая ячейка памяти, пятый и шестой элементы И, второй элемент ИЛИ.

При этом элемент И-ИЛИ выполнен в виде элемента 2-2-2И-3ИЛИ, а дешифратор снабжен пятым выходом, соответствующий вход элемента 2-2-2И-3ИЛИ подключен к пятому выходу дешифратора, прямой выход первой ячейки памяти связан со счетным входом счетного триггера, вход сброса в нуль которого соединен с выходом пятого элемента И, а выход подключен к информационному входу второй ячейки памяти, ее управляющий вход соединен с выходом шестого элемента И, а выход - с элементом 2-2-2И-3ИЛИ, первые входы пятого и шестого элементов И соединены с третьим и вторым выходами блока синхронизации, а вторые входы пятого и шестого элементов И объединены с выходом второго элемента ИЛИ, входы которого подключены к третьему и четвертому выходам дешифратора.

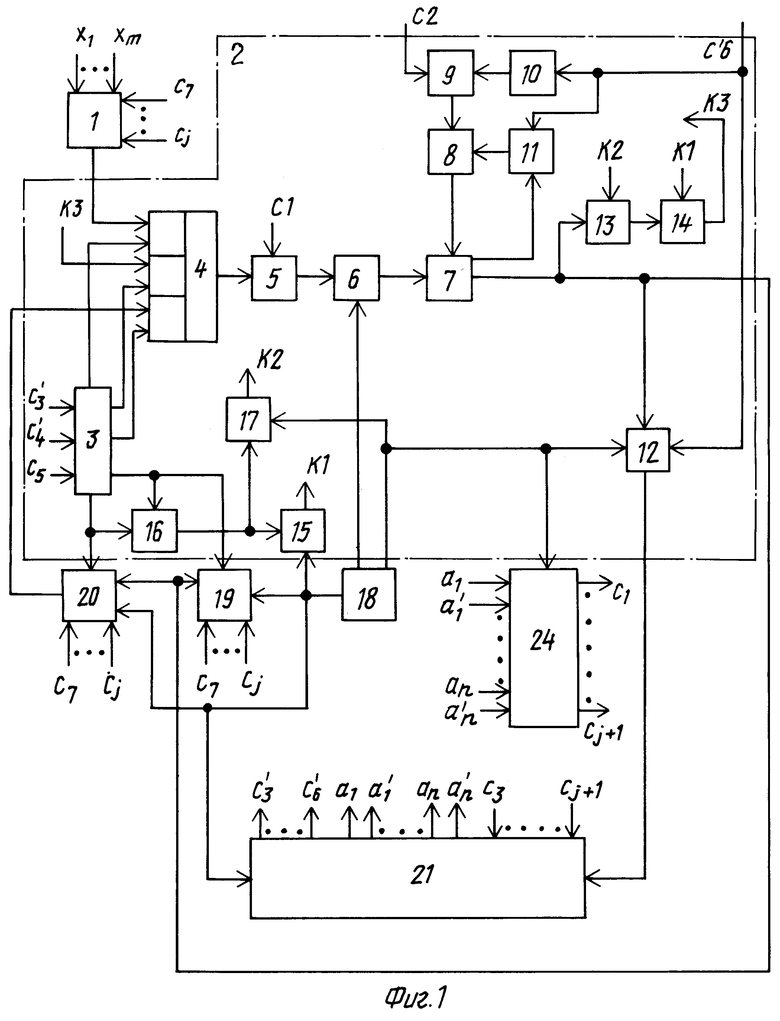

Предлагаемое устройство поясняется фиг.1.

Устройство состоит из входного блока 1, соответствующие входы которого подключены к первичным дискретным датчикам (задатчикам), которые на чертеже не показаны и с которых поступают сигналы Х1...Хm к адресным шинам, а выход соединен с коммутационно-вычислительным блоком (КВБ) 2, содержащим дешифратор 3, первым, пятым и вторым выходами соединенный с соответствующими входами элемента 2-2-2И-3ИЛИ 4, выход которого через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 и первый элемент И 6 подключен к управляющему входу первой ячейки памяти 7, информационный вход которой соединен с выходом элемента ИЛИ 8, первый вход которого связан с выходом второго элемента И 9, вход последнего подключен к выходу элемента НЕ 10, вход которого соединен с входом четвертого элемента И 11 и вторым входом третьего элемента И 12, третий вход последнего связан со счетным входом счетного триггера 13, выход которого соединен с информационным входом второй ячейки памяти 14, ее вход связан с выходом шестого элемента И 15, один из входов которого подключен к выходу второго элемента ИЛИ 16 и к входу пятого элемента И 17, другой вход последнего соединен с третьим выходом блока синхронизации 18, связанного вторым выходом с соответствующими входами выходного блока 19, блока оперативной памяти 20 и блока прерывания 21, подключенного своими входами и выходами к блоку программ 22.

C1...C6, Сj+1 - командные шины с выходов программного блока 22.

С7. . . Сj - адресные шины с выходов программного блока 22, сигналы на которых принимают значения "1" или "0" и определяют адреса операндов Х1...Хm входного блока 1 и ячеек памяти в блоках 19 и 20.

а1, а'1...аn, а'n - сигналы, устанавливающие счетные триггеры в блоке 22 в состояние внеочередного такта, имеют значение "0", "1".

Х1. . . Хm - дискретные сигналы от датчиков (задатчиков), т.е. кнопок, тумблеров, путевых выключателей, аналого-цифровых преобразователей и т.д.

В качестве первой ячейки памяти 7 можно использовать стандартный двухступенчатый D-триггер, срабатывающий по заднему фронту импульса.

В качестве триггера 13 можно использовать счетный триггер, срабатывающий по заднему фронту импульса и имеющий вход сброса в "0".

В качестве второй ячейки памяти 14 можно использовать D-триггер.

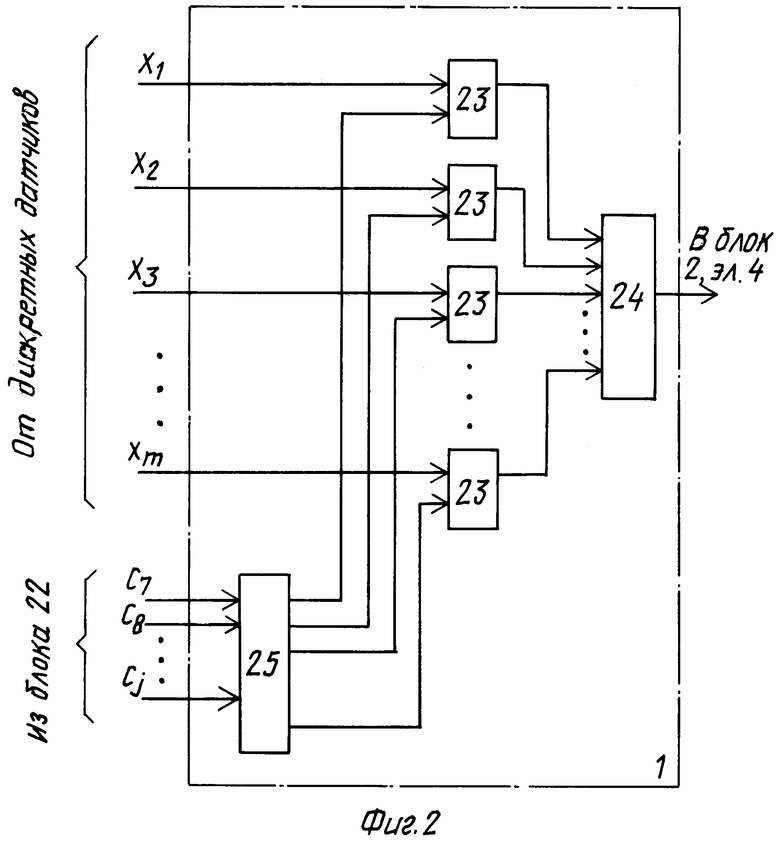

Входной блок 1 (фиг.2) содержит элементы И 23, связанные первыми входами с сигналами датчиков Х1...Хm, а выходами через элемент ИЛИ 24 соединенные с блоком 2, вторые входы элементов И 23 подключены к выходам дешифратора 25, входы которого соединены адресными шинами с блоком программ 22. В соответствии с сигналами С7...Сj переменные Х1...Хm поочередно считываются и подаются на вход блока 2.

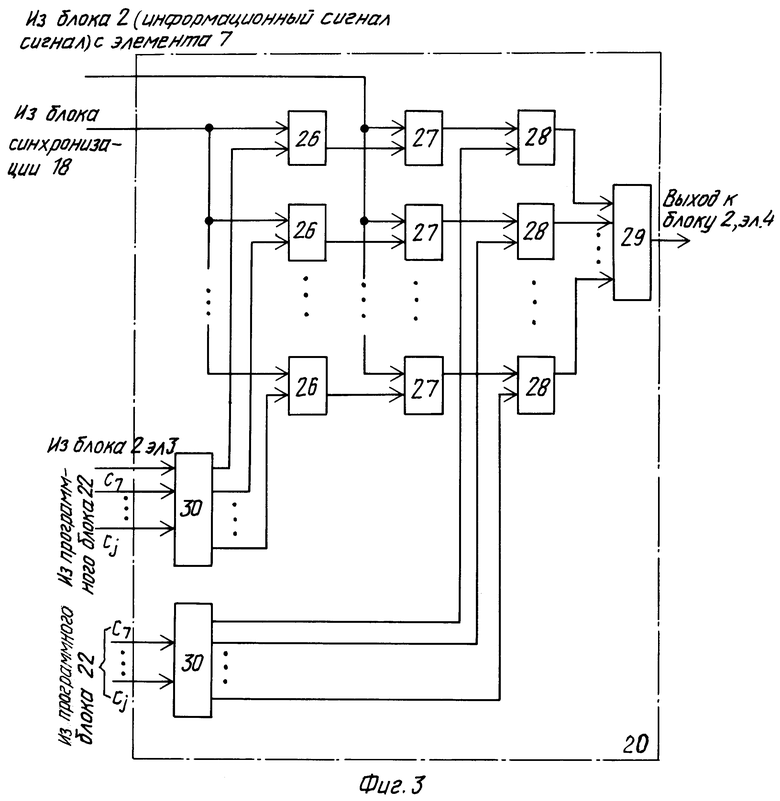

Блок оперативной памяти 20, представленный на фиг.3, содержит элементы И 26 обращения к ячейкам памяти 27, элементы считывания 28 (например, элементы И), элемент ИЛИ 29, первый и второй дешифраторы 30, при этом через соответствующие элементы 26 или 28 заносится в ячейку 27 или считывается из ячейки 27 информация по командам из дешифратора 3 блока 2 и в соответствии с адресами С7...Сj.

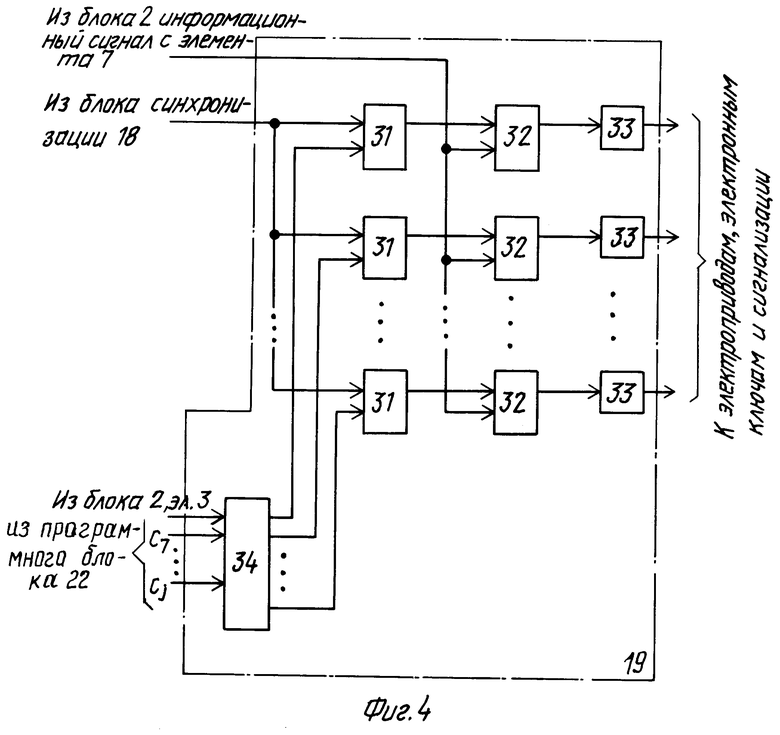

Выходной блок 19 (фиг.4) состоит из элементов И 31, ячеек памяти 32, куда заносится информация с выхода ячейки памяти 7 блока 2, и соответствующих усилителей 33, передающих логические сигналы из ячеек памяти 32 на электроприводы и т.д., по адресам С7...Сj и по команде с третьего выхода дешифратора 3 блока 2, поступающих на вход дешифратора 34 блока 19.

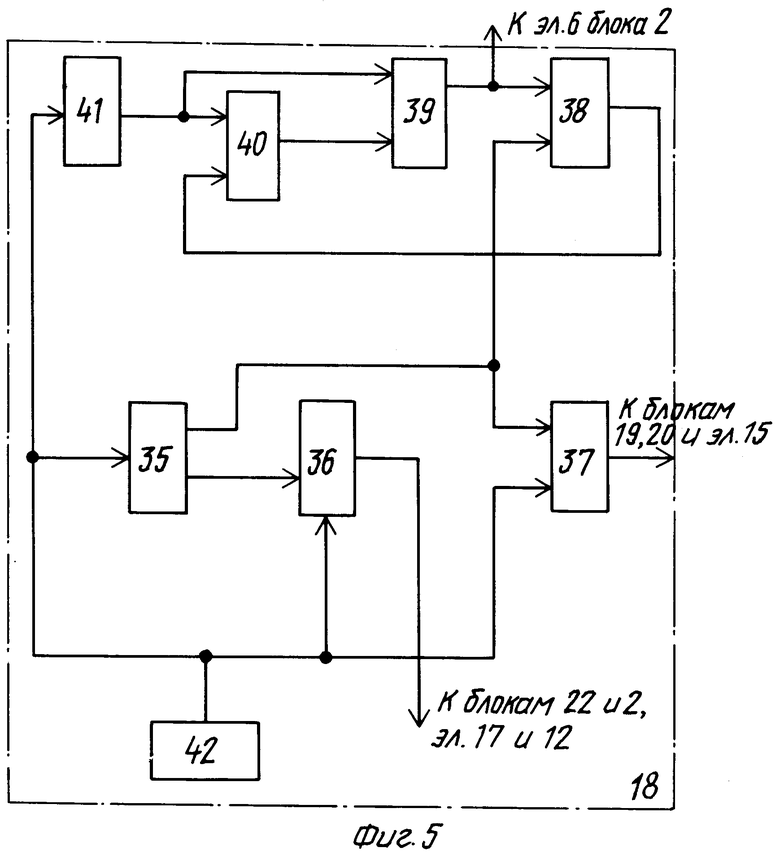

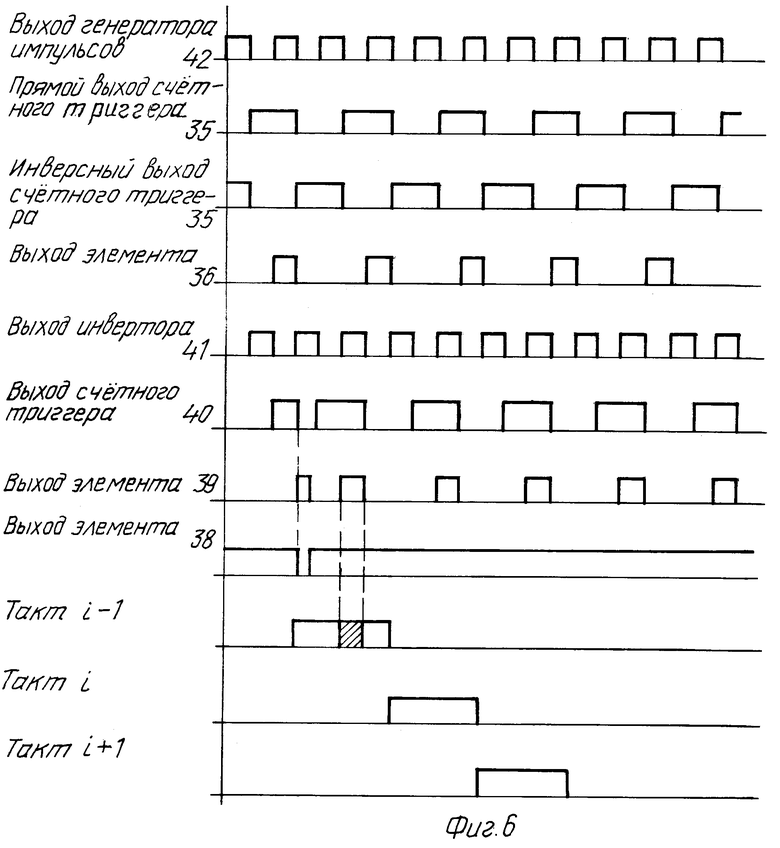

Блок синхронизации также известной конструкции (фиг. 5) 18 содержит первый счетный триггер 35, подключенный прямым выходом к элементу И 36, а инверсным выходом к первым входам элементов И 37 и И 38, второй вход последнего соединен с выходом элемента И 39, входы которого связаны с прямым выходом второго счетного триггера 40 и с выходом инвертора 41, вход которого вместе с входом триггера 35 подключены к генератору прямоугольных импульсов 42. Работа блока 18 поясняется диаграммами на фиг.6.

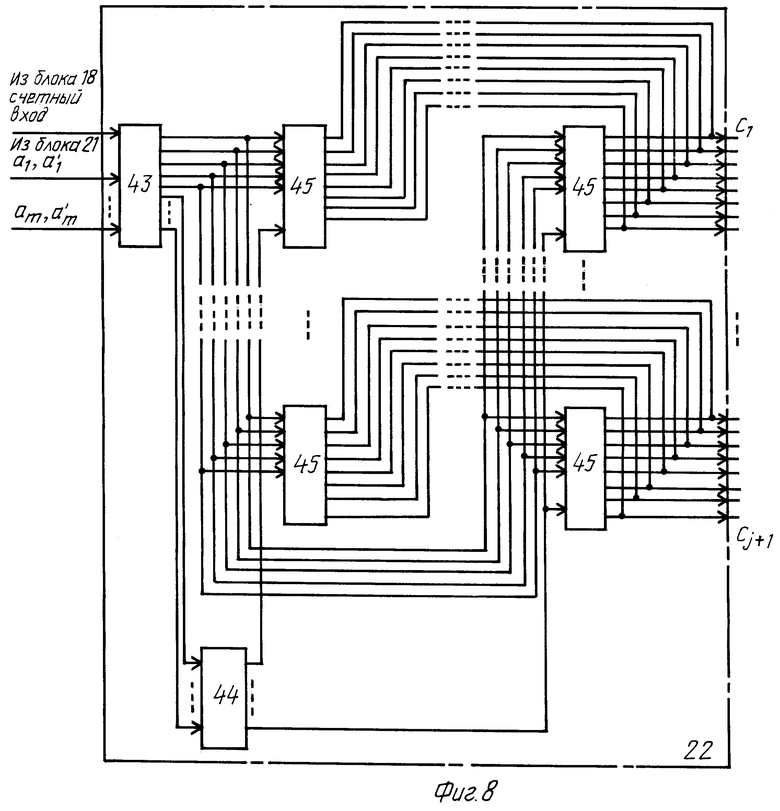

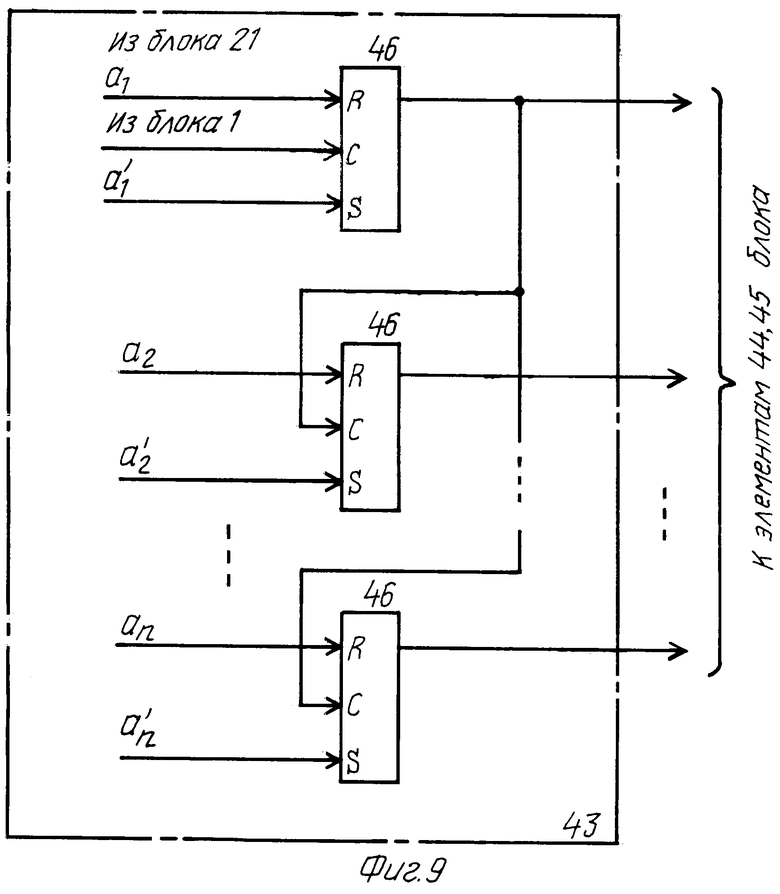

Программный блок 22 известной конструкции (фиг.8) состоит из счетчика импульсов с установочными R- и S-входами 43, на счетный вход которого поступают импульсы из блока 18 в четвертой четверти такта, а на установочные входы подаются сигналы a1, a'1...an, a'n, которые при нулевом сигнале на выходе элемента И 12 блока 2 и соответственно на входе электронного ключа 50 блока 21 все равны "1", что обеспечивает работу триггеров 46 (например, К531ТВ9) в штатном режиме переключений, если же на указанном выше управляющем входе ключа 50 присутствует единичный сигнал, то значения выходов ячеек памяти 49 блока 21 через открытый ключ 50 поступят на установочные R- и S-входы триггеров 46, устанавливая их во внеочередное состояние, определяемое ранее записанной в ячейках памяти 49 блока 21 информацией. Дешифратор 44 распределяет импульсы по элементам постоянной памяти 45 (например, серии ПЗУ 155РЕ3), где записывается программа работы всего устройства. Подробнее схема счетчика из триггеров 43 представлена на фиг.9, где индексом 46 обозначены счетные триггеры с установочными R- и S-входами. Структура блока прерывания 21 представлена ниже.

Отметим, что каждая переменная (сигнал) из всех рассматриваемых нами может принимать значение либо логического "0", либо логической "1".

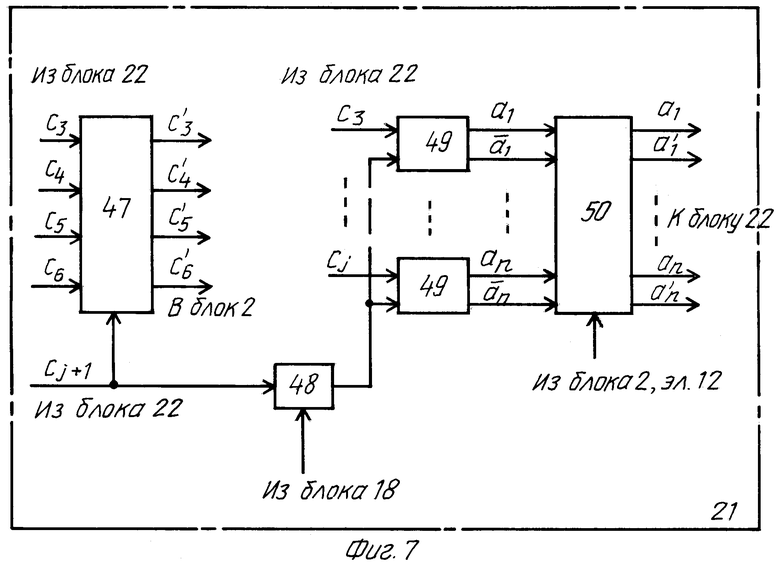

Блок прерывания известной конструкции 21 (фиг.7) содержит первый электронный ключ 47, на управляющий вход которого поступает сигнал Сj+1 с выхода блока программ 22, на информационные входы ключа 47 поступают сигналы С3, С4, С5, С6 из блока 22, а с выходов ключа 47 передаются сигналы С'3, С'4, С'5, С'6, которые все равны логическим "0" при Сj+1=1 независимо от значений С3, С4, С5, С6, двухвходовой элемент И 48, на первый вход которого поступает импульс со второго выхода блока синхронизации 18, а на второй вход элемента И 48 - сигнал Сj+1 из блока 22, ряд ячеек памяти 49 с прямыми и инверсными выходами, на управляющие входы которых поступает сигнал с выхода элемента И 48, на информационные входы ячеек памяти 49 приходят сигналы С3...Сj с выхода блока 22, которые записываются туда по единичному сигналу с выхода элемента И 48, второй электронный ключ 50, на входы которого поступают сигналы с прямых и инверсных выходов ячеек памяти 49, а с выходов ключа 50 поступают сигналы а1, а'1. ..аn, а'n, которые все равны логическим "1", когда сигнал приходящий на управляющий вход электронного ключа 50 с выхода элемента 12 блока 2 равен "0", когда же этот сигнал равен "1", то на выходе ключа 50 имеются сигналы а1, а'1...аn, а'n, повторяющие значения сигналов с выходов ячеек памяти 49. Взаимодействие элементов блока 21 и элементов блока 22 раскрыто выше, при описании структуры блока 22. Подробнее работа блока прерывания описана в работе [2].

Работу предлагаемого устройства покажем на примере определения суммы положительного числа А1=+0,101, заданного прямым кодом, и отрицательного числа А2= -0,010, преобразованного в дополнительный код А'2=1,110, который, как известно, получается прибавлением единицы к младшему разряду обратного (инверсного) значения числа А2, и знаковый единичный разряд перед запятой указывает, что данное число отрицательно. В представленных числах правые разряды младшие.

Числа А1 и А2 в виде "0" и "1" имеются среди множества Х1...Хm-1 по соответствующим адресам C7...Сj. Оговоримся, что значение Хm всегда равно "1" и все ячейки памяти и триггеры сброшены в "0" перед работой.

Условимся, что при C'3= 1, C'4=0, C'5=0 активизируется первый в соответствии с описанием выход дешифратора 3, при C'3=0, C'4=1, C'5=0 активизируется пятый выход, при C'3=1, C'4=1, C'5=0 активизируется второй выход, при C'3= 0, C'4= 0, C'5=1 активизируется третий выход, а при C'3=1, C'4=0, C'5=1 активизируется четвертый выход.

Запись в ячейку 14 и сброс в "0" триггера 13 происходит соответственно во второй и четвертой четвертях такта по командам К1 и К2 при активизации третьего или четвертого выхода дешифратора 3 блока 2, т.е. при записи информации в блок 19 или в блок 20 из блока 2.

В блоке 21 при Сj+1=0 на выходе ключа 47 сигналы C'3, C'4, C'5 и C'6 повторяют значения сигналов С3, С4, С5, С6 на входах ключа 47.

Суммирование чисел А1 и А2 происходит следующим образом. Поразрядно, начиная с младшего разряда, определяются результат суммы этих разрядов путем вычисления функции ИСКЛЮЧАЮЩЕЕ ИЛИ и значение переноса, которое автоматически определяется триггером 13. При этом в этом процессе число А2 преобразуется в дополнительный код. На следующем такте результат суммы записывается в ячейку памяти с адресом C7...Сj в блок 19 или в блок 20, а значение переноса записывается во вторую ячейку памяти 14, откуда считывается при вычислении суммы следующего разряда. Ниже рассмотрим подробнее этот процесс.

На первом такте под действием команд С1=0, Сj+1=0, C2=0, С'6=1, C'3=1, С'4=0, С'5=0 из блока 1 с адресом C7...Сj на вход управления ячейки памяти 7 через элементы 4, 5 и 6 поступит значение младшего разряда числа А1 и состояние ячейки памяти 7 изменится на противоположное (единичное), т.к. при С'6= 1 ячейка 7 работает как счетный триггер. При этом состояние триггера 13 не изменится.

На втором такте младший разряд числа А2 по адресу С7...Сj с учетом команд С1= 1, С2=0, C'3=1, С'4=0, С'5=0, С'6=1 и Сj+1=0 поступит с выхода элемента 4 на вход элемента 5 блока 2, где инвертируется (для перевода А2 в дополнительный код) и через элемент 6 попадет на управляющий вход ячейки памяти 7, которая поменяет свое состояние на "0" и переведет триггер 13 в единичное состояние, зафиксировав, что перенос равен "1".

На третьем такте для завершения перевода числа А2 в дополнительный код логическая единица Хm по адресу С7...Сj с учетом команд С1=0, С2=0, Cj+1=0, С'3= 1, С'5=0, С'4= 0, C'6=1 через элементы 4, 5, 6 поступит на управляющий вход ячейки 7 и состояние ячейки 7 изменится с "0" на "1", что является результатом суммы младших разрядов чисел А1 и А2.

Этот результат на четвертом такте под действием команд С1=1, С2=0, С'3= 1, С'4= 0, C'5= 1, С'6=0, Сj+1=0 за счет активизации четвертого выхода дешифратора 3 блока 2 и импульса во второй четверти такта, поступающего со второго выхода блока синхронизации 18, поступит на информационный вход блока 19 и запишется по адресу C7...Cj. Одновременно за счет сигнала К1, сформированного активизацией четвертого выхода дешифратора 3, единичным выходом элемента ИЛИ 16 и импульсом с выхода элемента И 15, произойдет запись информации с выхода триггера 13 в ячейку памяти 14. В третьей четверти такта произойдет запись логического нуля с выхода элемента ИЛИ 8 в ячейку памяти 7. В четвертой четверти того же такта триггер 13 сбросится в "0" по команде К2, сформированной на выходе элемента И 17.

На пятом такте по командам, аналогичным первому такту и в соответствии с описанным для первого такта процессом, при С7...Сj, определяющих адрес нового операнда, второй после младшего разряд числа А1 через элементы 4, 5, 6 поступит на вход управления ячейки памяти 7 и, т.к. он равен "0", состояние ячейки 7 не изменится.

На шестом такте под действием тех же команд, что и на втором такте, значение второго разряда числа А2 с адресом С7...Сj после инверсии в элементе 5 блока 2 через элемент 6 поступит на управляющий вход ячейки 7 и, являясь логическим "0", не изменит состояние ячейки 7 и, значит, триггера 13.

На седьмом такте под действием команд C1=0, С2=0, С'3=0, C'4=1, С'5=0, С'6= 1, Сj+1=0 активизируется пятый выход дешифратора 3 и значение переноса, равное "1", с выхода второй ячейки памяти 14 появится на выходе элемента 4 и через элементы 5 и 6 поступит на управляющий вход ячейки памяти 7, эта ячейка памяти поменяет свое состояние на единичное, а триггер 13 останется в прежнем состоянии.

Результат суммы вторых разрядов чисел А1 и А2, а также переноса от суммы предыдущих разрядов в соответствии с командами и процессами, описанными выше для четвертого такта, запишется в ячейку памяти с адресом С7...Сj в блок 19 на восьмом такте. На этом же такте в соответствии с командами и процессами, описанными для четвертого такта, произойдет запись значения переноса с выхода триггера 13 в ячейку памяти 14, во второй четверти такта, далее в третьей четверти такта в ячейку памяти 7 запишется "0", а в четвертой четверти такта триггер 13 сбросится в "0".

На девятом, десятом и одиннадцатом тактах произойдет сложение третьих разрядов чисел A1, A2 и переноса от сложения предыдущих разрядов по правилам и командам, приведенным выше, соответственно для первого, второго и седьмого тактов. На двенадцатом такте результаты сложения в виде "0" и переноса в виде "1" в соответствии с правилами и командами для четвертого такта запишутся соответственно с выхода ячейки 7 в блок 19 по адресу С7...Сj и с выхода триггера 13 в ячейку 14, а затем произойдет запись нуля в ячейку 7 и сброс триггера 13 в нуль.

На 13, 14 и 15 тактах произойдет сложение аналогично процессам соответственно на 1, 2 и 7 тактах знаковых разрядов (до запятой) чисел А1, A2 с соответствующими адресами С7. . . Сj и переноса из ячейки 14, в результате значение указанной суммы в виде "0" находится в ячейке 7. На 16 такте информация из ячейки 7 запишется в блок 19 известным способом, описанным для четвертого такта.

Таким образом, в блоке 19 имеется результат вычисления суммы двух чисел А1 и A2, который равен 0,011. Запятая в данном случае стоит условно, т.к. можно считать, что знаковый разряд есть старший разряд, и если он равен "0", как в нашем случае, то полученная сумма положительна, если бы он равнялся "1", то полученная сумма была бы отрицательна и задана дополнительным кодом, который преобразуется в прямой код так же, как прямой в дополнительный.

Получается, что на каждый разряд полученного результата с учетом считывания операндов из блока 1 или 20 (при активизации третьего выхода дешифратора 3), определения результатов суммы и переноса, а также записи результатов соответственно в блок 19 или блок 20 (при активизации второго выхода дешифратора 3) и ячейку памяти 14 требуется четыре такта в предлагаемом устройстве. В прототипе определение переноса при каждом поразрядном суммировании потребовало бы дополнительные такты. Например, чтобы определить значение переноса от сложения трех однобитовых операндов, в прототипе требуется вначале определить конъюнкцию от каждой пары операндов из трех имеющихся, а затем три полученных результата логически сложить, т.е. реализовать функцию ИЛИ, и если функция равна "1", то перенос равен "1" или "0" в" противном случае, что потребует 11 тактов работы устройства, взятого за прототип, и четыре такта необходимы на реализацию функции ИСКЛЮЧАЮЩЕЕ ИЛИ для трех операндов и записи результата, например, в блок 19, т.е. всего 15 тактов. Это почти в четыре раза больше, чем в предлагаемом устройстве.

Технико-экономический эффект от предлагаемого изобретения заключается в том, что за счет сокращения числа рабочих тактов при реализации логических операций в процессе алгебраического суммирования двух двоичных чисел имеет место:

- повышение быстродействия системы управления при определении величины рассогласования заданных режимов от реально протекающих процессов в технологических линиях, что сокращает время реакции системы управления на изменение режимов работы от установленных и повышает точность поддержания технологических режимов,

- снижает объем ПЗУ в программном блоке и трудоемкость процесса программирования.

Источники информации

1. Патент на изобретение 2134442 от 10.08.1999.

2. Патент на изобретение 2154852 от 20.08.2000.

Изобретение относится к средствам управления и может применяться при автоматизации в технологических процессах и в производстве. Технический результат заключается в повышении быстродействия и упрощении процесса программирования. Устройство содержит входной блок, блок оперативной памяти, блок синхронизации, блок программ, блок прерывания, коммутационно-вычислительный блок (КВБ), причем в КВБ введены вторая ячейка памяти, счетный триггер, пятый и шестой элементы И, второй элемент ИЛИ, а элемент И-ИЛИ выполнен в виде элемента 2-2-2И-3ИЛИ и дешифратор снабжен пятым выходом. 9 ил.

Программируемое устройство для управления электроприводами, электронными ключами и сигнализацией, содержащее входной блок, блок оперативной памяти, блок синхронизации, блок программ, блок прерывания, коммутационно-вычислительный блок, содержащий дешифратор, логический элемент И-ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй, третий и четвертый элементы И, элемент ИЛИ, элемент НЕ и первую ячейку памяти, при этом первые входы логического элемента И-ИЛИ соединены соответственно с первым и вторыми выходами дешифратора, а вторые входы подключены соответственно к выходу входного блока, соединенного первой и второй группами входов соответственно с группой информационных выходов объекта управления и с адресными шинами блока программ, и к выходу блока оперативной памяти, выход логического элемента И-ИЛИ подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с соответствующим выходом блока программ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом первого элемента И, подключенного вторым входом к первому выходу блока синхронизации, соединенного вторым выходом с блоком прерывания, с первыми управляющими входами блока оперативной памяти и выходного блока, группы входов которых соединены с группой адресных шин блока программ, а информационные входы объединены и связаны с прямым выходом первой ячейки памяти, третий выход блока синхронизации соединен со счетным входом блока программ, третий и четвертый выходы дешифратора связаны соответственно со вторыми управляющими входами блока оперативной памяти и выходного блока, управляющий вход первой ячейки памяти соединен с выходом первого элемента И, ее информационный вход связан с выходом элемента ИЛИ, первый вход которого соединен с выходом второго элемента И, входы которого связаны с выходом элемента НЕ и с выходом программного блока, вход элемента НЕ подключен к выходу блока прерывания, второму входу третьего элемента И и первому входу четвертого элемента И, второй вход которого соединен с инверсным выходом первой ячейки памяти, а выход со вторым входом элемента ИЛИ, прямой выход первой ячейки памяти связан с третьим входом третьего элемента И, выходы выходного блока соединены с электроприводами, электронными ключами и сигнализацией, четвертый вход третьего элемента И подключен к третьему выходу блока синхронизации, а выход третьего элемента И соединен с соответствующим входом блока прерывания, соединенного входами с определенными выходами блока программ, входы дешифратора соединены с выходами блока прерывания, отличающееся тем, что в коммутационно-вычислительный блок введены счетный триггер, вторая ячейка памяти, пятый и шестой элементы И, второй элемент ИЛИ, при этом элемент И-ИЛИ выполнен в виде элемента 2-2-2И-3ИЛИ, а дешифратор снабжен пятым выходом, соответствующий вход элемента 2-2-2И-3ИЛИ подключен к пятому выходу дешифратора, прямой выход первой ячейки памяти связан со счетным входом счетного триггера, вход сброса в нуль которого соединен с выходом пятого элемента И, а выход подключен к информационному входу второй ячейки памяти, ее управляющий вход соединен с выходом шестого элемента И, а выход - с элементом 2-2-2И-3ИЛИ, первые входы пятого и шестого элементов И соединены с третьим и вторым выходами блока синхронизации, а вторые входы пятого и шестого элементов И объединены с выходом второго элемента ИЛИ, входы которого подключены к третьему и четвертому выходам дешифратора.

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1999 |

|

RU2154852C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1997 |

|

RU2134442C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1996 |

|

RU2106676C1 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ И СИГНАЛИЗАЦИЕЙ | 1996 |

|

RU2117978C1 |

| DE 2846686 B1, 27.09.1979. | |||

Авторы

Даты

2003-02-27—Публикация

2001-07-03—Подача