113056622

Изобретение относится к вычисли-операнда, образуя узел МОНТАЖНОЕ ИЛИ,

тельной технике, может быть использо-выход которого подключен к входу ревано при построении арифметическихгистра 1, а вторая группа выходов соеустройств ЭВМ и специализированныхдинена с входом второго операнда и

векторно-матричных вьгаислителей и яв- выходом сумматора 7, образуя также

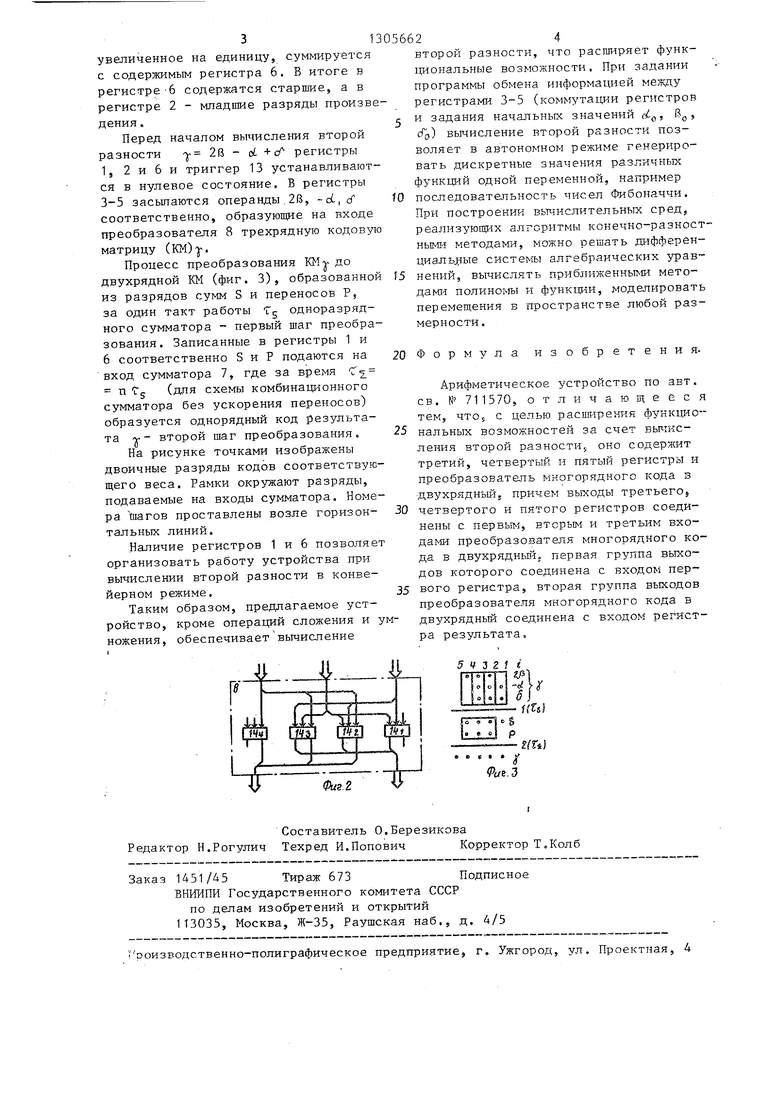

ляется усовершенствованием устройст-узел МОНТАЖНОЕ ИЛИ. ва по авт. св. № 711570.В пределах преобразователя 8 шина

Цель изобретения - расширение фун-i-ro разряда первого- входа (i 1,...,

кциональных возможностей устройствап) соединена с первым входом (i+1)за счет обеспечения вычисления второй fOго сумматора 14, шина i-ro разряда

разности.второго и третьего входов - с вторым

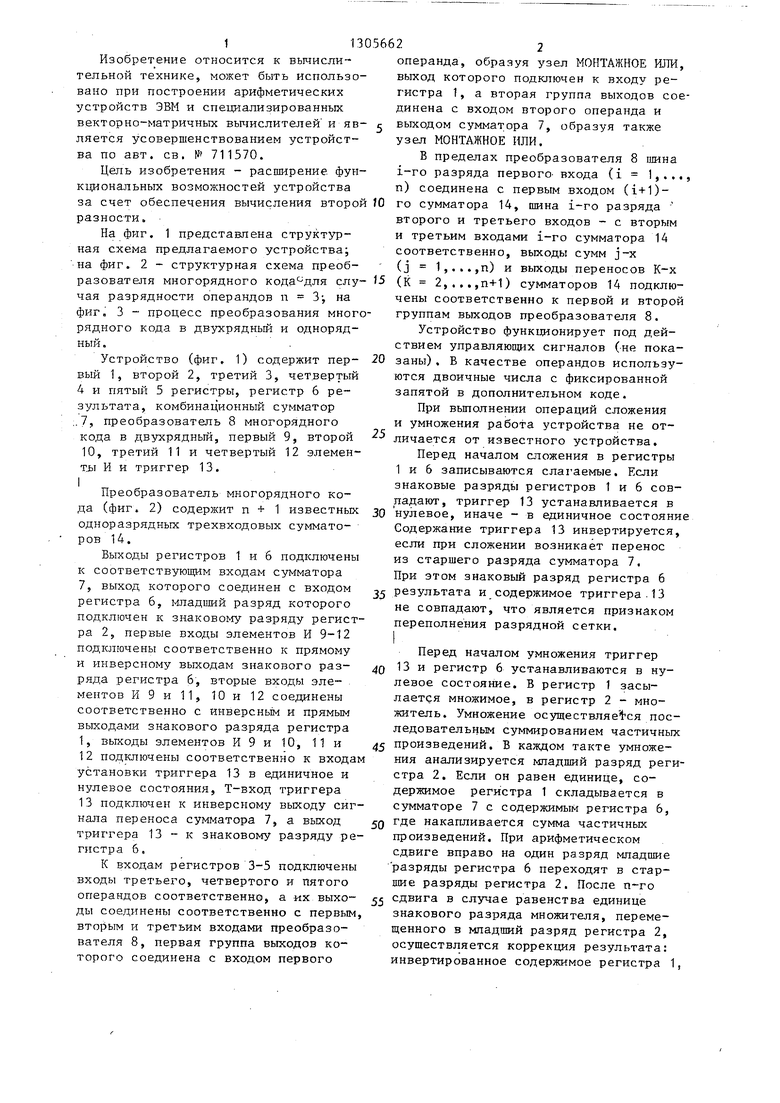

На фиг. 1 представлена структур-и третьим входами i-ro сумматора 14 ная схема предлагаемого устройства;соответственно, выходы сумм j-x на фиг. 2 - структурная схема преоб- -(j 1,...,п) и выходы переносов К-х разователя многорядного кода - для слу- 15(к 2п+1) сумматоров 14 подключая разрядности операндов п 3-, начены соответственно к первой и второй фиг, 3 - процесс преобразования много-группам выходов преобразователя 8. рядного кода в двухрядный и одноряд- Устройство функционирует под дей- ный. ствием управляющих сигналов Сне пока- Устройство (фиг. 1) содержит пер- 20заны). В качестве операндов использу- вый 1, второй 2, третий 3, четвертыйются двоичные числа с фиксированной 4 и пятый 5 регистры, регистр 6 результата, комбинационный сумматор :.7, преобразователь 8 многорядного

кода в двухрядный, первый 9, второй

10, третий 11 и четвертый 12 элеменTii И и триггер 13.

25

запятой в дополнительном коде.

При выполнении операций сложения и умножения работа устройства не отличается от известного устройства.

Перед началом сложения в регистры 1 и 6 записываются слагаемые. Если знаковые разряды регистров 1 и 6 совI

Преобразователь многорядного коПеред началом сложения в регистры 1 и 6 записываются слагаемые. Если знаковые разряды регистров 1 и 6 совпадают, триггер 13 устанавливается в да (фиг. 2) содержит п + 1 известных ЗО нулевое, иначе - в единичное состояние

Содержание триггера 13 инвертируется, если при сложении возникает перенос из старшего разряда сумматора 7. При этом знаковый разряд регистра 6 5 результата и содержимое триггера. 13 не совпадают, что является признаком

одноразрядных трехвходовых сумматоров 14.

Выходы регистров 1 и 6 подключены к соответствующим входам сумматора 7, выход которого соединен с входом регистра 6, 1 Шадший разряд которого подключен к знаковому разряду регистра 2, первые входы элементов И 9-12 подключены соответственно к прямому и инверсному выходам знакового разряда регистра 6, вторые входы элементов И 9 и 11, 10 и 12 соединены соответственно с инверсньтм и прямым вькодами знакового разряда регистра 1, выходы элементов И 9 и 10, 11 и 12 подключены соответственно к входам установки триггера 13 в единичное и нулевое состояния, Т-вход триггера

переполнения разрядной сетки.

Перед началом умножения триггер 4Q 13 и регистр 6 устанавливаются в нулевое состояние. В регистр 1 засылается множимое, в регистр 2 - множитель. Умножение осуществляемся последовательным суммированием частичных 45 произведений. В каждом такте умножения анализируется мпадший разряд регистра 2, Если он равен единице, содержимое регистра 1 складывается в 13 подключен к инверсному выходу сиг- сумматоре 7 с содержимым регистра 6, нала переноса сумматора 7, а выход ,50 накапливается сумма частичных триггера 13 - к знаковому разряду ре- произведений. При арифметическом

сдвиге вправо на один разряд младшие разряды регистра 6 переходят в старшие разряды регистра 2. После п-го операндов соответственно, а их выхо- 5 сдвига в случае равенства единице ды соединены соответственно с первым, знакового разряда множителя, перемещенного в мпадший разряд регистра 2, осуществляется коррекция результата: инвертированное содержимое регистра 1,

гистра 6.

К входам регистров 3-5 подключены входы третьего, четвертого и пятого

вторым и третьим входами преобразователя 8, первая группа выходов которого соединена с входом первого

и третьим входами i-ro сумматора 14 соответственно, выходы сумм j-x -(j 1,...,п) и выходы переносов К-х 15(к 2п+1) сумматоров 14 подключены соответственно к первой и второй группам выходов преобразователя 8. Устройство функционирует под дей- ствием управляющих сигналов Сне пока- 20заны). В качестве операндов использу- ются двоичные числа с фиксированной

25

запятой в дополнительном коде.

При выполнении операций сложения и умножения работа устройства не отличается от известного устройства.

Перед началом сложения в регистры 1 и 6 записываются слагаемые. Если знаковые разряды регистров 1 и 6 совпереполнения разрядной сетки.

увеличенное на единицу, суммируется с содержимым регистра 6. В итоге в регистре-6 содержатся старшие а в регистре 2 - младшие разряды произведения.

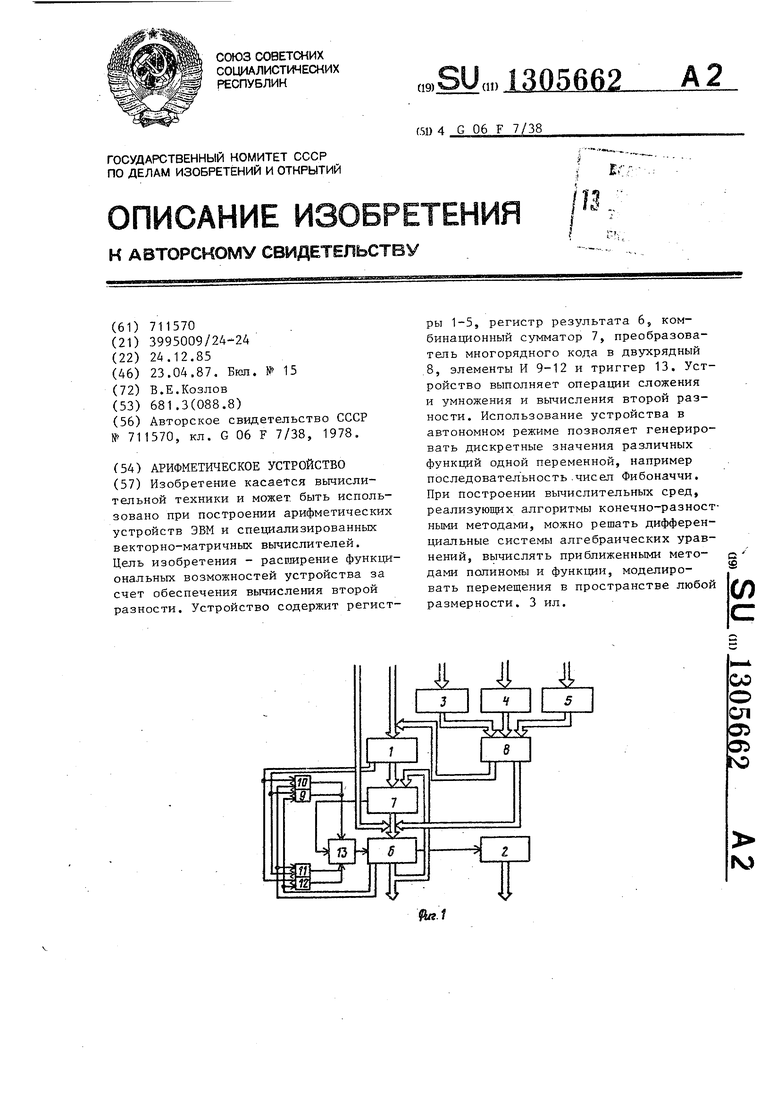

Перед началом вычисления второй разности j- 2R - d + tf регистры 1, 2 и 6 и триггер 13 устанавливаются в нулевое состояние. В регистры 3-5 засылаются операнды. 2В, -оС, сГ соответственно, образующие на входе преобразователя 8 трехрядную кодовую матрицу (KM) j-.

Процесс преобразования KMv до двухрядной КМ (фиг. 3), образованной из разрядов сумм S и переносов Р, за один такт работы Tg одноразрядного сумматора - первый шаг преобразования. Записанные в регистры 1 и 6 соответственно S и Р подаются на

вход сумматора 7, где за время п Tj (для схемы комбинационного сумматора без ускорения переносов) образуется однорядный код результата -v-- второй шаг преобразования.

На рисунке точками изображены двоичные разряды кодов соответствующего веса. Рамки окружают разряды, подаваемые на входы сумматора. Номера шагов проставлены возле горизонтальных линий.

Наличие регистров 1 и 6 позволяет организовать работу устройства при вычислении второй разности в конвейерном режиме.

Таким образом, предлагаемое устройство, кроме операций сложения и уножения, обеспечивает вычисление

второй разности, что расширяет функ- 1щональные возможности. При задании программы обмена информацией между регистрами 3-5 (коммутации регистров и задания начальных значений d, В,, сГ) вьиисление второй разности позволяет в автономном режиме генерировать дискретные значения различных функций одной переменной, например последовательность чисел Фибоначчи. При построении вычислительных сред, реализующих алгоритмы конечно-разностными методами, можно решать дифферен- циаль:ные системы алгебраических уравнений, вычислять приближенными методами полино1)ы и фз нкщаИ, моделировать перемещения в пространстве любой размерности.

5

20 Фор мула изобретенияАрифметическое устройство по авт. ев, №711570, отличающееся тем, что, с целью расширения фуккциональных возможностей за счет вычисления второй разности,,, оно содержит третий, четвертый и пятый регистры и преобразователь многорядного кода з двухрядный, причем выходы третьего

четвертого и пятого регистров соединены с первьм, вторым и третьим входами преобразователя многорядного кода в двухрядньш. первая группа выхо дов которого соединена с входом пер

вого регистра, вторая группа выходов преобразователя многорядного кода в двухрядньи соединена с входом регистра результата.

Составитель О.Березикова Редактор Н.Рогулич Техред И.ПоповичКорректор Т.Колб

Заказ 1451/45Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий П3035, Москва, Ж-35, Раушская наб., д. 4/5

ооизводственно-полиграфическое предприятие, г, Ужгород, ул, Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Конвейерное устройство для одновременного выполнения арифметических операций над множеством чисел | 1977 |

|

SU922726A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU451078A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

Изобретение касается вычислительной техники и может, быть использовано при построении арифметических устройств ЭВМ и специализированных векторно-матричных вычислителей. Цель изобретения - распшрение функциональных возможностей устройства за счет обеспечения вычисления второй разности. Устройство содержит регистры 1-5, регистр результата 6, комбинационный сумматор 7, преобразователь многорядного кода в двухрядный 8, элементы И 9-12 и триггер 13. Устройство выполняет операции сложения и умножения и вычисления второй разности. Использование устройства в автономном режиме позволяет генерировать дискретные значения различных функций одной переменной, например последовательность .чисел Фибоначчи, При Построении вычислительных сред, реализующих алгоритмы конечно-разностными методами, можно решать дифференциальные системы алгебраических уравнений, вычислять приближенными методами полиномы и функции, моделировать перемещения в пространстве любой размерности. 3 ил. i (Л со о Ol О5 О5 ю SO

| Арифметическое устройство | 1978 |

|

SU711570A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-12-24—Подача