Устройство относится к вычислительной технике и может найти применение в вычислительных системах для сопряжения двух и нескольких ЦВМ с различным представлением данных.

Целью изобретения является повышение эффективности диагностики неисправностей путем автоматизации поиска неисправности, увеличения глубины контроля и его разрешающей способности.

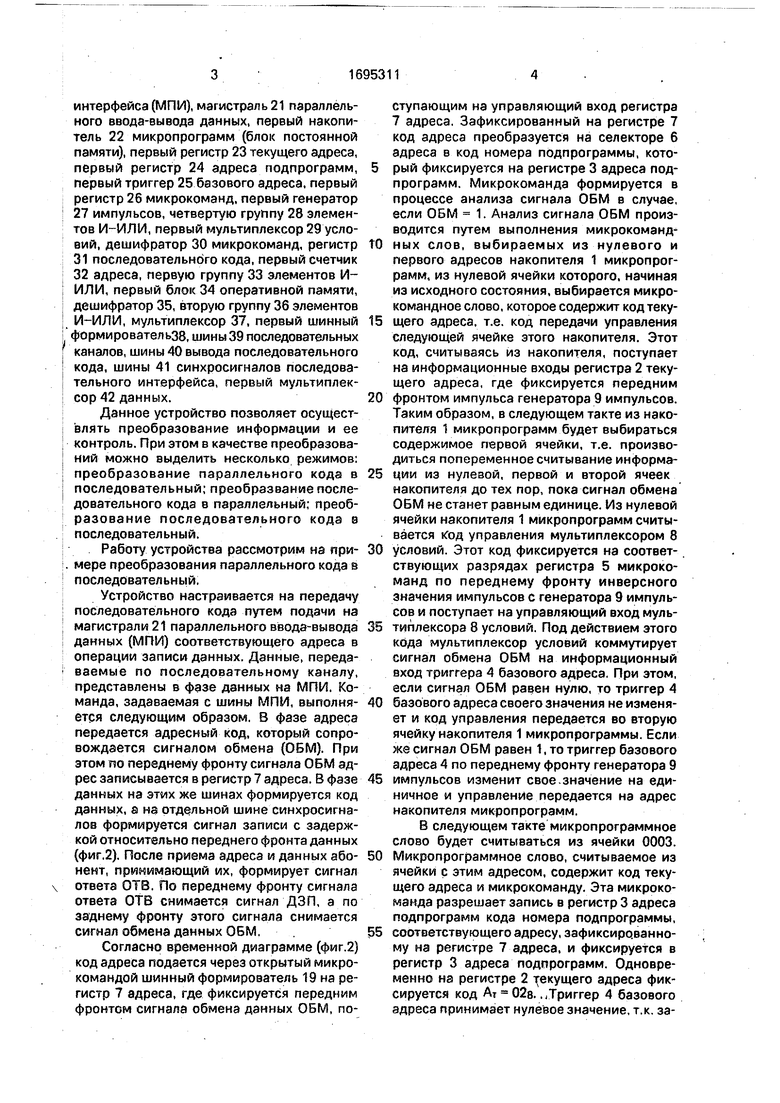

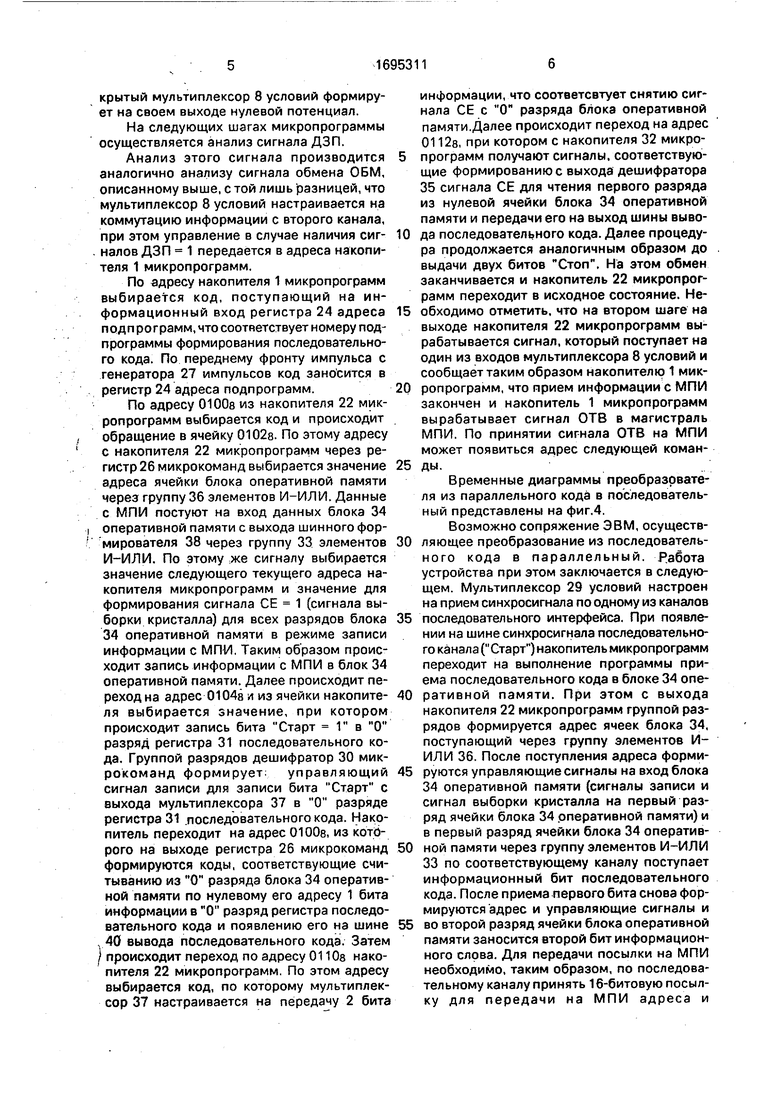

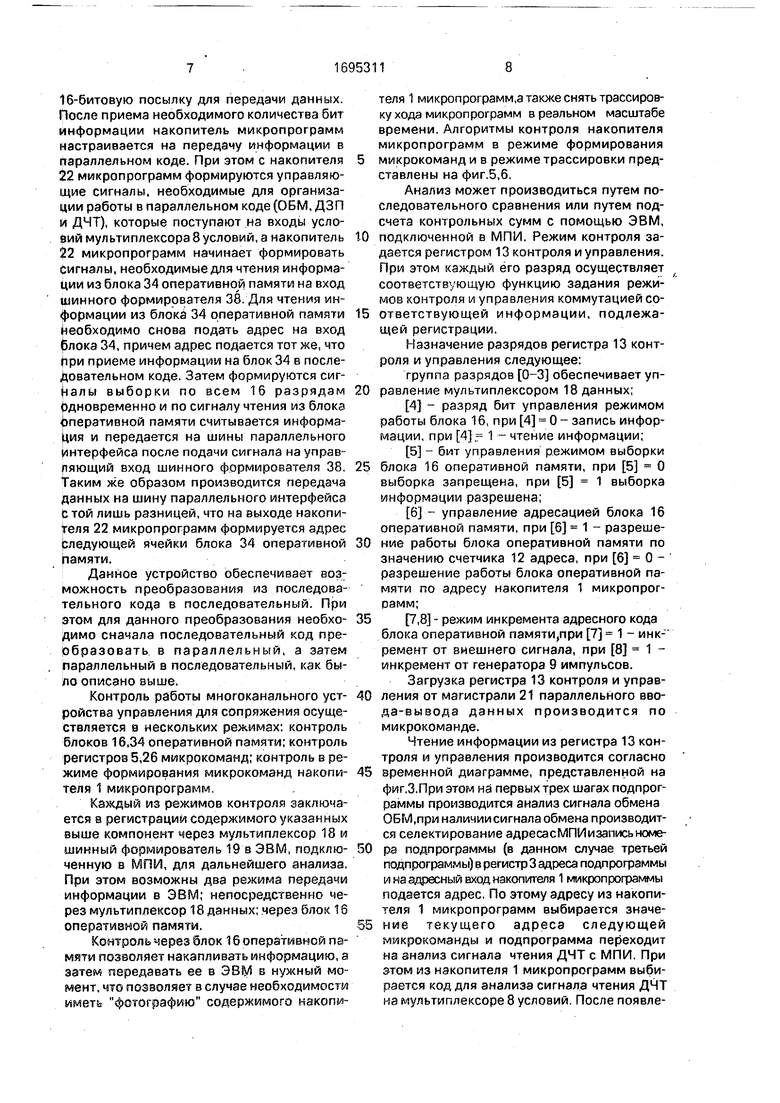

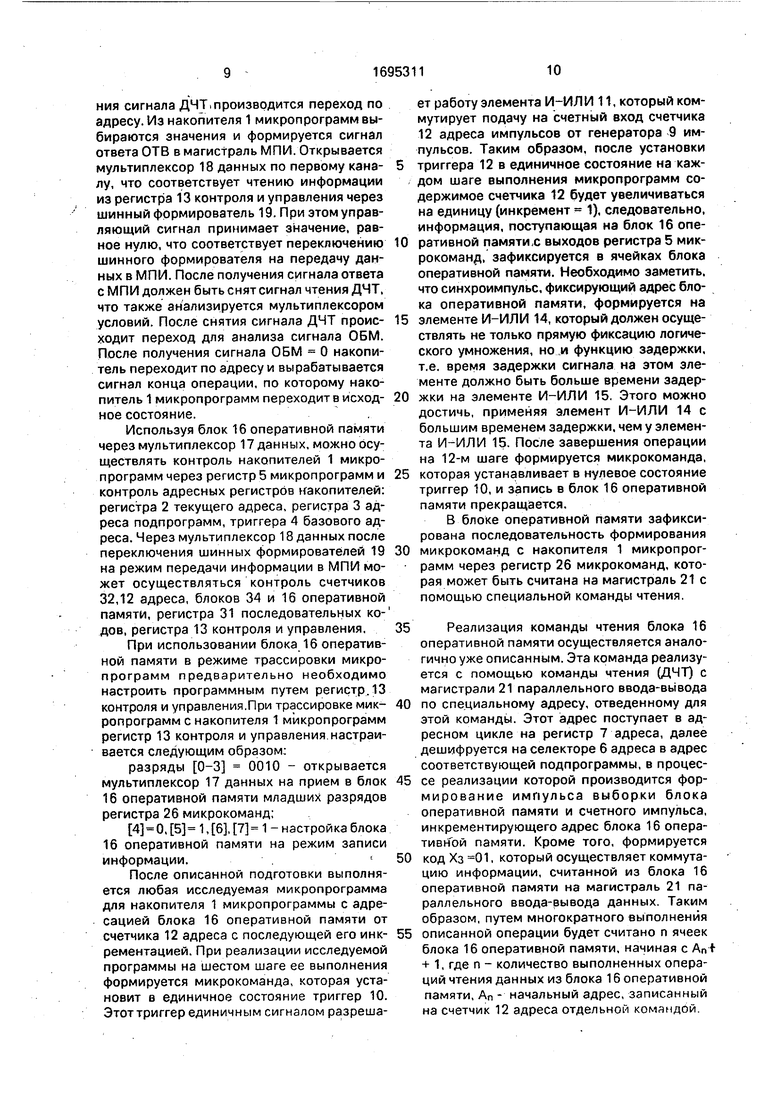

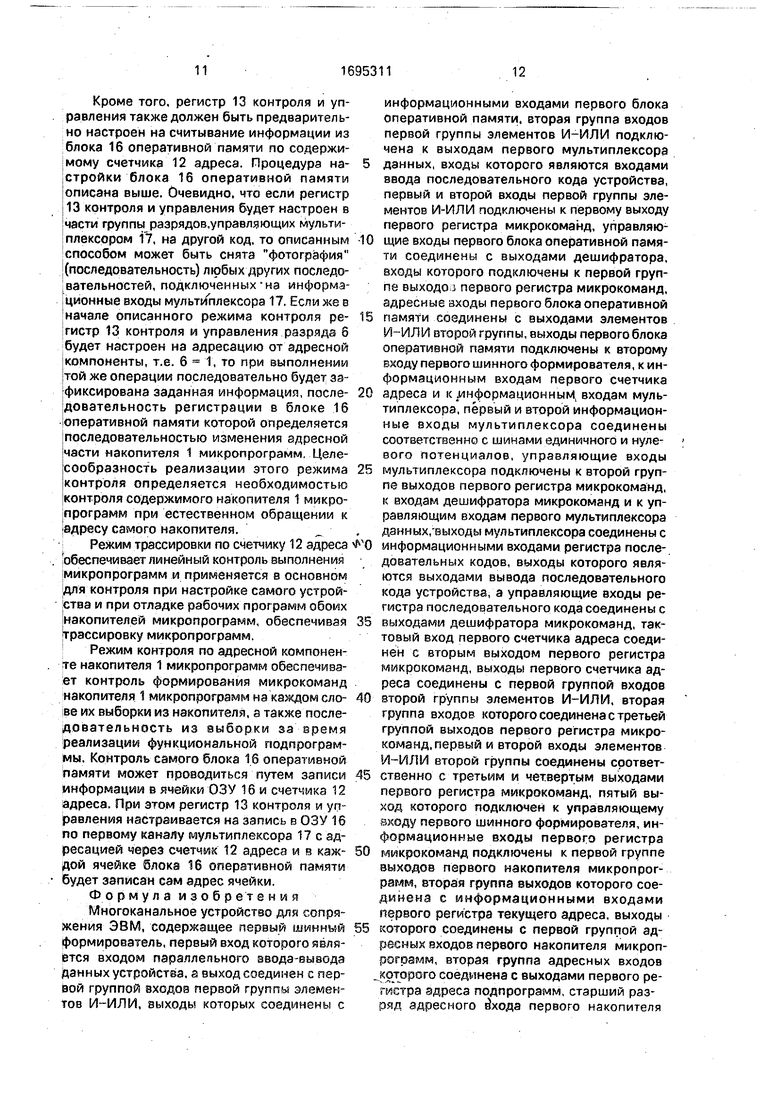

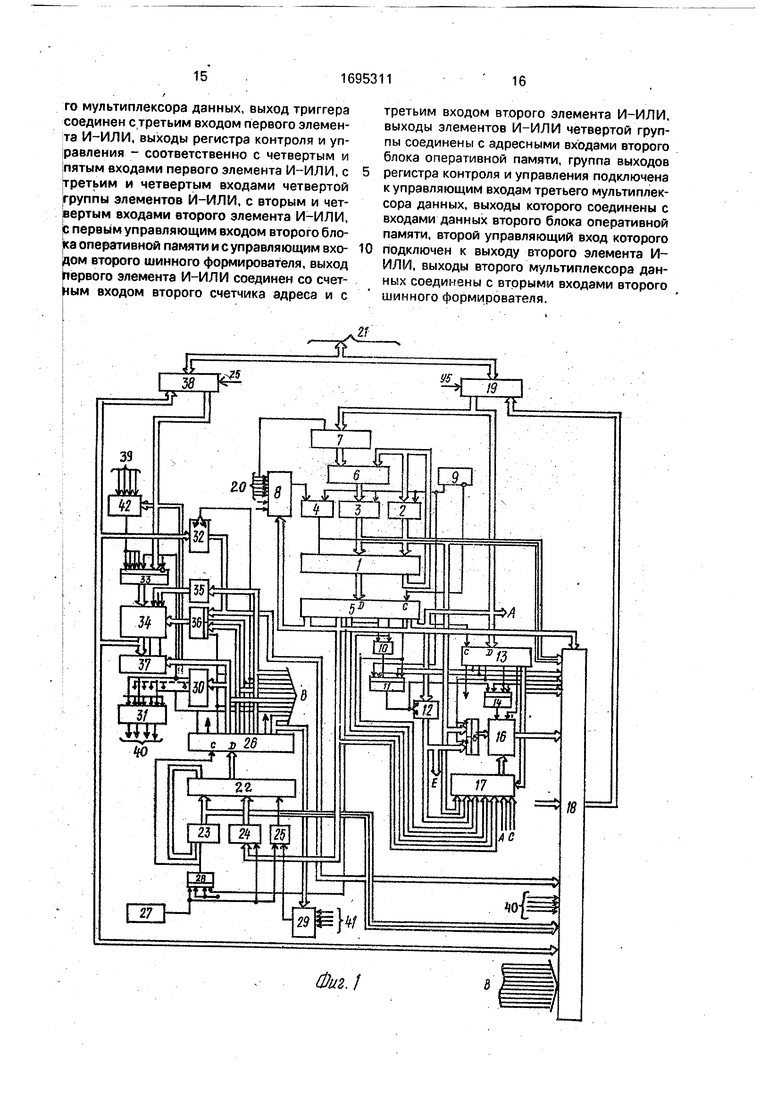

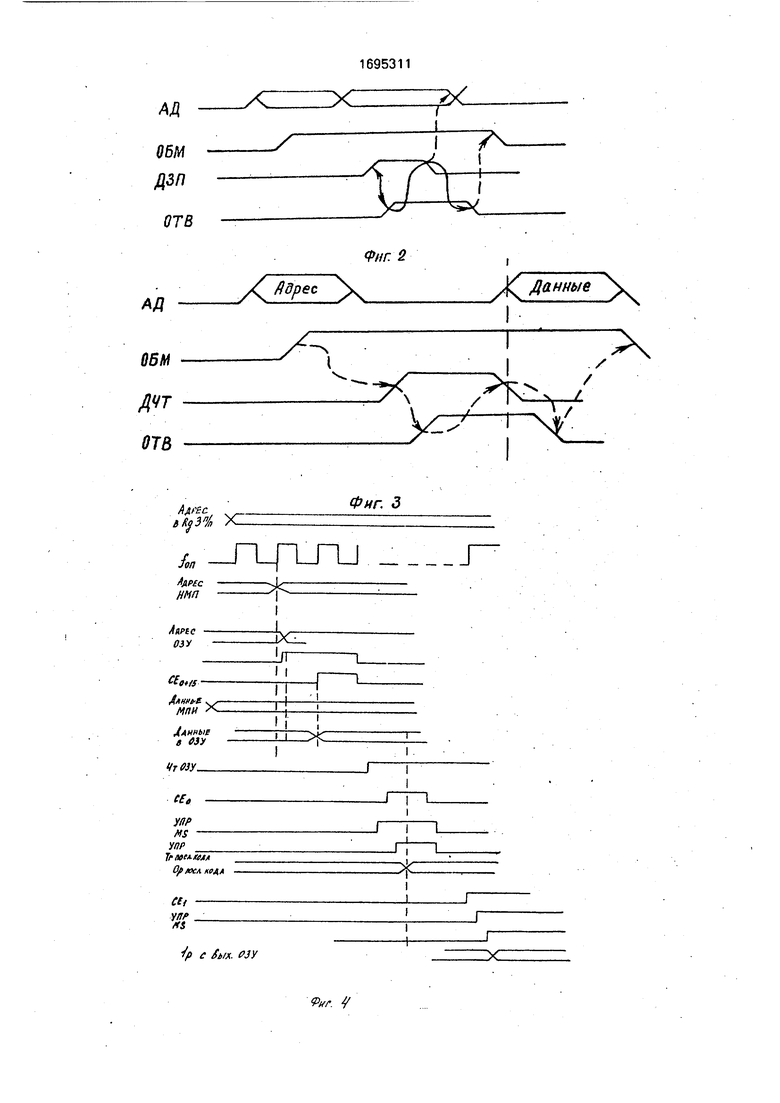

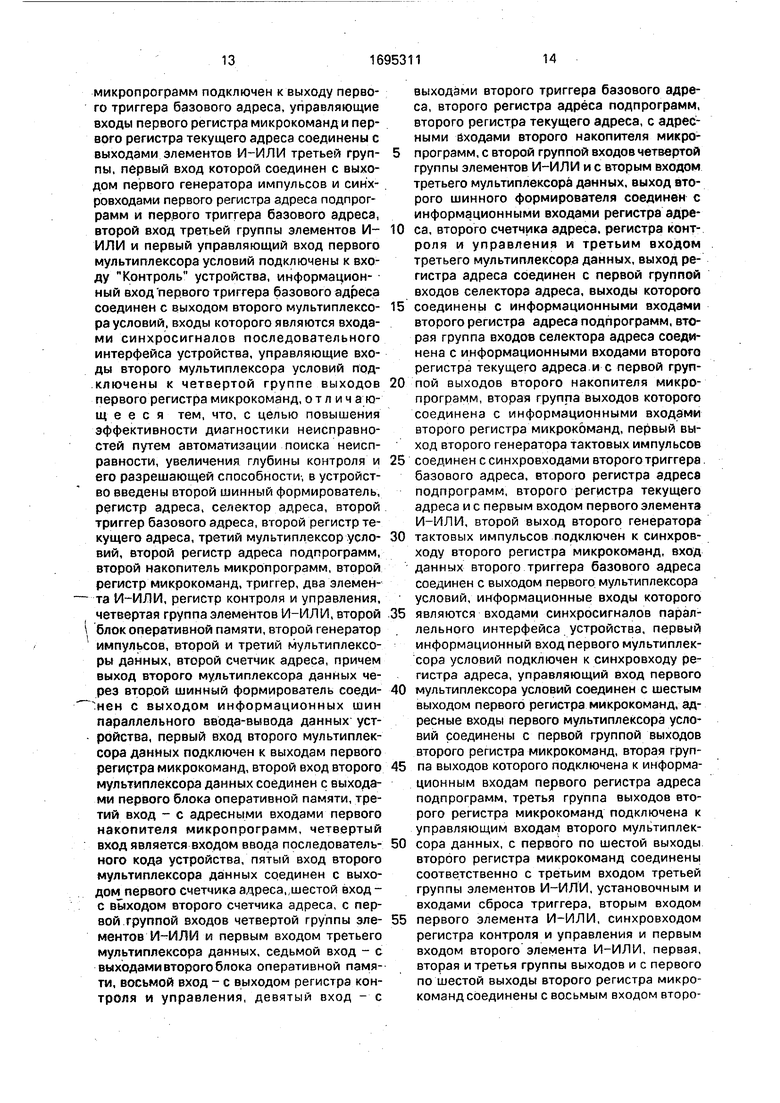

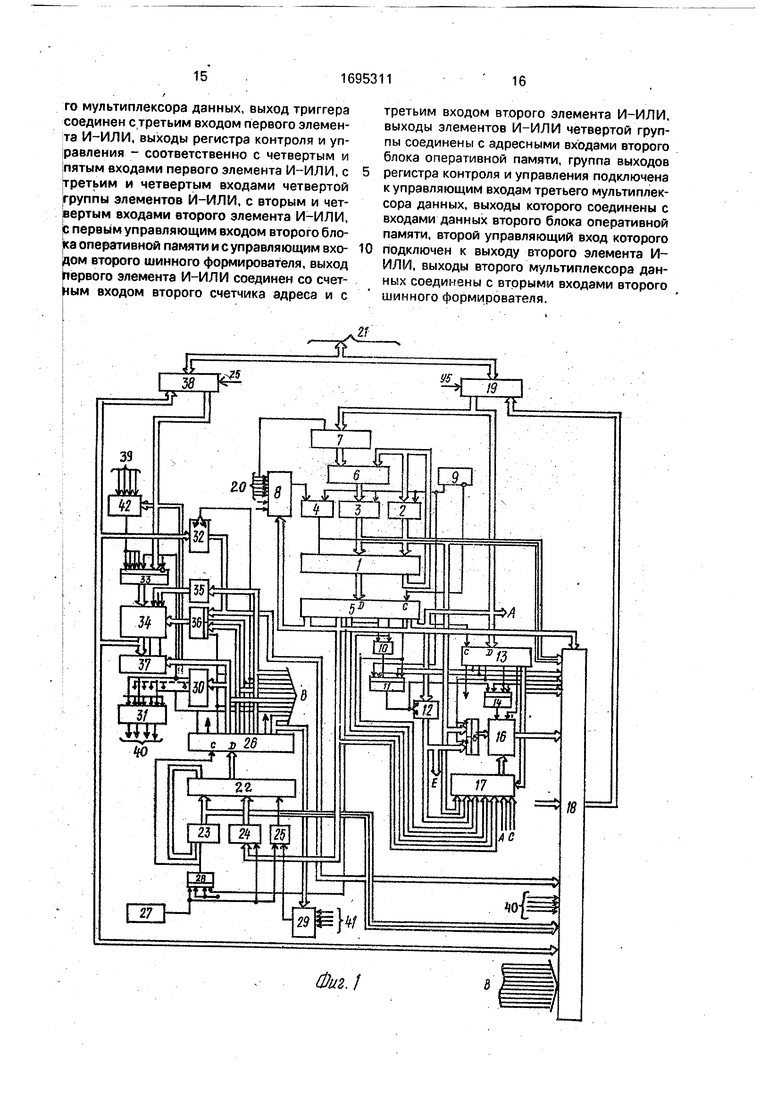

На фиг.1 представлена функциональная схема устройства; на фиг.2 - временная диаграмма операции записи данных в любой программно-доступный элемент памяти; на фиг.З - временная диаграмма операции чтения данного любого программно-доступного функционального элемента; на фиг.4 - временная диаграмма чтения данных из

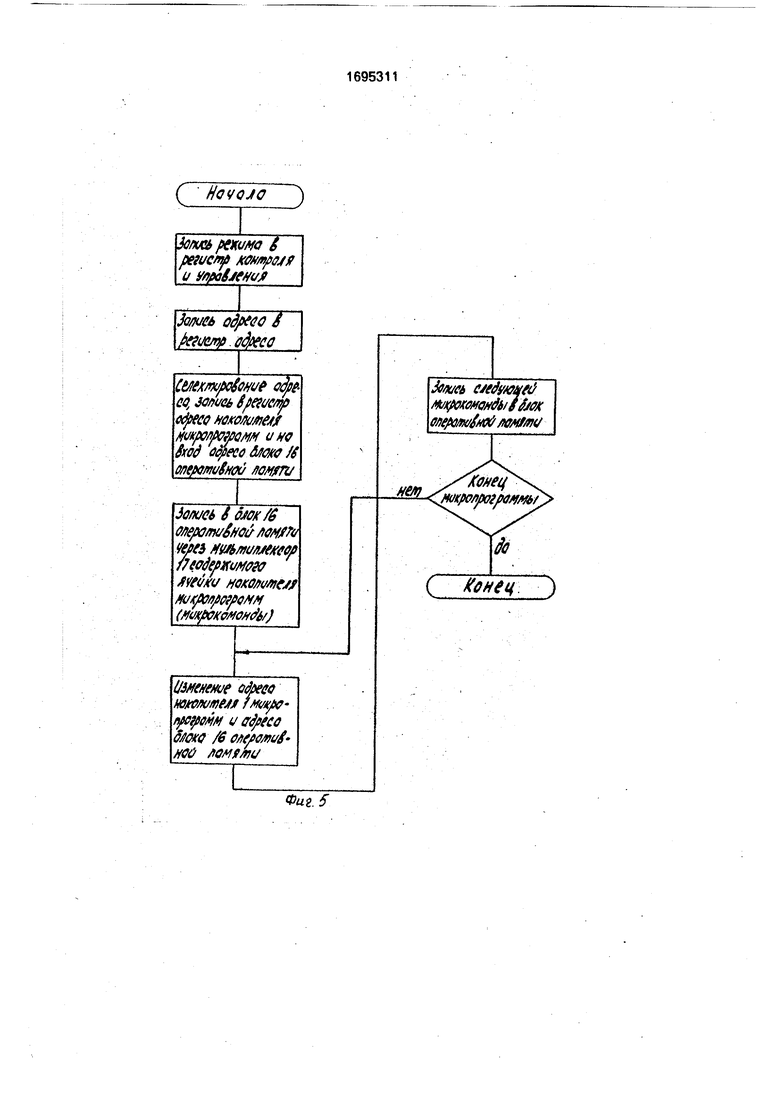

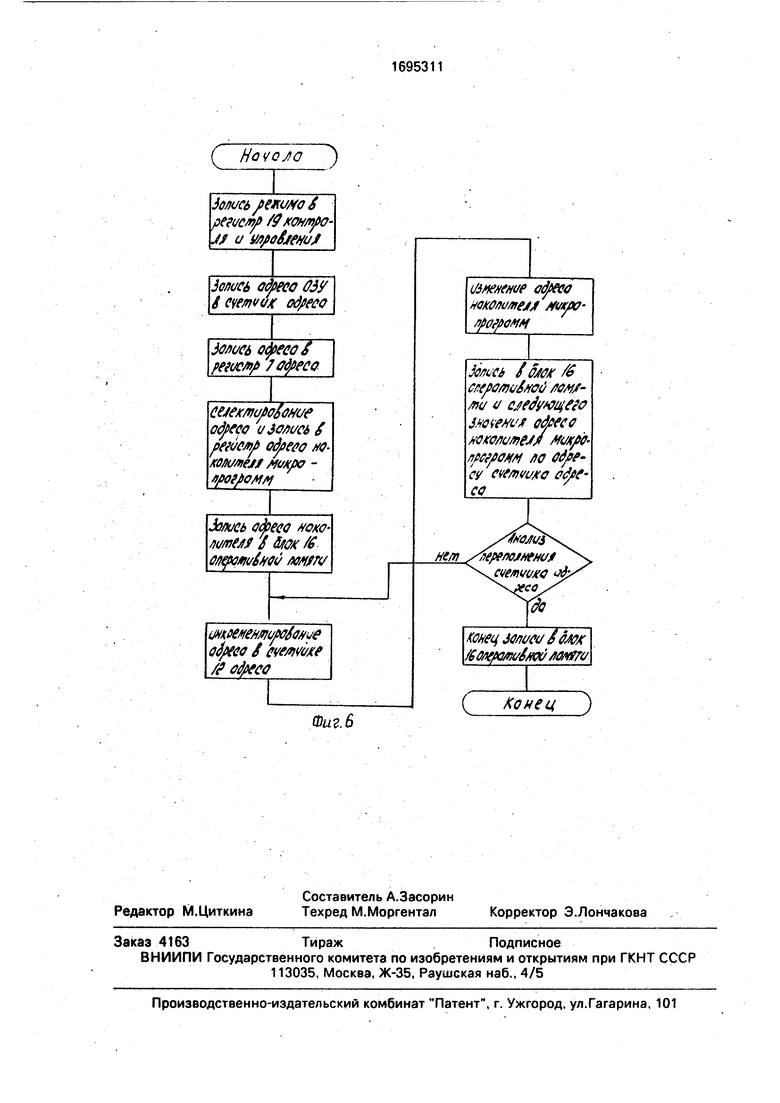

ОЗУ в последовательном коде; на фиг.5 и 6 - алгоритмы контроля устройства.

Многоканальное устройство для сопряжения ЭВМ содержит второй накопитель микропрограмм 1 (блок постоянной памяти), второй регистр 2 текущего адреса, второй регистр 3 адреса подпрограмм, второй триггер 4 базового адреса, второй регистр 5 микрокоманд, селектор 6 адреса, регистр 7 адреса, второй мультиплексор 8 условий, второй генератор 9 тактовых импульсов, триггер 10, второй элемент И-ИЛИ 11, счетчик 12 адреса, регистр 13 контроля и управления, первый элемент И-ИЛИ 14, третью группу 15 элементов И-ИЛИ, второй блок 16 оперативной памяти, второй мультиплексор 17 данных, третий мультиплексор 18 данг ных, второй шинный формирователь 19. шины 20 синхросигналов параллельного

О

о

СП

00

}

интерфейса (МПИ), магистраль 21 параллельного ввода-вывода данных, первый накопитель 22 микропрограмм (блок постоянной памяти), первый регистр 23 текущего адреса, первый регистр 24 адреса подпрограмм, первый триггер 25 базового адреса, первый регистр 26 микрокоманд, первый генератор 27 импульсов, четвертую группу 28 элементов И-ИЛИ, первый мультиплексор 29 условий, дешифратор 30 микрокоманд, регистр

31последовательного кода, первый счетчик

32адреса, первую группу 33 элементов И- ИЛИ, первый блок 34 оперативной памяти, дешифратор 35, вторую группу 36 элементов

1 И-ИЛИ, мультиплексор 37, первый шинный формировательзв, шины 39 последовательных каналов, шины 40 вывода последовательного кода, шины 41 синхросигналов последовательного интерфейса, первый мультиплексор 42 данных.

Данное устройство позволяет осуществлять преобразование информации и ее контроль. При этом в качестве преобразований можно выделить несколько режимов: преобразование параллельного кода в последовательный; преобразвание последовательного кода в параллельный; преобразование последовательного кода в последовательный.

Работу устройства рассмотрим на при- . мере преобразования параллельного кода в последовательный.

Устройство настраивается на передачу последовательного кода путем подачи на магистрали 21 параллельного ввода-вывода данных (МПИ) соответствующего адреса в операции записи данных. Данные, переда- ваемые по последовательному каналу, представлены в фазе данных на МПИ. Команда, задаваемая с шины МПИ, выполняется следующим образом. В фазе адреса передается адресный код, который сопровождается сигналом обмена (ОБМ). При этом по переднему фронту сигнала ОБМ адрес записывается в регистр 7 адреса. В фазе данных на этих же шинах формируется код данных, а на отдельной шине синхросигналов формируется сигнал записи с задержкой относительно переднего фронта данных (фиг.2). После приема адреса и данных абонент, принимающий их, формирует сигнал ответа ОТВ. По переднему фронту сигнала ответа ОТВ снимается сигнал ДЗП, а по заднему фронту этого сигнала снимается сигнал обмена данных ОБМ.

Согласно временной диаграмме (фиг.2) код адреса подается через открытый микрокомандой шинный формирователь 19 на регистр 7 адреса, где фиксируется передним фронтом сигнала обмена данных ОБМ, поступающим на управляющий вход регистра 7 адреса. Зафиксированный на регистре 7 код адреса преобразуется на селекторе 6 адреса в код номера подпрограммы, который фиксируется на регистре 3 адреса подпрограмм. Микрокоманда формируется в процессе анализа сигнала ОБМ в случае, если ОБМ 1. Анализ сигнала ОБМ производится путем выполнения микрокомэндО ных слов, выбираемых из нулевого и первого адресов накопителя 1 микропрограмм, из нулевой ячейки которого, начиная из исходного состояния, выбирается микрокомандное слово, которое содержит код теку5 щего адреса, т.е. код передачи управления следующей ячейке этого накопителя. Этот код, считываясь из накопителя, поступает на информационные входы регистра 2 текущего адреса, где фиксируется передним

0 фронтом импульса генератора 9 импульсов. Таким образом, в следующем такте из накопителя 1 микропрограмм будет выбираться содержимое первой ячейки, т.е. производиться попеременное считывание информа5 ции из нулевой, первой и второй ячеек накопителя до тех пор, пока сигнал обмена ОБМ не станет равным единице. Из нулевой ячейки накопителя 1 микропрограмм считывается «Год управления мультиплексором 8

0 условий. Этот код фиксируется на соответствующих разрядах регистра 5 микрокоманд по переднему фронту инверсного значения импульсов с генератора 9 импульсов и поступает на управляющий вход муль5 типлексора 8 условий. Под действием этого кода мультиплексор условий коммутирует сигнал обмена ОБМ на информационный вход триггера 4 базового адреса. При этом, если сигнал ОБМ равен нулю, то триггер 4

0 базового адреса своего значения не изменяет и код управления передается во вторую ячейку накопителя 1 микропрограммы. Если же сигнал ОБМ равен 1, то триггер базового адреса 4 по переднему фронту генератора 9

5 импульсов изменит свое значение на единичное и управление передается на адрес накопителя микропрограмм.

В следующем такте микропрограммное слово будет считываться из ячейки 0003.

0 Микропрограммное слово, считываемое из ячейки с этим адресом, содержит код текущего адреса и микрокоманду. Эта микрокоманда разрешает запись в регистр 3 адреса подпрограмм кода номера подпрограммы,

5 соответствующего адресу, зафиксированному на регистре 7 адреса, и фиксируется в регистр 3 адреса подпрограмм. Одновременно на регистре 2 текущего адреса фиксируется код Ат 02в..,Триггер 4 базового адреса принимает нулевое значение, т.к. закрытый мультиплексор 8 условий формирует на своем выходе нулевой потенциал.

На следующих шагах микропрограммы осуществляется анализ сигнала ДЗП.

Анализ этого сигнала производится 5 аналогично анализу сигнала обмена ОБМ, описанному выше, с той лишь разницей, что мультиплексор 8 условий настраивается на коммутацию информации с второго канала, при этом управление в случае наличия сиг- 10 . налов ДЗП 1 передается в адреса накопителя 1 микропрограмм.

По адресу накопителя 1 микропрограмм выбирается код, поступающий на информационный вход регистра 24 адреса 15 подпрограмм, что соответствует номеру подпрограммы формирования последовательного кода. По переднему фронту импульса с генератора 27 импульсов код заносится в регистр 24 адреса подпрограмм.20

По адресу ОЮОа из накопителя 22 микропрограмм выбирается код и происходит обращение в ячейку 0102в. По этому адресу с накопителя 22 микропрограмм через регистр 26 микрокоманд выбирается значение 25 адреса ячейки блока оперативной памяти через группу 36 элементов И-ИЛИ. Данные с МПИ постуют на вход данных блока 34 оперативной памяти с выхода шинного фор- мирователя 38 через группу 33 элементов 30 И-ИЛИ. По этому же сигналу выбирается значение следующего текущего адреса накопителя микропрограмм и значение для формирования сигнала СЕ 1 (сигнала выборки кристалла) для всех разрядов блока 35 34 оперативной памяти в режиме записи информации с МПМ. Таким образом происходит запись информации с МПИ в блок 34 оперативной памяти. Далее происходит переход на адрес 0104а я из ячейки накопите- 40 ля выбирается значение, при котором происходит запись бита Старт 1 в О разряд регистра 31 последовательного кода. Группой разрядов дешифратор 30 микрокоманд формирует. управляющий 45 сигнал записи для записи бита Старт с выхода мультиплексора 37 в О разряде регистра 31 .последовательного кода. Накопитель переходит на адрес ОЮОе, из которого на выходе регистра 26 микрокоманд 50 формируются коды, соответствующие считыванию из О разряда блока 34 оперативной памяти по нулевому его адресу 1 бита информации в О разряд регистра последовательного кода и появлению его на шине 55 40 вывода последовательного кода. Затем происходит переход по адресу 0110а накопителя 22 микропрограмм. По этом адресу выбирается код, по которому мультиплексор 37 настраивается на передачу 2 бита

информации, что соответсвтует снятию сигнала СЕ с О разряда блока оперативной памяти.Далее происходит переход на адрес 0112s, при котором с накопителя 32 микропрограмм получают сигналы, соответствующие формированию с выхода дешифратора 35 сигнала СЕ для чтения первого разряда из нулевой ячейки блока 34 оперативной памяти и передачи его на выход шины вывода последовательного кода. Далее процедура продолжается аналогичным образом до выдачи двух битов Стоп, На этом обмен заканчивается и накопитель 22 микропрограмм переходит в исходное состояние. Необходимо отметить, что на втором шаге на выходе накопителя 22 микропрограмм вырабатывается сигнал, который поступает на один из входов мультиплексора 8 условий и сообщает таким образом накопителю 1 микропрограмм, что прием информации с МПИ закончен и накопитель 1 микропрограмм вырабатывает сигнал ОТВ в магистраль МПИ. По принятии сигнала ОТВ на МПИ может появиться адрес следующей команды.

Временные диаграммы преобразователя из параллельного кода в последовательный представлены на фиг,4.

Возможно сопряжение ЭВМ, осуществляющее преобразование из последовательного кода в параллельный. Работа устройства при этом заключается в следующем. Мультиплексор 29 условий настроен на прием синхросигнала по одному из каналов последовательного интерфейса. При появлении на шине синхросигнала последовательного канала (Старт) накопитель микропрограмм переходит на выполнение программы приема последовательного кода в блоке 34 оперативной памяти. При этом с выхода накопителя 22 микропрограмм группой разрядов формируется адрес ячеек блока 34, поступающий через группу элементов И- ИЛИ 36. После поступления адреса формируются управляющие сигналы на вход блока 34 оперативной памяти (сигналы записи и сигнал выборки кристалла на первый разряд ячейки блока 34 оперативной памяти) и в первый разряд ячейки блока 34 оперативной памяти через группу элементов И-ИЛИ 33 по соответствующему каналу поступает информационный бит последовательного кода. После приема первого бита снова формируются адрес и управляющие сигналы и во второй разряд ячейки блока оперативной памяти заносится второй бит информационного слова. Для передачи посылки на МПИ необходимо, таким образом, по последовательному каналу принять 16-битовую посылку для передачи на МПИ адреса и

16-битовую посылку для передачи данных. После приема необходимого количества бит информации накопитель микропрограмм настраивается на передачу информации в параллельном коде. При этом с накопителя 22 микропрограмм формируются управляющие сигналы, необходимые для организации работы в параллельном коде (ОБМ, ДЗП и ДЧТ), которые поступают на входы условий мультиплексора 8 условий, а накопитель 22 микропрограмм начинает формировать сигналы, необходимые для чтения информации из блока 34 оперативной памяти на вход шинного формирователя 38. Для чтения информации из блока 34 оперативной памяти необходимо снова подать адрес на вход блока 34, причем адрес подается тот же, что fipn приеме информации на блок 34 в последовательном коде. Затем формируются сиг- (налы выборки по всем 16 разрядам рдновременно и по сигналу чтения из блока оперативной памяти считывается информация и передается на шины параллельного Интерфейса после подачи сигнала на управляющий вход шинного формирователя 38. Таким же образом производится передача данных на шину параллельного интерфейса с той лишь разницей, что на выходе накопителя 22 микропрограмм формируется адрес Следующей ячейки блока 34 оперативной Памяти.

Данное устройство обеспечивает возможность преобразования из последовательного кода в последовательный. При этом для данного преобразования необходимо сначала последовательный код преобразовать в параллельный, а затем параллельный в последовательный, как было описано выше.

Контроль работы многоканального устройства управления для сопряжения осуществляется в нескольких режимах: контроль блоков 16,34 оперативной памяти; контроль регистров 5,26 микрокоманд; контроль в режиме формирования микрокоманд накопителя 1 микропрограмм.

Каждый из режимов контроля заключается в регистрации содержимого указанных выше компонент через мультиплексор 18 и шинный формирователь 19 в ЭВМ, подключенную в МПИ, для дальнейшего анализа. При этом возможны два режима передачи информации в ЭВМ; непосредственно через мультиплексор 18 данных; через блок 16 оперативной памяти.

Контроль через блок 16 оперативной памяти позволяет накапливать информацию, а затем передавать ее в ЭВМ в нужный момент, что позволяет э случае необходимости иметь фотографию содержимого накопителя 1 микропрограмму также снять трассировку хода микропрограмм в реальном масштабе времени. Алгоритмы контроля накопителя микропрограмм в режиме формирования

микрокоманд и в режиме трассировки представлены на фиг.5,6.

Анализ может производиться путем последовательного сравнения или путем подсчета контрольных сумм с помощью ЭВМ,

0 подключенной в МПИ. Режим контроля задается регистром 13 контроля и управления. При этом каждый его разряд осуществляет соответствующую функцию задания режимов контроля и управления коммутацией со5 ответствующей информации, подлежащей регистрации.

Назначение разрядов регистра 13 контроля и управления следующее:

группа разрядов 0-3 обеспечивает уп0 равление мультиплексором 18 данных;

4 - разряд бит управления режимом работы блока 16, при 4 0 - запись информации, при 4 г 1 - чтение информации; 5 - бит управления режимом выборки

5 блока 16 оперативной памяти, при 5 О выборка запрещена, при 5 1 выборка информации разрешена;

6 - управление адресацией блока 16 оперативной памяти, при 6 1 - разреше0 ние работы блока оперативной памяти по значению счетчика 12 адреса, при 6 0 - разрешение работы блока оперативной памяти по адресу накопителя 1 микропрограмм;

5 7,8 - режим инкремента адресного кода блока оперативной памяти,при 7 1 - инкремент от внешнего сигнала, при 8 1 - инкремент от генератора 9 импульсов.

Загрузка регистра 13 контроля и управ0 ления от магистрали 21 параллельного ввода-вывода данных производится по микрокоманде.

Чтение информации из регистра 13 контроля и управления производится согласно

5 временной диаграмме, представленной на фиг.З.При этом на первых трех шагах подпрограммы производится анализ сигнала обмена ОБМ.при наличии сигнала обмена производится селектирование адресасМПИизаписьноме0 ра подпрограммы (в данном случае третьей подпрограммы) в регистр 3 адреса подпрограммы и на адресный вход накопителя 1 микропрограммы подается адрес, По этому адресу из накопителя 1 микропрограмм выбирается значе5 ние текущего адреса следующей микрокоманды и подпрограмма переходит на анализ сигнала чтения ДЧТ с МПИ. При этом из накопителя 1 микропрограмм выбирается код для анализа сигнала чтения ДЧТ на мультиплексоре 8 условий После появления сигнала ДЧТП производится переход по адресу. Из накопителя 1 микропрограмм выбираются значения и формируется сигнал ответа ОТВ в магистраль МПИ. Открывается мультиплексор 18 данных по первому кана- лу, что соответствует чтению информации из регистра 13 контроля и управления через шинный формирователь 19. При этом управляющий сигнал принимает значение, равное нулю, что соответствует переключению шинного формирователя на передачу данных в МПИ. После получения сигнала ответа с МПИ должен быть снят сигнал чтения ДЧТ, что также анализируется мультиплексором условий. После снятия сигнала ДЧТ проис- ходит переход для анализа сигнала ОБМ. После получения сигнала ОБМ 0 накопитель переходит по адресу и вырабатывается сигнал конца операции, по которому накопитель 1 микропрограмм переходит в исход- ное состояние.

Используя блок 16 оперативной памяти через мультиплексор 17 данных, можно осуществлять контроль накопителей 1 микропрограмм через регистр 5 микропрограмм и контроль адресных регистров накопителей: регистра 2 текущего адреса, регистра 3 адреса подпрограмм, триггера 4 базового адреса. Через мультиплексор 18 данных после переключения шинных формирователей 19 на режим передачи информации в МПИ может осуществляться контроль счетчиков 32,12 адреса, блоков 34 и 16 оперативной памяти, регистра 31 последовательных кодов, регистра 13 контроля и управления.

При использовании блока 16 оперативной памяти в режиме трассировки микропрограмм предварительно необходимо настроить программным путем регистр. 13 контроля и управления.При трассировке мик- ропрограмм с накопителя 1 микропрограмм регистр 13 контроля и управления настраивается следующим образом:

разряды 0-3 0010 - открывается мультиплексор 17 данных на прием в блок 16 оперативной памяти младших разрядов регистра 26 микрокоманд;

4 0, 5 1, 6, 7 1 - настройка блока 16 оперативной памяти на режим записи информации.

После описанной подготовки выполняется любая исследуемая микропрограмма для накопителя 1 микропрограммы с адресацией блока 16 оперативной памяти от счетчика 12 адреса с последующей его инк- рементацией. При реализации исследуемой программы на шестом шаге ее выполнения формируется микрокоманда, которая установит в единичное состояние триггер 10. Этот триггер единичным сигналом разрешает работу элемента И-ИЛИ 11, который коммутирует подачу на счетный вход счетчика 12 адреса импульсов от генератора 9 импульсов. Таким образом, после установки триггера 12 в единичное состояние на каждом шаге выполнения микропрограмм содержимое счетчика 12 будет увеличиваться на единицу (инкремент 1), следовательно, информация, поступающая на блок 16 оперативной памяти .с выходов регистра 5 микрокоманд, зафиксируется в ячейках блока оперативной памяти. Необходимо заметить, что синхроимпульс, фиксирующий адрес блока оперативной памяти, формируется на элементе И-ИЛИ 14, который должен осуществлять не только прямую фиксацию логического умножения, но и функцию задержки, т.е. время задержки сигнала на этом элементе должно быть больше времени задержки на элементе И-ИЛИ 15. Этого можно достичь, применяя элемент И-ИЛИ 14 с большим временем задержки, чем у элемента И-ИЛИ 15. После завершения операции на 12-м шаге формируется микрокоманда, которая устанавливает в нулевое состояние триггер 10, и запись в блок 16 оперативной памяти прекращается.

В блоке оперативной памяти зафиксирована последовательность формирования микрокоманд с накопителя 1 микропрограмм через регистр 26 микрокоманд, которая может быть считана на магистраль 21с помощью специальной команды чтения.

Реализация команды чтения блока 16 оперативной памяти осуществляется аналогично уже описанным. Эта команда реализуется с помощью команды чтения (ДЧТ) с магистрали 21 параллельного ввода-вывода по специальному адресу, отведенному для этой команды. Этот адрес поступает в адресном цикле на регистр 7 адреса, далее дешифруется на селекторе 6 адреса в адрес соответствующей подпрограммы, в процессе реализации которой производится формирование импульса выборки блока оперативной памяти и счетного импульса, инкрементирующего адрес блока 16 опера- THBrfon памяти. Кроме того, формируется код Хз 01, который осуществляет коммутацию информации, считанной из блока 16 оперативной памяти на магистраль 21 параллельного ввода-вывода данных. Таким образом, путем многократного выполнения описанной операции будет считано п ячеек блока 16 оперативной памяти, начиная с An + 1, где п - количество выполненных операций чтения данных из блока 16 оперативной памяти, An - начальный адрес, записанный на счетчик 12 адреса отдельной командой.

Кроме того, регистр 13 контроля и управления также должен быть предварительно настроен на считывание информации из блока 16 оперативной памяти по содержимому счетчика 12 адреса. Процедура на- стройки блока 16 оперативной памяти описана выше. Очевидно, что если регистр 13 контроля и управления будет настроен в части группы разрядов,управляющих мультиплексором 17, на другой код, то описанным способом может быть снята фотография (последовательность) любых других последовательностей, подключенных на информационные входы мультиплексора 17. Если же в начале описанного режима контроля ре- гистр 13 контроля и управления разряда б будет настроен на адресацию от адресной компоненты, т.е. 6 1, то при выполнении Той же операции последовательно будет зафиксирована заданная информация, после- довательность регистрации в блоке 16 оперативной памяти которой определяется последовательностью изменения адресной части накопителя 1 микропрограмм. Целесообразность реализации этого режима контроля определяется необходимостью контроля содержимого накопителя 1 микропрограмм при естественном обращении к адресу самого накопителя.

Режим трассировки по счетчику 12 адреса обеспечивает линейный контроль выполнения микропрограмм и применяется а основном для контроля при настройке самого устройства и при отладке рабочих программ обоих накопителей микропрограмм, обеспечивая трассировку микропрограмм.

Режим контроля по адресной компоненте накопителя 1 микропрограмм обеспечивает контроль формирования микрокоманд накопителя 1 микропрограмм на каждом ело- ве их выборки из накопителя, а также после- довательность из выборки за время реализации функциональной подпрограммы. Контроль самого блока 16 оперативной памяти может проводиться путем записи информации в ячейки ОЗУ 16 и счетчика 12 адреса. При этом регистр 13 контроля и управления настраивается на запись в ОЗУ 16 по первому каналу мультиплексора 17с адресацией через счетчик 12 адреса и в каж- дои ячейке блока 16 оперативной памяти будет записан сам адрес ячейки.

Формула изобретения

Многоканальное устройство для сопряжения ЭВМ, содержащее первый шинный формирователь, первый вход которого является входом параллельного ввода-вывода данных устройства, а выход соединен с первой группой входов первой группы элементов И-ИЛИ, выходы которых соединены с

информационными входами первого блока оперативной памяти, вторая группа входов первой группы элементов И-ИЛИ подключена к выходам первого мультиплексора данных, входы которого являются входами ввода последовательного кода устройства, первый и второй входы первой группы элементов И-ИЛИ подключены к первому выходу первого регистра микрокоманд, управляющие входы первого блока оперативной памяти соединены с выходами дешифратора, входы которого подключены к первой группе выходо i первого регистра микрокоманд, адресные входы первого блока оперативной памяти соединены с выходами элементов И-ИЛИ второй группы, выходы первого блока оперативной памяти подключены к второму входу первого шинного формирователя, к ин- формационным входам первого счетчика адреса и к информационным, входам мультиплексора, первый и второй информационные входы мультиплексора соединены соответственно с шинами единичного и нулевого потенциалов, управляющие входы мультиплексора подключены к второй группе выходов первого регистра микрокоманд, к входам дешифратора микрокоманд и к управляющим входам первого мультиплексора данных. выходы мультиплексора соединены с информационными входами регистра последовательных кодов, выходы которого являются выходами вывода последовательного кода устройства, а управляющие входы регистра последовательного кода соединены с выходами дешифратора микрокоманд, тактовый вход первого счетчика адреса соединен с вторым выходом первого регистра микрокоманд, выходы первого счетчика адреса соединены с первой группой входов второй группы элементов И-ИЛИ, вторая группа входов которого соединена с третьей группой выходов первого регистра микрокоманд, первый и второй входы элементов И-ИЛИ второй группы соединены соответственно с третьим и четвертым выходами первого регистра микрокоманд, пятый выход которого подключен к управляющему входу первого шинного формирователя, информационные входы первого регистра микрокоманд подключены к первой группе выходов первого накопителя микропрограмм, вторая группа выходов которого соединена с информационными входами первого регистра текущего адреса, выходы которого соединены с первой группой адресных входов первого накопителя микропрограмм, вторая группа адресных входов „которого соединена с выходами первого ре- гаетра адреса подпрограмм, старший разряд адресного йхода первого накопителя

микропрограмм подключен к выходу первого триггера базового адреса, управляющие входы первого регистра микрокоманд и первого регистра текущего адреса соединены с выходами элементов И-ИЛИ третьей группы, первый вход которой соединен с выходом первого генератора импульсов и синх- ровходами первого регистра адреса подпрограмм и первого триггера базового адреса, второй вход третьей группы элементов И- ИЛИ и первый управляющий вход первого мультиплексора условий подключены к входу Контроль устройства, информационный вход первого триггера базового адреса соединен с выходом второго мультиплексора условий, входы которого являются входами синхросигналов последовательного интерфейса устройства, управляющие входы второго мультиплексора условий подключены к четвертой группе выходов первого регистра микрокоманд, отличающееся тем, что, с целью повышения эффективности диагностики неисправностей путем автоматизации поиска неисправности, увеличения глубины контроля и его разрешающей способности, в устройство введены второй шинный формирователь, регистр адреса, селектор адреса, второй триггер базового адреса, второй регистр текущего адреса, третий мультиплексор условий, второй регистр адреса подпрограмм, второй накопитель микропрограмм, второй регистр микрокоманд, триггер, два элемента И-ИЛИ, регистр контроля и управления, четвертая группа элементов И-ИЛИ, второй блок оперативной памяти, второй генератор импульсов, второй и третий мультиплексоры данных, второй счетчик адреса, причем выход второго мультиплексора данных через второй шинный формирователь соеди нен с выходом информационных шин параллельного ввода-вывода данных уст- ройства, первый вход второго мультиплексора данных подключен к выходам первого региртра микрокоманд, второй вход второго мультиплексора данных соединен с выходами первого блока оперативной памяти, третий вход - с адресными входами первого накопителя микропрограмм, четвертый вход является входом ввода последовательного кода устройства, пятый вход второго мультиплексора данных соединен с выходом первого счетчика адреса,,шестой вход- с выходом второго счетчика адреса, с первой группой входов четвертой группы элементов И-ИЛИ и первым входом третьего мультиплексора данных, седьмой вход - с выходами второго блока оперативной памяти, восьмой вход - с выходом регистра контроля и управления, девятый вход - с

выходами второго триггера базового адреса, второго регистра адреса подпрограмм, второго регистра текущего адреса, с адресными йходами второго накопителя микропрограмм, с второй группой входов четвертой группы элементов И-ИЛИ и с вторым входом третьего мультиплексора данных, выход второго шинного формирователя соединен с информационными входами регистра адре0 са, второго счетчика адреса, регистра контроля и управления и третьим входом третьего мультиплексора данных, выход регистра адреса соединен с первой группой входов селектора адреса, выходы которого

5 соединены с информационными входами второго регистра адреса подпрограмм, вторая группа входов селектора адреса соединена с информационными входами второго регистра текущего адреса и с первой груп0 пой выходов второго накопителя микропрограмм, вторая группа выходов которого соединена с информационными входами второго регистра микрокоманд, первый выход второго генератора тактовых импульсов

5 соединен с синхровходами второго триггера базового адреса, второго регистра адреса подпрограмм, второго регистра текущего адреса и с первым входом первого элемента И-ИЛИ, второй выход второго генератора

0 тактовых импульсов подключен к синхров- ходу второго регистра микрокоманд, вход данных второго триггера базового адреса соединен с выходом первого мультиплексора условий, информационные входы которого

5 являются входами синхросигналов параллельного интерфейса устройства, первый информационный вход первого мультиплексора условий подключен к синхровходу регистра адреса, управляющий вход первого

0 мультиплексора условий соединен с шестым выходом первого регистра микрокоманд, адресные входы первого мультиплексора условий соединены с первой группой выходов второго регистра микрокоманд, вторая груп5 па выходов которого подключена к информационным входам первого регистра адреса подпрограмм, третья группа выходов второго регистра микрокоманд подключена к управляющим входам второго мультиплек0 сора данных, с первого по шестой выходы второго регистра микрокоманд соединены соответственно с третьим входом третьей группы элементов И-ИЛИ, установочным и входами сброса триггера, вторым входом

5 первого элемента И-ИЛИ, синхровходом регистра контроля и управления и первым входом второго элемента И-ИЛИ, первая, вторая и третья группы выходов и с первого по шестой выходы второго регистра микрокоманд соединены с восьмым входом второго мультиплексора данных, выход триггера соединен с третьим входом первого элемента И-ИЛИ, выходы регистра контроля и управления - соответственно с четвертым и 1ятым входами первого элемента И-ИЛИ, с третьим и четвертым входами четвертой группы элементов И-ИЛИ, с вторым и четвертым входами второго элемента И-ИЛИ, с первым управляющим входом второго блока оперативной памяти и с управля ющим входом второго шинного формирователя, выход Первого элемента И-ИЛИ соединен со счет- ным входом второго счетчика адреса и с

третьим входом второго элемента И-ИЛИ, выходы элементов И-ИЛИ четвертой группы соединены с адресными входами второго блока оперативной памяти, группа выходов регистра контроля и управления подключена к управляющим входам третьего мультиплексора данных, выходы которого соединены с входами данных второго блока оперативной памяти, второй управляющий вход которого подключен к выходу второго элемента И- ИЛИ, выходы второго мультиплексора данных соединены с вторыми входами второго шинного формирователя.

РИГ. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1476477A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для отладки программ | 1988 |

|

SU1661771A1 |

Изобретение относится к вычислительной технике и может найти применение в вычислительных системах для сопряжения двух и нескольких ЦВМ с различным представлением данных. Целью изобретения является повышение эффективности диагностики неисправностей путем автоматизации поиска неисправности, увеличения глубины контроля и его разрешающей способности. Устройство содержит накопители микропрограмм, регистры текущего адреса, регистры адреса подпрограмм, триггеры базового адреса, регистры микрокоманд, селектор адреса, регистр адреса, мультиплексоры условий, генераторы тактовых импульсов, триггер,злементыИ-ИЛИ, счетчики адреса, регистр контроля и управления, группы элементов И-ИЛИ, блоки оперативной памяти, мультиплексоры данных, шинные формирователи, дешифратор микрокоманд, регистр последовательного кода, дешифратор, мультиплексор. 6 ил. « Ј

/jfldpec X

fty3% XL.

Jon

Адрес НМП

k

GT

Анные в ОЗУ

СЕв

yap

MS

У/7/3

Тгюмшл

OptOC b9J(/(

Ј(/

Yfff

$

1( с Јш ОЗУ

Данные X

. 3

( HOVOJO )

tows ремма 6 регистр MMpGjt и yfipaSjet/vf

Фи 5

(HovoJo )

Зомсь ptJKVMot регислР jf и upelKwJf

ЗС/К/СА cdwc 03У & счет их одресо

Змись ofyecof ренхлр 7ffdjpeco

сыек/м/робоние odjtCQ иЗо/х/сь / ремелр ofyew ко/к/aiej/ /fujyx - apOtyoMfl

Запись Q&ecQ HOKG- w/пш / SiOK /6

0/ ф }/1К/&МУ MtffW

1МКяетрЖ# # fffaw / evouwxf / cfaeo

Фиг. 6

вменение odfKo мкомтелл Марс- /рофомм

Зот,сь /&юк /6 скро/мбюй jw v cjedwyew

№№W ffdffffff HOKO/K/ftW Mwfi- nMtyOM /10 Ofyf- СУ CVf/nVi/jKO fftyf- Cff

( Конец )

| Авторское свидетельство СССР Мг 1151125, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для сопряжения двух ЭВМ | 1985 |

|

SU1312585A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1988-10-24—Подача