Изобретение относитей к телевиде- i нию и может быть использовано для воспроизведения ннфсрмацш на экране.

Цель изобретения - устранение мерцания яркости быстро изменяющегося изображения за счет введения дополнительного цикла развертки.

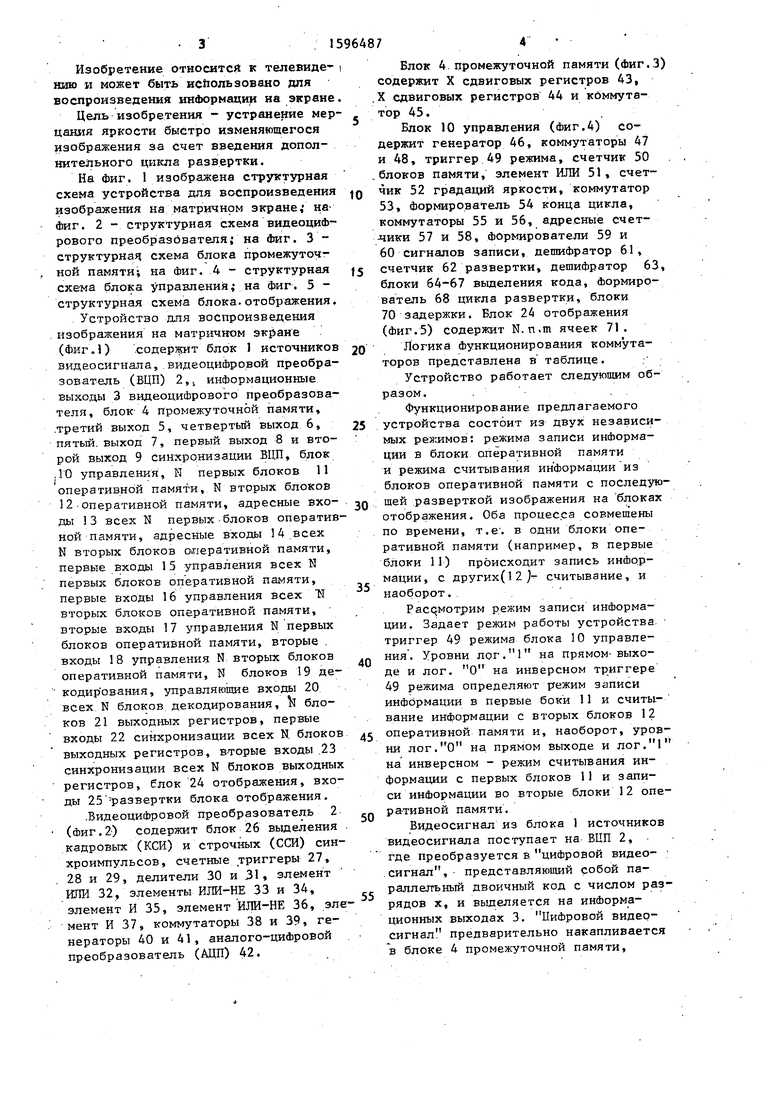

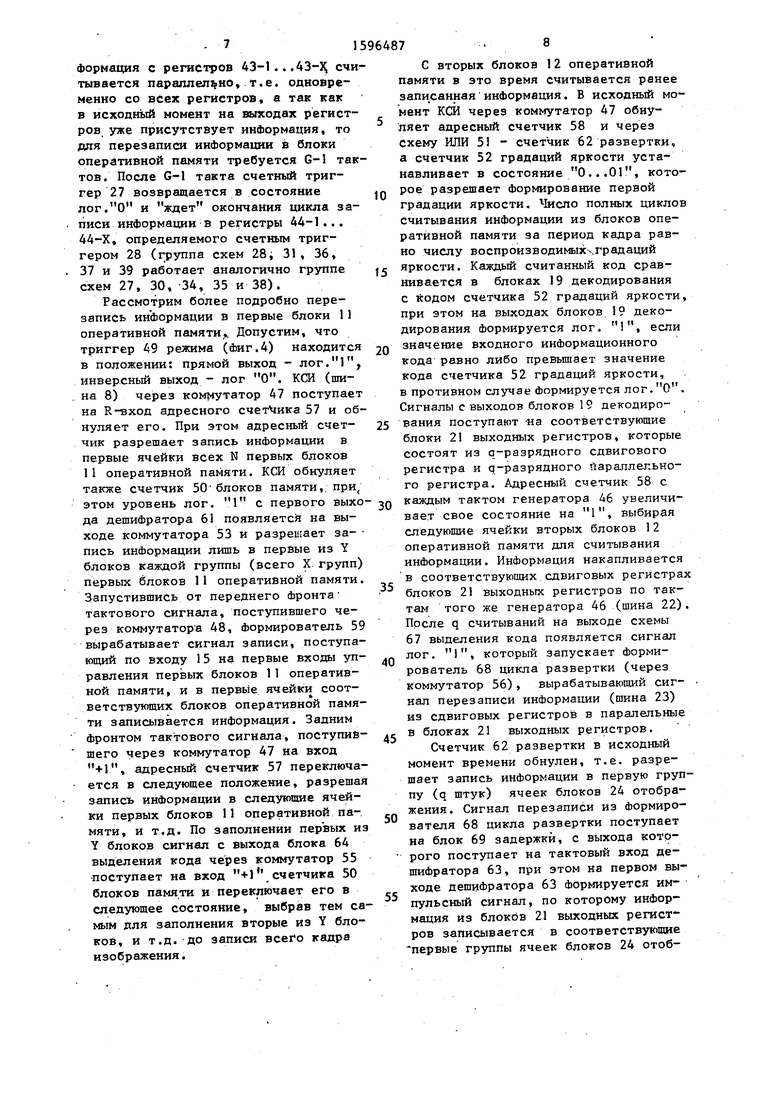

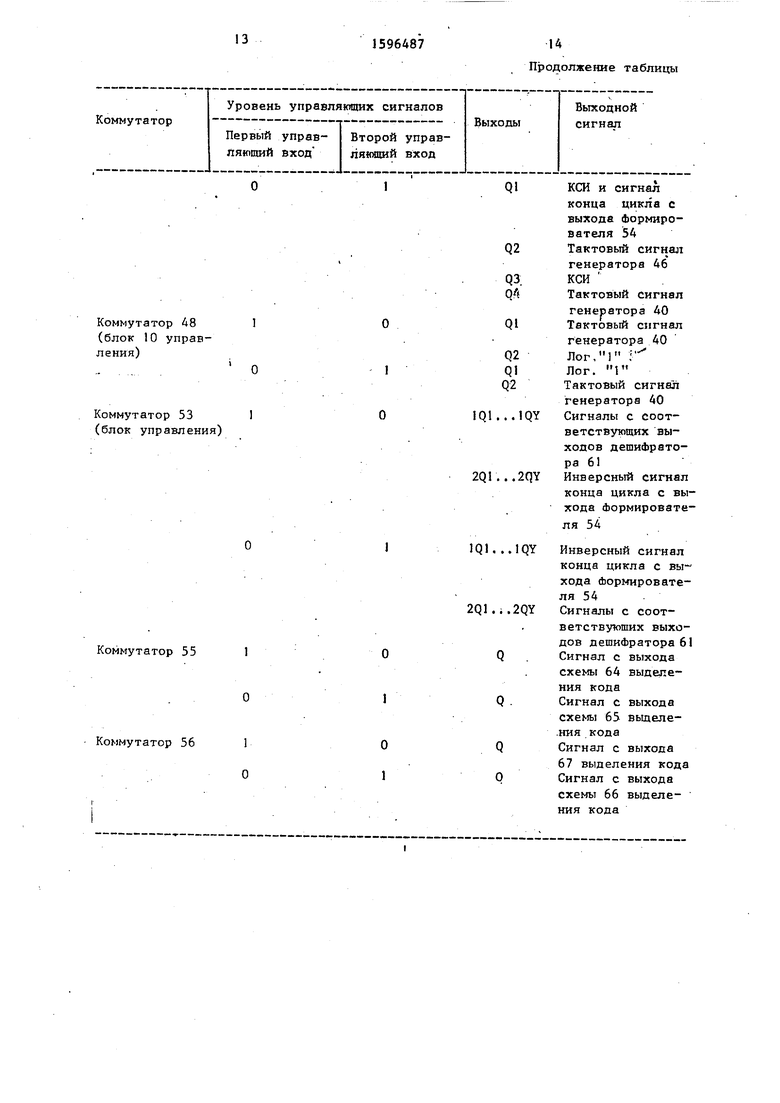

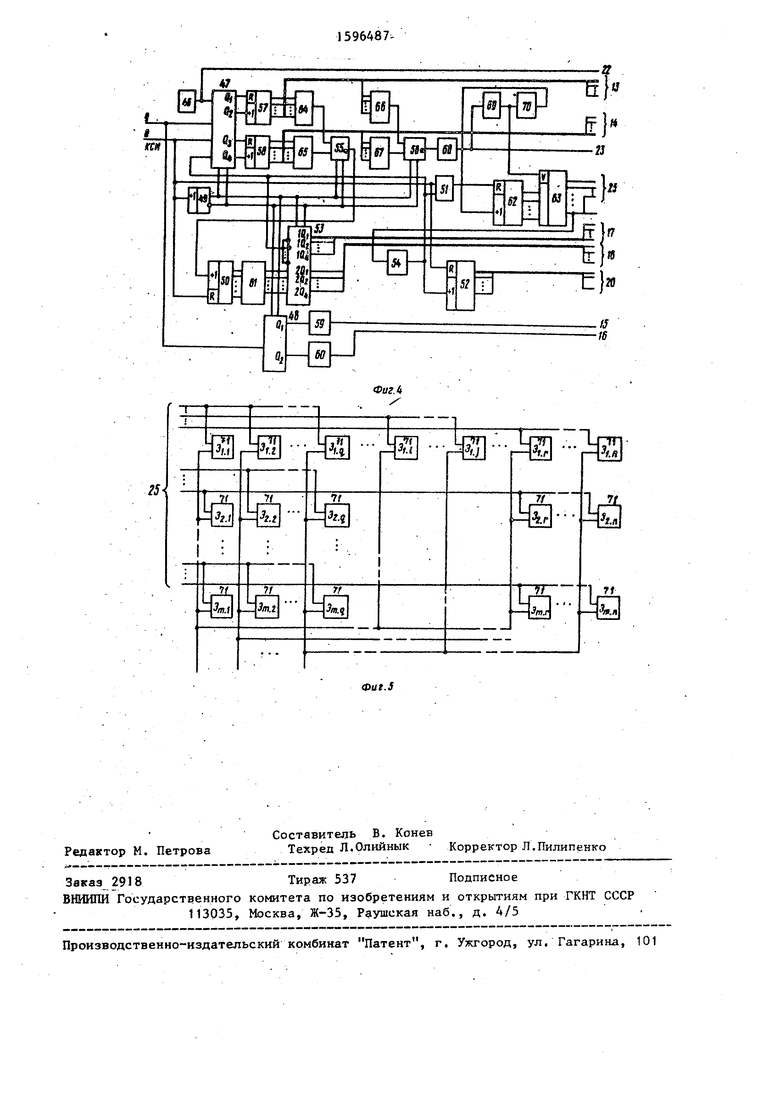

На Фиг. 1 изображена структурная схема устройства для воспроизведения изображения на матричном экране,- наФиг. 2 - структурная схема видеоциЛрового преобразЬвателя; на Фиг. 3 структурная схема блока промежуточной памяти; на Фиг. 4 - структурная схема блока управлени)й1{ на фиг. 5 структурная схема блока.отображения.

Устройство для воспроизведения изображения на матричном экране (Фиг.О .содержит блок 1 источников видеосигнала, видеоцифровой преобразователь (ВЦП) 2,1 информационные выходы 3 видеоцифрового преобразователя, блок- 4 промежуточной памяти, третий выход 5, четвертый выход 6, пятый, выход 7, первый выход 8 и второй выход 9 синхронизации ВЦП, блок 10 управления, N первых блоков 11 оперативной памяти, N вторых блоков 12.оперативной памяти, адресные вхо- . ды 3 всех N первых-блоков оперативной памяти, адресные входы 14 всех N вторых блоков оперативной памяти, первые входы 15 управления всех N первых блоков оперативной памяти, первые входы 16 управления всех N вторых блоков оперативной памяти, вторые входы 17 управления N первых блоков оперативной памяти, вторые . входы 18 управления N вторых блоков оперативной памяти, N блоков 19 декодирования, управляющие входы 20 всех N блоков декодирования, N блоков 21 вькодных регистров, первые входы 22 синхронизации всех N, блоков выходных регистров, вторые входы .23 синхронизации всех N блоков выходных регистров, блок 24 отображения, входы 25развертки блока отображения.

.Видеоцифровой преобразователь 2 (фиг. 2} содержит блок 26 вьщеления кадровых (КСИ) и строчных (ССИ) синхроимпульсов, счетные триггеры 27, 28 и 29, делители 30 и 31, элемент ИЛИ 32, элементы ИЛИ-НЕ 33 и 34, элемент И 35, элемент ИЛИ-НЕ 36, элемент И 37, коммутаторы 38 и 39, генераторы 40 и 41, аналого-цифровой преобразователь (АЦП) 42.

Блок 4 промежуточной памяти (Фиг. содержит X сдвиговых регистров 43, .X сдвиговых регистров 44 и коммутатор 45.

Блок 10 управления (Фиг.4) содержит генератор 46, коммутаторы 47 и 48, триггер 49 режима, счетчик 50 .блоков памяти, элемент ИЛИ 51, счетчик 52 градаций яркости, коммутатор 53, формирователь 54 конца цикла, коммутаторы 55 и 56, адресные счет ики 57 и 58, формирователи 59 и 60 сигналов записи, дешифратор 61, счетчик 62 развертки, дешифратор 63 блоки 64-67 вьщеления кода. Формирователь 68 цикла развертки, блоки 70 задержки. Блок 24 отображения (Фиг.5) содержит N.n.m ячеек 71.

Логика Функционирования коммутаторов представлена в таблице.

Устройство работает следующим образом. ..

Функционирование предлагаемого устройства состоит из двух независимых режимов: режима записи информации в блоки оперативной памяти и режима считывания информации из блоков оперативной памяти с последуюшей разверткой изображения на блоках отображения. Оба процес.са совмешены по времени, т.е . в одни блоки оперативной памяти (например, в первые блоки 11) происходит запись информации, с других(12)- считывание, и наоборот.

Расс мотрим режим записи информации. Задает режим работы устройства. триггер 49 режима блока 10 управления. Уровни лог.М на прямом-выходе и лог. О на инверсном триггере 49 режима определяют режим записи информации в первые боки 11 и считы.вание информации с вторых блоков 12 оперативной памяти и, наоборот, уровни лог.О на прямом выходе и лог.1 на инверсном - режим считывания информации с первых блоков 11 и записи информации во вторые блоки 12 оперативной памяти.

Видеосигнал из блока 1 источников видеосигнала поступает на ВЦП 2, где преобразуется в цифровой видео.сигнал,- представляющий собой параллельный двоичный код с числом разрядов X, и выделяется на информационных выходах 3. Цифровой видеосигнал предварительно накапливается в блоке 4 промежуточной памяти.

представляюшем собой явубуферное устройство памяти на х-разрядных параллельно-последовательных регистрах. Каждый регистр вмешает G слов (здесь под словом понимается одна посылка цифрового видеосигнала, т.е. один х-раэрядный двоичный код).

Таким образом, каждый буфер блока 4 промежуточной памяти предназначен для хранения информации о яркости X«G точек изображения. Информация, накопленная в блоке 4 промежуточной памяти, переписывается в. первые 6jiOки 11 оперативной памяти, причем первые G точек изображения записываются в первую группу первых блоков 11 оперативной памяти; вторые G точек изображения - во вторую группу первых блоков 1I оперативной памяти и так далее, последние G точек изображения - в Х-ю группу первых блоков 1I оперативной памяти. По заполнении первого из группы (Y штук) блока оперативной памяти начинает заполняться следуюший блок и так до заполнения последнего Y-ro блока оперативной памяти либо до записи полного кадра изображения.

Рассмотрим режим записи более подробно . Входной аналоговый видеосигнал-(Фиг.2) в ВЦП 2 поступает на АДП 42 и блок 26 выделения КСИ и ССИ. АЦП 42 преобразует входной видеосигнал в х-разрядньгй параллельный код синхронно тактам генератора 4J, являюшегося генератором квантования видеосигнала. КСИ поступает в блок 10 управления, а ССИ служит для синхронизации работы ВЦП 2. ССИ обнуляет триггеры 27, 28 и 29, при этом лог. 1 с выхода схемы ИЛИ-КЕ 33 запрещает работу генератора 40, лог.О с выхода схемы ИЛИ-ВЕ 36 и выхода схемы И 37 запрепают работу коммутатора 39, а лог. 1 и лог.О с выходов схемы Hnii-HE 34 и схемы И 35 соответственно подключают коммутатор 38 на пропускание тактовой частоты генератора 41, которая поступает в блок 4 промежуточной памяти (выход 5) и на делитель 30. Делитель 30 (31) управляемый с переменным коэффициентом деления. При лог. О на управляющем входе он рассчитан на так-с тов работы, а при лог. 1 на управ- ляющем входе - на G-1 тактов работы. Итак, после обнуления триггеров первым тактом генератора 41 выделяется информация о яркости первой точки изображения на выходе АЦП 42, которая по заднему .фронту тактового сигнала записывается в сдвиговый регистр 43-1 (Фиг.З). Следукщим тактом генератора 41 вьщеляется инофрмация о яркости второй точки изображения, которая записывается в сдвиговый регистр 43-1 на место ранее записаннойпервой точки, которая при этом сдвигается во вторые ячейки регистра, и т.д. После X-G такта генератора 41 информация о яркости первой точки

изображения оказывается записанной в последних ячейках сдвигового регистра 43-х. При этом сигнал с выхода делителя 30 переключает счетный триггер 27 в состояние лог. 1, что вызывает появление на выходе схемы ИЛИ

32лог. 1 и переключение счетного триггера 29 в состояние лог.1. Кроме того, лог. О и лог. 1 с выходов схемы ШШ-НЕ 34 и схемы И 35 соответственно разрешают прохождение тактовых сигналов генератора 40 через коммутатор 38, лог. 1 и лог.О с выходов схемы РШИ-НЕ 36 и схемы И 37 соответственно - тактовых сигналов генератора 41 через коммутатор 39, а лог. О с выхода схемы ИЛИ-НЕ

33- работу генератора 40. При этом информация, записанная в регистрах 43-1...43-х, выделяется на выходах

коммутатора 45 (на управляющем входе коммутатора 45 уровень лог.1), по тактам генератора 40 сдвигается,дальше (прямой выход генератора 40) и записывается (инверсный выход генератора 40) в соответствующие первые блоки 11 оперативной памяти.

боты генератора 40 на его инверсном выходе 9 появляется сигнал с уровнем лог. 1, который, поступая в блок 10 управления, вырабатывает сигнал записи информации в П1ервые блоки I 1 оперативной памяти. Так как на выходах регистров 43-1...43-х уже имеется информация о яркости соответствующих точек изображения, то она записывается в соответствующие оперативной памяти. Первый тактовый сигнал на прямом выходе генератора 40 сдвигает информацию в регистрах 43-1... 43-Х, а следующий тактовый сигнал с инверсного выхода генератора 40 записывает новую информацию в блоки оперативной памяти и так далее. ИнФормация с регистров ...43-S; счи тывается параллельно, т.е. одновременно со всех регистров, а так как в исходнь1й момент на выходах регистров уже присутствует информация, то для перезаписи информации в блоки оперативной памяти требуется G-1 так тов. После G-1 такта счетный триггер 27 возвращается в состояние лог.О и ждет окончания цикла записи информации в регистры 44-1... 44-х, определяемого счетным триггером 28 (группа схем 28; 31, 36, 37 и 39 работает аналогично группе схем 27, 30, 34, 35 и 38). Рассмотрим более подробно перезапись информации в первые блоки 11 оперативной памяти Допустим, что триггер 49 режима (Фиг.4) находится в положении: прямой выход - лог.М, инверсный выход - лог О. КСИ (ши. на В) через коммутатор 47 поступает на Е.-вход адресного счетчика 57 и об нуляет его. При этом адресный счетчик разрешает запись информации в первые ячейки всех N первых блоков 11 оперативной памяти. КСИ обнуляет также счетчик 50- блоков памяти,, при этом уровень лог. 1 с первого выхо да дешифратора 6 появляется на выходе коммутатора 53 и разрешает запись информации лишь в первые из Y блоков каждой группы (всего X групп) первых блоков 11 оперативной памяти Запустившись от переднего Фронтатактового сигнала, поступившего через коммутатора 48, формирователь 59 вырабатывает сигнал записи, поступающий по входу 15 на первые входы управления первых блоков 11 оперативной памяти, и в первые ячейки соответствующих блоков оперативной памяти записывается информация. Задним Фронтом тактового сигнала, поступившего через коммутатор 47 на вход +1, адресный счетчик 57 переключа ется в следующее положение, разрешая запись информации в следующие ячейки первых блоков 11 оперативной памяти, и т.д. По заполнении первых и Y блоков сигнал с выхода блока 64 выделения кода через коммутатор 55 поступает на вход +1 счетчика 50 блоков памяти и переключает его в следующее состояние, выбрав тем са мым для заполнения вторые из Y блоков, и т.д. до записи всего кадра изображения. 7 С вторых блоков 12 оперативной памяти в это время считывается ранее запи санная информация. В исходный момент КСИ через коммутатор 47 обнуляет адресный счетчик 58 и через схему ИЛИ 51 - счетчик 62 развертки, а счетчик 52 градаций яркости устанавливает в состояние 0.. .01, которое разрешает формирование первой градации яркости. Число полных циклов считывания информации из блоков оперативной памяти за период кадра равно числу воспроизводимыхчградаций яркости. Каждый считанный код сравнивается в блоках 19 декодирования с одом счетчика 52 градаций яркости, при этом на выходах блоков 19 декодирования Формируется лог. 1, если значение входного информационного кода равно либо превьшает значение кода счетчика 52 градаций яркости, в противном случае Формируется лог. О. Сигналы с выходов блоков 19 декодирования поступают -на соответствующие блоки 21 выходных регистров, которые состоят из а-разрядного сдвигового регистра и q-разрядного параллельного регистра. Адресный счетчик 58 с каждым тактом генератора 46 увеличивает свое состояние на 1, выбирая следующие ячейки вторых блоков 12 оперативной памяти для считывания информации. Информация накапливается в соответствующих сдвиговых регистрах блоков 21 выходных регистров по тактам того же генератора 46 (шина 22). После q считываний на выходе схемы 67 выделения кода появляется сигнал лог. 1, который запускает формирователь 68 цикла развертки (через коммутатор 56), вырабатывающий сиг- нал перезаписи информации (щина 23) из сдвиговых регистров в паралельные в блоках 21 выходных регистров. Счетчик 62 развертки в исходный момент времени обнулен, т.е. разрешает запись информации в первую группу (q штук) ячеек блоков 24 отображения. Сигнал перезаписи из формирователя 68 цикла развертки поступает на блок 69 задержки, с выхода которого поступает на тактовый вход дешифратора 63, при этом на первом выходе дешифратора 63 Формируется импульсный сигнал, по которому информация из блоков 21 выходных регистров записывается в соответствующие первые группы ячеек блоков 24 отображения. Затем этот же сигнал перезаписи, задержанный блоком 70 задержки, поступает на вход Ч счетчика 62 развертки и переводит его в следукявее состояние и т.д. до записи информации во все группы ячеек блоков 24 отображения. После записи информации в последние группы ячеек сигнал с последнего выхода дешифратора 63 поступает на йзормирователь 54 конца цикла, который вырабатывает сигнал конца цикла считывания, Этот сигнал обнуляет счетчик 62 развертки адресный счетчик 58 и переводит счет чик 52 градаций яркости в следующее состояние. Описанный процесс повторяется для следующей градации яркости и т.д. После поступления очередного КСИ триггер 49 режима переключается в положение: прямой выход лог.О,инверсный выход- лог. 1, и описанный процесс повторяется, только запись информации производится во вторые блоки I2 оперативной памяти, а считывание - с первых блоков 1 оперативной памяти.

Каждая ячейка 71 блоков отображения состоит из элемента памяти (триггер D-типа) и светоизлучающего элемента. Длительность свечения светоизлучаюших элементов определяется состоянием соответствующих элементов памяти. Так, при первом цикле считывания все элементы памяти устанавливаются в состояние лог. I (кроме соответствующих состоянию 0...00 уровень черного), при втором считывании элементы первой градации яркости (первой после уровня черного), включаются, при третьем считывании выключаются элементы второй градации яркости и т.д. При последнем К-ом цикле считывания включенными остаются лшпь з лементы памяти самой старше градации яркости.

Выбор значений N, X, Y, G, т, п, q определяется Форматом поля изображения и типом применяемой оперативной памяти. Так как в основу устройства заложены принципы цифровой, техники, то данные значения оптимально . выбирать кратными 2 , где d « 1,2,3.

Например, при Формате изображения и оперативной буферной памят с емкостью 4096 бит, можно выбрать следующие значения:

(Х.п)() 512У512

Допустим G-4, q-16, , тогда

x.Ai .LL2. 4viL. IIL 8

n 128 q 16

(8 - число входов блока 24 одной групы развертки),

4096 4096

32

m

128

n

отсюда

V 512 512 ., « XY - 4 Чб 64.

Таким образом, устройство позволяет обеспечить воспроизведение изображения на матричном экране, причем структура предлагаемого устройства упрошена по сравнению с известным за счет исключения реверсирования развертки. Формула изобретения

Устройство для воспроизведения изображения на матричном экране, содержащее видеоцифровой преобразователь, вход которого является входом устройства, первый и второй выходы видеоцифрового преобразователя соединены соответственно с первым и вторым входами синхронизации блока управления , N групп первых и вторых блоков оперативной памяти, выходы которых объединены и соединены соответственно с входами N блоков декодирования, выходы которых соединены соответственно с входами N блоков выходных регистров, выходы которых соединены соответственно с информационными входами блока отображения, адресные входы всех N первых блоков оперативной памяти объединены поразрядно и соединены с первой группой выходов блока управления, вторая группа выходов которого соединена с объединенными поразрядно адресными входами всех N вторых блоков оперативной памяти, первые входы управления которых объединены и соединены с первым выходом блока управления, первые входы управления всех N первых блоков оперативной памяти объединены и соединены с вторым выходом блока управления, третья группа выходов блока управления подключена к соответствующим управляющим входам каждого из N блоков декодирования, третий выход блока управления соединен с первым входом синхронизации каждого

из N блоков выходш пс регистров, четвертый выход блока управления соединен с йторым входом синхронизации каждого из N блоков выходных регистров, инйюрмационньте входы первых и вторых блоков оперативной памяти объединены поразрядно, отличающееся тем, что, с целью устранения мерцания яркости быстро изменяющегося изображения за счет введения дополнительного цикла развертки, в него введен блок промежуточной памяти, первый, второй и третий Bxopw синхронизации которого соединены соответственно с третьим, четвертым и пятым выходами видеоцифрового преобразователя., информационные выходы которого подключены к соответствзтопшм информационным входам блока промежуточной памяти, информационные входы всех Y первых и Y вторьж блоков оперативной памяти в каждой из X групп, где X N/Y, объединены и подключены к соответствующим группам выходов блока промежуточной памяти, вторые входы управления N первых блоков оперативной памяти образуют группу из Y входов и подключены к четвертой группе выходов блока управления, вторые входы управления N вторых блоков оперативной памяти образуют группу из Y входов и подключены к пятой группе выходов блока управления, входы развертки блока отображения соединены с шестой группой выходов блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения изображения | 1986 |

|

SU1334395A1 |

| Устройство для воспроизведения изображения | 1980 |

|

SU1085014A1 |

| Устройство для воспроизведения цветного изображения | 1988 |

|

SU1589429A1 |

| Устройство для воспроизведения изображения | 1989 |

|

SU1662016A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Устройство для отображения информации на экране видеоконтрольного блока | 1988 |

|

SU1562954A1 |

| Многоканальный преобразователь амплитуды телевизионного сигнала во временной интервал | 1983 |

|

SU1124452A1 |

| Устройство отображения информации на экране телевизионного индикатора | 1986 |

|

SU1425768A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

Изобретение относится к телевидению. Цель изобретения - устранение мерцания яркости быстро изменяющегося изображения. Устройство для воспроизведения изображения на матричном экране содержит блок источников 1 видеосигнала, видеоцифровой преобразователь 2, блок 4 промежуточной памяти, блок 10 управления, блоки 11 и 12 оперативной памяти, блоки 19 декодирования, блоки 21 выходных регистров и блок 24 отображения. Устройство работает в двух независимых режимах: в режиме записи информации в блоки оперативной памяти и в режиме считывания информации из блоков оперативной памяти с последующей разверткой изображения на блоках 24 отображения. Оба процесса совмещены по времени, т.е. в один, например, блоки 11 оперативной памяти происходит запись информации, а с других блоков 12 оперативной памяти - считывание, и наоборот. Цель достигается за счет введения дополнительного цикла развертки. 5 ил., 1 табл.

Коммутатор 39 (ВЦП.2)

Коммутатор 45 (блок 4 промежуточной памяти)

Коммутатор 47 (блок 10 управления)

генератора 40 Тактовый сигнал генератора 41 Лог.0

Q О

Тактовый сигнал генератора 40 Тактовый сигнал . генератора 41 Информационные

10х

Q1 сигналы с выхода регистра 43-1 Информационные

Q

.ХОх сигналы свыхода регистра 43-Х Информационные

10х

Q1 сигналы с выхода регистра 44-1

QI...XQx Информационные сигналы с выхода регистра 44-Х

кси

Q1

Тактовый сигнал

Q2 Q3 генератора 40 КОТ и сигнал конца цикла с выхода Формирователя 54

Тактовый сигнал

Q4 генератора 46

13

Коммутатор 48 (блок 10 управления)

Коммутатор 53 (блок управления)

Коммутатор 55 1

О

Коммутатор 56 1

О

14

1596487

Продолжение таблицы

Q1

КСИ и сигнал конца цикла с выхода Формирователя 54 Тактовый сигнал

Q2 генератора 46 КСИ

Q3. Qt

Тактовый сигнал генератора 40

Ql Тактовый сигнал генератора 40 Лог,1 V

Q2 Лог. 1

Ql Тактовый сигнал

Q2 генератора 40

IQ1...1QY Сигналы с соответствующих выходов дешифратора 61

Инверсный сигнал

2Q...2QY конца цикла с выхода Формирователя 54

IQl...IQY

Инверсный сигнал конца цикла с выхода Формирователя 54

2Ql.i.2QY

Сигналы с соответствующих выходов дешифратора 61 Q . Сигнал с выхода схемы 64 выделения кода Q. Сигнал с выхода схемы 65 вьщеле.ния кода

Q 0 Сигнал с выхода 67 выделения кода Сигнал с выхода схемы 66 выделения кода

7J

лл -ЧУ

| Устройство для воспроизведения изображения | 1986 |

|

SU1334395A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-09-30—Публикация

1987-09-14—Подача