сл

CD

00

1

Изобретение относится к электро- технике и может быть использовано во вторичных источниках электропитания радиоэлектрбнной аппаратуры.

Целью изобретения является обеспечение универсальности интегральной микросхемы стабилизатора постоянного напряжения.

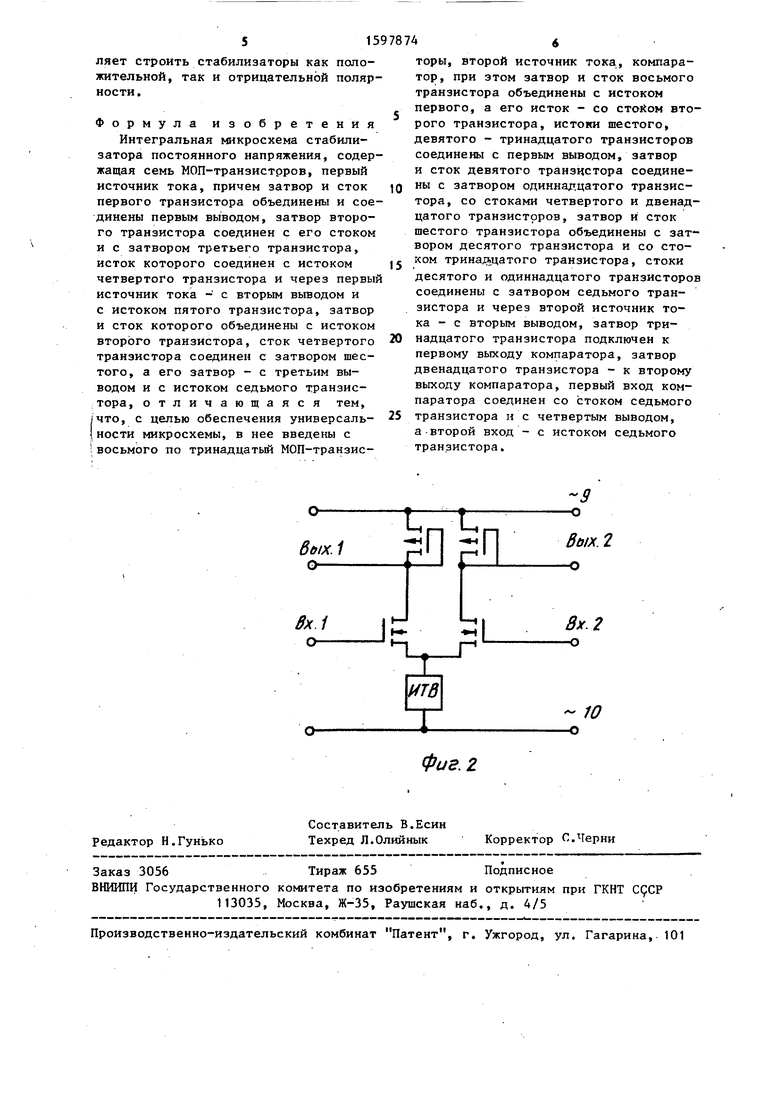

На фиг. 1 представлена пpинципиaль ная электрическая схема устройства; на фиг. 2 - электрическая схема компаратора .

Интегральная микросхема стабилизатора постоянного напряжения, содержит первый 1 седьмой 7 МОП-транзисторы, первый источник 8 тока, затвор транзистора 1 соединен с его стоком и первым выводом 9, затвор транзистора 2 соединен с его стоком и с затво- ром транзистора 3, исток которого соединен с истоком транзистора 4 и через первый источник тока 8 - с вторым выводом 10 и с истоком транзистора |5, затвор и сток которого объединены ,с истоком транзистора 2, сток транзистора 4 соединен с затвором и стоком транзистора 6, его затвор - с третьим выводом 11 и с истоком транзистора 7, восьмой 12 - тринадцатый

17МОП-транзисторы, второй источник

18тока, компаратор 19, затвор и

I сток транзистора 12 объединены с истоком. транзистора 1, а его исток - со стоком транзистора 2, истоки шее- того 6, девятого 13 - тринадцатого 17. транзисторов соединены р выводом 9, затвор и сток транзистора 13 соединены с затвором транзистора 15, а также со стоками транзисторов 4 и 16, затвор и сток транзистйра 6 объединены с затвором транзистора 14 и стоком транзистора 17, стоки транзисторов 14 и 15 соединены с затвором транзистора 7 и через второй источник тока 18 - с выводом 10, затвор транзистора 17 подключен к первому выходу 20 компаратора 19, затвор двенадцатого 16 транзистора - к второму выходу 21 компаратора 19, пер- вый вход 22 компаратора 19 соединен со стоком седьмого транзистора 7 и с четвертым вьгоодом 23, а второй вхо 24 - с истоком седьмого транзистора 7.

Для получения положительного напржения выводы 9 и 23 микросхемы сое- .диняются с источником положительного напряжения, вывод 10 - с общей

шиной, а нагрузка подключается к выводу 11. При этом компаратор 19 находится в первом устойчивом состоянии, т.е. на выходе 21 компаратора 19 устанавливается высокий потенциал а на выходе 20 - низкий. Такое состояние компаратора 19 обеспечивает пребывание транзистора 17 в линейной области своей выходной характеристики и отсечку транзистора 16. При этом на затворе транзистора 3 появляется опорное напряжение положительной полярности. На выводе 11 появляется требуемое выходное напряжение одноименной полярности. Для получения стабилизатора напряжения отрицательной полярности выводы 10 и 11 микросхемы подключаются к отрицательной шине питания, вывод 9 - к общей (положительной шине питания, а вывод 23 - к нагрузке. В этом случае компаратор 19 изменяет свои выходные напряжения так, что на выходе 20 устанавливается высокий потенциал, а на выходе 21 - низкий потенциал. В результате замыкается ключ на транзисторе 16 и размыкается ключ на транзисторе 17, что обеспечивает необходимую фазировку в схеме.

Регулирующий транзистор 7 в таком устройстве должен быть симметричным (двунаправленным). В этом случае при смене полярности выходного напряжени сток и исток транзистора 7 меняются местами. Поскольку входы компаратора 19 .соединены с истоком и стоком, транзистора 7, то изменяется полярность входного напряжения компаратора 19, что дает возможность изменять функционирование микросхемы.

Работа устройства в составе стабилизатора происходит следующим образом.

Усилитель сигнала рассогласования (на транзисторах 3 и 4) выделяет разность напряжений между источником I опорного напряжения (транзисторы 1, 2, 5, 12) и выходным напряжением (на выходе 11), усиливает ее и через согласующие цепи воздействует на управляющий вход регулирующего транзистора 7 таким образом, что при изменении влияющих величин выходное напряжение стабилизатора остается на заданном уровне.

Таким образом, предлагаемое устройство по сравнению с известным является универсальным, так как позволяет строить стабилизаторы как положительной, так и отрицательной полярности.

Формула изобретения

Интегральная микросхема стабилизатора постоянного напряжения, содержащая семь МОП-транзисторов, первый источник тока, причем затвор и сток первого транзистора объединены и соединены первым выводом, затвор второго транзистора соединен с его стоком и с затвором третьего транзистора, исток которого соединен с истоком четвертого транзистора и через первый источник тока - с вторым вьгаодом и с истоком пятого транзистора, затвор и сток которого объединены с истоком второго транзистора, сток четвертого транзистора соединен с затвором шестого, а его затвор - с третьим выводом и с истоком седьмого транзистора, отличающаяся тем, что, с цепью обеспечения универсаль- ности микросхемы, в нее введены с восьмого по тринадцатый МОП-транзис

о 5

5

0

торы, второй источник тока, компаратор, при этом затвор и сток восьмого транзистора объединены с истоком первого, а его исток - со стоЛом второго транзистора, истоки шестого, девятого - тринадцатого транзисторов соединены с первым выводом, затвор и сток девятого транзистора соединены с затвором одиннадцатого транзистора, со стоками четвертого и двенадцатого транзисторов, затвор и сток шестого транзистора объединены с затвором десятого транзистора и со стоком тpинa цaтoгo транзистора, стоки десятого и одиннадцатого транзисторов соединены с затвором седьмого транзистора и через второй источник тока - с вторым выводом, затвор тринадцатого транзистора подключен к первому выходу компаратора, затвор двенадцатого транзистора - к второму выходу компаратора, первый вход компаратора соединен со стоком седьмого транзистора не четвертым выводом, а-второй вход - с истоком седьмого транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСТОЧНИК СТАБИЛЬНОГО ТОКА ИЛИ НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 2022 |

|

RU2795478C1 |

| Стабилизатор постоянного напряжения | 1987 |

|

SU1467549A1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| ЧИП УСИЛИТЕЛЯ КЛАССА D С ФУНКЦИЕЙ ОГРАНИЧЕНИЯ КОЭФФИЦИЕНТА ЗАПОЛНЕНИЯ И ЕГО УСТРОЙСТВО | 2014 |

|

RU2598336C1 |

| ЧЕТЫРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ | 2022 |

|

RU2784457C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ЛЕВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2021 |

|

RU2776031C1 |

| Операционный усилитель | 1990 |

|

SU1741255A1 |

Изобретение относится к электротехнике и может быть использовано во вторичных источниках электропитания радиоэлектронной аппаратуры. Цель - обеспечение универсальности интегральной микросхемы стабилизатора постоянного напряжения. Устройство содержит регулирующий транзистор 7, усилитель сигнала рассогласования на транзисторах 3, 4, источник опорного напряжения на транзисторах 1, 2, 5, 12. Введение компаратора 19, транзисторных ключей 16 и 17 и подключение входа компаратора параллельно регулирующему транзистору 7, а выходов - к входам транзисторов 16 и 17 позволяет автоматически изменять фазировку схемы и тем самым строить стабилизаторы напряжения как положительной, так и отрицательной полярности, т.е. сделать микросхему универсальной. 2 ил.

| Двухполярный стабилизатор постоянного напряжения | 1983 |

|

SU1133588A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Стабилизатор постоянного напряжения | 1984 |

|

SU1233125A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-10-07—Публикация

1988-05-19—Подача