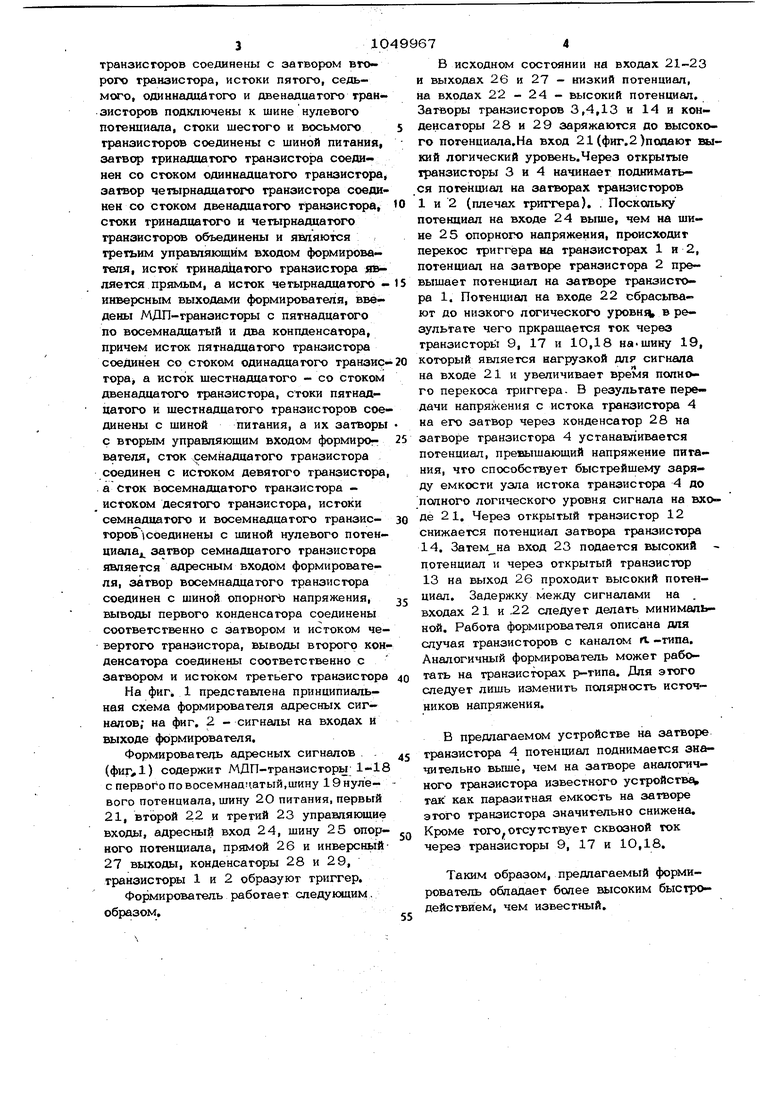

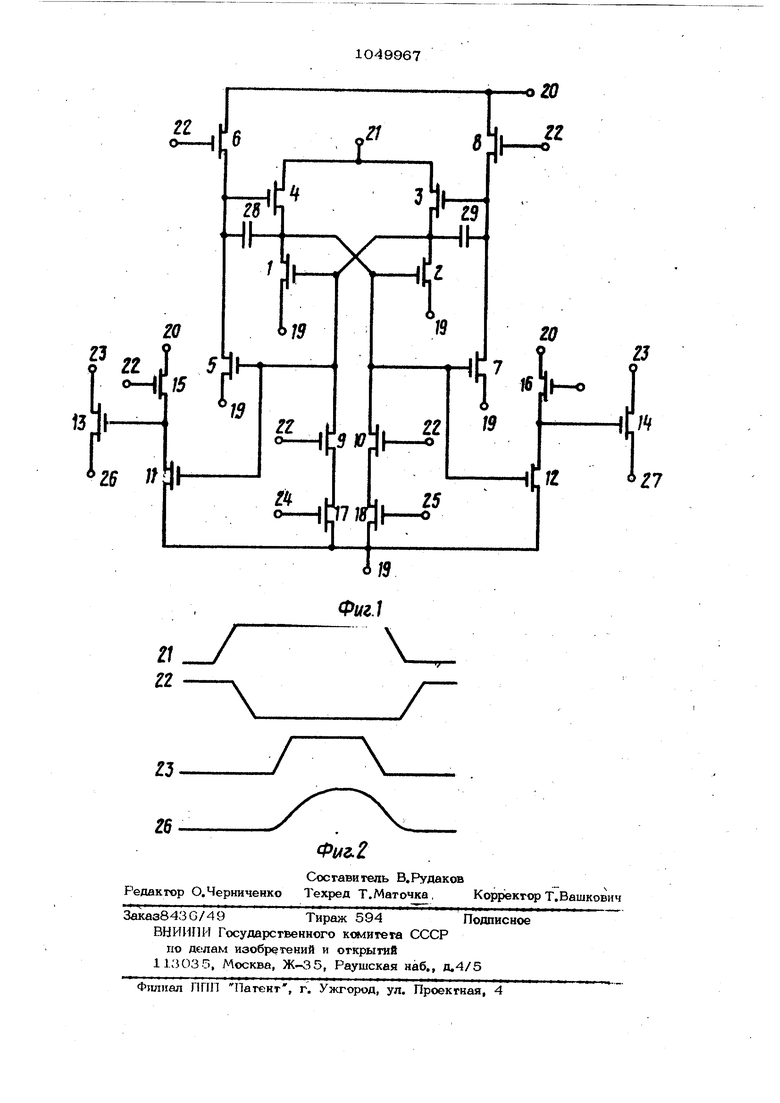

Изобретение относится к вычислительной технике и может быть использовано в больших HHTerpanbtn-jx схемах (БИС) на МДП-транзисторах. Известен формирователь андресных сигналов, содержащий 12 транзисторов, шины земли, питания и опорного потенциала, входную адресную шину, шины прямого и инверсного сигналов, две управляющие шины, причем истоку первого и второго транзисторов соединены с шиной земли, затворы первого и второго транзисторов соединены с входной адресной шиной н с шиной опорного напряжения соответственно, сток первого гранзисгора соединен с затворами треть го и четвертого, с истоком пятого и со стоком шестого транзисторов, сток второго транзистора соединен с затворами шестого и седьмого, с истоком восьмого и со стоком третьего транзисторов, ист ки третьехх), четвертого, шестогч) и седь мого транзисторов соединены с шиной земли, затворы восьмого и девятого транзисторов соединены с истоком десятого и со стоком четвертого транзисторов, затворы пятого и одиннадцатого транзисторов соединены с истоком двенадцатого и со стоком седьмого транзисторов, стоки десятого и двенадцатого транзис оров соединены с шиной питания, стоки пятого и восьмого тран зисторов - с первой управпяюшей шиной, стоки одиннадцатого и девятого транзисторов соединены со второй управляющей шиной, а их истоки - с инверсным и с прямым адресными выходами соответственно, затворы десятого и двенадцатого транзисторов соединены с третьей управ ляющей шиной 1 . Недостатком данного адресного формирователя является значительная потребляемая мощность и недостаточное быстродействие. Наиболее близким к изобретению по технической сущности является формирователь адресных сигналов, который содержит шины земли и питания, три управляющие шины, шину опорного напряже ния, входную адресную шину, выходные шины прямого и инверсного адресного сигнала, двенадцать транзисторов, причем истоки первого и второго транзисторов соединены с шиной земли, стоК первого и исток третьего транзисторов объединены, затвор первого транзистора является адресным входом, сток второго н исток четвертого транзисторов объединены, зат вор второго транзистора соединен с шино опорного напряжения, сгок третьего транзистора соединен с затворами.1ятого, шестого, с истоком седьмого и со стоком восьмого транзисторов, сток четвертого транзистора соединен с затворами восьмого и девятого, с истоком Десятого и со стоком шестого транзисторов, затворы третьего, десятого и одиннадцатого транзисторов соединены со стоком пятого и с истоком двенадцатого .транзисторов, затворы четвертого, седьмого и тринадцатого соединены со стоком девятого и с истоком четырнадцатого транзисторов, стоки двенадцатого и четырнадцатого транзисторов соединены с шиной питания, а их их затворы - с первой управляюшей шиной, стоки одиннадцатого и тринадцатого транзисторов соединены с второй управляюшей шиной, а их истоки - с прямым и инверсным адресными выходами соответственно, истоки пятого, шестого, восьмого и девятого транзисторов соединены с шиной земли, стоки седьмого и десятого транзисторов соединены с третьей управлякдцей шиной 2 , Однако известный формирователь обладает низким быстродействием, которое определяется значительной задержкой, необ ходимой для усиления разбаланса плеч триггера, собранного на шестом и восьмом транзисторах. 11ель изобретения - повышение быстродействия формирователя адресных сигналов. иоставленная цель достигается тем, что в формирователь адресных сигналов, содержащий МДП-транзисторы, причем истоки первого и второго транзисторов соединены с шиной нулевого потенциала, затвор первого транзистора соединен со стоком второго и с истоком третьего транзисторов, завтор второго транзистора соединен со стоком первого и с истоком четвертого транзисторов, стоки третьего и четвертого транзисторов объединены и являются первым управляк щим входом формирователя, затвор четвертого транзистора соединен со стоком пятого и с истоком шестого транзисторов, затвор .1 третьего транзистора соединен со стоком седьмого и с истоком восьмого транзисторов, затворы шестого, восьмого, девятого и десятого транзисторов объединены и являются вторым управляющим входом формирователя, за т-, воры пятого и одиннадцатого и сток девятого транзисторов соединены с затво ром первого транзистора, затворы седьмого и двенадцатого и сток десятого транзисторов соединены с затвором второго транзистора, истоки пятого, седьмого, одиннадцатого и двенадцатого транзисторов подключены к шине нулевого потенциала, стоки шестого и восьмого транзисторов соединены с шиной питания, затвор тринадцатого транзистора соединен со стоком одиннадцатого транзистора, затвор четырнадцатого транзистора соединен со стоком двенадцатого транзистора, стоки тринадцатого и четырнадцатого транзисторов объединены и яшяются третьим управляющим входом формирователя, исток тринадцатого транзистора является прямым, а исток четырнадцатого инверсным выходами формирователя, введены МДП-транаисторы с пятнадцатого по восемнадцатый и два конпденсатора, причем исток пятнадцатого транзистора соединен со стоком одинадцатого транзистора, а исток шестнадцатого - со стоком двенадцатого транзистора, стоки пятналцатого и шестнадцатого транзисторов соединены с шиной питания, а их затворы с вторым управляющим входом формирогвателя, сток семнадцатого транзистора соединен с истоком девятого транзистора, а Сток восемнадцатого транзистора истоком десятого транзистора, истоки семнадцатого и восемнадцатого транзисторов соединены с шиной нулевого потенциала затвор семнадцатого транзистора является адресным входом формирователя, затвор восемнадцатого транзистора соединен с шиной опорногЪ напряжения, выводы первого конденсатора соединены соответственно с затвором и истоком че- вертого транзистора, выводы второго конденсатора соединены соответственно с затвором и истоком третьего транзистора На фиг 1 представлена принципиальная схема формирователя адресных сигналов, на фиг. 2 - сигналы на входах и выходе формирователя. Формирователь адресных сигналов . . (фиг,1) содержит МДП-транзисторы 1-18 с первого по восемнадцатый,шину 19нуле- вого потенциала, шину 2О питания, первый 21, второй 22 и третий 23 управляющие входы, адресный вход 24, шину 25 опорного потенциала, прямой 26 и инверснь1й27 выходы, конденсаторы 28 и 29, транзисторы 1 и 2 образуют триггер. Формирователь работает следующим, образом. В исходном состоянии на входах 21-23 и выходах 26 к 27 - низкий потенциал, на входах 22 - 24 - высокий потенциал. Затворы транзисторов 3,4,13 и 14 и конденсаторы 28 и 29 заряжаются до высокого потенциала.На вход 21 (фиг.2)подают вы кий логический уровень.Через открытые транзисторы 3 к 4 начинает поднимат1 ся потенциал на затворах транзисторов 1 и 2 (плечах триггера), . Поскольку потенциал на входе 24 выше, чем на шине 25 опорного напряжения, происходит перекос триггера на транзисторах 1 и 2, потенциал на затворе транзистора 2 превышает потенциал на затворе транэистора 1. Потенциал на входе 22 сбрасывают До низкого логического ypoBHiv в результате чего пркрашается ток через транзисторй 9, 17 и 10,18 на-шину 19, который является нагрузкой для сигнала на входе 21 и увеличивает время попного перекоса триггера. В результате передачи напряжения с истока транзистора 4 на его затвор через конденсатор 28 на затворе транзистора 4 устанавливается потенциал, превышающий напряжение питания, что способствует быстрейшему заряду емкости узла истока транзистора 4 до полного логического уровня сигнала на вхо открытый транзистор 12 снижается потенциал затвора транзистора . Затем на вход 23 подается высокий потенциал и через открытый транзистор 13 на выход 26 проходит высокий потенциал. Задержку между сигналами на входах 21 и .22 следует делать минимальной. Работа формирователя описана для случая транзисторов с каналом rt -типа. Аналогичный формирователь может работать на транзисторах р-типа. Лля этого следует лишь изменить полярность источников напряжения. В предлагаемом устройстве на затворе транзистора 4 потенциал поднимается значительно выше, чем на затворе аналогичного транзистора известного устройству так как паразитнеш емкость на затворю этого транзистора значительно снижена, Кроме того отсутствует сквозной ток через транзисторы 9, 17 и 10,18, Таким образом, предлагаемый формирователь обладает более высоким быстродействием, чем известный.

-oZO

Zl

го

5

h-o

Й

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1982 |

|

SU1238230A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2016 |

|

RU2628152C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ЛЕВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2021 |

|

RU2776031C1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

| Аналоговый четырехквадрантный перемножитель | 1988 |

|

SU1504655A1 |

| Комбинационный сумматор | 1988 |

|

SU1596321A1 |

ФОРМИРОВАТЕЛЬ АДРЁС ПЫХ СИГНАЛОВ, содержащий МД.П-транэисторы, причем истоки первого и второго транзисторов соединены с .шиной нулевого потенциала, затвор первого транзистора соединен со.стоком второго и с истоком третьего транзисторо1в, затвор второт-о транзистора соединен со стоком первого и о истоком четвертого транзисторов, стоки третьего и четвертого транзисторов объединенные и явля- . ются первым управляющим входом формирователя, затвор четвертого транзистора соединен со стоком пятого и с истоком шестого транзисторов, затвор третьего транзистора соединен со стоком седьмого и с истоком восьмого транзисторов, затворы шестого, восьмого, девятого и де сятого транзисторов объединены и являют- ся вторым управляющим входом формирователя, затворы пятого и одиннадцатого и сток девятого транзисторов соединены . с затвором первого транзистора, затворь седьмого и двенадцатого и сток десятого транзисторов соединены с затвором второго транзистора, истоки пятого, седьMof-o, одиннадцатого и двенадцатого транзисторов подключены к шине нулевого потенциала, стоки шестого и восьмого транзисторов соединены с шиной питания, затвор тринадцатого транзистора соединен со стоком одиннадцатого транзистора, затвор четырнадцатого транзистора соединен ср стоком двенадцатого транзистора, стоки тринадцатого и четырнадцатого транзисторов объединены и являются третьим управляющим входом формирователя, исток тринадцатого транзистора является прямым, а исток четырнадцатого - инверсным выходами формирователя, отличающи й-- с я тем, что, с целью повышения быстродействия формирователя, в него введены МДП-транзисторы с пятнадцатого по во- g семнадцатый и два конденсатора, причем (Л исток пятнадцатого .транзистора соединен со стоком одиннадцатого транзистора, а исток шестнадцатого - со стоком двенадцатого транзистора, а истоки пятнадцатого и шестнадцатого транзисторов соединены с шиной питания, а их затворы - с вторым управляющим входом форh мирователя, сток семнадцатого транзиссо тора соединен с истоком девятого транIUD 05 зистора, а сток восемнадцатого транзистора - с истоком десятого транзистора, истоки семнадцатого и восемчодца того транзисторов соединены с дншой нулевого потенциала, затвор семнадцатого транзистора является адресным входом формирователя, затвор росемнадцатого транзистора соединен с шиной опорного напряжения,выводы первого конденсатора соединены соответственно с затвором и истоком четвертого транзистора,- выводы второго конденсатора соединены соответственно с затвором и истоком третьего транзистора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроника, 1978, ,№ 7, с | |||

| Коридорная многокамерная вагонеточная углевыжигательная печь | 1921 |

|

SU36A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1983-10-23—Публикация

1982-07-05—Подача