Предлагаемое изобретение относится к цифровой вычислительной технике и может быть использовано при создании устройств, использующих функции ИСКЛЮЧАЮЩЕЕ-ИЛИ и(или) ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ, например, в схемах контроля четности и(или) нечетности и других многоразрядных цифровых устройств.

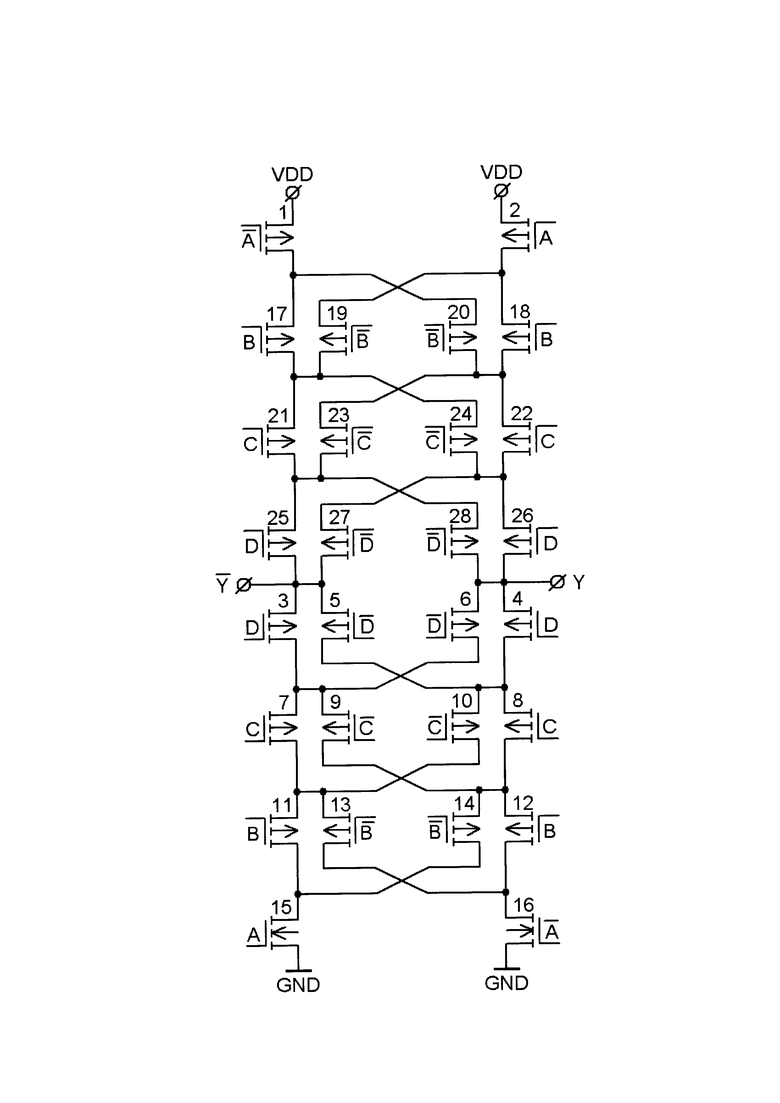

Известен 4-входовой вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ (4-input XOR gate) [1] (Стр. 339, Рис. 9.20 (c)).

Данный 4-входовой вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ содержит триггерную «защелку», выполненную на первом и втором (1,2) МОП транзисторах Р-типа, и МОП транзисторы N-типа с третьего по шестнадцатый (3-16), вывод питания высокого уровня напряжения VDD, вывод питания низкого уровня напряжения GND, прямые А, В, С и D и инверсные  входы и выходы

входы и выходы

Недостатком известной схемы является низкое быстродействие. Для обеспечения устойчивой работы указанного 4-входового вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ, построенного на триггерной «защелке», требуется смещение вниз передаточных характеристик двух «полу-защелок», построенных на МОП транзисторах Р-типа 1 и 2. Данное условие достигается существенным уменьшением проводимости цепей сети подтяжки вверх (Pull-Up Network) на транзисторах (1,2) по сравнению с проводимостью цепей сети подтяжки вниз (Pull-Down Network) на транзисторах с третьего по шестнадцатый (3-16). Обеспечение этого условия приводит к увеличению времени переходного процесса при переключении сигнала из низкого уровня напряжения GND в напряжение высокого уровня VDD и, следовательно, к уменьшению общего быстродействия известного 4-входового вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ, вследствие увеличения задержки времени формирования сигнала высокого уровня напряжения на выходах

Кроме того, динамический ток потребления известного 4-входового вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ увеличивается из-за повышенного времени переходного процесса, что приводит к дополнительному перегреву элементов схемы и снижает общую надежность схемы.

Задачей предлагаемого изобретения является повышение быстродействия известного 4-входового вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ, и повышение надежности за счет уменьшения его динамического тока потребления.

Поставленная задача достигается тем, что в известный 4-входовой вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ, содержащий МОП транзисторы Р-типа первый и второй, N-типа с третьего по шестнадцатый, вывод питания высокого уровня напряжения VDD, соединенный с истоками первого и второго транзисторов, вывод питания низкого уровня напряжения GND, соединенный с истоками пятнадцатого и шестнадцатого транзисторов, прямые входы А, В, С, D, инверсные входы  выход Y, соединенный со стоками четвертого и шестого транзисторов и выход

выход Y, соединенный со стоками четвертого и шестого транзисторов и выход соединенный со стоками третьего и пятого транзисторов, в котором затворы пятнадцатого и шестнадцатого транзисторов соединены, соответственно, с входами

соединенный со стоками третьего и пятого транзисторов, в котором затворы пятнадцатого и шестнадцатого транзисторов соединены, соответственно, с входами  одиннадцатого и двенадцатого - с входом В, тринадцатого и четырнадцатого - с входом

одиннадцатого и двенадцатого - с входом В, тринадцатого и четырнадцатого - с входом  седьмого и восьмого - с входом С, девятого и десятого - с входом

седьмого и восьмого - с входом С, девятого и десятого - с входом  третьего и четвертого - с входом D, пятого и шестого - с входом

третьего и четвертого - с входом D, пятого и шестого - с входом  сток пятнадцатого транзистора соединен с истоками одиннадцатого и четырнадцатого, сток шестнадцатого - с истоками двенадцатого и тринадцатого, сток одиннадцатого - со стоком тринадцатого и истоками седьмого и десятого, сток двенадцатого - со стоком четырнадцатого и истоками восьмого и девятого, сток седьмого - со стоком девятого и истоками третьего и шестого и сток восьмого - со стоком десятого и истоками четвертого и пятого, введены МОП транзисторы Р-типа с семнадцатого по двадцать восьмой, причем, затворы первого и второго транзисторов соединены, соответственно, с входами

сток пятнадцатого транзистора соединен с истоками одиннадцатого и четырнадцатого, сток шестнадцатого - с истоками двенадцатого и тринадцатого, сток одиннадцатого - со стоком тринадцатого и истоками седьмого и десятого, сток двенадцатого - со стоком четырнадцатого и истоками восьмого и девятого, сток седьмого - со стоком девятого и истоками третьего и шестого и сток восьмого - со стоком десятого и истоками четвертого и пятого, введены МОП транзисторы Р-типа с семнадцатого по двадцать восьмой, причем, затворы первого и второго транзисторов соединены, соответственно, с входами  семнадцатого и восемнадцатого - с входом В, девятнадцатого и двадцатого - с входом

семнадцатого и восемнадцатого - с входом В, девятнадцатого и двадцатого - с входом  двадцать первого и двадцать второго - с входом С, двадцать третьего и двадцать четвертого - с входом

двадцать первого и двадцать второго - с входом С, двадцать третьего и двадцать четвертого - с входом  двадцать пятого и двадцать шестого - с входом D, двадцать седьмого и двадцать восьмого - с входом

двадцать пятого и двадцать шестого - с входом D, двадцать седьмого и двадцать восьмого - с входом  сток первого транзистора соединен с истоками семнадцатого и двадцатого транзисторов, а сток второго - с истоками восемнадцатого и девятнадцатого, сток семнадцатого - со стоком девятнадцатого и истоками двадцать первого и двадцать четвертого, сток восемнадцатого - со стоком двадцатого и истоками двадцать второго и двадцать третьего, сток первого транзистора соединен с истоками семнадцатого и двадцатого транзисторов, а сток второго - с истоками восемнадцатого и девятнадцатого, сток семнадцатого - со стоком девятнадцатого и истоками двадцать первого и двадцать четвертого, сток восемнадцатого - со стоком двадцатого и истоками двадцать второго и двадцать третьего,

сток первого транзистора соединен с истоками семнадцатого и двадцатого транзисторов, а сток второго - с истоками восемнадцатого и девятнадцатого, сток семнадцатого - со стоком девятнадцатого и истоками двадцать первого и двадцать четвертого, сток восемнадцатого - со стоком двадцатого и истоками двадцать второго и двадцать третьего, сток первого транзистора соединен с истоками семнадцатого и двадцатого транзисторов, а сток второго - с истоками восемнадцатого и девятнадцатого, сток семнадцатого - со стоком девятнадцатого и истоками двадцать первого и двадцать четвертого, сток восемнадцатого - со стоком двадцатого и истоками двадцать второго и двадцать третьего,

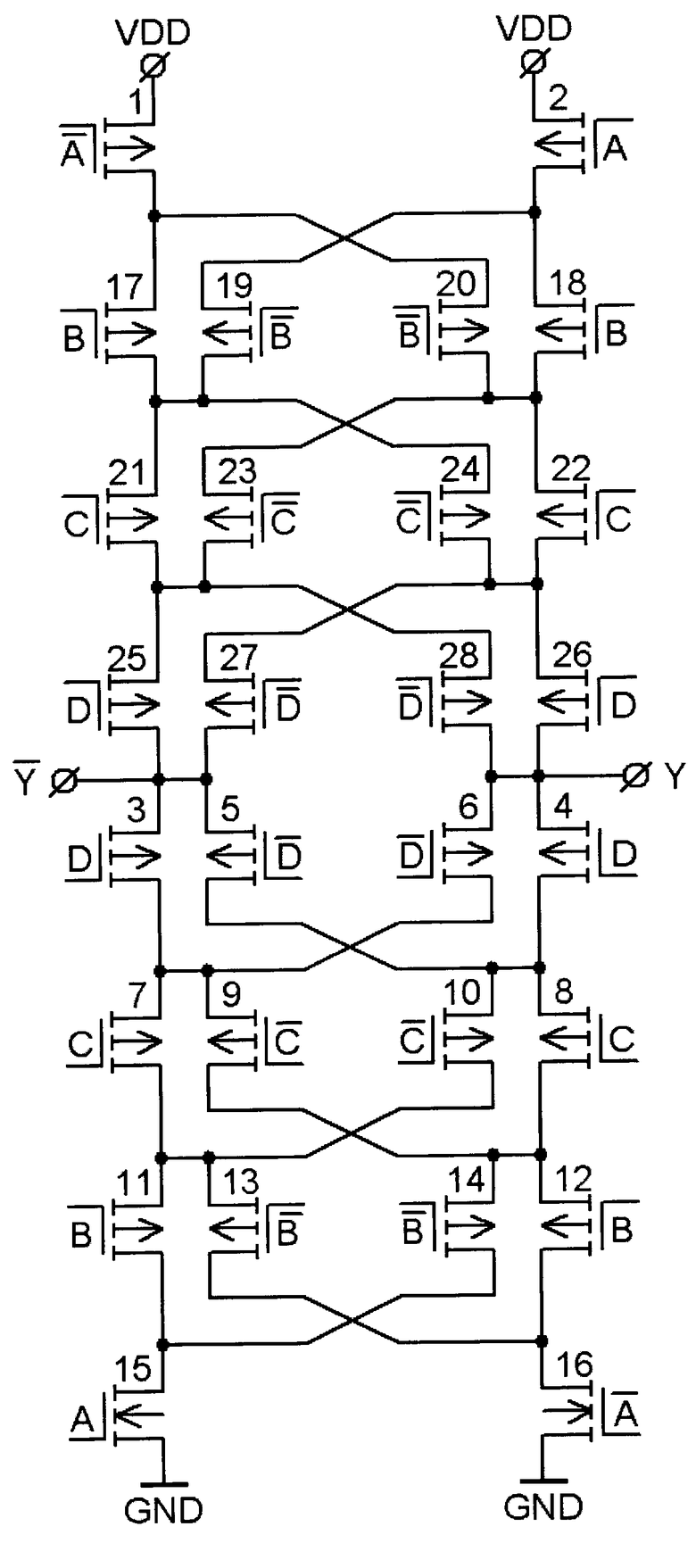

В результате чего, в предлагаемом Четырехвходовом КМОП логическом вентиле ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ, в отличие от известного 4-входового вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ, схема «защелки» исключена, а сеть подтяжки вверх (PUN) организована введением дополняющих (комплементарных) МОП транзисторов. Такое построение схемы позволяет оптимизировать соотношение проводимостей сетей подтяжки вверх (PUN) и подтяжки вниз (PDN) и тем самым повысить быстродействие Четырехвходового КМОП логического вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ за счет уменьшения времени переходного процесса при переключении выходных сигналов из низкого уровня напряжения GND в высокий VDD. Кроме того, так как время переходного процесса уменьшено, динамический ток потребления снижен. Снижение величины динамического тока потребления уменьшает избыточный перегрев элементов схемы, что повышает надежность Четырехвходового КМОП логического вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ.

На Рисунке приведена схема предлагаемого Четырехвходового КМОП логического вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ.

Предлагаемый Четырехвходовой КМОП логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ содержит МОП транзисторы Р-типа первый и второй (1,2) и с семнадцатого по двадцать восьмой (17-28), МОП транзисторы N-типа с третьего по шестнадцатый (3-16), вывод питания высокого уровня напряжения VDD, соединенный с истоками транзисторов первого и второго (1,2), вывод питания низкого уровня напряжения GND, соединенный с истоками транзисторов пятнадцатого и шестнадцатого (15,16), прямые входы А, В, С и D, инверсные входы  выход Y, соединенный со стоками транзисторов четвертого, шестого, двадцать шестого и двадцать восьмого (4,6,26,28) и выход

выход Y, соединенный со стоками транзисторов четвертого, шестого, двадцать шестого и двадцать восьмого (4,6,26,28) и выход  соединенный со стоками транзисторов третьего, пятого, двадцать пятого и двадцать седьмого (3,5,25,27). Причем, затворы транзисторов второго и пятнадцатого (2,15) соединены с входом А, а первого и шестнадцатого (1,16) - с входом

соединенный со стоками транзисторов третьего, пятого, двадцать пятого и двадцать седьмого (3,5,25,27). Причем, затворы транзисторов второго и пятнадцатого (2,15) соединены с входом А, а первого и шестнадцатого (1,16) - с входом  одиннадцатого, двенадцатого семнадцатого и восемнадцатого (11,12,17,18) - с входом В, а тринадцатого, четырнадцатого, девятнадцатого и двадцатого (13,14,19,20) - с входом

одиннадцатого, двенадцатого семнадцатого и восемнадцатого (11,12,17,18) - с входом В, а тринадцатого, четырнадцатого, девятнадцатого и двадцатого (13,14,19,20) - с входом  седьмого, восьмого, двадцать первого и двадцать второго (7,8,21,22) - с входом С, а девятого, десятого, двадцать третьего и двадцать четвертого (9,10,23,24) - с входом

седьмого, восьмого, двадцать первого и двадцать второго (7,8,21,22) - с входом С, а девятого, десятого, двадцать третьего и двадцать четвертого (9,10,23,24) - с входом  третьего, четвертого, двадцать пятого и двадцать шестого (3,4,25,26) - с входом D, а пятого, шестого, двадцать седьмого и двадцать восьмого (5,6,27,28) - с входом

третьего, четвертого, двадцать пятого и двадцать шестого (3,4,25,26) - с входом D, а пятого, шестого, двадцать седьмого и двадцать восьмого (5,6,27,28) - с входом  сток первого (1) транзистора соединен с истоками транзисторов семнадцатого и двадцатого (17,20), а сток второго (2) - с истоками восемнадцатого и девятнадцатого (18,19), сток пятнадцатого (15) - с истоками одиннадцатого и четырнадцатого (11,14), а сток шестнадцатого (16) - с истоками двенадцатого и тринадцатого (12,13), сток семнадцатого (17) - со стоком девятнадцатого (19) и истоками двадцать первого и двадцать четвертого (21,24), сток восемнадцатого (18) - со стоком двадцатого (20) и истоками двадцать второго и двадцать третьего (22,23), сток одиннадцатого (11) - со стоком тринадцатого (13) и истоками седьмого и десятого (7,10), сток двенадцатого (12) - со стоком четырнадцатого (14) и истоками восьмого и девятого (8,9), сток двадцать первого (21) - со стоком двадцать третьего (23) и истоками двадцать пятого и двадцать восьмого (25,28), сток двадцать второго (22) - со стоком двадцать четвертого (24) и истоками двадцать шестого и двадцать седьмого (26,27), сток седьмого (7) -со стоком девятого (9) и истоками третьего и шестого (3,6) и сток восьмого (8) - со стоком десятого (10) и истоками четвертого и пятого (4,5).

сток первого (1) транзистора соединен с истоками транзисторов семнадцатого и двадцатого (17,20), а сток второго (2) - с истоками восемнадцатого и девятнадцатого (18,19), сток пятнадцатого (15) - с истоками одиннадцатого и четырнадцатого (11,14), а сток шестнадцатого (16) - с истоками двенадцатого и тринадцатого (12,13), сток семнадцатого (17) - со стоком девятнадцатого (19) и истоками двадцать первого и двадцать четвертого (21,24), сток восемнадцатого (18) - со стоком двадцатого (20) и истоками двадцать второго и двадцать третьего (22,23), сток одиннадцатого (11) - со стоком тринадцатого (13) и истоками седьмого и десятого (7,10), сток двенадцатого (12) - со стоком четырнадцатого (14) и истоками восьмого и девятого (8,9), сток двадцать первого (21) - со стоком двадцать третьего (23) и истоками двадцать пятого и двадцать восьмого (25,28), сток двадцать второго (22) - со стоком двадцать четвертого (24) и истоками двадцать шестого и двадцать седьмого (26,27), сток седьмого (7) -со стоком девятого (9) и истоками третьего и шестого (3,6) и сток восьмого (8) - со стоком десятого (10) и истоками четвертого и пятого (4,5).

В дальнейшем описании принято соглашение, что напряжение высокого уровня VDD соответствует напряжению логического уровня «1», а напряжение низкого уровня GND - напряжению логического уровня «0». Кроме того, принято что, напряжение логических уровней на инверсных входах  всегда инверсно относительно соответствующих напряжений логических уровней на прямых входах А, В, С и D. Поэтому в дальнейшем при описании работы схемы и в таблице истинности нет необходимости приводить значения напряжений логических уровней на инверсных входах

всегда инверсно относительно соответствующих напряжений логических уровней на прямых входах А, В, С и D. Поэтому в дальнейшем при описании работы схемы и в таблице истинности нет необходимости приводить значения напряжений логических уровней на инверсных входах

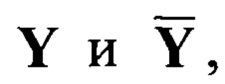

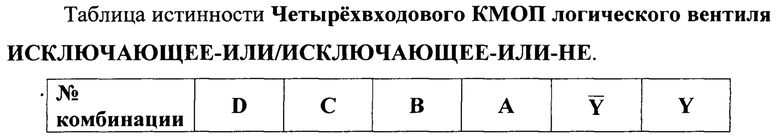

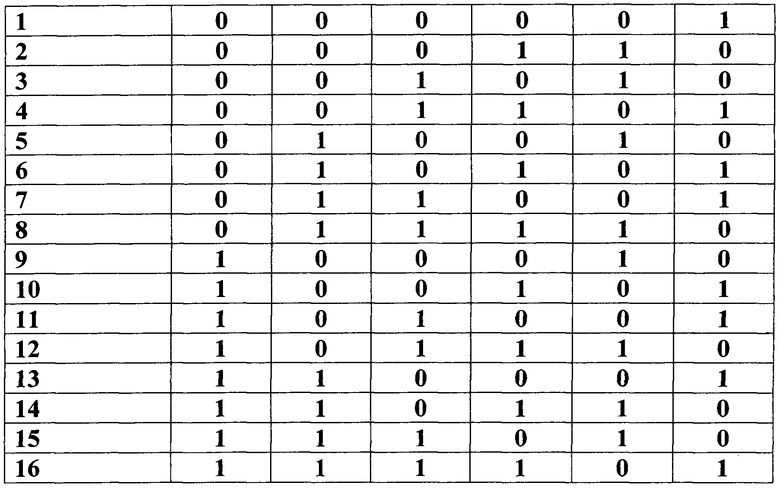

Предлагаемый Четырехвходовой КМОП логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ предназначен для формирования логических сигналов ИСКЛЮЧАЮЩЕЕ-ИЛИ и ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ на выходах  согласно представленной ниже в таблице истинности.

согласно представленной ниже в таблице истинности.

Таким образом, предлагаемый Четырехвходовой КМОП логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ представляет собой логическую схему комбинационного типа и работает следующим образом.

В комбинации №1 A=B=C=D=«0». При этом на выходе  через проводящие транзисторы 16, 13, 10 и 5 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 2,18, 22 и 26 - уровень напряжения логической «1».

через проводящие транзисторы 16, 13, 10 и 5 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 2,18, 22 и 26 - уровень напряжения логической «1».

В комбинации №2 А=«1» и В=С=D=«0». При этом на выходе  через проводящие транзисторы 1, 17, 21 и 25 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 15,14, 9 и 6 - уровень напряжения логического «0».

через проводящие транзисторы 1, 17, 21 и 25 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 15,14, 9 и 6 - уровень напряжения логического «0».

В комбинации №3 А=С=D=«0» и В=«1». При этом на выходе  через проводящие транзисторы 2, 19, 21 и 25 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 16,12, 9 и 6 - уровень напряжения логического «0».

через проводящие транзисторы 2, 19, 21 и 25 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 16,12, 9 и 6 - уровень напряжения логического «0».

В комбинации №4 А=В=«1» и С=D=«0». При этом на выходе через проводящие транзисторы 15, 11, 10 и 5 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 1, 20, 22 и 26 - уровень напряжения логической «1».

через проводящие транзисторы 15, 11, 10 и 5 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 1, 20, 22 и 26 - уровень напряжения логической «1».

В комбинации №5 А=В=D=«0» и С=«1». При этом на выходе  через проводящие транзисторы 2, 18, 23 и 25 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 16,13, 7 и 6 - уровень напряжения логического «0».

через проводящие транзисторы 2, 18, 23 и 25 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 16,13, 7 и 6 - уровень напряжения логического «0».

В комбинации №6 А=С=«1» и В=D=«0». При этом на выходе  через проводящие транзисторы 15, 14, 8 и 5 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 1,17, 24 и 26 - уровень напряжения логической «1».

через проводящие транзисторы 15, 14, 8 и 5 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 1,17, 24 и 26 - уровень напряжения логической «1».

В комбинации №7 А=D=«0» и В=С=«1». При этом на выходе  через проводящие транзисторы 16, 12, 8 и 5 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 2,19, 24 и 26 - уровень напряжения логической «1».

через проводящие транзисторы 16, 12, 8 и 5 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 2,19, 24 и 26 - уровень напряжения логической «1».

В комбинации №8 А=В=С=«1» и D=«0». При этом на выходе  через проводящие транзисторы 1, 20, 23 и 25 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 15,11,7 и 6 - уровень напряжения логического «0».

через проводящие транзисторы 1, 20, 23 и 25 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 15,11,7 и 6 - уровень напряжения логического «0».

В комбинации №9 А=В=С=«0» и D=«1». При этом на выходе  через проводящие транзисторы 2, 18, 22 и 27 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 16,13,10 и 4 - уровень напряжения логического «0».

через проводящие транзисторы 2, 18, 22 и 27 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 16,13,10 и 4 - уровень напряжения логического «0».

В комбинации №10A=D=«1» и B=C=«0». При этом на выходе  через проводящие транзисторы 15, 14, 9 и 3 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 1,17, 21 и 28 - уровень напряжения логической «1».

через проводящие транзисторы 15, 14, 9 и 3 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 1,17, 21 и 28 - уровень напряжения логической «1».

В комбинации №11 А=С=«0» и В=D=«1». При этом на выходе  через проводящие транзисторы 16, 12, 9 и 3 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 2,19, 21 и 28 - уровень напряжения логической «1».

через проводящие транзисторы 16, 12, 9 и 3 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 2,19, 21 и 28 - уровень напряжения логической «1».

В комбинации №12A=B- D=«1» и C=«0». При этом на выходе  через проводящие транзисторы 27, 22, 20 и 1 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 4, 10,11 и 15 - уровень напряжения логического «0».

через проводящие транзисторы 27, 22, 20 и 1 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 4, 10,11 и 15 - уровень напряжения логического «0».

В комбинации №13 А=В=«0» и С=D=«1». При этом на выходе  через проводящие транзисторы 16, 13, 7 и 3 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 2,18, 23 и 28 - уровень напряжения логической «1».

через проводящие транзисторы 16, 13, 7 и 3 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 2,18, 23 и 28 - уровень напряжения логической «1».

В комбинации №14A=C=D=«1» и В=«0». При этом на выходе  через проводящие транзисторы 1, 17, 24 и 27 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 15,14, 8 и 4 - уровень напряжения логического «0».

через проводящие транзисторы 1, 17, 24 и 27 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 15,14, 8 и 4 - уровень напряжения логического «0».

В комбинации №15 А=«0» и В=С=D=«1». При этом на выходе  через проводящие транзисторы 2, 19, 24 и 27 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 16,12, 8 и 4 - уровень напряжения логического «0».

через проводящие транзисторы 2, 19, 24 и 27 устанавливается уровень напряжения логической «1», а на выходе Y через проводящие транзисторы 16,12, 8 и 4 - уровень напряжения логического «0».

В комбинации №16A=B=C=D=«1». При этом на выходе  через проводящие транзисторы 15, 11, 7 и 3 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 1, 20, 23 и 28 - уровень напряжения логической «1».

через проводящие транзисторы 15, 11, 7 и 3 устанавливается уровень напряжения логического «0», а на выходе Y через проводящие транзисторы 1, 20, 23 и 28 - уровень напряжения логической «1».

Таким образом, предложенная схема выполняет необходимую функцию и за счет внесенных изменений в известную схему обладает более высоким быстродействием и более высокой надежностью.

Литература

1. Veste, N. Н. Е. CMOS VLSI Design: A Circuits and Systems Perspective. / Neil H. E. Veste, David Money Harris. - 4nd ed. - Boston: Pearson-Wesley, 2011. -838 p.Figure 9.20(c), page 339.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2802665C1 |

| КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2814896C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

| ЧИП УСИЛИТЕЛЯ КЛАССА D С ФУНКЦИЕЙ ОГРАНИЧЕНИЯ КОЭФФИЦИЕНТА ЗАПОЛНЕНИЯ И ЕГО УСТРОЙСТВО | 2014 |

|

RU2598336C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2016 |

|

RU2628152C1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| СУММАТОР | 2010 |

|

RU2435196C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при создании устройств, использующих функции ИСКЛЮЧАЮЩЕЕ-ИЛИ и(или) ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ, например, в схемах контроля четности и(или) нечетности и других многоразрядных цифровых устройств. Техническим результатом изобретения является повышение быстродействия 4-входового вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ, и повышение надежности за счет уменьшения его динамического тока потребления. Четырехвходовой КМОП логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ содержит МОП транзисторы P-типа первый, второй и с семнадцатого по двадцать восьмой, МОП транзисторы N-типа с третьего по шестнадцатый, вывод питания высокого уровня напряжения VDD, вывод питания низкого уровня напряжения GND, прямые входы А, В, С, D, инверсные входы  выход Y и выход

выход Y и выход  . 1 табл., 1 ил.

. 1 табл., 1 ил.

Четырехвходовой КМОП логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ, содержащий МОП транзисторы P-типа первый и второй, N-типа с третьего по шестнадцатый, вывод питания высокого уровня напряжения VDD, соединенный с истоками первого и второго транзисторов, вывод питания низкого уровня напряжения GND, соединенный с истоками пятнадцатого и шестнадцатого транзисторов, прямые входы А, В, С, D, инверсные входы  выход Y, соединенный со стоками четвертого и шестого транзисторов, и выход

выход Y, соединенный со стоками четвертого и шестого транзисторов, и выход  соединенный со стоками третьего и пятого транзисторов, причем затворы пятнадцатого и шестнадцатого транзисторов соединены, соответственно, с входами А и

соединенный со стоками третьего и пятого транзисторов, причем затворы пятнадцатого и шестнадцатого транзисторов соединены, соответственно, с входами А и  одиннадцатого и двенадцатого - с входом В, тринадцатого и четырнадцатого - с входом

одиннадцатого и двенадцатого - с входом В, тринадцатого и четырнадцатого - с входом  седьмого и восьмого - с входом С, девятого и десятого - с входом

седьмого и восьмого - с входом С, девятого и десятого - с входом  третьего и четвертого - с входом D, пятого и шестого - с входом

третьего и четвертого - с входом D, пятого и шестого - с входом  сток пятнадцатого транзистора соединен с истоками одиннадцатого и четырнадцатого, сток шестнадцатого - с истоками двенадцатого и тринадцатого, сток одиннадцатого - со стоком тринадцатого и истоками седьмого и десятого, сток двенадцатого - со стоком четырнадцатого и истоками восьмого и девятого, сток седьмого - со стоком девятого и истоками третьего и шестого и сток восьмого - со стоком десятого и истоками четвертого и пятого, отличающийся тем, что в него введены МОП транзисторы Р-типа с семнадцатого по двадцать восьмой, причем затворы первого и второго транзисторов соединены, соответственно, с входами

сток пятнадцатого транзистора соединен с истоками одиннадцатого и четырнадцатого, сток шестнадцатого - с истоками двенадцатого и тринадцатого, сток одиннадцатого - со стоком тринадцатого и истоками седьмого и десятого, сток двенадцатого - со стоком четырнадцатого и истоками восьмого и девятого, сток седьмого - со стоком девятого и истоками третьего и шестого и сток восьмого - со стоком десятого и истоками четвертого и пятого, отличающийся тем, что в него введены МОП транзисторы Р-типа с семнадцатого по двадцать восьмой, причем затворы первого и второго транзисторов соединены, соответственно, с входами  и А, семнадцатого и восемнадцатого - с входом В, девятнадцатого и двадцатого - с входом

и А, семнадцатого и восемнадцатого - с входом В, девятнадцатого и двадцатого - с входом  двадцать первого и двадцать второго - с входом С, двадцать третьего и двадцать четвертого - с входом

двадцать первого и двадцать второго - с входом С, двадцать третьего и двадцать четвертого - с входом  двадцать пятого и двадцать шестого - с входом D, двадцать седьмого и двадцать восьмого - с входом

двадцать пятого и двадцать шестого - с входом D, двадцать седьмого и двадцать восьмого - с входом  сток первого транзистора соединен с истоками семнадцатого и двадцатого транзисторов, а сток второго - с истоками восемнадцатого и девятнадцатого, сток семнадцатого - со стоком девятнадцатого и истоками двадцать первого и двадцать четвертого, сток восемнадцатого - со стоком двадцатого и истоками двадцать второго и двадцать третьего, сток двадцать первого - со стоком двадцать третьего и истоками двадцать пятого и двадцать восьмого, сток двадцать второго - со стоком двадцать четвертого и истоками двадцать шестого и двадцать седьмого, сток двадцать пятого - со стоком двадцать седьмого и выходом

сток первого транзистора соединен с истоками семнадцатого и двадцатого транзисторов, а сток второго - с истоками восемнадцатого и девятнадцатого, сток семнадцатого - со стоком девятнадцатого и истоками двадцать первого и двадцать четвертого, сток восемнадцатого - со стоком двадцатого и истоками двадцать второго и двадцать третьего, сток двадцать первого - со стоком двадцать третьего и истоками двадцать пятого и двадцать восьмого, сток двадцать второго - со стоком двадцать четвертого и истоками двадцать шестого и двадцать седьмого, сток двадцать пятого - со стоком двадцать седьмого и выходом  а сток двадцать шестого - со стоком двадцать восьмого и выходом Y.

а сток двадцать шестого - со стоком двадцать восьмого и выходом Y.

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| Преобразователь уровней сигналов на МДП-транзисторах | 1988 |

|

SU1538246A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

| US 4417161 A, 22.11.1983 | |||

| US 6469541 B2, 22.10.2002 | |||

| US 2007008014 A1, 11.01.2007 | |||

| RJ BAKER "CMOS: Circuit Design, Layout, and Simulation | |||

| Second Edition | |||

| IEEE Press Series on Microelectronic Systems, 2005.1039 p | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

Авторы

Даты

2022-11-25—Публикация

2022-06-23—Подача