Предлагаемое изобретение относится к цифровой вычислительной технике и может быть использовано при создании устройств, использующих функции ИСКЛЮЧАЮЩЕЕ ИЛИ и(или) ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, например, схемах контроля четности и(или) нечетности и многоразрядных сумматорах.

Известна схема трехвходового вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ (three-input XOR/XNOR gate) [1] (р.250, Fig.12.21).

Данная схема «трехвходового вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ содержит триггерную «защелку», выполненную на первом и втором (1, 2) МОП транзисторах Р-типа, и МОП транзисторы N-типа с третьего по двенадцатый (3-12), вывод питания высокого уровня напряжения VDD, вывод питания низкого уровня напряжения GND, прямые  и С и инверсные А, В и С входы и выходы XOR и XNOR.

и С и инверсные А, В и С входы и выходы XOR и XNOR.

Недостатком указанной выше схемы является низкое быстродействие. Для обеспечения устойчивой работы известного трехвходового вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, построенного на триггерной «защелке», требуется смещение вниз передаточных характеристик двух «полу-защелкок», построенных на транзисторах 1 и 2. Данное условие достигается существенным уменьшением проводимости цепей сети подтяжки вверх (PUN) на транзисторах (1, 2) по сравнению с проводимостью цепей сети подтяжки вниз (PDN) на транзисторах с третьего по двенадцатый (3-12). В свою очередь, обеспечение этого условия приводит к увеличению времени переходного процесса при переключении сигнала из низкого уровня напряжения GND в напряжение высокого уровня VDD и, следовательно, к уменьшению общего быстродействия известного трехвходового вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ вследствие увеличения задержки времени формирования сигнала высокого уровня напряжения на выходах XOR и XNOR.

Кроме того, из-за повышенного времени переходного процесса увеличивается динамический ток потребления.

Задачей предлагаемого изобретения является повышение быстродействия известного трехвходового вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и повышение надежности за счет уменьшения динамического тока потребления.

Поставленная задача достигается тем, что в трехвходовой вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, содержащий первый и второй МОП транзисторы Р-типа (1, 2), МОП транзисторы N-типа с третьего по двенадцатый (3-12), вывод питания высокого уровня напряжения VDD, соединенный с истоками первого и второго транзисторов (1, 2), вывод питания низкого уровня напряжения GND, соединенный с истоками пятого и восьмого транзисторов (5, 8), прямые входы А, В и С и инверсные входы  выходы XOR и XNOR, причем вход А соединен с затворами транзисторов девятого и одиннадцатого (9, 11), а

выходы XOR и XNOR, причем вход А соединен с затворами транзисторов девятого и одиннадцатого (9, 11), а  - с затворами транзисторов третьего и шестого (3, 6), вход В - с затворами транзисторов четвертого и седьмого (4, 7), а

- с затворами транзисторов третьего и шестого (3, 6), вход В - с затворами транзисторов четвертого и седьмого (4, 7), а  - с затворами транзисторов десятого и двенадцатого (10, 12), вход С - с затвором пятого транзистора (5), а

- с затворами транзисторов десятого и двенадцатого (10, 12), вход С - с затвором пятого транзистора (5), а  - с затвором восьмого транзистора (8), выход XOR - со стоками транзисторов третьего и девятого (3, 9), а выход XNOR - со стоками транзисторов шестого и одиннадцатого (6, 11), истоки третьего и одиннадцатого транзисторов (3, 11) - со стоками четвертого и десятого (4, 10), а истоки шестого и девятого транзисторов (6, 9) - со стоками седьмого и двенадцатого (7, 12), истоки четвертого и двенадцатого транзисторов (4, 12) - со стоком пятого (5), а истоки седьмого и десятого транзисторов (7, 10) - со стоком восьмого (8) введены МОП транзисторы Р-типа с тринадцатого по двадцатый, (13-20), причем затвор первого транзистора соединен со входом С, а затвор второго (2) - со входом

- с затвором восьмого транзистора (8), выход XOR - со стоками транзисторов третьего и девятого (3, 9), а выход XNOR - со стоками транзисторов шестого и одиннадцатого (6, 11), истоки третьего и одиннадцатого транзисторов (3, 11) - со стоками четвертого и десятого (4, 10), а истоки шестого и девятого транзисторов (6, 9) - со стоками седьмого и двенадцатого (7, 12), истоки четвертого и двенадцатого транзисторов (4, 12) - со стоком пятого (5), а истоки седьмого и десятого транзисторов (7, 10) - со стоком восьмого (8) введены МОП транзисторы Р-типа с тринадцатого по двадцатый, (13-20), причем затвор первого транзистора соединен со входом С, а затвор второго (2) - со входом  затворы тринадцатого и пятнадцатого транзисторов (13, 15) - со входом В, а затворы семнадцатого и восемнадцатого (17, 18) - со входом

затворы тринадцатого и пятнадцатого транзисторов (13, 15) - со входом В, а затворы семнадцатого и восемнадцатого (17, 18) - со входом  затворы девятнадцатого и двадцатого транзисторов (19, 20) - со входом А, а затворы четырнадцатого и шестнадцатого (14, 16) - со входом

затворы девятнадцатого и двадцатого транзисторов (19, 20) - со входом А, а затворы четырнадцатого и шестнадцатого (14, 16) - со входом  сток первого транзистора (1) - с истоками тринадцатого и восемнадцатого транзисторов (13, 18), а сток второго транзистора (2) - с истоками пятнадцатого и семнадцатого транзисторов (15, 17), стоки тринадцатого и семнадцатого транзисторов (13, 17) - с истоками четырнадцатого и двадцатого (14, 20), а стоки пятнадцатого и восемнадцатого транзисторов (15, 18) - с истоками шестнадцатого и девятнадцатого (16, 19), и стоки четырнадцатого и девятнадцатого транзисторов (14, 19) - с выходом XOR, а стоки шестнадцатого и двадцатого транзисторов (16, 20) - с выходом XNOR.

сток первого транзистора (1) - с истоками тринадцатого и восемнадцатого транзисторов (13, 18), а сток второго транзистора (2) - с истоками пятнадцатого и семнадцатого транзисторов (15, 17), стоки тринадцатого и семнадцатого транзисторов (13, 17) - с истоками четырнадцатого и двадцатого (14, 20), а стоки пятнадцатого и восемнадцатого транзисторов (15, 18) - с истоками шестнадцатого и девятнадцатого (16, 19), и стоки четырнадцатого и девятнадцатого транзисторов (14, 19) - с выходом XOR, а стоки шестнадцатого и двадцатого транзисторов (16, 20) - с выходом XNOR.

В предлагаемом Трехвходовом КМОП логическом вентиле ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, в отличие от известного трехвходового вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ схема «защелки» исключена, а сеть подтяжки вверх (PUN) организована введением дополняющих (комплементарных) МОП транзисторов. Такое построение схемы позволяет оптимизировать соотношение проводимостей сетей подтяжки вверх (PUN) и подтяжки вниз (PDN) и тем самым повысить быстродействие Трехвходового КМОП логического вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ за счет уменьшения времени переходного процесса при переключении выходных сигналов из низкого уровня напряжения GND в высокий VDD. Кроме того, так как время переходного процесса уменьшено, динамический ток потребления снижен. Снижение величины динамического тока потребления уменьшает избыточный перегрев элементов схемы, что повышает надежность Трех-входового КМОП логического вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ.

На Рисунке приведена схема Трехвходового КМОП логического вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ.

Предлагаемый Трехвходовой КМОП логический вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ содержит МОП транзисторы Р-типа - первый, второй (1, 2) и с тринадцатого по двадцатый и (13-20), МОП транзисторы N-типа - с третьего по двенадцатый (3-12), вывод питания высокого уровня напряжения VDD, соединенный с истоками транзисторов первого и второго (1, 2), вывод питания низкого уровня напряжения GND, соединенный с истоками транзисторов пятого и восьмого (5, 8), прямые входы А, В и С и инверсные входы  выход XOR и выход XNOR. Причем вход А соединен с затворами транзисторов девятого, одиннадцатого, девятнадцатого и двадцатого (9, 11, 19 и 20), а

выход XOR и выход XNOR. Причем вход А соединен с затворами транзисторов девятого, одиннадцатого, девятнадцатого и двадцатого (9, 11, 19 и 20), а  - с затворами транзисторов третьего, шестого, четырнадцатого и шестнадцатого (3, 6, 14 и 16), вход В - с затворами транзисторов четвертого, седьмого, тринадцатого и пятнадцатого (4, 7, 13 и 15), а

- с затворами транзисторов третьего, шестого, четырнадцатого и шестнадцатого (3, 6, 14 и 16), вход В - с затворами транзисторов четвертого, седьмого, тринадцатого и пятнадцатого (4, 7, 13 и 15), а  - с затворами транзисторов десятого, двенадцатого, семнадцатого и восемнадцатого (10, 12, 17 и 18), вход С - с затворами транзисторов первого и пятого (1, 5), а

- с затворами транзисторов десятого, двенадцатого, семнадцатого и восемнадцатого (10, 12, 17 и 18), вход С - с затворами транзисторов первого и пятого (1, 5), а  - с затворами транзисторов второго и восьмого (2, 8), выход XOR - со стоками транзисторов третьего, девятого, четырнадцатого и девятнадцатого (3, 9, 14 и 19), а выход XNOR - со стоками транзисторов шестого, одиннадцатого, шестнадцатого и двадцатого (6, 11, 16 и 20). Кроме того, сток первого транзистора (1) соединен с истоками транзисторов тринадцатого и восемнадцатого (13, 18), а сток второго транзистора (2) - с истоками транзисторов пятнадцатого и семнадцатого (15, 17), стоки тринадцатого и семнадцатого транзисторов (13, 17) - с истоками четырнадцатого и двадцатого (14, 20), а стоки пятнадцатого и восемнадцатого транзисторов (15, 18) - с истоками шестнадцатого и девятнадцатого (16, 19), сток пятого транзистора (5) - с истоками транзисторов четвертого и двенадцатого (4, 12), а сток восьмого (8) - с истоками транзисторов седьмого и десятого (7, 10) и стоки четвертого и десятого транзисторов (4, 10) - с истоками третьего и одиннадцатого (3, 11), а стоки седьмого и двенадцатого транзисторов (7, 12) - с истоками шестого и девятого (6, 9).

- с затворами транзисторов второго и восьмого (2, 8), выход XOR - со стоками транзисторов третьего, девятого, четырнадцатого и девятнадцатого (3, 9, 14 и 19), а выход XNOR - со стоками транзисторов шестого, одиннадцатого, шестнадцатого и двадцатого (6, 11, 16 и 20). Кроме того, сток первого транзистора (1) соединен с истоками транзисторов тринадцатого и восемнадцатого (13, 18), а сток второго транзистора (2) - с истоками транзисторов пятнадцатого и семнадцатого (15, 17), стоки тринадцатого и семнадцатого транзисторов (13, 17) - с истоками четырнадцатого и двадцатого (14, 20), а стоки пятнадцатого и восемнадцатого транзисторов (15, 18) - с истоками шестнадцатого и девятнадцатого (16, 19), сток пятого транзистора (5) - с истоками транзисторов четвертого и двенадцатого (4, 12), а сток восьмого (8) - с истоками транзисторов седьмого и десятого (7, 10) и стоки четвертого и десятого транзисторов (4, 10) - с истоками третьего и одиннадцатого (3, 11), а стоки седьмого и двенадцатого транзисторов (7, 12) - с истоками шестого и девятого (6, 9).

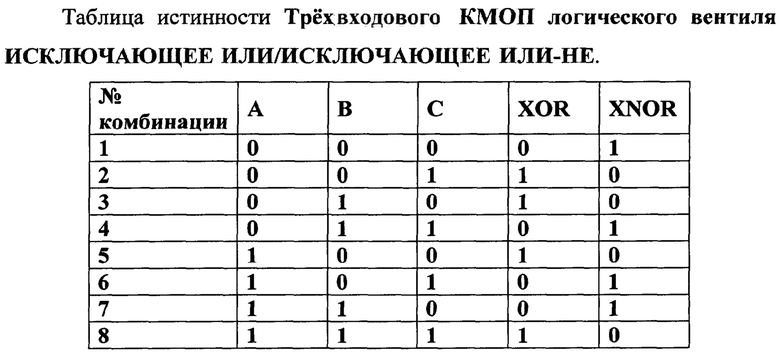

в последующем описании принимается соглашение, что напряжение высокого уровня VDD соответствует напряжению логического уровня «1», а напряжение низкого уровня GND - напряжению логического уровня «0». Кроме того, напряжения логических уровней на инверсных входах  всегда инверсно относительно соответствующих напряжений логических уровней на прямых входах А, В и С по определению. Поэтому в дальнейшем при описании работы схемы и в таблице истинности нет необходимости приводить значения напряжений логических уровней на инверсных входах

всегда инверсно относительно соответствующих напряжений логических уровней на прямых входах А, В и С по определению. Поэтому в дальнейшем при описании работы схемы и в таблице истинности нет необходимости приводить значения напряжений логических уровней на инверсных входах

Предлагаемый Трехвходовой КМОП логический вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ предназначен для формирования логических сигналов ИСКЛЮЧАЮЩЕЕ ИЛИ на выходе XOR и ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ на выходе XNOR, как представлено ниже в таблице истинности.

Таким образом, предлагаемый Трехвходовой КМОП логический вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ представляет собой логическую схему комбинационного типа и работает следующим образом.

В комбинации №1 А=В=С=«0». При этом на выходе XOR через проводящие транзисторы 8, 10 и 3 устанавливается уровень напряжения логического «0», а на выходе XNOR через проводящие транзисторы 1, 13 и 20 - уровень напряжения логической «1».

В комбинации №2 А=В=«0» и С=«1». При этом на выходе XOR через проводящие транзисторы 2, 15 и 19 устанавливается уровень напряжения логической «1», а на выходе XNOR через проводящие транзисторы 5, 12 и 6 - уровень напряжения логического «0».

В комбинации №3 А=С=«0» и В=«1». При этом на выходе XOR через проводящие транзисторы 1, 18 и 19 устанавливается уровень напряжения логической «1», а на выходе XNOR через проводящие транзисторы 8, 7 и 6 - уровень напряжения логического «0».

В комбинации №4 А=«0», В=С=«1». При этом на выходе XOR через проводящие транзисторы 5, 4 и 3 устанавливается уровень напряжения логического «0», а на выходе XNOR через проводящие транзисторы 2, 17 и 20 - уровень напряжения логической «1».

В комбинации №5 А=«1» и В=С=«0». При этом на выходе XOR через проводящие транзисторы 1, 13 и 14 устанавливается уровень напряжения логической «1», а на выходе XNOR через проводящие транзисторы 8, 10 и 11 - уровень напряжения логического «0».

В комбинации №6 А=С=«1» и В=«0». При этом на выходе XOR через проводящие транзисторы 5, 12 и 9 устанавливается уровень напряжения логического «0», а на выходе XNOR через проводящие транзисторы 2, 15 и 16 - уровень напряжения логической «1».

В комбинации №7 А=В=«1» и С=«0». При этом на выходе XOR через проводящие транзисторы 8, 7 и 9 устанавливается уровень напряжения логического «0», а на выходе XNOR через проводящие транзисторы 1, 18 и 16 - уровень напряжения логической «1».

В комбинации №8 А=В=С=«1». При этом на выходе XOR через проводящие транзисторы 2, 17 и 14 устанавливается уровень напряжения логической «1», а на выходе XNOR через проводящие транзисторы 5, 4 и 11 - уровень напряжения логического «0».

Литература

1. Baker Jacob. R. CMOS. Circuit Design, Layout, and Simultion // Published by Wiley - IEEE Press, ISBN 9780470881323, 2th ed. 2005. 1039 p.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧЕТЫРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ | 2022 |

|

RU2784457C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

| КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2814896C1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2802665C1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2016 |

|

RU2628152C1 |

| СУММАТОР | 2010 |

|

RU2435196C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2011 |

|

RU2444050C1 |

Изобретение относится к вычислительной технике и может быть использовано при создании устройств, использующих функции ИСКЛЮЧАЮЩЕЕ ИЛИ и (или) ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, например в схемах контроля четности и (или) нечетности и многоразрядных сумматорах. Техническим результатом изобретения является повышение быстродействия известного трехвходового вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и повышение надежности за счет уменьшения динамического тока потребления. Трехвходовой КМОП логический вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ содержит первый и второй и с тринадцатого по двадцатый МОП транзисторы Р-типа, МОП транзисторы N-типа с третьего по двенадцатый, вывод питания высокого уровня напряжения VDD, вывод питания низкого уровня напряжения GND, прямые входы А, В и С и инверсные входы  выход XOR и выход XNOR. 1 ил.

выход XOR и выход XNOR. 1 ил.

Трехвходовой КМОП логический вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, содержащий первый и второй МОП транзисторы Р-типа, МОП транзисторы N-типа с третьего по двенадцатый, вывод питания высокого уровня напряжения VDD, соединенный с истоками первого и второго транзисторов, вывод питания низкого уровня напряжения GND, соединенный с истоками пятого и восьмого транзисторов, прямые входы А, В и С и инверсные входы  выход XOR и выход XNOR, причем вход А соединен с затворами транзисторов девятого и одиннадцатого, а

выход XOR и выход XNOR, причем вход А соединен с затворами транзисторов девятого и одиннадцатого, а  - с затворами транзисторов третьего и шестого, вход В - с затворами транзисторов четвертого и седьмого, а

- с затворами транзисторов третьего и шестого, вход В - с затворами транзисторов четвертого и седьмого, а  - с затворами транзисторов десятого и двенадцатого, вход С - с затвором пятого транзистора, а

- с затворами транзисторов десятого и двенадцатого, вход С - с затвором пятого транзистора, а  - с затвором восьмого транзистора, выход XOR - со стоками транзисторов третьего и девятого, а выход XNOR - со стоками транзисторов шестого и одиннадцатого, истоки третьего и одиннадцатого транзисторов - со стоками четвертого и десятого, а истоки шестого и девятого транзисторов - со стоками седьмого и двенадцатого, истоки четвертого и двенадцатого транзисторов - со стоком пятого, а истоки седьмого и десятого транзисторов - со стоком восьмого, отличающийся тем, что в него введены МОП транзисторы Р-типа с тринадцатого по двадцатый, причем затвор первого транзистора соединен со входом С, а затвор второго - со входом

- с затвором восьмого транзистора, выход XOR - со стоками транзисторов третьего и девятого, а выход XNOR - со стоками транзисторов шестого и одиннадцатого, истоки третьего и одиннадцатого транзисторов - со стоками четвертого и десятого, а истоки шестого и девятого транзисторов - со стоками седьмого и двенадцатого, истоки четвертого и двенадцатого транзисторов - со стоком пятого, а истоки седьмого и десятого транзисторов - со стоком восьмого, отличающийся тем, что в него введены МОП транзисторы Р-типа с тринадцатого по двадцатый, причем затвор первого транзистора соединен со входом С, а затвор второго - со входом  затворы тринадцатого и пятнадцатого транзисторов - со входом В, а затворы семнадцатого и восемнадцатого - со входом

затворы тринадцатого и пятнадцатого транзисторов - со входом В, а затворы семнадцатого и восемнадцатого - со входом  затворы девятнадцатого и двадцатого транзисторов - со входом А, а затворы четырнадцатого и шестнадцатого - со входом

затворы девятнадцатого и двадцатого транзисторов - со входом А, а затворы четырнадцатого и шестнадцатого - со входом  сток первого транзистора - с истоками транзисторов тринадцатого и восемнадцатого, а сток второго транзистора - с истоками транзисторов пятнадцатого и семнадцатого, стоки тринадцатого и семнадцатого транзисторов - с истоками четырнадцатого и двадцатого, а стоки пятнадцатого и восемнадцатого транзисторов - с истоками шестнадцатого и девятнадцатого и стоки четырнадцатого и девятнадцатого транзисторов - с выходом XOR, а стоки шестнадцатого и двадцатого - с выходом XNOR.

сток первого транзистора - с истоками транзисторов тринадцатого и восемнадцатого, а сток второго транзистора - с истоками транзисторов пятнадцатого и семнадцатого, стоки тринадцатого и семнадцатого транзисторов - с истоками четырнадцатого и двадцатого, а стоки пятнадцатого и восемнадцатого транзисторов - с истоками шестнадцатого и девятнадцатого и стоки четырнадцатого и девятнадцатого транзисторов - с выходом XOR, а стоки шестнадцатого и двадцатого - с выходом XNOR.

| RJ BAKER "CMOS: Circuit Design, Layout, and Simulation | |||

| Second Edition | |||

| IEEE Press Series on Microelectronic Systems, 2005.1039 p | |||

| ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКОГО УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2642416C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2008 |

|

RU2360359C1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| Преобразователь уровней сигналов на МДП-транзисторах | 1988 |

|

SU1538246A1 |

| US 6469541 B2, 22.10.2002 | |||

Авторы

Даты

2021-12-06—Публикация

2020-11-25—Подача