ти отклика производится проверка следующих за выделенным синхрословом комбинаций символов на их соответствие разрешенному алфавиту адресов синхроблока и сравнение декодированных комбинаций с опорным адресом. Если сравниваемые комбинации отличаются одна от другой на величину больше допустимой, то на выходе элемента 16 сравнения формируется сигнал ошибки, поступающий на блок 12 памяти блока 7 управления. В блоке 12 памяти сигнал ошибки контролируется только на тех временных позициях, которые соответствуют местоположению слов адреса синхроблока в предположении, что отклик опознавателя 1 синхрогруппы истинньй. Вырабатывается сигнал в блрке 12 памяти, по которому регистр 17 запоминает состояние на выходах регистра 6, а также разрешается запись в регистр 23 блока 8 комбинаций символов, поступающих с блока 22 памяти, которые опознаны как истинный адрес синхроблока. Сигнал с вьпсода элемента ИЛИ 26 разрешает запись этих комбинаций с регистра 23 в регистр 24. 1 з.п. ф-лы,3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1987 |

|

SU1529284A1 |

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1985 |

|

SU1278970A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

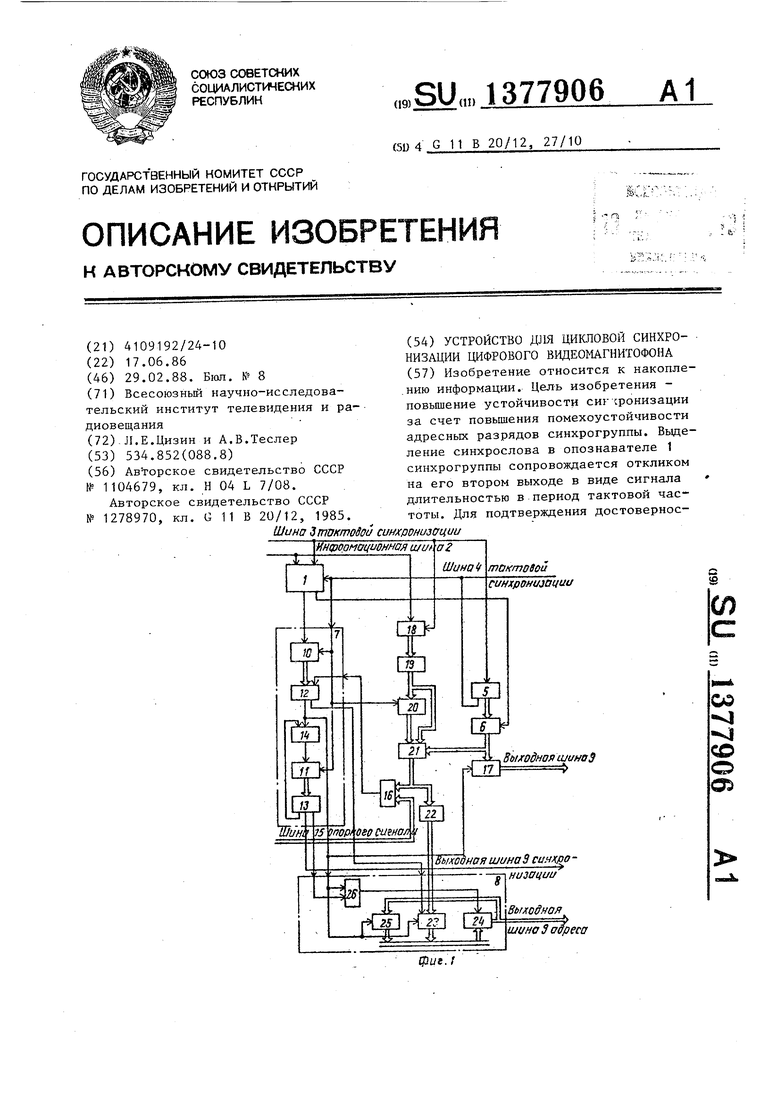

Изобретение относится к накопле- .нию информации. Цель изобретения - повышение устойчивости сиг сронизации за счет повышения помехоустойчивости адресных разрядов синхрогруппы. Выделение синхрослова в опознавателе 1 синхрогруппы сопровождается откликом на его втором выходе в виде сигнала длительностью в период тактовой частоты. Для подтверждения достоверносаг Шина / тактовой синхронизации о (Л Е 1ГУ Выходная шинаЗ оо Ч СО О О5 шина 3 адреса

1

Изобретение относится к .накоплению информации, а именно к устройствам для цикловой синхронизации цифрового видеомагнитофона.

Целью изобретения является повышение устойчивости синхроризахщи за счет повышения помехоустойчивости адресных разрядов синхрогруппы.

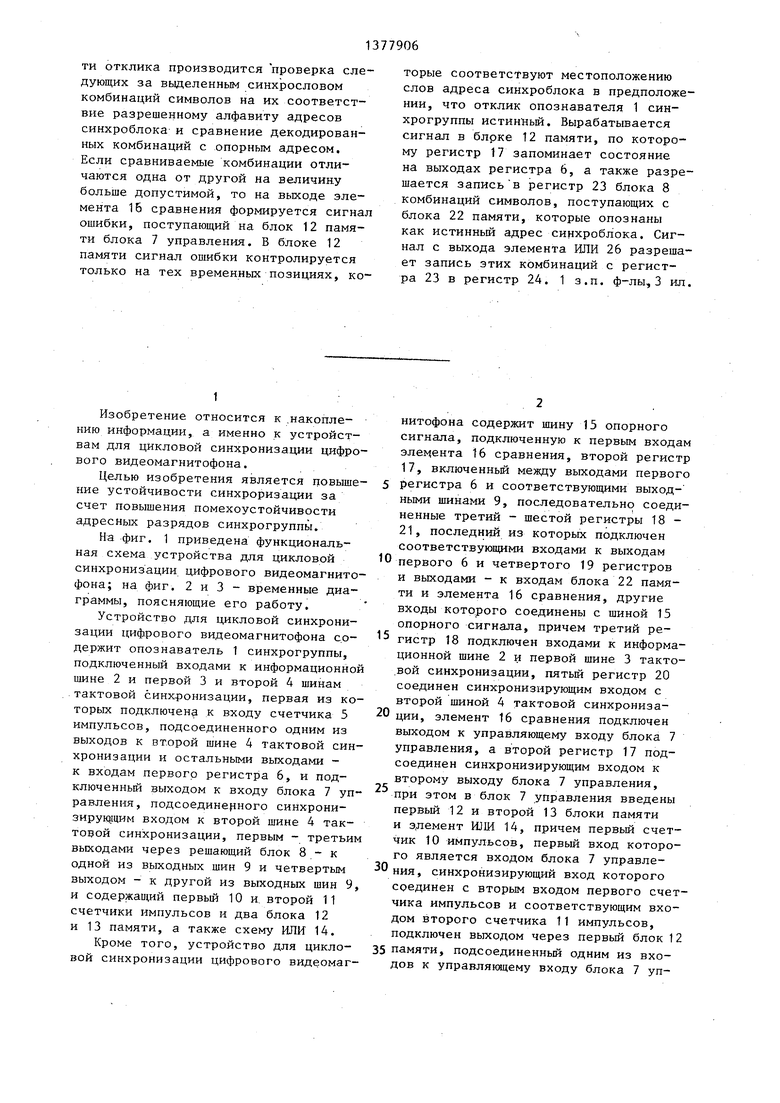

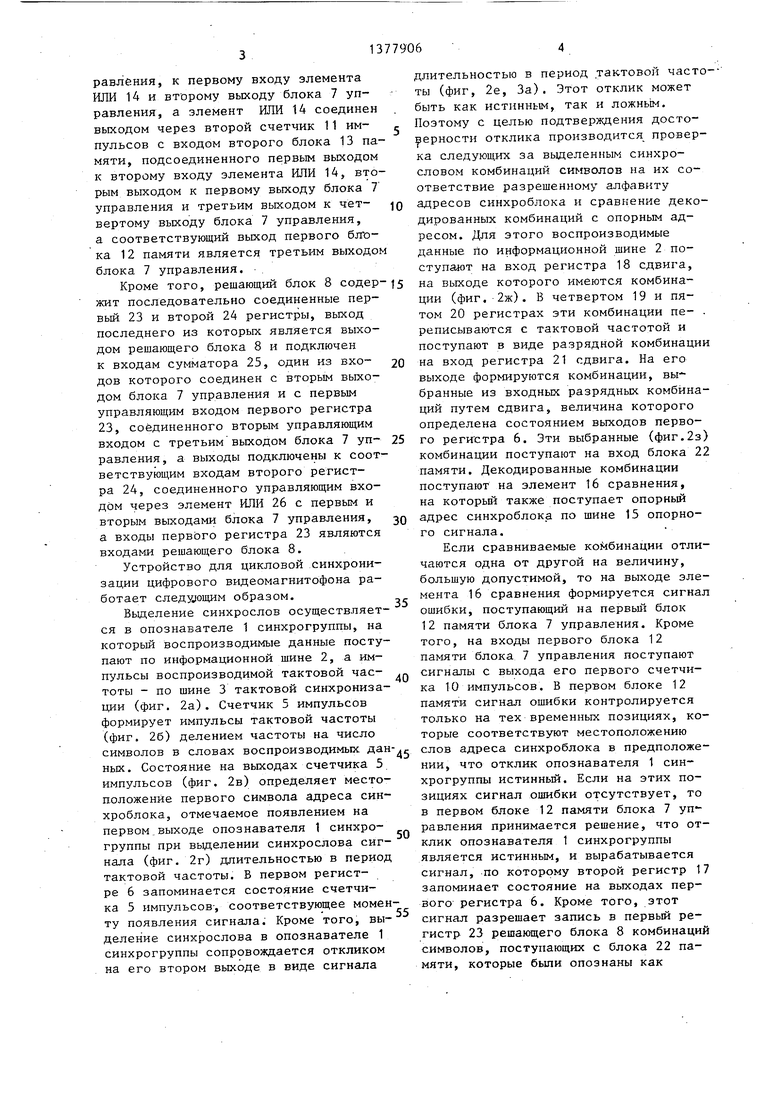

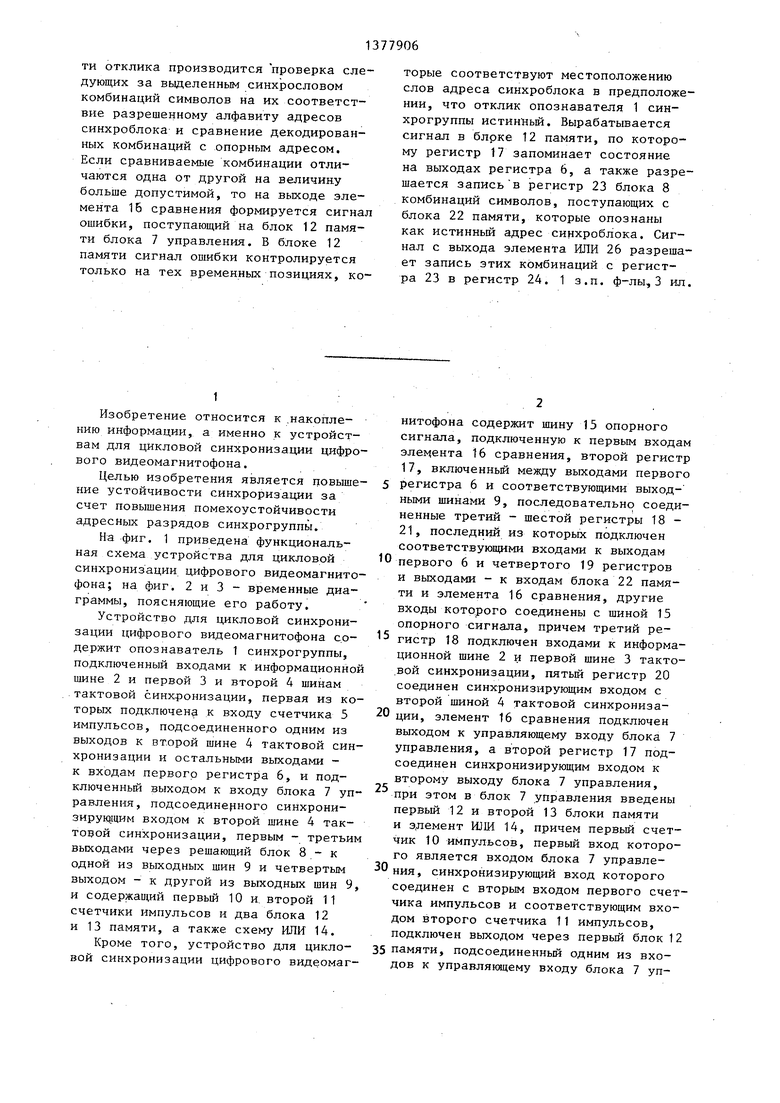

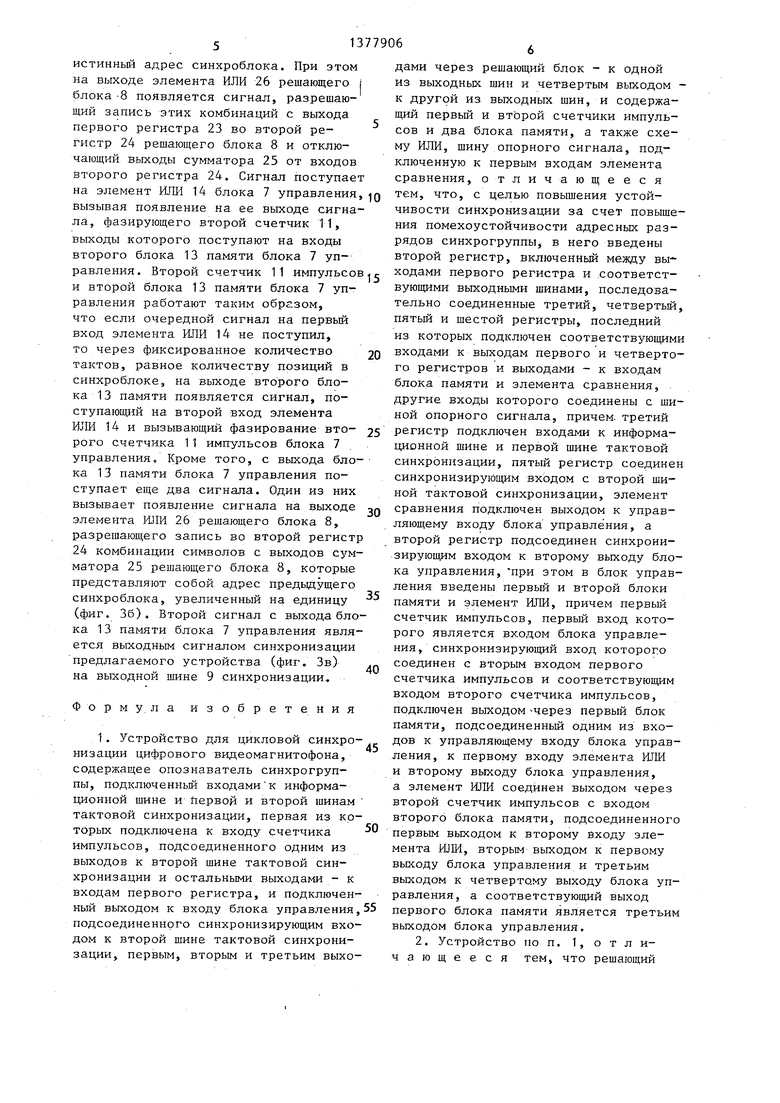

На фиг. 1 приведена функциональная схема устройства для цикловой синхронизации цифрового видеомагнитофона; на фиг. 2 и 3 - временные диаграммы, поясняющие его работу.

Устройство для цикловой синхронизации цифрового видеомагнитофона с.о- держит опознаватель 1 синхрогруппы, подключенный входами к информационной шине 2 и первой 3 и второй 4 шинам тактовой синхронизации, первая из которых подключена к входу счетчика 5 импульсов, подсоединенного одним из выходов к второй шине 4 тактовой синхронизации и остальными выходами - к входам первого регистра 6, и подключенный выходом к входу блока 7 управления, подсоединенного синхрони- зирувдим входом к второй шине 4 тактовой синхронизации, первым - третьим выходами через решающий блок 8 - к одной из выходных шин 9 и четвертым выходом - к другой из выходных шин 9 и содержащий первый 10 и, второй 11 счетчики импульсов и два блока 12 и 13 памяти, а также схему ИЛИ 14.

Кроме того, устройство для цикловой синхронизации цифрового видеомагнитофона содержит шину 15 опорного сигнала, подключенную к первым входам элемента 16 сравнения, второй регистр 17, включенньй между выходами первого

регистра 6 и соответствующими выход- ными шинами 9, последовательно соединенные третий - шестой регистры 18 - 21, последний из которых подключен соответствующими входами к выходам

первого 6 и четвертого 19 регистров и выходами - к входам блока 22 памяти и элемента 16 сравнения, другие входы которого соединены с шиной 15 опорного сигнала, причем третий регистр 18 подключен входами к информационной шине 2 и первой шине 3 такто- .вой синхронизации, пятьй регистр 20 соединен синхронизирующим входом с второй шиной 4 тактовой синхронизации, элемент 16 сравнения подключен выходом к управляющему входу блока 7 управления, а второй регистр 17 подсоединен синхронизирующим входом к второму выходу блока 7 управления, при этом в блок 7 управления введены первый 12 и второй 13 блоки памяти и элемент ИЛИ 14, причем первый счетчик 10 импульсов, первый вход которого является входом блока 7 управления, синхронизирующий вход которого соединен с вторым входом первого счетчика импульсов и соответствующим входом второго счетчика 11 импульсов, подключен выходом через первый блок 12

памяти, подсоединенный одним из входов к управляклцему входу блока 7 управления, к первому входу элемента ИЛИ 14 и второму выходу блока 7 управления, а элемент ИЛИ 14 соединен выходом через второй счетчик 11 им- пульсов с входом второго блока 13 памяти, подсоединенного первым выходом к второму входу элемента ИЛИ 14, вторым выходом к первому выходу блока 7 управления и третьим выходом к чет- вертому выходу блока 7 управления, а соответствующий выход первого бл о- ка 12 памяти является третьим выходом блока 7 управления.

Кроме того, решающий блок 8 содержит последовательно соединенные первый 23 и второй 24 регистры, выход последнего из которых является выходом решающего блока 8 и подключен к входам сумматора 25, один из вхо- дов которого соединен с вторым выходом блока 7 управления и с первым управляющим входом первого регистра 23, соединенного вторым управляющим входом с третьим выходом блока 7 уп- равления, а выходы подключены к соответствующим входам второго регистра 24, соединенного управляющим входом через элемент ИЛИ 26 с первьм и вторым выходами блока 7 управления, а входы первого регистра 23 являются входами решающего блока 8.

Устройство для цикловой синхронизации цифрового видеомагнитофона работает cлeдyJoщнм образом.

Выделение синхрослов осуществляется в опознавателе 1 синхрогруппы, на который воспроизводимые данные поступают по информационной шине 2, а им

пульсы воспроизводимой тактовой час

тоты - по шине 3 тактовой синхронизации (фиг. 2а). Счетчик 5 импульсов формирует импульсы тактовой частоты (фиг. 25) делением частоты на число символов в словах воспроизводимых дан ных. Состояние на выходах счетчика 5 импульсов (фиг. 2в) определяет местоположение первого символа адреса син- хроблока, отмечаемое появлением на первом выходе опознавателя 1 синхрогруппы при выделении синхрослова сигнала (фиг. 2г) длительностью в период тактовой частоты. Б первом регистре 6 запоминается состояние счетчика 5 импульсов-, соответствующее момен ту появления сигнала. Кроме того, вы деление синхрослова в опознавателе 1 синхрогруппы сопровождается откликом на его втором выходе в виде сигнгша

, ю

J5 20 25 О

35

40

-дг-

50

55

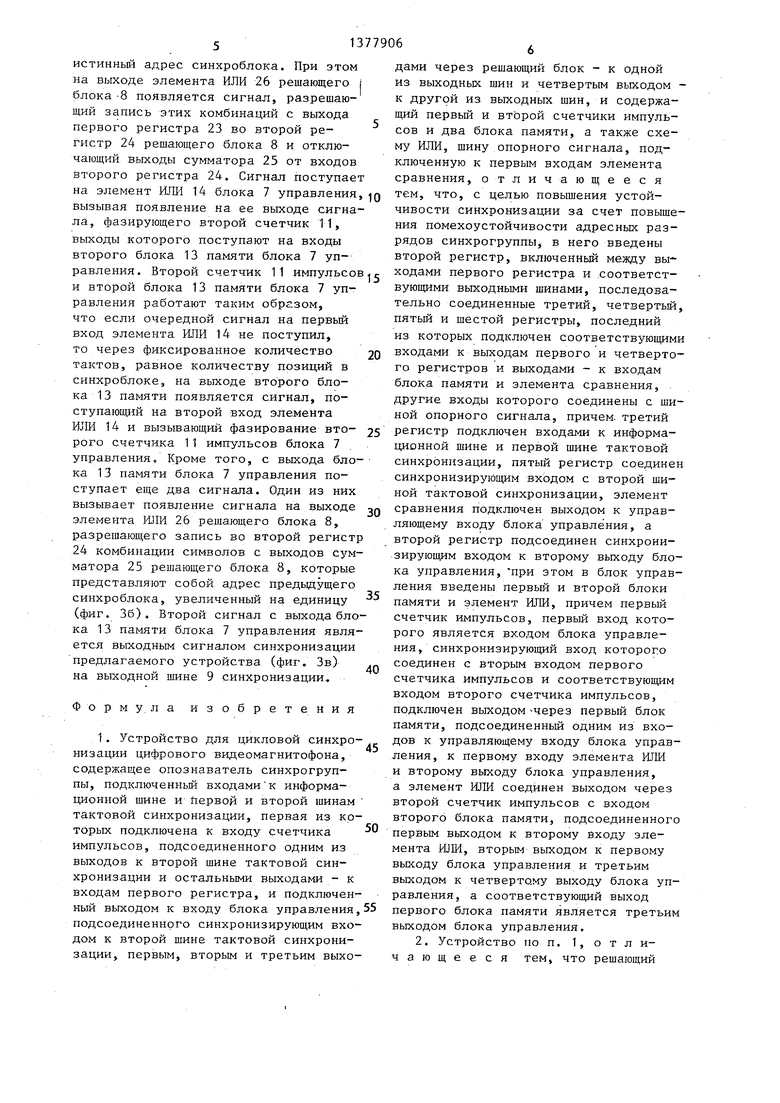

длительностью в период тактовой частоты (фиг, 2е, За). Этот отклик может быть как истинным, так и ложньЫ. Поэтому с целью подтверждения достоверности отклика производится проверка следующих за вьщеленным синхро- словом комбинаций символов на их соответствие разрешенному алфавиту адресов синхроблока и сравнение декодированных комбинаций с опорным адресом. Для этого воспроизводимые данные по информационной шине 2 по- ступайт на вход регистра 18 сдвига, на выходе которого имеются комбинации (фиг. 2ж). В четвертом 19 и пятом 20 регистрах эти комбинации пе- . реписываются с тактовой частотой и поступают в виде разрядной комбинации на вход регистра 21 сдвига. На его выходе формируются комбинации, выбранные из входных разрядных комбинаций путем сдвига, величина которого определена состоянием выходов первого регистра 6. Эти выбранные (фиг.2з) комбинации поступают на вход блока 22 памяти. Декодированные комбинации поступают на элемент 16 сравнения, на которьй также поступает опорньй адрес синхроблока по шине 15 опорного сигнала.

Если сравниваемые комбинации отличаются одна от другой на величину, большую допустимой, то на выходе элемента 16 сравнения формируется сигнал ошибки, поступающий на первьш блок 12 памяти блока 7 управления. Кроме того, на входы первого блока 12 памяти блока 7 управления поступают сигналы с выхода его первого счетчика ТО импульсов. В первом блоке 12 памяти сигнал ошибки контролируется только на тех временных позициях, которые соответствуют местоположению слов адреса синхроблока в предположении, что отклик опознавателя 1 синхрогруппы истинньш. Если на этих позициях сигнал ошибки отсутствует, то в первом блоке 12 памяти блока 7 управления принимается решение, что отклик опознавателя 1 синхрогруппы является истинным, и вырабатывается сигнал, по которому второй регистр 17 запоминает состояние на выходах первого регистра 6. Кроме того, этот сигнал разрешает запись в первый регистр 23 решающего блока 8 комбинаций символов, поступающих с блока 22 памяти, которые бьши опознаны как

истинньй адрес синхроблока. При этом на выходе элемента ИЛИ 26 решающего j блока -8 появляется сигнал, разрешающий запись этих комбинаций с выхода первого регистра 23 во второй регистр 24 решающего блока 8 и отключающий выходы сумматора 25 от входов второго регистра 24, Сигнал поступает на элемент ИЛИ 14 блока 7 управления, вызывая появление на ее выходе сигнала, фазирующего второй счетчик 11, выходы которого поступают на входы второго блока 13 памяти блока 7 управления. Второй счетчик 11 импульсов и второй блока 13 памяти блока 7 управления работают таким образом, что если очередной сигнал на первый вход элемента ИЛИ 14 не поступил, то через фиксированное количество тактов, равное количеству позиций в синхроблоке, на выходе второго блока 13 памяти появляется сигнал, поступающий на второй вход элемента ИЛИ 14 и вызывающий фазирование вто- рого счетчика 11 импульсов блока 7 управления. Кроме того, с выхода блока 13 памяти блока 7 управления поступает еще два сигнала. Один из них вызывает появление сигнала на выходе элемента ИЛИ 26 решающего блока 8, разрешающего запись во второй регистр 24 комбинации символов с выходов сумматора 25 решающего блока 8, которые представляют собой адрес предьщущего синхроблока, увеличенный на единицу (фиг. 36), Второй сигнал с выхода блока 13 памяти блока 7 управления является выходным сигналом синхронизации предлагаемого устройства (фиг. Зв) на выходной шине 9 синхронизации.

Формула изобретения

низации цифрового видеомагнитофона, содержащее опознаватель синхрогруппы, подключенньм входами к информационной шине и йервой и второй шинам тактовой синхронизации, первая из которых подключена к входу счетчика импульсов, подсоединенного одним из выходов к второй шине тактовой синхронизации и остальными выходами - к входам первого регистра, и подключенный выходом к входу блока управления подсоединенного синхронизирующим входом к второй шине тактовой синхронизации, первым, вторым и третьим выхос 0 5

0

5

0

5

0

5

дами через решающий блок - к одной из выходных шин и четвертым выходом - к другой из выходных шин, и содержащий первьш и второй счетчики импульсов и два блока памяти, а также схему ИЛИ, шину опорного сигнала, подключенную к первым входам элемента сравнения, отличающееся тем, что, с целью повышения устойчивости синхронизации за счет повышения помехоустойчивости адресных разрядов синхрогруппы, в него введены второй регистр, включенньй между вы - ходами первого регистра и соответствующими выходными шинами, последовательно соединенные третий, четзертьш, пятьй и шестой регистры, последний из которых подключен соответствующими входами к выходам первого и четвертого регистров и выходами - к входам блока памяти и элемента сравнения, другие входы которого соединены с шиной опорного сигнала, причем, третий регистр подключен входами к информационной шине и первой шине тактовой синхронизации, пятый регистр соединен синхронизирующим входом с второй шиной тактовой синхронизации, элемент сравнения подключен выходом к управляющему вход;у блока управления, а второй регистр подсоединен синхронизирующим входом к второму выходу блока управления, при этом в блок управления введены первый и второй блоки памяти и элемент ИЛИ, причем первьш счетчик импульсов, первый вход которого является входом блока управления, синхронизирующий вход которого соединен с вторым входом первого счетчика импульсов и соответствующим входом второго счетчика импульсов, подключен выходом -через первый блок памяти, подсоединенный одним из входов к управляющему входу блока управления, к первому входу элемента ИЛИ и второму выходу блока управления, а элемент ИЛИ соединен выходом через второй счетчик импульсов с входом второго блока памяти, подсоединенного первым выходом к второму входу элемента ШШ, вторым выходом к первому выходу блока управления и третьим выходом к четвертому выходу блока управления, а соответствующий выход первого блока памяти является третьим выходом блока управления.

блок содержит последовательно соединенные первый и второй регистры, выход последнего из которых является выходом решающего блока и подключен к входам сумматора, один из входов которого соединен с вторым выходом блока управления и с первым управляющим входом первого регистра, соедии Г1П1и1Г1ГШЯПЛЛиГ1ПЛ Ш

5 frl

S О г 2

J

П о г 2 ... П or

Л. irдJC2

е h

sw

ж )C)C)OOCXDCX CXDC)CXDOOCXDC

-И

I fJepdoc слод синхроолона

3 DC

nefidoe слобо

афеса сиН рОбЛОНОГ

Фиг. 2

ненного вторым управляющим, входом с третьим выходом блока управления, а выходы подключены к соответствую- ищм входам второго регистра, соединенного управляющим входом через элемент ИЛИ с первым и вторым выходами блока управления,а входы первого регистра являются входами решающего блока.

C)CXDOOCXDC

I fJepdoc слодо адреса синхроолона

k

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1983 |

|

SU1104679A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1985 |

|

SU1278970A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Шина юштоЗои синхронизации | |||

Авторы

Даты

1988-02-28—Публикация

1986-06-17—Подача