Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи информации для восстановления скорости цифрового потока при асинхронном сопряжении.

Целью изобретения является повышение точности восстановления скорости входного сигнала.

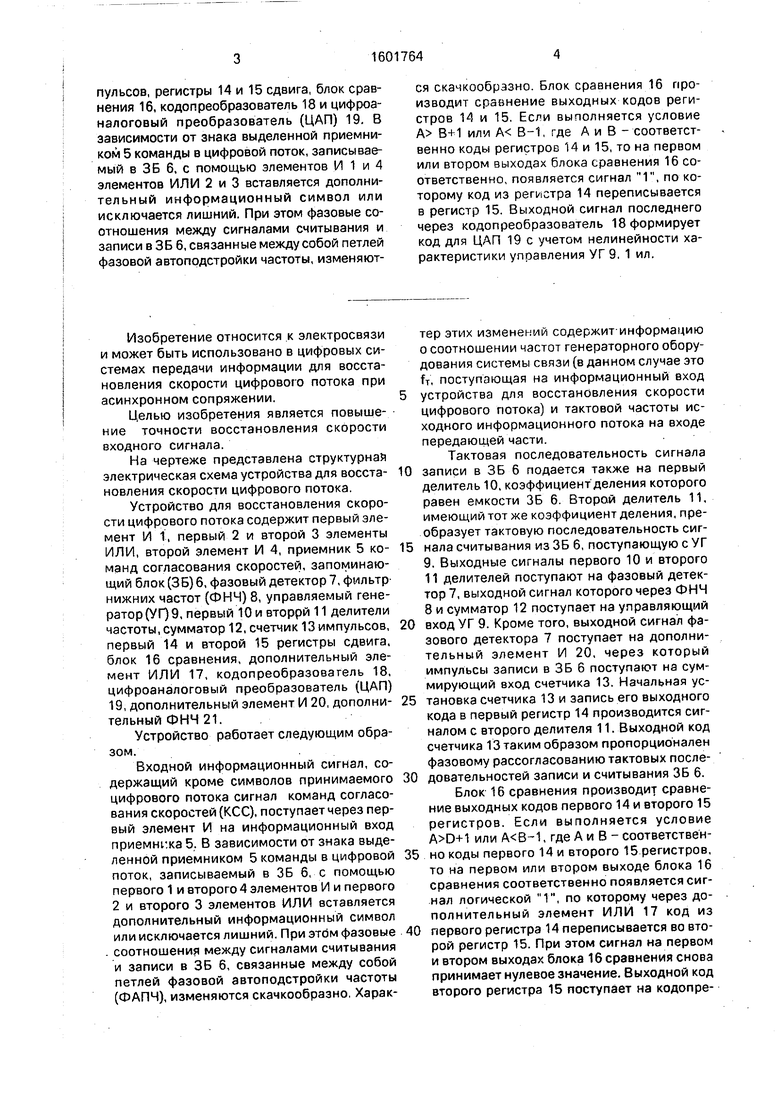

На чертеже представлена структурная электрическая схема устройства для восстановления скорости цифрового потока.

Устройство для восстановления скорости цифрового потока содержит первый элемент И 1, первый 2 и второй 3 элементы ИЛИ, второй элемент И 4, приемник 5 команд согласования скоростей, запоминающий блок (ЗБ) 6, фазовый детектор 7, фмльтр нижних частот (ФНЧ) 8, управляемый генератор (УГ) 9. первый 10 и вторрй 11 делители частоты, сумматор 12, счетчик 13 импульсов, первый 14 и второй 15 регистры сдвига, блок 16 сравнения, дополнительный элемент ИЛИ 17, кодопреобразователь 18, цифроаналоговый преобразователь (ЦАП) 19, дополнительный элемент И 20, дополнительный ФНЧ 21.

Устройство работает следующим образом.

Входной информационный сигнал, содержащий кроме символов принимаемого цифрового потока сигнал команд согласования скоростей (КСС), поступает через первый элемент И на информационный вход приемнг.ка 5. В зависимости от знака выделенной приемником 5 команды в цифровой поток, записываемый в ЗБ 6. с помощью первого 1 и второго 4 элементов И и первого 2 и второго 3 элементов ИЛИ вставляется дополнительный информационный символ или исключается лишний. При этом фазовые . соотношения между сигналами считывания и записи в ЗБ 6, связанные между собой петлей фазовой автоподстройки частоты (ФАПЧ), изменяются скачкообразно. Характер этих изменений содержит-информацию о соотношении частот генераторного оборудования системы связи (в данном случае это ft, поступающая на информационный вход устройства для восстановления скорости цифрового потока) и тактовой частоты исходного информационного потока на входе передающей части.

Тактовая последовательность сигнала 0 записи в ЗБ 6 подается также на первый делитель 10, коэффициент деления которого равен емкости ЗБ 6. Второй делитель 11, имеющий тот же коэффициент деления, преобразует тактовую последовательность сиг- 5 нала считывания из ЗБ 6, поступающую с УГ 9. Выходные сигналы первого 10 и второго 11 делителей поступают на фазовый детектор 7, выходной сигнал которого через ФНЧ 8 и сумматор 12 поступает на управляющий 0 вход УГ 9. Кроме того, выходной сигнал фазового детектора 7 поступает на дополнительный элемент И 20, через который импульсы записи в ЗБ 6 поступают на суммирующий вход счетчика 13. Начальная ус- 5 тановка счетчика 13 и запись его выходного кода в первый регистр 14 производится сигналом с второго делителя 11. Выходной код счетчика 13 таким образом пропорционален фазовому рассогласованию тактовых после- 0 довательностей записи и считывания ЗБ 6. Блок 16 сравнения производит сравнение выходных кодов первого 14 и второго 15 регистров. Если выполняется условие A D-t-1 или , где А и В - соответствен- 35 но коды первого 14 и второго 15 регистров, то на первом или втором выходе блока 16 сравнения соответственно появляется сигнал логической 1, по которому через дополнительный элемент ИЛИ 17 код из 40 первого регистра 14 переписывается во второй регистр 15. При этом сигнал на первом и втором выходах блока 16 сравнения снова принимает нулевое значение. Выходной код второго регистра 15 поступает на кодопреобразователь 18, который формирует код для ЦАП 19 с учетом нелинейности характеристики управления УГ 9.

В момент приема команды согласования скоростей (КСС) приемником 5 проис- ходит изменение фазы тактовой последовательности записи в ЗБ 6 ни ± 27Г. Этот сдвиг вызывает изменение выходного сигнала фазового детектора 7 и, как следствие, изменение напряжения на ФНЧ 8. Под воздействием управляющего напряжения с выхода сумматора 12 изменяется частота УГ 9, что приводит к уменьшению фазового рассогласования. Если величина этого рассогласования успевает свестись к нулю до прихода следующей КСС, то коды на выходах первого 14 и второго 15 регистров равны и значение напряжения на выходе ЦАП 19 не изменится. Эта ситуация наблюдается в том случае, если частотное рассогласование цифровых потоков не превышает полосы захвата петли ФАПЧ.

В противном случае возникает разность в кодах на выходах первого 14 и второго 15 регистров, превышающая единицу. Это приводит к изменению выходного напряжения на выходы ЦАП 19 и сумматора 12 и, как следствие, к изменению частоты Af УГ9.Ес- ли это изменение приводит к попаданию собственной частоты УГ 9 в полосу захвата, петли ФАПЧ, далее выходное напряжение ЦАП 19 не изменится, если нет, процесс повторяется. Таким образом, если минимальное значение Аf не превышает полосу захвата петли ФАПЧ, при условии обеспечения необходимой полосы перестройки УГ 9 устанавливается стационарный режим. Медленное изменение взаимного рассогласования частот обеспечивается петлей ФАПЧ, имеющей относительно меньшую полосу захвата. Практически это означает, что подстройка частоты по петле ФАПЧ через ФНЧ 8 производится в полосе, равной кратковременной взаимной нестабильности генерато- ров (частоты УГ 9 и fr), другая же часть устройства для восстановления скорости цифрового потока обеспечивает подстройку в полосе, равной долговременной нестабильности генераторов.

Формула и зобретения Устройство для восстановления, скорости цифрового потока, содержащее последовательно соединенные первый элемент ИЛИ, первый элемент И, приемник команд согласования скоростей, последовательно соединенные второй элемент ИЛИ, второй элемент И и запоминающий блок, последовательно соединенные фазовый детектор и фильтр нижних частот, а также управляемый генератор, выход которого подсоединен к считывающему входу запоминающего блока, информационный вход которого подключен к выходу первого элемента И, первые входы первого и вгоро- го элементов ИЛИ подключены к первому выходу приемника команд согласования скоростей, второй выход которого подсоединен к второму входу второго элемента И, а вторые входы первого и второго элементов ИЛИ объединены с тактовым входом приемника команд согласования скоростей, причем вторые входы первого элемента И и первого элемента ИЛИ и выход запоминающего блока являются соответственно информационным и тактовым входами и выходом устройства, отличающееся тем, что, с целью повышения точности восстановления -скорости входного сигнала, на приемной стороне введены последовательно соединенные дополнительный элемент И, счетчик импульсов, первый регистр сдвига, блок сравнения, дополнительный элемент ИЛИ, второй регистр сдвига, кодопреобразователь, цифроаналоговый преобразователь, дополнительный фильтр нижних частот и сумматор, второй вход и выход которого подключены соответственно к выходу фильтра нижних частот и входу управляемого генератора, а также первый и второй делители частоты, при этом выход второго элемента И подсоединен непосредственно к первому входу дополнительного элемента И и через первый делитель частоты подсоединен к первому входу фазового детектора, выход которого подсоединен к второму входу дополнительного элемента И, выход управляемого генератора через второй делитель частоты подсоединен к второму входу фазового детектора, управляющему входу счетчика импульсов и тактовому входу первого регистра сдвига, выход кр- торого подключен к информационному входу второго регистра сдвига, а выход второго регистра сдвига подсоединен к второму входу блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛЬТА-КОДЕК | 1998 |

|

RU2172554C2 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2395899C1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 2000 |

|

RU2191468C2 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Частотный модулятор | 1982 |

|

SU1166267A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Устройство синтеза испытательного сигнала измерителей фазочастотных характеристик | 1990 |

|

SU1795415A1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| СЛЕДЯЩИЙ ПРИЕМНИК ШИРОКОПОЛОСНОГО СИГНАЛА | 1999 |

|

RU2157052C1 |

| Цифровой телевизионный приемник | 1983 |

|

SU1321384A3 |

Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи информации для восстановления скорости цифрового потока при асинхронном сопряжении. Целью изобретения является повышение точности восстановления скорости входного сигнала. Устройство содержит элементы И 1, 4 и 20, элементы ИЛИ 2, 3 и 17, приемник 5 команд согласования скоростей, запоминающий блок (ЗБ) 6, фазовый детектор 7, фильтры 8 и 21 нижних частот, управляемый генератор (УГ) 9, делители 10 и 11 частоты, сумматор 12, счетчик 13 импульсов, регистры 14 и 15 сдвига, блок сравнения 16, кодопреобразователь 18 и цифроаналоговый преобразователь (ЦАП) 19. В зависимости от знака выделенной приемником 5 команды в цифровой поток, записываемый в ЗБ 6, с помощью элементов И 1 и 4 и элементов ИЛИ 2 и 3 вставляется дополнительный информационный символ или исключается лишний. При этом фазовые соотношения между сигналами считывания и записи в ЗБ 6, связанные между собой петлей фазовой автоподстройки частоты, изменяются скачкообразно. Блок сравнения 16 производит сравнение выходных кодов регистров 14 и 15. Если выполняется условие A*98В+1 или A*98B-1, гле A и B - соответствно коды регистров 14 и 15, то на первом или втором выходах блока сравнения 16 соответственно появляется сигнал "1", по которому код из регистра 14 переписывается в регистр 15. Выходной сигнал последнего через кодопреобразователь 18 формирует код для ЦАП 19 с учетом неленейности характеристики управления УГ 9. 1 ил.

| Аппарат для радиометрической съемки | 1922 |

|

SU124A1 |

| М.У.Поляка, - М Связь, 1976 | |||

| Левин Я.С. | |||

| Плоткин М.А | |||

| Цифровые системы передачи информации | |||

| - М.: Радио и связь, 1982 | |||

| с | |||

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-10-23—Публикация

1988-03-30—Подача