(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СИНТЕЗАТОР СЕТКИ ЧАСТОТ | 1995 |

|

RU2108655C1 |

| Синтезатор дискретной сетки частот | 1990 |

|

SU1762382A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

| Устройство для декодирования данных | 1988 |

|

SU1629912A1 |

| Генератор сигнала с дискретной частотной модуляцией | 1983 |

|

SU1152092A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| УСТРОЙСТВО ДЛЯ МОНИТОРИНГА СОСТОЯНИЯ ВЫСОКОВОЛЬТНЫХ ВВОДОВ | 2009 |

|

RU2401434C1 |

| Устройство для формирования частоты квантования цифрового фазометра | 1988 |

|

SU1541530A1 |

Изобретение относится к радиоизмерительной технике и может быть использовано для построения измерителей фазочастот- ных характеристик и группового времени запаздывания рздиоустройств. Цель - расширение частотного диапазона синтезирующих сигналов. В устройство, содержащее эталонный генератор 1, блок 2 ФАПЧ и делитель 3 частоты, введены мультиплексор 4, второй делитель 5 частоты, запоминающий блок 6, регистр 7, ЦАП 8 и ФНЧ 9, а также вычислительный блок 10 и блок 11 управления, которые соединены между собой шиной 12 адреса, шиной 13 управляющих сигналов и шиной 14 данных. 7 ил.

фиг. 1

Изобретение касается радиоизмерений и может быть использовано для построения высоко точных измерителей фазочастотных характеристик (ФЧХ) и группового времени запаздывания (ГВЗ) радиоустройств.

Цель изобретения - расширение частотного диапазона синтезируемых сигналов. ,; . ,;... ..:

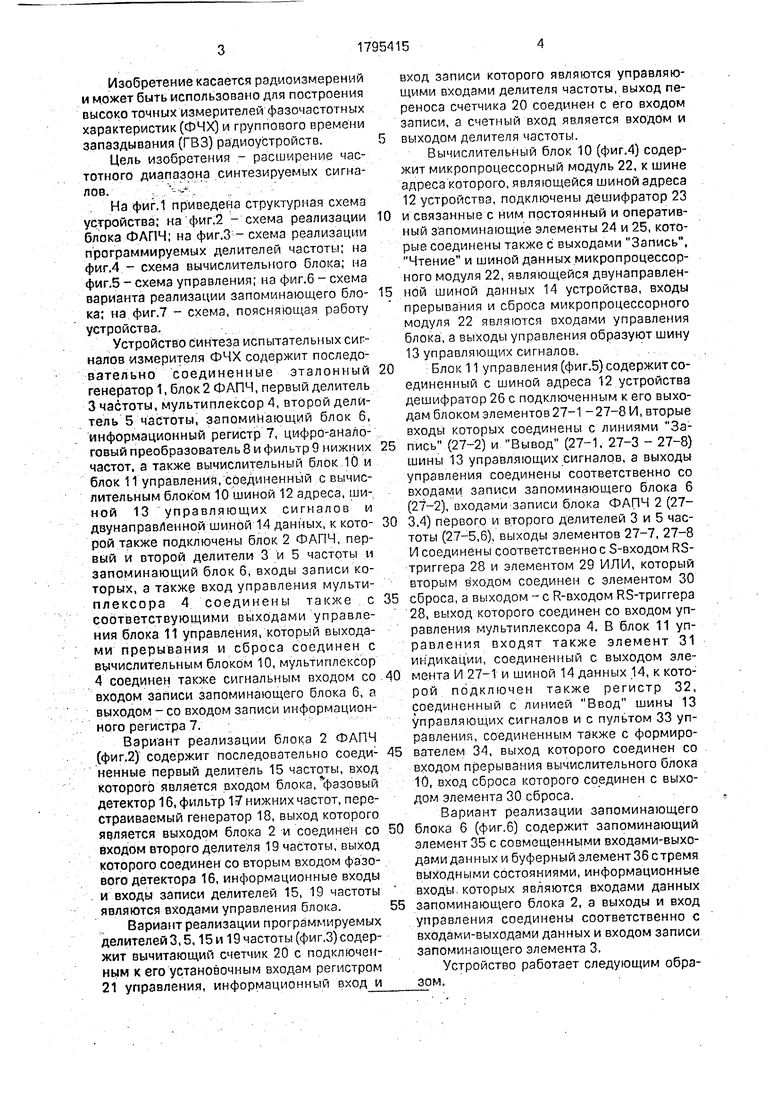

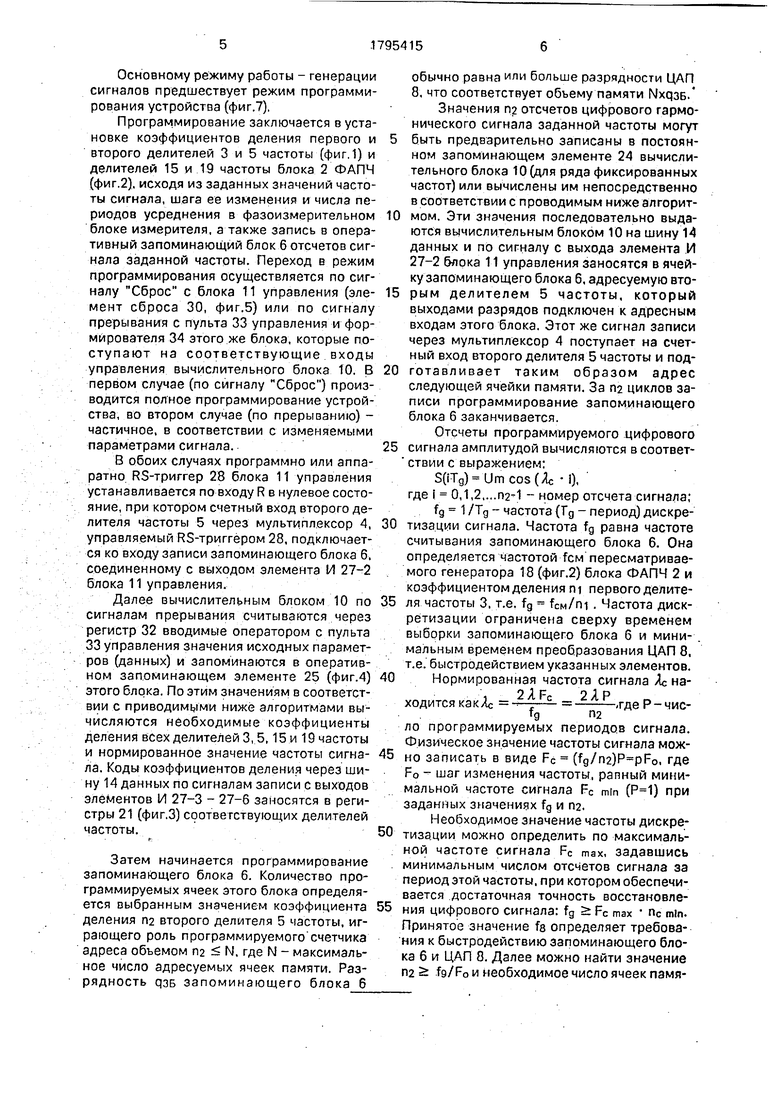

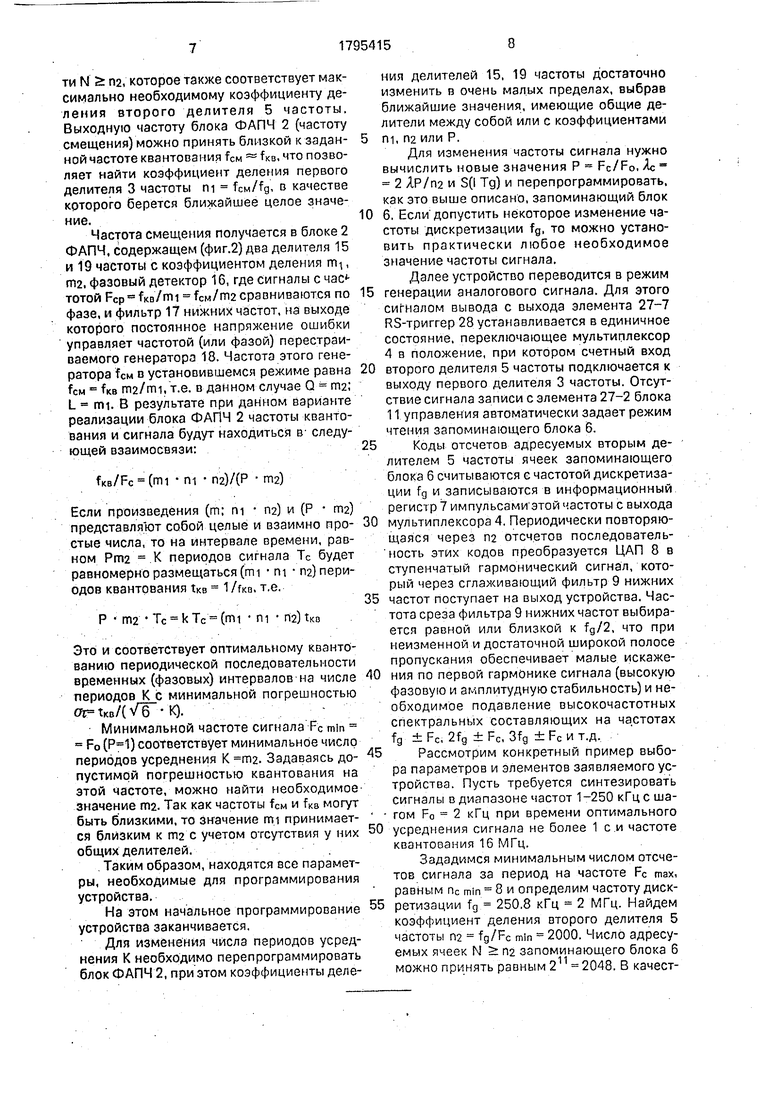

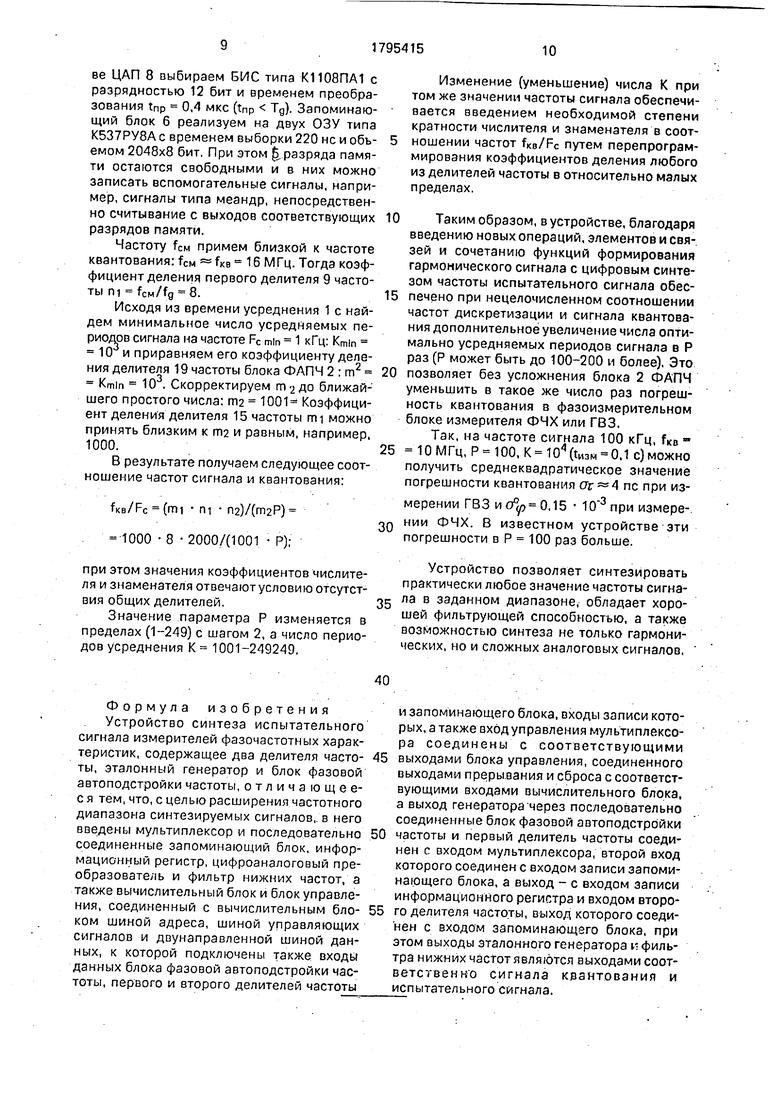

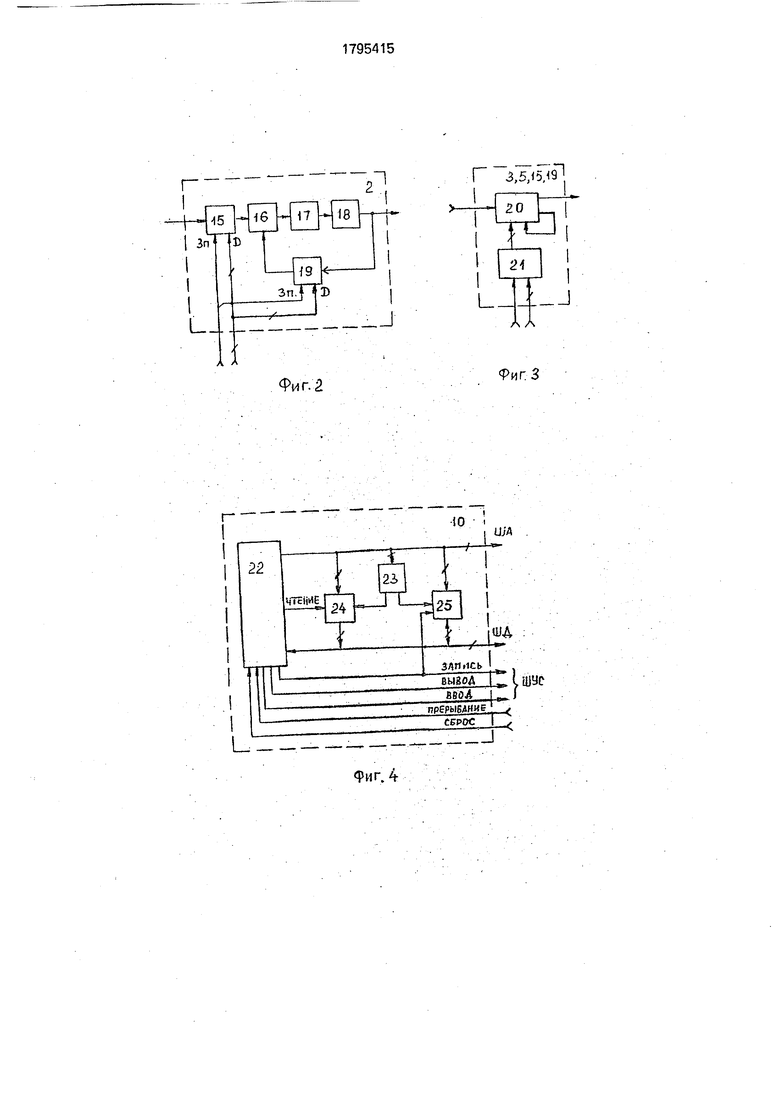

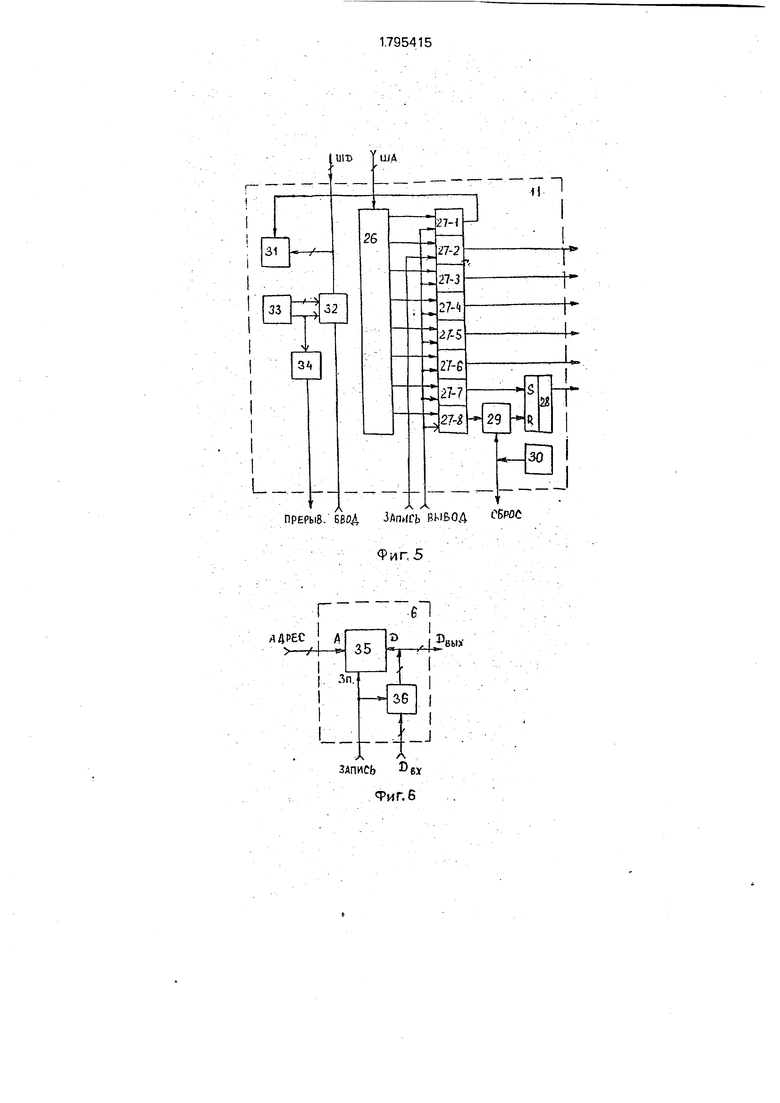

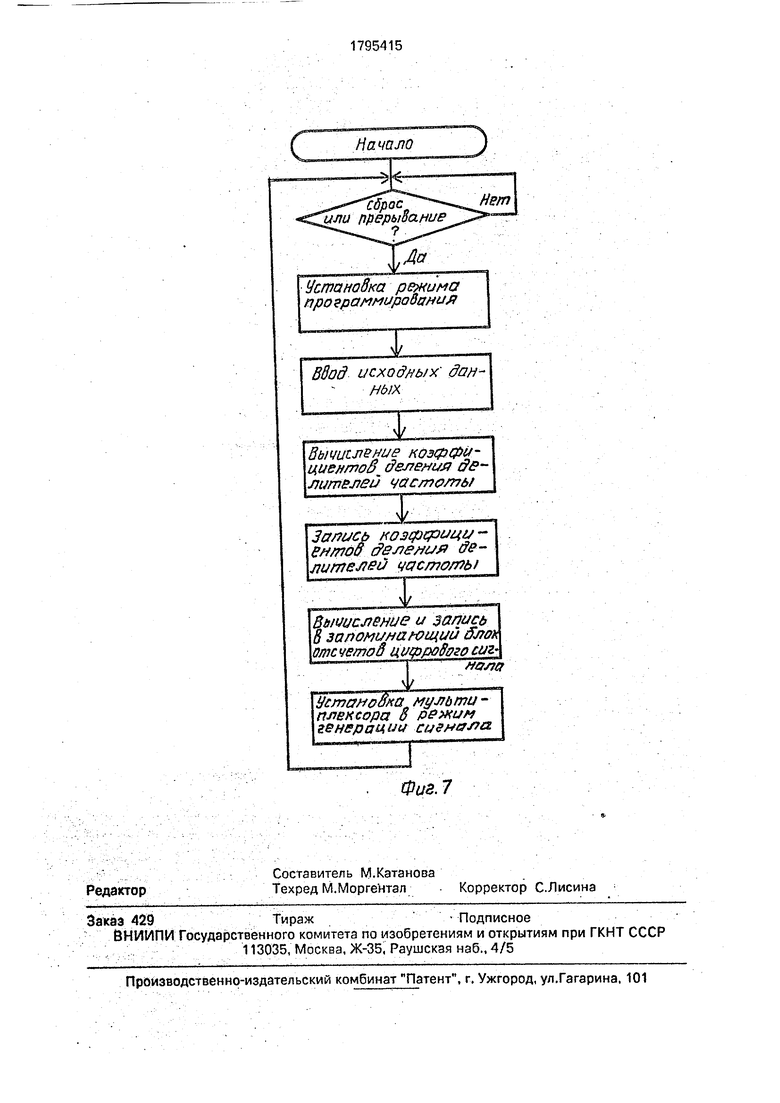

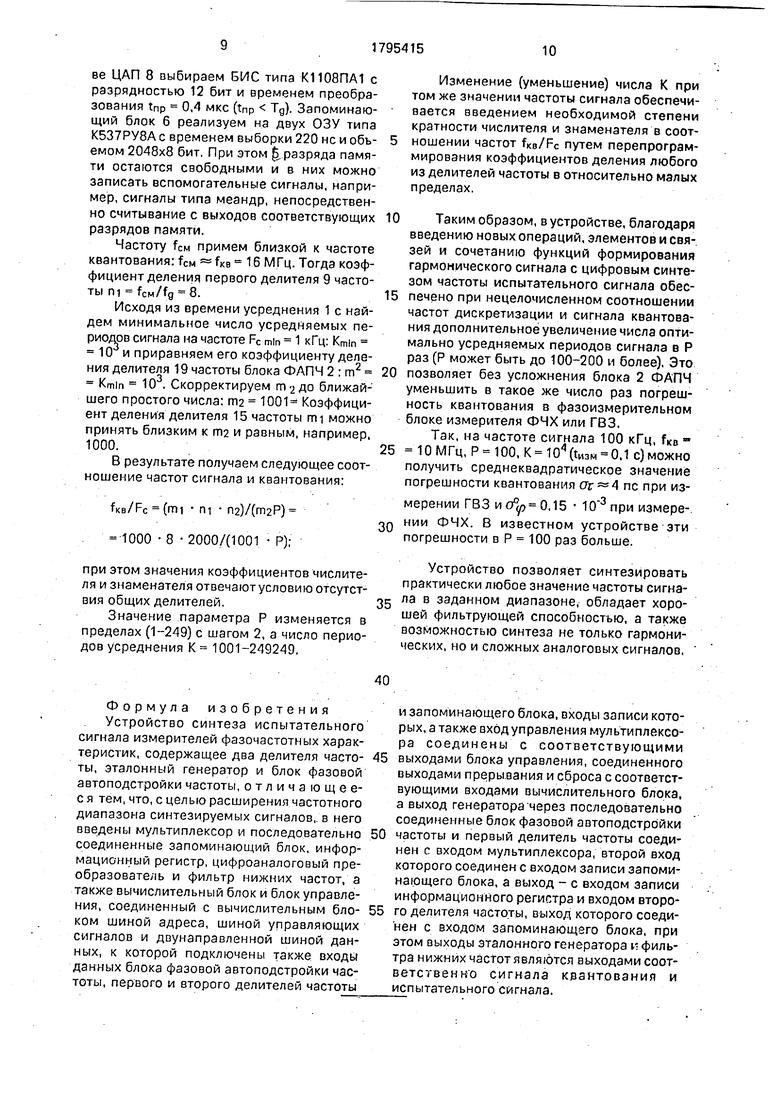

На фиг.1 приведена структурная схема устройства; на фиг.2 - схема реализации блока ФАПЧ; на фиг.З - схема реализации программируемых делителей частоты; на фиг.4 - схема вычислительного блока; на фиг.5 - схема управления; на фиг.6 - схема варианта реализации запоминающего бло- ка; на фиг.7 - схема, поясняющая работу устройства.

Устройство синтеза испытательных сигналов измерителя ФЧХ содержит последовательно соединенные эталонный генератор 1, блок2 ФАПЧ, первый делитель

3 частоты, мультиплексор 4, второй делитель 5 частоты, запоминающий блок 6, информационный регистр 7, цифро-аналоговый преобразователь 8 и фильтр 9 нижних частот, а также вычислительный блок 10 и блок 11 управления,соединенный с вычислительным блоком 10 шиной 12 адреса, шиной 13 управляющих сигналов и двунаправленной шиной 14 данных, к кото- рой также подключены блок 2 ФАПЧ, первый и второй делители 3 и 5 частоты и запоминающий блок 6, входы записи которых, а также вход управления мультиплексора 4 соединены также с соответствующими выходами управления блока 11 управления,который выходами прерывания и сброса соединен с вычислительным блоком 10, мультиплексор

4 соединен также сигнальным входом со входом записи запоминающего блока б, а выходом - со входом записи информационного регистра 7.

Вариант реализации блока 2 ФАПЧ (фиг.2) содержит последовательно соеди: ненные первый делитель 15 частоты, вход которого является входом блока, фазовый детектор 16, фильтр 17 нижних частот, перестраиваемый генератор 18, выход которого является выходом блока 2 и соединен со входом второго делителя .19 частоты, выход которого соединен со вторым входом фазового детектора 16, информационные входы . и входы записи делителей 15, 19 частоты являются входами управления блока.

Вариант реализации программируемых делителейЗ, 5,15 и 19 частоты (фиг.З)содержит вычитающий счетчик 20 с подключенным к его установочным входам регистром 21 управления, информационный вход и

вход записи которого являются управляющими входами делителя частоты, выход переноса счетчика 20 соединен с его входом записи, а счетный вход является входом и выходом делителя частоты.

Вычислительный блок 10 (фиг.4) содержит микропроцессорный модуль 22, к шине адреса которого, являющейся шиной адреса

12 устройства, подключены дешифратор 23 и связанные с ним постоянный и оперативный запоминающие элементы 24 и 25, которые соединены также с выходами Запись, Чтение и шиной данных микропроцессорного модуля 22, являющейся двунаправленной шиной данных 14 устройства, входы прерывания и сброса микропроцессорного модуля 22 являются входами управления блока, а выходы управления образуют шину

13 управляющих сигналов....

Блок 11 управления (фиг.5) содержит соединенный с шиной адреса 12 устройства дешифратор 26 с подключенным к его выходам блоком элементов 27-1 -27-8 И, вторые входы которых соединены с линиями Запись (27-2) и Вывод (27-1. 27-3 - 27-8) шины 13 управляющих сигналов, а выходы управления соединены соответственно со входами записи запоминающего блока 6 (27-2), входами записи блока ФАПЧ 2 (27- 3.4) первого и второго делителей 3 и 5 частоты (27-5,6), выходы элементов 27-7, 27-8 И соединены соответственно с S-входом RS- триггера 28 и элементом 29 ИЛИ, который вторым входом соединен с элементом 30 сброса, а выходом -с R-входом RS-триггера 28, выход которого соединен со входом управления мультиплексора 4. В блок 11 управления входят также элемент 31 индикации, соединенный с выходом элемента И 27-1 и шиной 14 данных 14, к которой подключен также регистр 32, соединенный с линией Ввод шины 13 управляющих сигналов и с пультом 33 управления, соединенным также с формирователем 34, выход которого соединен со входом прерывания вычислительного блока 10, вход сброса которого соединен с выходом элемента 30 сброса.

Вариант реализации запоминающего блока 6 (фиг.6) содержит запоминающий элемент 35 с совмещенными входами-выходами данных и буферный элемент 36 стремя выходными состояниями, информационные входы, которых являются входами данных запоминающего блока 2, а выходы и вход управления соединены соответственно с входами-выходами данных и входом записи Запоминающего элемента 3.

Устройство работает следующим образом,.

Основному режиму работы - генерации сигналов предшествует режим программирования устройства (фиг.7).

Программирование заключается в установке коэффициентов деления первого и второго делителей 3 и 5 частоты (фиг. 1) и делителей 15 и 19 частоты блока 2 ФАПЧ (фиг.2), исходя из заданных значений частоты сигнала, шага ее изменения и числа периодов усреднения в фазоизмерительном блоке измерителя, а также запись в оперативный запоминающий блок 6 отсчетов сигнала заданной частоты. Переход в режим программирования осуществляется по сигналу Сброс с блока 11 управления (элемент сброса 30, фиг.5) или по сигналу прерывания с пульта 33 управления и формирователя 34 этого же блока, которые поступают на соответствующие входы управления вычислительного блока 10. В первом случае (по сигналу Сброс) производится полное программирование устройства, во втором случае (по прерыванию) - частичное, в соответствии с изменяемыми параметрами сигнала.

В обоих случаях программно или аппа- ратно RS-триггер 28 блока 11 управления устанавливается по входу R в нулевое состояние, при котором счетный вход второго делителя частоты 5 через мультиплексор 4, управляемый RS-триггером 28, подключается ко входу записи запоминающего блока 6, соединенному с выходом элемента И 27-2 блока 11 управления.

Далее вычислительным блоком 10 по сигналам прерывания считываются через регистр 32 вводимые оператором с пульта 33 управления значения исходных параметров (данных) и запоминаются в оперативном запоминающем элементе 25 (фиг.4) этого блока. По этим значениям в соответствии с приводимыми ниже алгоритмами вычисляются необходимые коэффициенты деления всех делителей 3,5,15 и 19 частоты и нормированное значение частоты сигнала. Коды коэффициентов деления через шину 14 данных по сигналам записи с выходов элементов И 27-3 - 27-6 заносятся в регистры 21 (фиг.З) сротвегствующих делителей частоты.

Р;

Затем начинается программирование запоминающего блока 6. Количество программируемых ячеек этого блока определяется выбранным значением коэффициента деления П2 второго делителя 5 частоты, играющего роль программируемого счетчика адреса объемом П2 N, где N - максимальное число адресуемых ячеек памяти. Разрядность дзБ запоминающего блока 6

0

5

0

5

0

5

0

0

5

обычно равна или больше разрядности ЦАП 8, что соответствует объему памяти NxqsB.

Значения отсчетов цифрового гармонического сигнала заданной частоты могут быть предварительно записаны в постоянном запоминающем элементе 24 вычислительного блока 10 (для ряда фиксированных частот) или вычислены им непосредственно в соответствии с проводимым ниже алгоритмом. Эти значения последовательно выдаются вычислительным блоком 10 на шину 14 данных и по сигналу с выхода элемента И 27-2 блока 11 управления заносятся в ячейку запоминающего блока 6, адресуемую вто- рым делителем 5 частоты, который выходами разрядов подключен к адресным входам этого блока. Этот же сигнал записи через мультиплексор 4 поступает на счетный вход второго делителя 5 частоты и под- готавливэет таким образом адрес следующей ячейки памяти. За П2 циклов записи программирование запоминающего блока 6 заканчивается.

Отсчеты программируемого цифрового сигнала амплитудой вычисляются в соответ- степи с выражением:

S(iTg)Umcos(: I), где i 0,1,2.... - номер отсчета сигнала;

fg 1 /Tg - частота (fg - период) дискретизации сигнала. Частота fg равна частоте считывания запоминающего блока 6. Она определяется частотой тем пересматриваемого генератора 18 (фиг.2) блока ФАПЧ 2 и коэффициентом деления ni первого делителя частоты 3. т.е. fg fcM/ni . Частота дискретизации ограничена сверху временем выборки запоминающего блока б и мини- . мальным временем преобразования ЦАП 8, т.е. быстродействием указанных элементов.

Нормированная частота сигнала Ас находится ка к Ас

2 A Fc 2 Я Р

.где Р - чисfg12ло программируемых периодов сигнала.

Физическое значение частоты сигнала мож- 5 но записать в виде Fc (fg/n2), где FQ - шаг изменения частоты, рапный минимальной частоте сигнала Fc mtn () при заданных значениях fg и П2.

Необходимое значение частоты дискретизации можно определить по максимальной частоте сигнала Fc max, задавшись минимальным числом отсчетов сигнала за период этой частоты, при котором обеспечивается достаточная точность восстановления цифрового сигнала: fg Fc max nc min. Принятое значение fa определяет требования к быстродействию запоминающего блока б и ЦАП 8. Далее можно найти значение П2 Э: fg/Fo и необходимое число ячеек пэмяти N 5: П2, которое также соответствует максимально необходимому коэффициенту деления второго делителя 5 частоты. Выходную частоту блока ФАПЧ 2 (частоту смещения) можно принять близкой к задан- ной частоте квантования fCM TKQ, что позволяет найти коэффициент деления первого делителя 3 частоты щ Тсм/fg, в качестве которого берется ближайшее целое значение.

Частота смещения получается в блоке 2 ФАПЧ, содержащем (фиг.2) два делителя 15 и 19 частоты с коэффициентом деления ггц, ГП2, фазовый детектор 16, где сигналы с тотой Fcp fKB/mi fcM/m2 сравниваются по фазе, и фильтр 17 нижних частот, на выходе которого постоянное напряжение ошибки управляет частотой (или фазой) перестраиваемого генератора 18. Частота этого генератора fCM в установившемся режиме равна fcM fue m2/mi, т.е. в данном случае Q т2, L mi. В результате при данном варианте реализации блока ФАПЧ 2 частоты квантования и сигнала будут находиться в- следующей взаимосвязи:

WFC (mi щ П2)/(Р rri2)

Если произведения (т; т 112) и (Р т2) представляют собой целые и взаимно про- стые числа, то на интервале времени, равном Ргп2 К периодов сигнала Тс будет равномерно размещаться (mi щ па) периодов квантования tKa 1/гкв, т.е.

Р ГП2 Тс k Тс (mi щ П2) tKO

Это и соответствует оптимальному квантованию периодической последовательности временных (фазовых) интервалов на числе периодов К с минимальной погрешностью

Ot-W().

Минимальной частоте сигнала PC min Fo () соответствует минимальное число периодов усреднения К mz. Задаваясь до- пуетимрй погрешностью квантования на этой частоте, можно найти необходимое Значение т2. Так как частоты fCM и Кв могут быть близкими, то значение mi принимает- ся близким к ГП2 с учетом отсутствия у них общих делителей.

. Таким образом, находятся все параметры, необходимые для программирования устройства.

На этом начальное программирование устройства заканчивается.

Для изменения числа периодов усреднения К необходимо перепрограммировать блок ФАПЧ 2, при этом коэффициенты деления делителей 15, 19 частоты достаточно изменить в очень малых пределах, выбрав ближайшие значения, имеющие общие делители между собой или с коэффициентами

Щ, П2 ИЛИ Р.

Для изменения частоты сигнала нужно вычислить новые значения Р Fc/Fo, Дс 2 Л.Р/П2 и S(l Tg) и перепрограммировать, как это выше описано, запоминающий блок 6. Если допустить некоторое изменение частоты дискретизации fg, то можно установить практически любое необходимое значение частоты сигнала.

Далее устройство переводится в режим генерации аналогового сигнала. Для этого сигналом вывода с выхода элемента 27-7 RS-триггер 28 устанавливается в единичное состояние, переключающее мультиплексор 4 в положение, при котором счетный вход второго делителя 5 частоты подключается к выходу первого делителя 3 частоты. Отсутствие сигнала записи с элемента 27-2 блока 11 управления автоматически задает режим чтения запоминающего блока 6.

Коды отсчетов адресуемых вторым делителем 5 частоты ячеек запоминающего блока 6 считываются с частотой дискретизации fg и записываются в информационный регистр 7 импульсами этой частоты с выхода мультиплексора 4. Периодически повторяющаяся через П2 отсчетов последователь- ность этих кодов преобразуется ЦАП 8 в ступенчатый гармонический сигнал, который через сглаживающий фильтр 9 нижних частот поступает на выход устройства. Частота среза фильтра 9 нижних частот выбирается равной или близкой к fg/2, что при неизменной и достаточной широкой полосе пропускания обеспечивает малые искажения по первой гармонике сигнала (высокую фазовую и амплитудную стабильность) и необходимое подавление высокочастотных спектральных составляющих на частотах

fg ± Fc, 2fg ± Fc, 3fg ± FC И Т.Д.

Рассмотрим конкретный пример выбора параметров и элементов заявляемого устройства. Пусть требуется синтезировать сигналы в диапазоне частот 1-250 кГц с шагом FQ 2 кГц при времени оптимального усреднения сигнала не более 1 с.и частоте квантования 16 МГц.

Зададимся минимальным числом отсчетов сигнала за период на частоте Fc max, равным nc min 8 и определим частоту дискретизации fg. 250.8 кГц 2 МГц. Найдем коэффициент деления второго делителя 5 частоты П2 fg/Fc min 2000. Число адресуемых ячеек N П2 запоминающего блока 6 можно принять равным 211 2048. В качестве ЦАП 8 выбираем БИС типа К1108ПА1 с разрядностью 12 бит и временем преобразования tnp 0,4 мкс (tnp Tg). Запоминающий блок б реализуем на двух ОЗУ типа К537РУ8А с временем выборки 220 не и объемом 2048x8 бит. При этом разряда памяти остаются свободными и в них можно записать вспомогательные сигналы, например, сигналы типа меандр, непосредственно считывание с выходов соответствующих разрядов памяти.

Частоту fCM примем близкой к частоте квантования: fen fxa 16 МГц. Тогда коэффициент деления первого делителя 9 частоты щ fcM/fg 8.

Исходя из времени усреднения 1 с найдем минимальное число усредняемых периодов сигнала на частоте Fc min 1 кГц: Kmin 10 и приравняем его коэффициенту деления делителя 19 частоты блока ФАПЧ 2 : m Kmin 103. Скорректируем т-2ДО ближайшего простого числа: т2 1001- Коэффициент деления делителя 15 частоты mi можно принять близким к та и равным, например, 1000.

В результате получаем следующее соотношение частот сигнала и квантования:

WFc (mi щ п2)/(т2Р) . 1000-8 2000/0 001 Р);

при этом значения коэффициентов числителя и знаменателя отвечают условию отсутствия общих делителей.

Значение параметра Р изменяется в пределах (1-249) с шагом 2, а число периодов усреднения К 1001-249249.

Формула изобретения Устройство синтеза испытательного сигнала измерителей фазочастотных характеристик, содержащее два делителя частоты, эталонный генератор и блок фазовой автоподстройки частоты, отличаю щее- с я тем, что, с целью расширения частотного диапазона синтезируемых сигналов,, в него введены мультиплексор и последовательно соединенные запоминающий блок, информационный регистр, цифроаналоговый преобразователь и фильтр нижних частот, а также вычислительный блок и блок управления, соединенный с вычислительным блоком шиной адреса, шиной управляющих сигналов и двунаправленной шиной данных, к которой подключены также входы данных блока фазовой автоподстройки частоты, первого и второго делителей частоты

Изменение (уменьшение) числа К при том же значении частоты сигнала обеспечивается введением необходимой степени кратности числителя и знаменателя в соот- ношении частот TKB/FC путем перепрограммирования коэффициентов деления любого из делителей частоты в относительно малых пределах.

Таким образом, в устройстве, благодаря введению новыхопераций, элементов и связей и сочетанию функций формирования гармонического сигнала с цифровым синтезом частоты испытательного сигнала обеспечено при нецелочисленном соотношении частот дискретизации и сигнала квантования дополнительное увеличение числа оптимально усредняемых периодов сигнала в Р раз (Р может быть до 100-200 и более), Это

позволяет без усложнения блока 2 ФАПЧ уменьшить в такое же число раз погрешность квантования в фазоизмерительном блоке измерителя ФЧХ или ГВЗ.

Так, на частоте сигнала 100 кГц, fKs

10 МГц, Р 100, (и,зм 0.1 с) можно получить среднеквадратическое значение погрешности квантования От 4 пс при измерении ГВЗ и о% 0,15 при измере-.

нии ФЧХ. В известном устройстве эти погрешности в Р 100 раз больше.

Устройство позволяет синтезировать практически любое значение частоты сигна- ла в заданном диапазоне, обладает хорошей фильтрующей способностью, а также возможностью синтеза не только гармонических, но и сложных аналоговых сигналов,

и запоминающего блока, входы записи которых, а также вход управления мультиплексора соединены с соответствующими

выходами блока управления, соединенного выходами прерывания и сброса с соответствующими входами вычислительного блока, а выход генератора через последовательно соединенные блок фазовой автоподстройки

частоты и первый делитель частоты соединен с входом мультиплексора, второй вход которого соединен с входом записи запоминающего блока, а выход - с входом записи информационного регистра и входом второго делителя частоты, выход которого соединен с входом запоминающего блока, при этом выходы эталонного генератора и фильтра нижних частот являются выходами соответственно сигнала квантования и испытательного сигнала.

j

, 3KH73l rf3dU

Ofiffl

id

m . -: j

vm

i °l

1 б1г Л J

1

3HH3ih

L0

aifrsea

г

ЗАПИСЬ D6X

Фиг. 6

.п

ВВод исходных данных

Вычиьление коэффициентов деленил делителей час/по/пы

Зались козфсрици- ентоу деления делителей уас/но/пы

Вычисление и запись 8 запоминающий ffjtok от с четод цуфро8яго сиг

Установка мультиплексора о режим генерации сиена-ля.

Начало

J

| Цифровые методы измерения сдвига фаз | |||

| Новосибирск, Наука, 1979 | |||

| с | |||

| Ротационный фильтр-пресс для отжатия торфяной массы, подвергшейся коагулированию, и т.п. работ | 1924 |

|

SU204A1 |

| Устройство для измерения фазочастотных характеристик четырехполюсников | 1977 |

|

SU691774A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-02-15—Публикация

1990-03-29—Подача