Изобретение относится к электронике, в частности к системам фазовой автоподстройки частоты с цифровыми детекторами, предназначено для точной настройки управляемого генератора на частоту внешнего сигнала в условиях пропусков синхроимпульсов в широком диапазоне частот и может найти применение в приборостроении, телевидении, электросвязи.

Известно устройство для фазовой автоподстройки частоты (ФАПЧ) [1], включающее в себя фазовый детектор на основе одновибратора, четырех ключей и двух D-триггеров, реверсивный счетчик, цифроаналоговый преобразователь (ЦАП), управляемый генератор и делитель частоты.

В указанном устройстве точная настройка на заданную частоту обеспечивается тем, что одновибратор фазового детектора, разрешающий поступление сигналов на входы триггеров, запускается импульсами входного сигнала, благодаря чему фазовая ошибка при пропуске этих импульсов не вычисляется.

Однако такое устройство имеет узкий диапазон перестройки по частоте, поскольку длительность импульсов входящего в состав фазового детектора одновибратора должна равняться половине периода входного сигнала. Кроме того, включение в контур ФАПЧ интегрального регулятора (счетчика) еще более сужает диапазон частот, в котором обеспечивается сходимость процесса настройки.

Известно также устройство ФАПЧ [2], включающее в себя фазовый детектор, состоящий из двух счетчиков и D-триггера, два дешифратора, реверсивный счетчик, ЦАП и управляемый генератор, причем детектор работает в релейном режиме.

Устройство обеспечивает точную настройку генератора в условиях пропусков импульсов входного сигнала, поскольку эти импульсы являются тактовыми для фазового детектора и реверсивного счетчика. При отсутствии сигнала на входе контура ФАПЧ величина фазовой ошибки, занесенная в реверсивный счетчик, не меняется.

Однако подобное устройство обладает узким рабочим диапазоном, поскольку при резком изменении частоты входного сигнала контур ФАПЧ может настраиваться на частоты, кратные заданной. Кроме того, включение в контур ФАПЧ интегрального регулятора (счетчика) существенно ухудшает динамические характеристики устройства.

Наиболее близким техническим решением является устройство ФАПЧ [3], включающее в себя фазовый детектор, усреднитель, цифровой ПИ-регулятор, ЦАП и управляемый генератор, а также блок коррекции ошибки по частоте при переполнении усреднителя.

Рассматриваемое устройство ФАПЧ обеспечивает точную настройку генератора в широком диапазоне частот, в том числе при пропуске импульсов входного сигнала, благодаря применению интегрального блока коррекции ошибки.

Недостатком данного устройства является выход системы из режима фазовой синхронизации при переполнении регистров ПИ-регулятора и блока коррекции. Кроме того, введение дополнительного контура коррекции ошибки ухудшает динамические характеристики системы ФАПЧ в режиме "захвата" частоты.

Технический результат изобретения состоит в обеспечении точной настройки контура ФАПЧ на частоту входного сигнала, в том числе при пропуске части его импульсов, возможности настройки в широком диапазоне частот, а также достижении высокого быстродействия и устойчивости системы.

Для достижения технического результата в контур ФАПЧ, состоящий из последовательно соединенных фазового детектора (ФД), ЦАП, фильтра нижних частот (ФНЧ), генератора, управляемого напряжением (ГУН), и делителя частоты с коэффициентом передачи 1/N, вводятся реверсивный счетчик (PC) по модулю N с возможностью установки в заданное состояние, параллельный регистр, три ключевых элемента, логический элемент "ИЛИ" и блок сравнения частот (БСЧ).

Первый вход БСЧ соединен с входом контура ФАПЧ, второй вход - с выходом ДЧ, а выход БСЧ подключен к управляющим входам первого и второго ключевых элементов. Входы PC +1 и -1 соединены с выходами ошибки ФД, тактовый вход PC через третий ключевой элемент соединен с выходом ГУН, выход переполнения PC через первый и второй ключевые элементы соединен с входом управления третьего ключевого элемента и входом элемента "ИЛИ", выход которого соединен с входом установки PC, на входы данных которого подается двоичный код числа N/2 (011...1). Выходы данных PC соединены с соответствующими входами регистра, тактовый вход которого соединен с выходом обнуления ФД и с другим входом логического элемента "ИЛИ".

Сопоставительный анализ с прототипом показал, что предлагаемое устройство ФАПЧ отличается наличием PC, параллельного регистра, блока сравнения частот (БСЧ), элемента "ИЛИ", первого, второго и третьего ключевых элементов, а также функциональными связями между ними.

Блок сравнения частот осуществляет переключение режимов работы устройства ФАПЧ в зависимости от величины ошибки по частоте. Если эта ошибка не превышает заданного уровня, устройство работает в режиме фазовой синхронизации, если превышает - в режиме "захвата" частоты.

Применение PC обеспечивает преобразование ШИМ сигнала фазовой ошибки в двоичный код путем счета импульсов ГУН по модулю N. Пределы изменения кода от 00. ..0 до 11...1 соответствуют изменению фазовой ошибки от - 2π до +2π, код нулевой ошибки - 011..1. При фазовых ошибках, превышающих по модулю 2π, код на выходе счетчика зависит от режима работы устройства ФАПЧ.

В режиме фазовой синхронизации за счет соединения выхода переполнения PC с его входом установки через первый ключевой элемент и элемент "ИЛИ" формируется код ошибки, взятой по модулю 2π.

В режиме "захвата" частоты благодаря соединению выхода переполнения PC через второй ключевой элемент с управляющим входом третьего ключевого элемента фиксируется максимальное значение кода ошибки.

Параллельный регистр, подключенный к выходам данных PC, обеспечивает хранение кода фазовой ошибки в течение периода преобразования сигнала ФД, причем запись в регистр осуществляется импульсом обнуления ФД.

Применения PC и блока сравнения частот в системах ФАПЧ являются известными техническими решениями. Однако в данном случае введение новых функциональных связей, а также регистра позволяет обрабатывать фазовую ошибку в зависимости от режима работы устройства. Вычисление ошибки по модулю 2π в режиме фазовой синхронизации дает возможность избежать смешения частоты настройки ФАПЧ при пропуске импульсов входного сигнала. Фиксация максимального по модулю значения ошибки в режиме "захвата" частоты позволяет ускорить переходный процесс в контуре ФАПЧ и избежать настройки на кратные частоты.

Таким образом, введение новых связей и элементов обеспечивает существенное повышение точности и быстродействия устройства ФАПЧ по сравнению с аналогами. Следовательно, отмеченные отличия предлагаемого устройства от прототипа являются существенными.

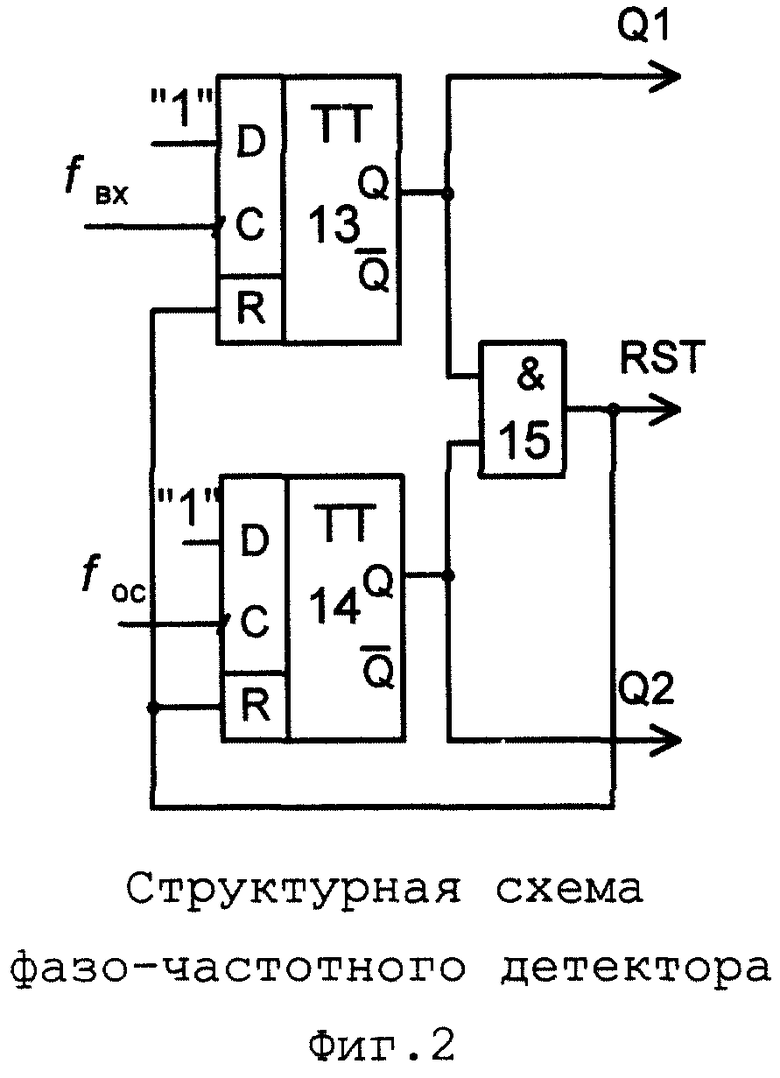

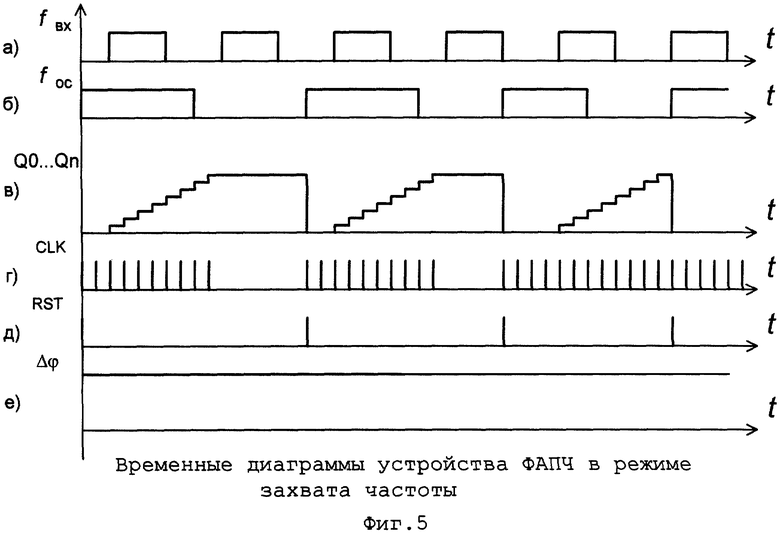

На фиг. 1, 2 и 3 приведены структурные схемы устройства ФАПЧ, фазового детектора и блока сравнения частот, а на фиг.4 и 5 - временные диаграммы, поясняющие работу устройства в режимах фазовой синхронизации и "захвата" частоты соответственно.

Структурная схема устройства ФАПЧ (фиг.1) включает в себя цифровой ФД 1, PC 2, ключевые элементы 3, 4 и 6, элемента "ИЛИ" 5, параллельный регистр 7, ЦАП 8, ФНЧ 9, ГУН 10, делитель частоты 11, блок сравнения частот (БСЧ) 12.

На входы ФД 1 и БСЧ 12 подается входной сигнал ФАПЧ fвх и сигнал обратной связи с выхода ДЧ 11 fоc, выход БСЧ 12 соединен с управляющими входами элементов 3 и 4. Выходы опережения Q1 и отставания Q2 ФД 1 подключены к входам +1 и -1 PC 2 соответственно, а выход обнуления ФД 1 соединен с входом элемента "ИЛИ" 5 и тактовым входом регистра 7. На входы данных D1...Dn PC 2 подается двоичный код числа N/2 01...1, тактовый вход PC 2 через ключевой элемент 6 соединен с выходом ГУН 10, выход переполнения PC 2 через ключевой элемент 4 соединен с управляющим входом элемента 6 и через ключевой элемент 3 - входом элемента "ИЛИ", выход которого подключен к входу установки PC 2 V. Выходы Q1...Qn PC 2 подключены к входам D1...Dn регистра 7, тактовый вход которого соединен с выходом обнуления ФД 1 и другим входом элемента "ИЛИ". Цифровой код с выходов Q1...Qn регистра 7 поступает на входы D1...Dn ЦАП 8, с выхода которого аналоговый сигнал фазовой ошибки через ФНЧ 9 поступает на вход управления ГУН 10. На выходе ГУН 10 формируется выходной сигнал контура ФАПЧ fвых, поступающий через делитель частоты 11 на вход обратной связи ФД 1 и блока сравнения частот 12.

Фазовый детектор 1 может быть реализован на основе двух D-триггеров 13, 14 и элемента "И" 15 (фиг.2). Сигналы fвх и fос поступают на тактовые входы триггеров, на входы данных которых подаются логические "1". Выходы Q1 и Q2 триггеров 13 и 14 подключены к входам элемента "И" 15, на выходе которого формируется сигнал обнуления RST, поступающий на входы сброса триггеров R.

Блок сравнения частот может быть реализован на базе счетчика 16, PC 19, двух элементов "НЕ-И" 17 и 18, D-триггера 20 (фиг.3). Входной сигнал fвх поступает на тактовый вход счетчика 16 и на вход элемента "НЕ-И" 17, а сигнал обратной связи foc - на вход другого элемента "НЕ-И" 18. Выход переполнения счетчика 16 соединен с его входом сброса, входом установки PC 19 и тактовым входом D-триггера 20. Выход переполнения PC 19 соединен с инвертирующими входами элементов "НЕ-И" 17, 18 и входом данных D-триггера 20, на входы данных PC 19 подается код 011...1.

В режиме фазовой синхронизации устройство ФАПЧ работает следующим образом. На входы ФД 1 поступают последовательности импульсов fвх и fос (фиг.4 а, б), в результате на выходах Q1 и Q2 формируются ШИМ сигналы фазовой ошибки. Сигналы фазовой ошибки поступают на входы +1 и -1 PC 2 и преобразуются в цифровой код путем счета импульсов ГУН 11 по модулю N (фиг.4 в). По окончании периода ШИМ сигнала на выходе ФД 1 возникает импульс обнуления (фиг. 4 д), по которому код ошибки заносится в регистр 7, a PC 2 устанавливается в исходное состояние 01....1.

Когда PC 2 переходит в состояние 00...0 или 11...1, формируется сигнал переполнения, поступающий через ключевой элемент 3 и элемент "ИЛИ" 5 на вход установки V, и в счетчик заносится код 01...1. Таким образом, на выходе PC 2 формируется и заносится в регистр код фазовой ошибки, взятой по модулю 2π. Этот код затем преобразуется ЦАП 8 в аналоговый сигнал ошибки (фиг.4 е), поступающий через ФНЧ 9 на вход ГУН 10. Такое преобразование сигнала ошибки предотвращает смещение частоты настройки ФАПЧ при пропуске импульсов входного сигнала.

В режиме "захвата" частоты преобразование сигнала фазовой ошибки ФД 1 в цифровой код осуществляется, как и в предыдущем случае, при помощи PC 2 (фиг.5 а-в). Однако при переполнении PC 2 сигнал с его выхода через ключевой элемент 4 поступает на управляющий вход ключевого элемента 6, блокируя прохождение импульсов ГУН 10 на тактовый вход PC 2. В результате максимальное значение кода ошибки фиксируется PC 2, а затем записывается в регистр 7. Тем самым обеспечивается оптимальное быстродействие, а также предотвращается настройка контура ФАПЧ на кратные частоты.

Переключение режимов работы устройства ФАПЧ осуществляется БСЧ 12, при этом PC 19 блока вычисляет ошибку по частоте как разность числа импульсов fвх и fос на интервале времени, задаваемом счетчиком 16 (фиг.3). Если полученная разность не превышает заданный уровень, устройство работает в режиме фазовой синхронизации, если превышает - в режиме "захвата" частоты. В первом режиме сигнал БСЧ 12 замыкает ключ 3, разрешая прохождение сигнала переполнения PC 2 на вход элемента "ИЛИ". Во втором режиме замыкается ключ 4, разрешая прохождение сигнала переполнения PC 2 на управляющий вход ключевого элемента 6.

Таким образом, предлагаемое устройство ФАПЧ обеспечивает по сравнению с прототипом более высокую точность настройки на частоту, в том числе при пропуске импульсов входного сигнала, и высокое быстродействие при отработке ошибок по частоте.

Источники информации

1. Импульсные системы фазовой автоподстройки частоты. /В.В. Григорьев, В.Н. Дроздов, Ю.А. Сабинин и др. - Л.: Энергоатомиздат, 1982. - 88 с., ил.

2. AC 1781820 /МКИ 5 H 03 L 7/06/ Зильберг Е.В. Устройство фазовой автоподстройки частоты. /"БИ", 1992 г. - 46, с. 210.

3. АС 1739487 /МКИ 5 Н 03 К 7/00. /Воробьев А.С. Устройство для фазовой автоподстройки частоты/ "БИ", 1992 г. - 21, с. 218.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР С V-ОБРАЗНЫМ ЗАКОНОМ МОДУЛЯЦИИ ЧАСТОТЫ | 2009 |

|

RU2407144C1 |

| Синтезатор частот | 1976 |

|

SU799101A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1995 |

|

RU2076458C1 |

| ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА | 1996 |

|

RU2138903C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СЛАБЫХ МАГНИТНЫХ ПОЛЕЙ | 2022 |

|

RU2799401C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Широкополосный цифровой фазометр | 1990 |

|

SU1746325A1 |

| ДЕЛЬТА-КОДЕК | 1998 |

|

RU2172554C2 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

Изобретение относится к электронике, может использоваться для точной настройки управляемого генератора на частоту внешнего сигнала в условиях пропусков синхроимпульсов. Устройство фазовой автоподстройки частоты содержит фазовый детектор, цифроаналоговый преобразователь, генератор, управляемый напряжением, делитель частоты, реверсивный счетчик с модулем счета N, три ключевых элемента, логический элемент ИЛИ, параллельный регистр и блок сравнения частот. Достигаемый технический результат - обеспечение точной настройки контура фазовой автоподстройки частоты на частоту входного сигнала в широком диапазоне частот, достижение высокого быстродействия и устойчивости. 5 ил.

Устройство фазовой автоподстройки частоты, состоящее из фазового детектора (ФД) и последовательно соединенных цифроаналогового преобразователя (ЦАП), фильтра нижних частот, генератора, управляемого напряжением (ГУН) и делителя частоты, причем один вход ФД является входом устройства, а другой соединен с выходом делителя частоты, отличающееся тем, что в него введены реверсивный счетчик с модулем счета N (РС), первый, второй и третий ключевые элементы, логический элемент ИЛИ, параллельный регистр и блок сравнения частот, причем входы +1 и -1 РС соединены с соответствующими выходами фазовой ошибки ФД, тактовый вход РС через третий ключевой элемент соединен с выходом ГУН, выход переполнения РС через первый ключевой элемент соединен с входом элемента ИЛИ и через второй ключевой элемент - с входом управления третьего ключевого элемента, выход элемента ИЛИ соединен с входом установки РС, на входы данных которого подается двоичный код числа N/2, выходы данных РС соединены с соответствующими входами параллельного регистра, тактовый вход которого соединен с выходом обнуления ФД и с другим входом элемента ИЛИ, выходы данных параллельного регистра соединены с соответствующими входами ЦАП, первый вход блока сравнения частот соединен с входом устройства, второй вход - с выходом делителя частоты, выход блока сравнения частот соединен с управляющими входами первого и второго ключевых элементов.

| Устройство для фазовой автоподстройки частоты | 1990 |

|

SU1739487A1 |

| Устройство фазовой автоподстройки частоты | 1985 |

|

SU1338071A1 |

| Устройство фазовой автоподстройки частоты | 1987 |

|

SU1518881A1 |

| US 5838205 A, 17.11.1998 | |||

| US 5726607 A, 10.03.1998 | |||

| US 5122762 A, 16.06.1992 | |||

| US 5128632 A, 07.07.1992 | |||

| US 5563552 A, 08.10.1996. | |||

Авторы

Даты

2002-10-20—Публикация

2000-06-21—Подача