Изобретение относится к электротехнике и может быть использовано в источниках гарантированного питания для управления преобразователями постоянного напряжения в переменное со ступенчато-синусоидальной формой выходного напряжения.

Цель изобретения - повышение КПД преобразователя.

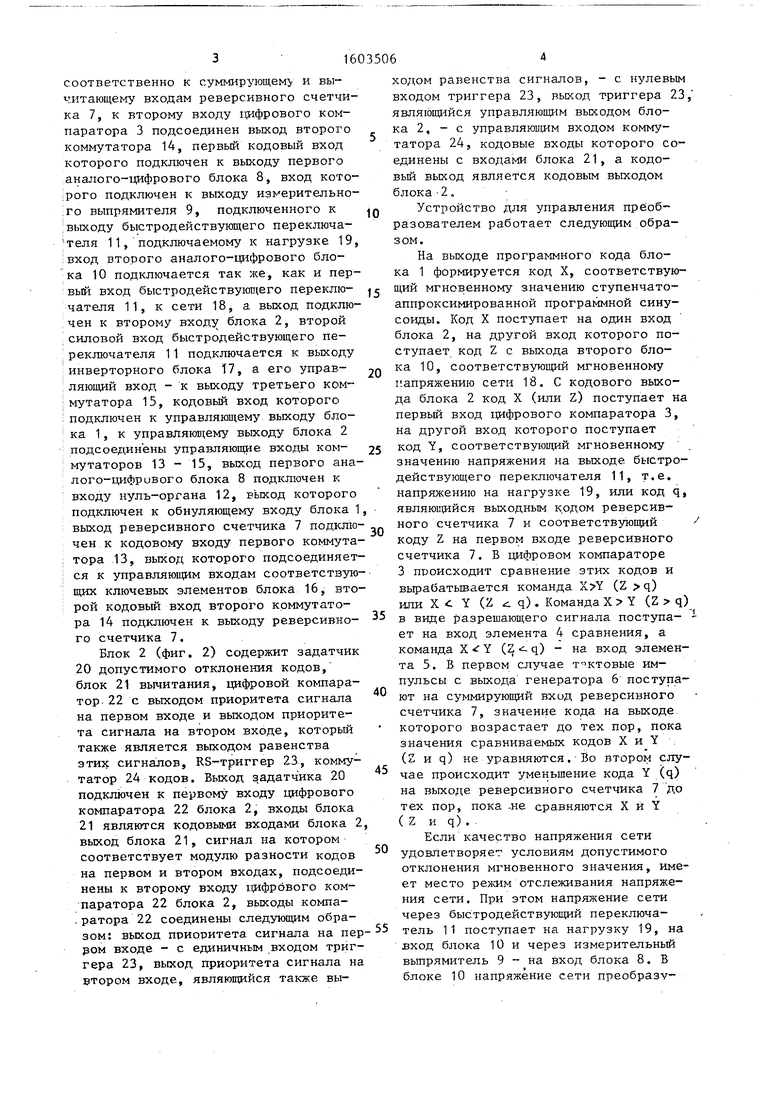

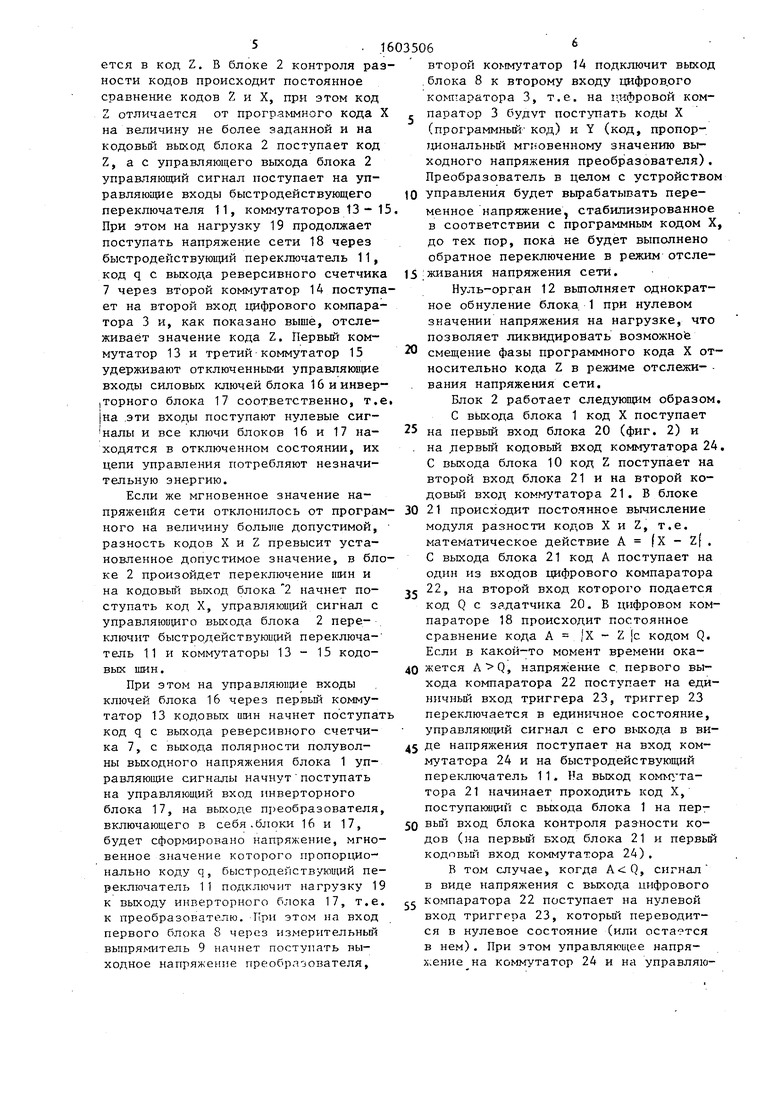

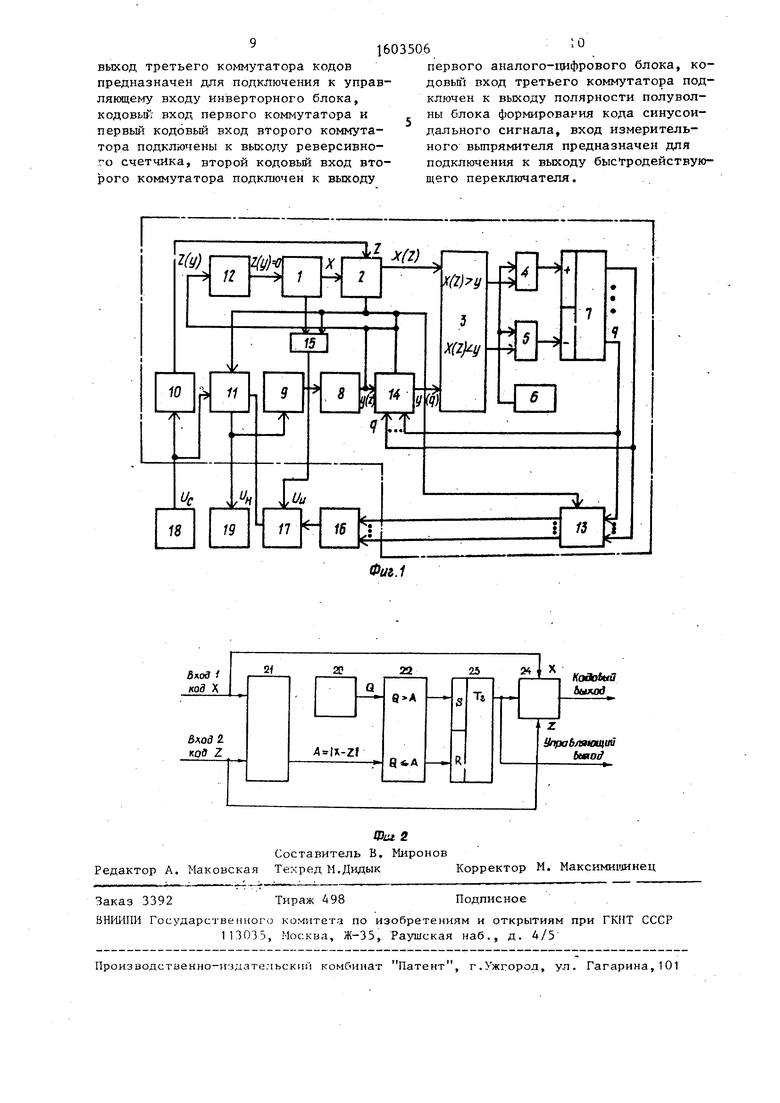

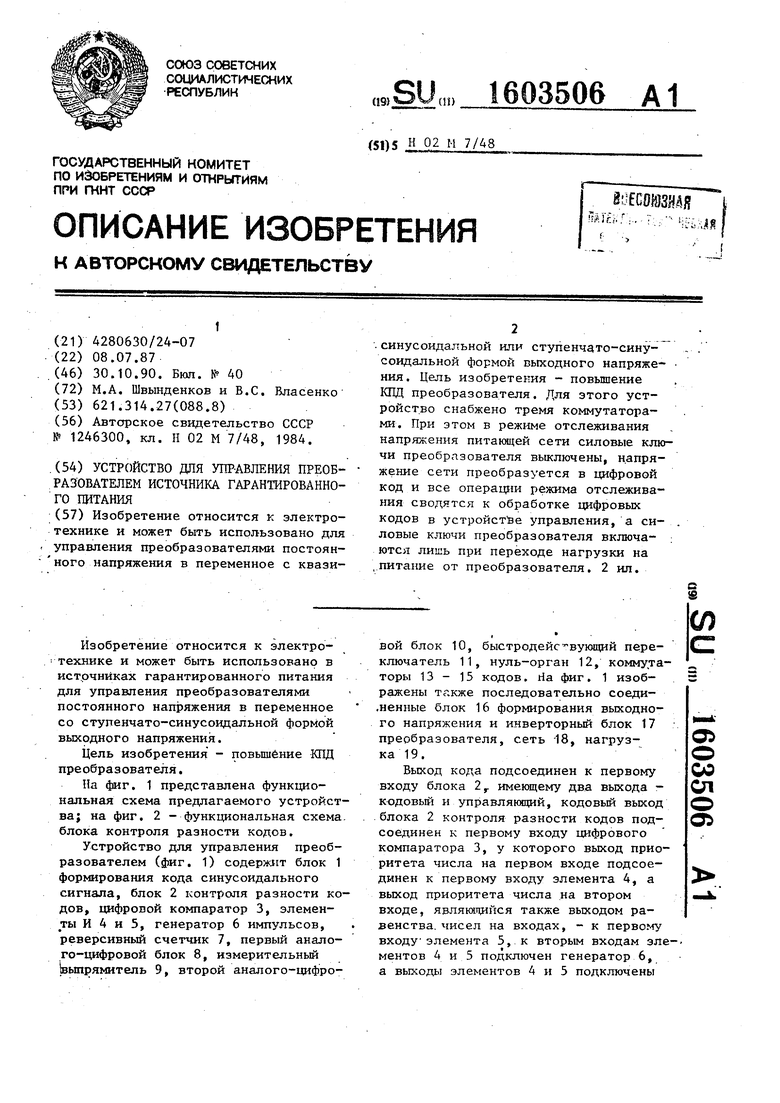

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема, блока контроля разности кодов.

Устройство для управления преобразователем (фиг. 1) содерз лт блок 1 формирования кода синусоидального сигнала, блок 2 контроля разности кодов, цифровой компаратор 3, элементы И 4 и 5, генератор 6 импульсов, реверсивный счетчик 7, первый аналого-цифровой блок 8, измерительньй Ьыпрямитель 9, второй аналого-цифровой блок 10, быстродействующий переключатель 11, нуль-орган 12, коммутаторы 13 - 15 кодов. На фиг. 1 изображены тг.кже последовательно соеди- ненные блок 16 формирования выходного напряжения и инверторный блок 17 преобразователя, сеть 18, нагрузка 19.

Выход кода подсоединен к первому входу блока 2,- имеющему два выхода - кодовый и управляющий, кодовый выход блока 2 контроля разности кодов подсоединен к первому входу цифрового компаратора 3, у которого выход приоритета числа на первом входе подсоединен к первому входу элемента 4, а выход приоритета числа на втором входе, ЯБЛЯЮ1ДИЙСЯ также выходом равенства, чисел на входах, - к nepBObiy входу элемента 5, к вторым входам элементов 4 и 5 подключен генератор 6, а выходы элементов 4 и 5 подключены

а

о со

СП

о

C3t

соответственно к суммирующему и вычитающему входам реверсивного счетчика 7, к второму входу 1ЩФРОВОГО компаратора 3 подсоединен выход второго коммутатора 14, первый кодовый вход которого подключен к выходу первого аналого-цифрового блока 8, вход которого подключен к выходу измерительно- ;го выпрямителя 9, подключенного к ; выходу быстродействующего переключа- теля 11, подключаемому к нагрузке 19, :вход второго аналого-цифрового бло- ка 10 подключается так же, как и первый вход быстродействуюп1его переключателя 11, к сети 18, а выход подключен к второму входу блока 2, второй силовой вход быстродействующего переключателя 11 подключается к выходу инверторного блока Т7, а его управ- : ляющий вход - к выходу третьего ком- : мутатора 15, кодовый вход которого : подключен к управляющему выходу бло- ка 1, к управляющему выходу блока 2 подсоединены управляющие входы коммутаторов 13 - 15, выход первого аналого-цифрового блока 8 подключен к входу нуль-органа 12, вькод которого подключен к обнуляющему входу блока 1 выход реверсивного счетчика 7 подключен к кодовому входу первого коммута- ; тора 13, выход которого подсоединяет- : ся к управляющим входам соответствуто- : щих ключевых элементов блока 16, второй кодовый вход второго коммутатора 14 подключен к выходу реверсивного счетчика 7.

Блок 2 (фиг. 2) содержит задатчик 20 допустимого отклонения кодов, блок 21 вычитания, цифровой компаратор 22 с выходом приоритета сигнала на первом входе и выходом приоритета сигнала на втором входе, который также является выходом равенства ЭТИ5 сигналов, RS-триггер 23, комму- татор 24 кодов. Выход задатчика 20 подключен к первому входу цифрового компаратора 22 блока 2, входы блока 21 являются кодовыми входами блока 2 выход блока 21, сигнал на котором соответствует модулю разности кодов на первом и втором входах, подсоединены к второму входу тщфрбвого компаратора 22 блока 2, выходы компа- . ратора 22 соединены следующим образом: выход приоритета сигнала на пер ром входе - с единичным входом триггера 23, выход приоритета сигнала на втором входе, являющийся также вы

0

5

0

5

0

35

40

45

50

55

ходом равенства сигналов, - с нулевым входом триггера 23, вькод триггера 23, являющийся управляющим выходом блока 2, - с управляюищм входом коммутатора 24, кодовые входы которого соединены с входами блока 21, а кодо- вьш выход является кодовым выходом блока 2.

Устройство для управления преобразователем работает следующим образом.

На выходе программного кода блока 1 формируется код X, соответствующий мгновенному значению ступенчато- аппроксимированной программной синусоиды. Код X поступает на один вход блока 2, на другой вход которого поступает код Z с выхода второго блока 10, соответствзтощий мгновенному напряжению сети 18. С кодового выхода блока 2 код X (или Z) поступает на первый вход 1ЩФРОВОГО компаратора 3, на другой вход которого поступает код Y, соответствующий мгновенному значению напряжения на выходе, быстродействующего переключателя 11, т.е. напряжению на нагрузке 19, или код q, являющийся выходным кодом реверсивного счетчика 7 и соответствующий коду Z на первом входе реверсивного счетчика 7. В цифровом компараторе 3 происходит сравнение этих кодов и вьфабатьшается команда (Z q) или X Y (Z q). Команда X Y (Z q) в виде разрешающего сигнала поступа- - ет на вход элемента 4 сравнения, а команда X : Y (Z q) - на вход элемента 5. В первом случае тактовые импульсы с выхода генератора 6 поступают на суммирующий вход реверсивного счетчика 7, значение кода на выходе которого возрастает до тех пор, пока значения сравниваемых кодов X и Y . (Z и q) не уравняются.Во втором случае происходит уменьшение кода Y (q) на выходе реверсивного счетчика 7 до тех пор пока -не сравняются X и Y ( Z и q) . Если качество напряжения сети удовлетворяет условиям допустимого отклонения мгновенного значения, имеет место режим отслеживания напряжения сети. При этом напряжение сети через быстродействующий переключатель 11 поступает на нагрузку 19, на вход блока 10 и через измерительный выпрямитель 9 - на вход блока 8. В блоке 10 напряжение сети преобразуется в код Z. В блоке 2 контроля разности кодов происходит постоянное сравнение кодов Z и X, при этом код Z отличается от программного кода X на величину не более заданной и на кодовьй выход блока 2 поступает код Z, ас управляющего выхода блока 2 управляющий сигнал поступает на управляющие входы быстродействующего переключателя 11, коммутаторов 13- 15 При этом на нагрузку 19 продолжает поступать напряжение сети 18 через быстродействующий переключатель 11, код q с выхода реверсивного счетчика 7 через второй коммутатор 14 поступает на второй вход цифрового компаратора 3 и, как показано выше, отслеживает значение кода Z. Первый коммутатор 13 и третий коммутатор 15 удерживают отключенными управляюп5ие входы силовых ключей блока 16 и инвер- |Торного блока 17 соответственно, т.е |на .эти входы поступают нулевые сиг- налы и все ключи блоков 16 и 17 находятся в отключенном состоянии, их цепи управления потребляют незначительную энергию.

Если же мгновенное значение напряжения сети отклонилось от програм ного на величину больше допустимой, разность кодов X и Z превысит установленное допустимое значение, в блоке 2 произойдет переключение шин и на кодовьй выход блока 2 начнет поступать код X, управляющий сигнал с управляюи {го выхода блока 2 переключит быстродействующий переключа- тель 11 и коммутаторы 13 - 15 кодовых шин.

При этом на управляющие входы ключей блока 16 через первый коммутатор 13 кодовых шин начнет поступат код q с выхода реверсивного счетчика 7, с выхода полярности полуволны выходного напряжения блока 1 уп- равляюш е сигналы начнут поступать на управляющий вход инверторного блока 17, на выходе преобразователя, включающего в себя,блоки 16 и 17, будет сформировано напряжение, мгновенное значение которого пропорционально коду q, быстродействующий переключатель 11 подключит нагрузку 19 к выходу инверторного блока 17, т.е. к преобразователю. При этом на вход первого блока 8 через измерительньв1 выпрямитель 9 начнет поступать выходное напряжение преобразователя.

второй коммутатор 14 подключит выход .блока 8 к второму входу цифрового компаратора 3, т.е. на пифровой компаратор 3 будут поступать коды X (программньй код) и Y (код, пропор- тщональньй мгновенному значению выходного напряжения преобразователя). Преобразователь в целом с устройством управления будет вырабатывать переменное напряжение, стабилизированное в соответствии с программным кодом X, до тех пор, пока не будет выполнено обратное переключение в режим отслеживания напряжения сети.

Нуль-орган 12 выполняет однократное обнуление блока. 1 при нулевом значении напряжения на нагрузке, что позволяет ликвидировать возможно е смещение фазы программного кода X относительно кода Z в режиме отслежи- - вания напряжения сети.

Блок 2 работает следзтощим образом. С вькода блока 1 код X поступает

на первый вход блока 20 (фиг. 2) и на дервый кодовьй вход коммутатора 24. С выхода блока 10 код Z поступает на второй вход блока 21 и на второй кодовьй вход коммутатора 21. В блоке

21 происходит постоянное вычисление модуля разности кодов X и Z, т.е. математическое действие А (Х - Z(. С выхода блока 21 код А поступает на один из входов цифрового компаратора

22, на второй вход которого подается код Q с задатчика 20. Б цифровом компараторе 18 происходит постоянное сравнение кода А |Х - Z |с кодом Q. Если в какой-то момент времени окажется , напряжение с. первого выхода компаратора 22 поступает на еди- ничньй вход триггера 23, триггер 23 переключается в единичное состояние, управляющий сигнал с его выхода в ви-

де напряжения поступает на вход коммутатора 24 и на быстродействующий переключатель 11. На выход тора 21 начинает проходить код X, поступающий с выхода блока 1 на первьй вход блока контроля раз ности кодов (на первьй вход блока 21 и первьй кодовьй вход коммутатора 24),

В том случае, когда , сигнал в виде напряжения с выхода цифрового компаратора 22 поступает на нулевой вход триггера 23, которьй переводится в нулевое состояние (или остается в нем). При этом управляющее напря- х;ение на коммутатор 24 и на управляю

щнй выход блока контроля разности ко- дов не поступает, на вход коммутатора 24 проходит код Z, поступающий с выхода второго блока 10 на второй кодовый вход блока контроля разно сти кодов ( на вторые входы блока 21 вычитания и коммутатора 24).

Устройство для управления преобразователем обеспечивает два режима работы преобразователя: режим отслеживания напряжения сети и режим рабо- ты;преобразователя на нагрузку. Первый из указанных режимов для преобразователя в установке гарантирован- ;Но|го питания является режимом поСтоян not o функцирнирования и по длительности многократно превьшает второй . В первом режиме нагрузка пи- от сети, а вся энергия, потреб ляёмая преобразователем, является энергией потерь. Снижение энергий, . потребляемой преобразователем, позволяет повысить общий КПД устаж вки гарантированного питания. Энергия, по- тр|вбляемая преобразователем в р.ежиме отслеживания, разходуется на работу ус|гройства управления if на потери в цепях управления силовами транзисторами.

Формула изобретения

Устройство для управления преобра- зо|вателем источника гарантированно- ..rcj питания, включающего быстродейст- переключатель, выход которого является выходом преобразователя, блок-формирования выходного напряжения, подключенный через инверторный блок к первому входу быстродействую- щёго переключателя, второй вход которого соединен с сетью, содержащее блок формирования кода синусоидального сигнала с выходом кода и выходом полярности полуволны, измерительный . вьшрямитель, первый аналого-дафровой блок, входом подключенньй к выходу измерительного вьшрямителя, цифровой компаратор с выходом приоритета числ на первом входе и выходом приоритета числа на втором входе, два элемента первые входы,.которых соединены с выходами цифрового компаратЬра, вторые входы подключены к выходу генератора импульсов, реверсивный счетчик, сум- мирующий вход которого соединен с вы : содом первого элемента И, вычитающий вход - с выходом второго элемента И, нуль-орган, вход которого подключен

к выходу первого аналого-цифрового блока, выход - к обнуляющему входу блока формирования кода синусоидального сигнала, второй аналого-цифровой блок, вход которого предназначен для подключения к сети, блок контроля разности кодов, имеющий два кодовых входа-, кодовый выход, управляющий выход и включакщий и себя задатчик допустимого отклонения кодов, блок вычитания, цифровой компаратор с выходом приоритета сигнала на первом входе и выходом приоритета сигнала на втором входе, который также использован как выход равенства этих сигналов RS-триггер, коммутатор, выход задат- чика допустимого отклонения подключен к первому входу цифрового компаратора блока контроля разности кодов, входы блока вычитания использованы как кодовые входы блока контроля раз- 1НОСТИ кодов, выход блока вычитания подключен к гторому входу цифрового компаратора блока контроля разности

.кодов, выход приоритета сигнала на t -

первом входе компаратора соединен с

S-входом RS-триггера, выход приоритета сигнала на втором.входе - с R-BXO- дом RS-триггера, выход RS-триггера является управляюп1им выходом блока контроля разности кодов и соединен с управляющим входом коммутатора, кодовые входы которого соединены с входами блока вычитания, кодовьй выход является кодовым выходом блока контроля разности кодов, первый кодовый вход блока кон -роля разности кодов подключен к выходу кода блока форми- ровани,. кода синусоидального сигнала, второй кодовый вход подключен к выходу второго аналого-цифрового блока, кодовьй выход - к первому входу цифрового компаратора, а управляющий выход предназначен для подключения к управлякицему входу быстродействующего переключателя, отличающееся тем, что, с целью повьше- ния КПД преобразователя, в устройство управления введены три коммутатора кодов, причем управляющее входы всех коммутаторов соединены с управляющим выходом блока контроля разности кодов, выход первого коммутатора кодов предназначен для соединения с управляющим входом блока формирова- .ния выходного напряжения, выход второго коммутатор а кодов подключен к второму входу цифрового компаратора

выход третьего коммутатора кодов предназначен для подключения к управляющему входу ин верторного блока, кодовый вход первого коммутатора и первый кодовый вход второго коммутатора подключены к выходу реверсивного счетчИка, второй кодовый вход второго коммутатора подключен к выходу

первого аналого-цифрового блока, ко- довьп вход третьего коммутатора подключен к выходу полярности полуволны блока формирования кода синусоидального сигнала, вход измерительного выпрямителя предназначен для подключения к выходу быстродействующего переключателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления преобразователем | 1985 |

|

SU1246300A1 |

| Устройство для автоматической проверки аналого-цифровых преобразователей | 1978 |

|

SU782144A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Устройство для управления преобразователем постоянного напряжения в многоступенчатое квазисинусоидальное | 1983 |

|

SU1319206A1 |

| Устройство для централизованного контроля параметров | 1988 |

|

SU1603400A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Логарифмический аналого-цифровойпРЕОбРАзОВАТЕль | 1979 |

|

SU840947A1 |

| УСТРОЙСТВО СЛЕДЯЩЕГО ТИПА ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ВТОРОЙ ОРТОГОНАЛЬНОЙ СОСТАВЛЯЮЩЕЙ ВЕКТОРА | 2000 |

|

RU2187839C2 |

| Устройство для измерения и контроля параметров аналого-цифровых преобразователей | 1981 |

|

SU1005297A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1319279A1 |

Изобретение относится к электротехнике и может быть использовано для управления преобразователями постоянного напряжения в переменное с квазисинусоидальной или ступенчато-синусоидальной формой выходного напряжения. Цель изобретения - повышение КПД преобразователя. Для этого устройство снабжено тремя коммутаторами. При этом в режиме отслеживания напряжения питающей сети силовые ключи преобразователя выключены, напряжение сети преобразуется в цифровой код и все операции режима отслеживания сводятся к обработке цифровых кодов в устройстве управления, а силовые ключи преобразователя включаются лишь при переходе нагрузки на питание от преобразователя. 2 ил.

ФЬг2

Составитель В, Миронов Редактор А. Маковская Техред М.Дидык Корректор М. Максимипинец

Заказ 3392

Тираж 498

ВНИИПИ Государственног(з комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Устройство для управления преобразователем | 1985 |

|

SU1246300A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1990-10-30—Публикация

1987-07-08—Подача