113

Изобретение относится к преобразовательной технике и может быть использовано в системах автономного электроснабжения.

Целью изобретения является повышение, точности стабилизации выходного напряжения при сохранении массогаба- ритных показателей и гармонического состава выходного напряжения.

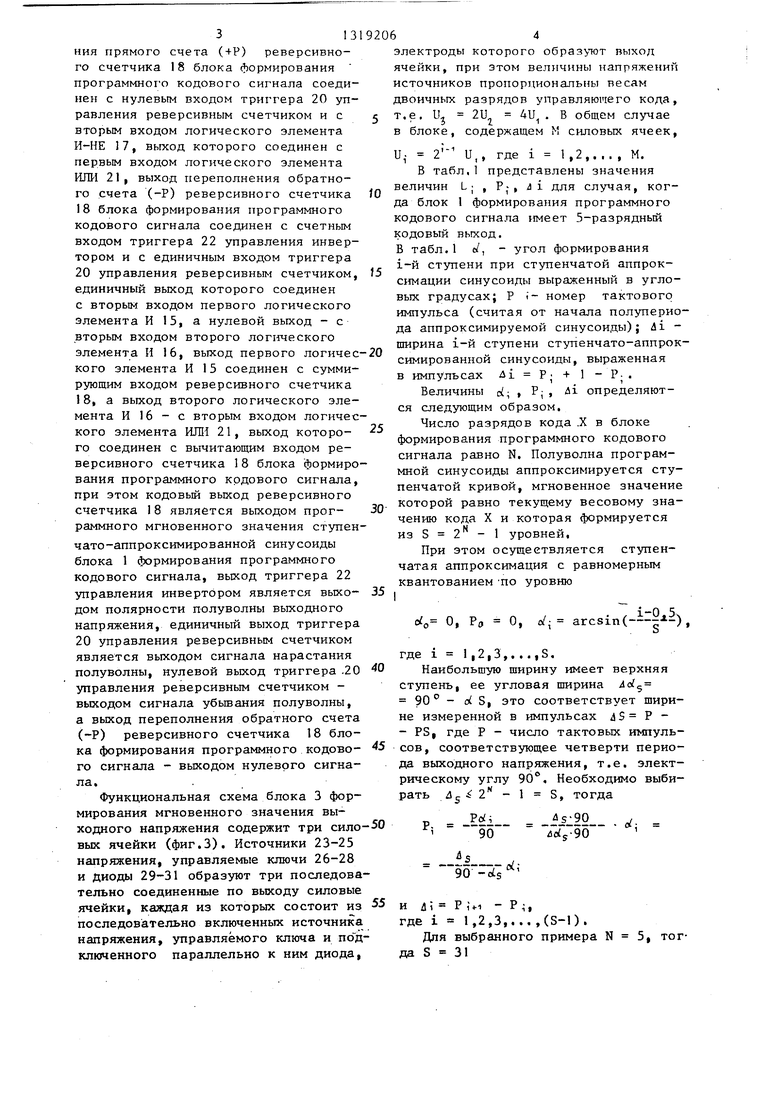

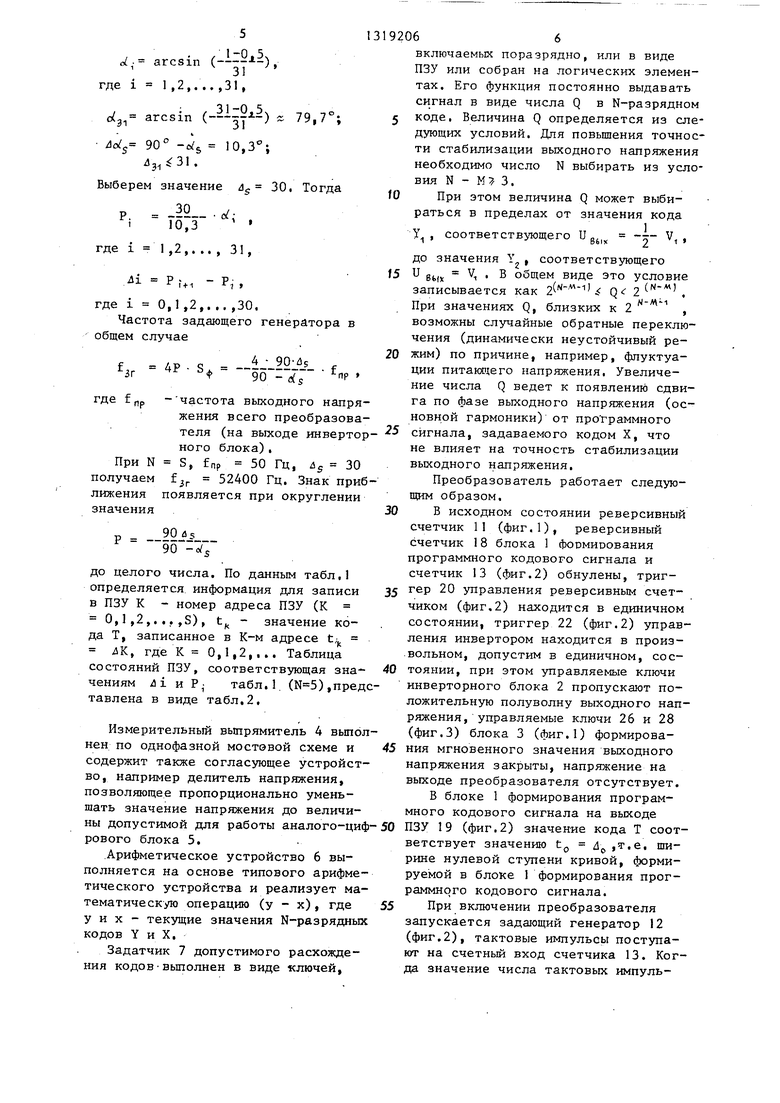

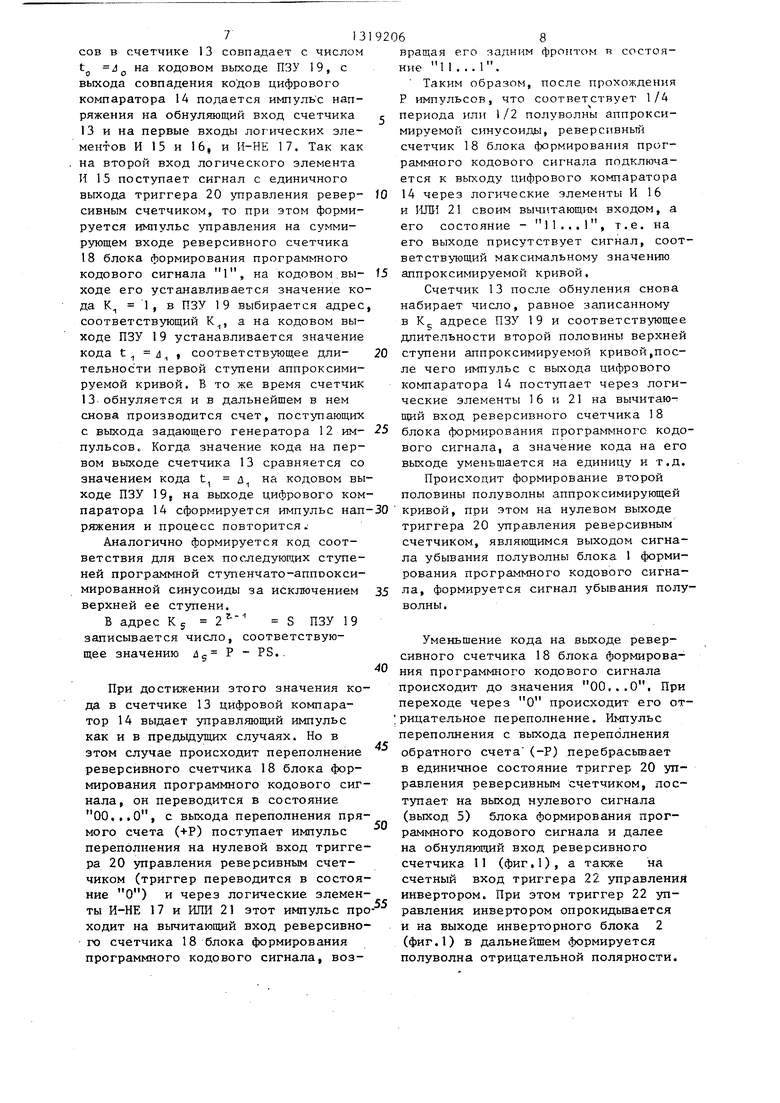

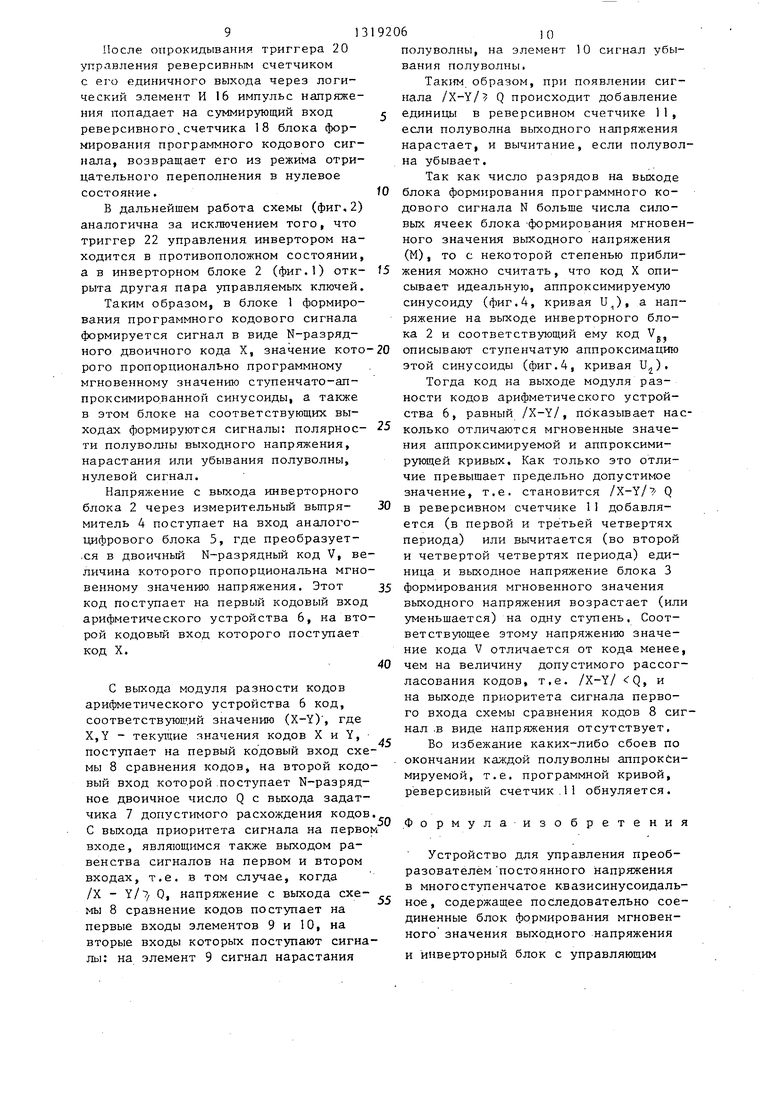

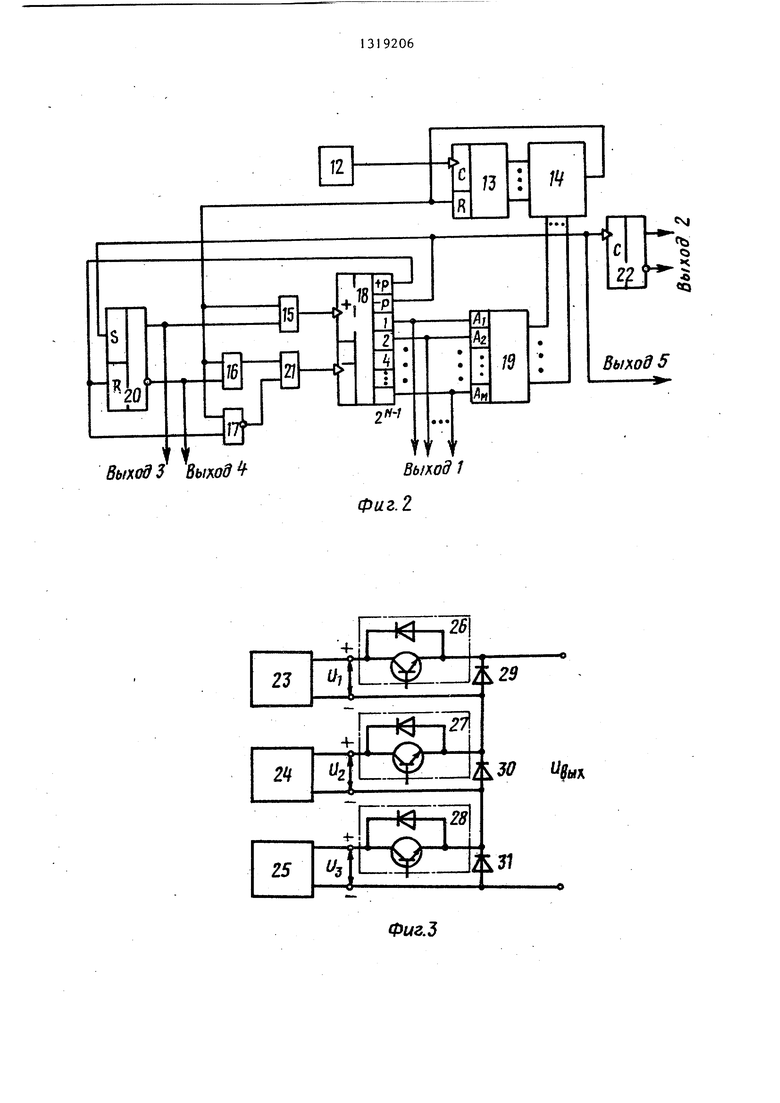

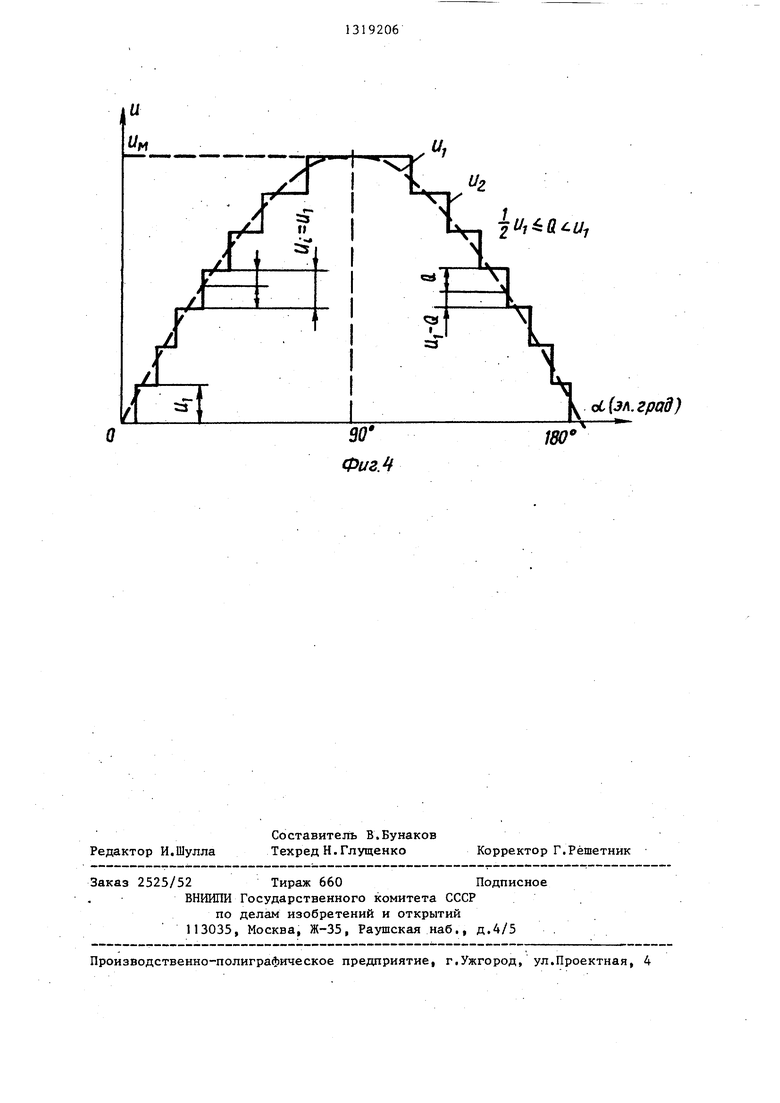

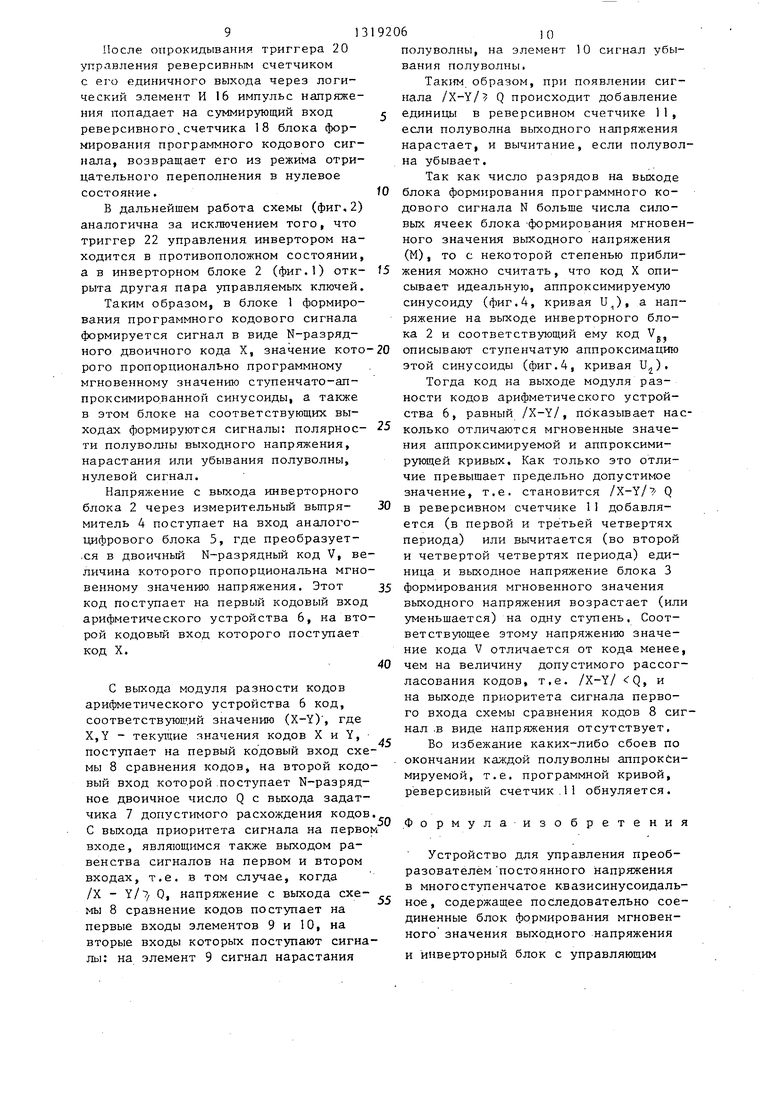

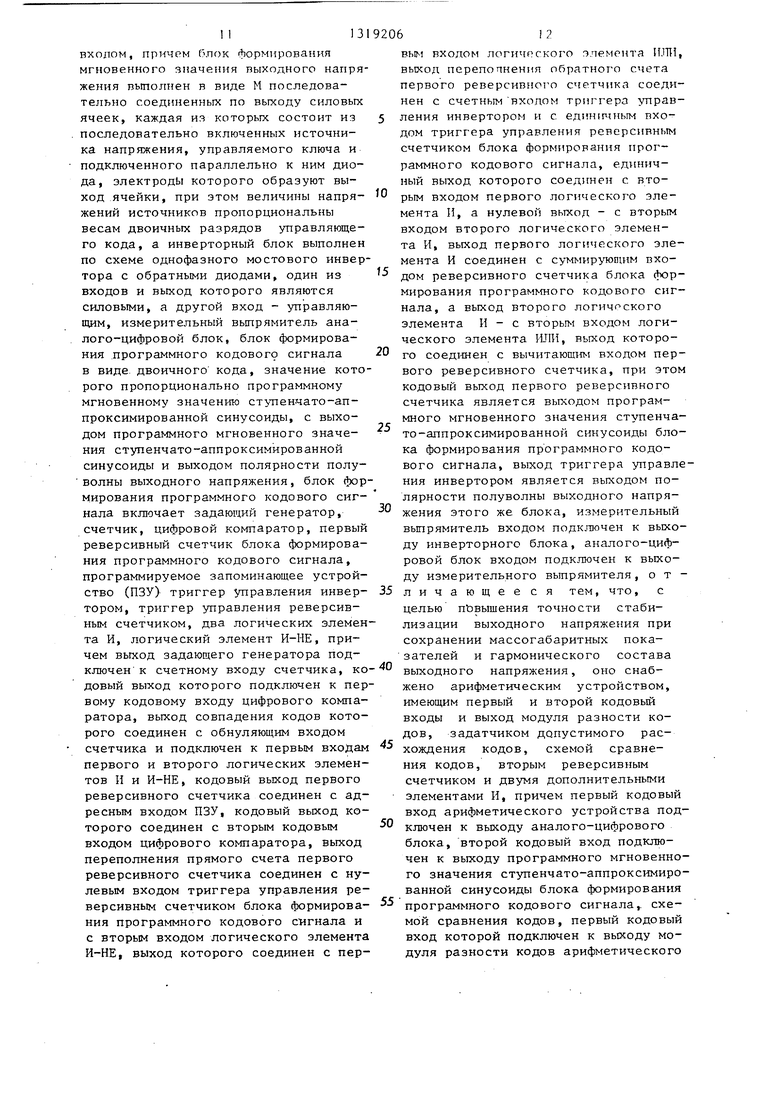

На фиг.1 приведена функциональная схема устройства для управления преобразователем постоянного напряжения в многоступенчатое квазисинусоидальное; на. фиг, 2 - функциональная схема блока формирования программного кодового сигнала; на фиг. 3 - функциональная схема блока формирования мгновенного значения выходного напряжения; на фиг. 4 - диаграммка выходного напряжения.

Предлагаемое устройство (фиг.1) содержит блок 1 формирования программного кодового сигнала в виде двоичного кода, значение которого пропорционально программному мгновенному значению ступенчато-аппроксимированной синусоиды, инвертарный блок 2, блок 3 формирования мгновенного значения выходного напряжения, измерительный выпрямитель 4, аналого-цифровой блок 5, арифметическое устройство 6, задатчик 7 допустимого расхождения кодов, схему 8 сравнения кодов, элементы И 9 и 10, реверсивный счетчик 11.

Выход полярности полуволны выходного напряжение блока 1 формирования мгновенного значения программного кодового сигнала соединен с управляющим входом инверторного блока 2, выполненного по схеме однофазного мостового инвертора с обратными диодами, силовой выход которого является выходом всего преобразователя, а силовой вход подсоединен .к выходу блока 3 формирования мгновенного значения выходного напряжения, выполненного в виде М последовательно соединенных по выходу силовых ячеек, каждая из которых состоит из последовательно включенных источника напряжения, управляемого ключа и подключенного параллельно к ним диода, электроды которого образуют выход ячейки, при этом величины напряжений источников пропорциональны весам.двоичных разрядов управляющего кода, к выходу инверторного блока 2 подсоединен вход измерительного выпрямителя 4,

62

выходом подключенный по выходу аналого-цифрового блока 5, выход которого подключен к первому кодовому входу арифметического устройства 6,

второй кодовый вход которого подключен к выходу программного мгновенного значения ступенчато-аппроксимированной синусоиды блока 1 формирования программного кодового сигнала,

выход задатчика 7 допустимого расхож- дения кодов подключен к второму кодовому входу схемы 8 сравнения кодов, к первому кодовому входу которой подключен выход модуля разности (т.е.

абсолютной величины разности) кодов арифметического устройства 6, выход приоритета сигнала на первом входе схемы 8 сравнения, являющейся также выходом равенства сигналов на первом

и втором входах, соединен с первыми входами дв5 входовых элементов И 9 и 10, суммирующий вход реверсивного счетчика 11 соединен с выходом элемента И 9, вычитающий вх од реверсивного счетчика 11 соединен с выходом элемента И 10, вход обнуления реверсивного счетчика 11 соединен с выходом нулевого сигнала блока 1 формирования программного кодового сигнала, имеющего также выход сигнала нарастания полуволны, соединенный с вторым входом элемента И 9 и выход сигнала убывания полуволны,соединенный с вторым входом элемента

И 10, М-разрядный кодовый выход реверсивного счетчика 11 поразрядно соединен с М управляющими входами силовых ячеек блока 3 формирования мгновенного значения вькодного нап- .

ряжения.

Блок формирования программного кодового сигнала (фиг.2) содержит задающий генератор 12, выходом подключенный к счетному входу счетчика 13, кодовый выход которого подключен к первому кодовому входу цифрового компаратора 14, выход совпадения кодов которого соединен с обнуляющим входом счетчика I3 и подключен к первым входам первого логического элемента И 15, второго логического элемента И 16, логического элемента И-НЕ 17, первый реверсивный счетчик 18, кодовой выход которого

соединен с адресным входом программируемого запоминающего устройства (ПЗУ) 19, кодовый выход которого соединен с вторым кодовым входом цифрового компаратора, выход переполне313

ния прямого счета (+Р) реверсивного счетчика 18 блока формирования программног о кодового сигнала соединен с нулевым входом триггера 20 управления реверсивным счетчиком и с вторым входом логического элемента И-НЕ 17, выход которого соединен с первым входом логического элемента ИЛИ 21, выход переполнения обратного счета (-Р) реверсивного счетчика 18 блока формирования программного кодового сигнала соединен с счетньм входом триггера 22 управления инвертором и с единичным входом триггера 20 управления реверсивным счетчиком, единичный выход которого соединен с вторым входом первого логического элемента И 15, а нулевой выход - с вторым входом второго логического элемента И 16, выход первого логичес кого элемента И 15 соединен с суммирующим входом реверсивного счетчика 18, а выход второго логического элемента И 16 - с вторым входом логического элемента HJli 21, выход которого соединен с вычитающим входом реверсивного счетчика 18 блока формирования программного кодового сигнала, при этом кодовый выход реверсивного счетчика 18 является выходом программного мгновенного значения ступенчато-аппроксимированной синусоиды блока 1 формирования программного кодового сигнала, выход триггера 22 управления инвертором является выходом полярности полуволны выходного напряжения, единичный выход триггера 20 управления реверсивным счетчиком является выходом сигнала нарастания полуволны, нулевой выход триггера .20 управления реверсивным счетчиком - выходом сигнала убьшания полуволны, а выход переполнения обратного счета (-Р) реверсивного счетчика 18 блока формирования программного кодового сигнала - выходом нулевого сигнала.

Функциональная схема блока 3 формирования мгновенного значения выходного напряжения содержит три сило вых ячейки (фиг.З). Источники 23-25 напряжения, управляемые ключи 26-28 и диоды 29-31 образуют три последова тельно соединенные по выходу силовые ячейки, каждая из которых состоит из последовательно включенных источника напряжения, управляемого ключа и по д ключенного параллельно к ним диода,

92064

электроды которого образуют выход ячейки, при этом величины напряжений источников пропорциональны весам двоичных разрядов управляюшего кода, 5 т.е. Uj 2U 4U . В общем случае в блоке, содержащем М силовых ячеек,

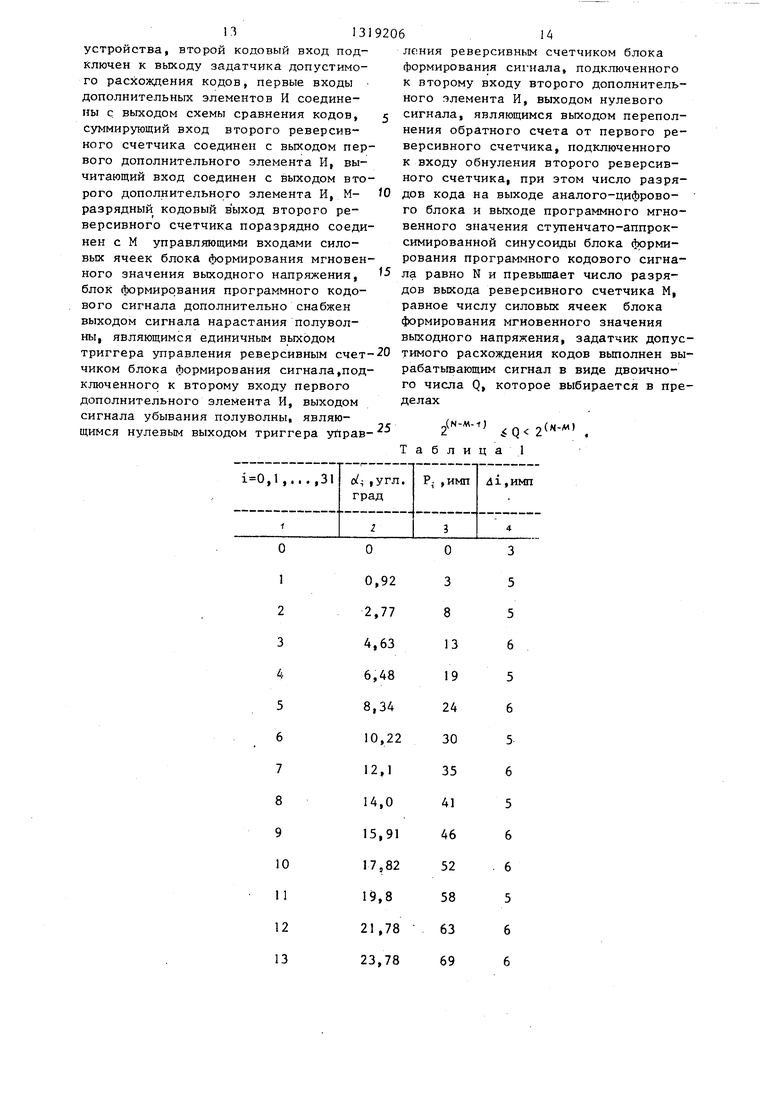

и- 2- и,, где i 1,2,... , М. В табл.1 представлены значения

. величин L; , PJ , Ai для случая, когда блок 1 формирования программного кодового сигнала имеет 5-разрядный кодовый выход.

В табл. 1 е/, - угол формирования i-й ступени при ступенчатой аппроксимации синусоиды выраженный в угловых градусах; Р ;- номер тактового импульса (считая от начала полупериода аппроксимируемой синусоиды); di - ширина i-й ступени ступенчато-аппроксимированной синусоиды, выраженная в импульсах л Р + 1 - Р-.

Величины ci. , Р; , л1 определяются следующим образом.

ус Число разрядов кода .X в блоке формирования программного кодового сигнала равно N. Полуволна программной синусоиды аппроксимируется ступенчатой кривой, мгновенное значение

эд. которой равно текущему весовому значению кода X и которая формируется

IJ

из S 2 - 1 уровней,

При этом осуществляется ступенчатая аппроксимация с равномерным квантованием По уровню

20

35

I

ofo О, Р„ 0, ci- arcsin().

где i 1,2,3,...,S.

Наибольшую ширину имеет верхняя ступень, ее угловая ширина Aci 90 ° - oi S| это соответствует ширине измеренной в импульсах 45 Р - - PS. сов,

, где Р - число тактовых импуль- , соответствующее четверти периода выходного напряжения, т.е. электрическому углу 90°. Необходимо выби50

55 и л; Р

- Р

где i 1,2,3,...,(S-1).

Для выбранного примера N 5, тогда S 31

/1-0±5. с. arcsin (),

где i 1,2,...,31,

/ / ,5ч -jr, -,0 arcsin (зУ ) 79,7 ;

90° -«fj 10, .

Выберем значение dg 20, Тогда

где i 1 ,231,

.Л1 Р;, - ,

где i 0,1,2,...,30.

Частота задающего генератора общем случае

зг 4F-S

4 - 90 i3 s 90 -Ts

-np

- частота выходного напряжения всего преобразователя (на выходе инвертор- ного блока),

S, fnp 50 Гц, ug 20 f |. 52400 Гц. Знак прибпоявляется при округлении

Р

90 й5

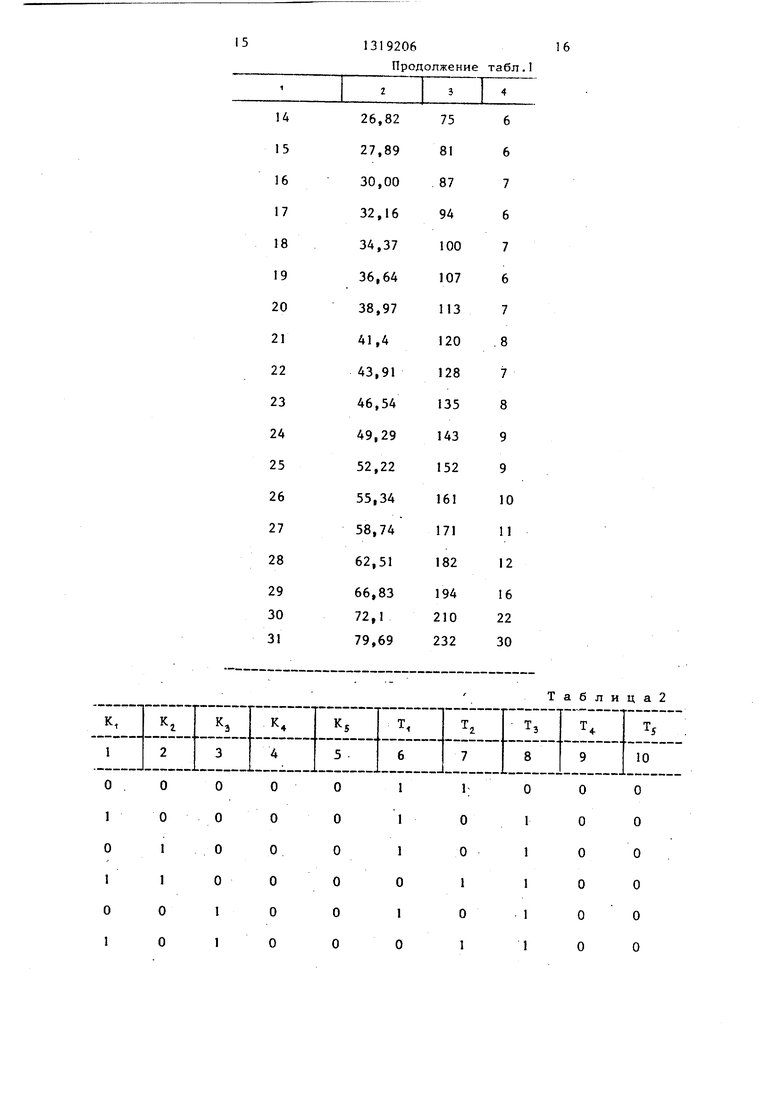

до целого числа. По данным табл,1 определяется информация для записи в ПЗУ К - номер адреса ПЗУ (К О,1,2,.,.,5), t - значение кода Т, записанное в К-м адресе t; 4К, где К 0,1,2,... Таблица состояний ПЗУ, соответствующая чениям Ai и Р,- табл.1. (),предтавлена в виде табл.2.

Измерительный выпрямитель 4 вьшол нен по однофазной мостэвой схеме и содержит также согласующее устройство, например делитель напряжения, позволяющее пропорционально уменьшать значение напряжения до величины допустимой для работы аналого-цифрового блока 5.

.Арифметическое устройство 6 выполняется на основе типового арифметического устройства и реализует математическую операцию (у - х), где у и X - текущие значения N-разрядных кодов Y и X.

Задатчик 7 допустимого расхождения кодов-выполнен в виде ключей.

-

-сл-фх

92066

включаемых поразрядно, или в виде ПЗУ или собран на логических элементах. Его функция постоянно выдавать сигнал в виде числа Q в N-разрядном

5 коде, Величина Q определяется из следующих условий. Для повышения точности стабилизации выходного напряжения необходимо число N выбирать из условия N - М 3.

fO При зтом величина Q может выбираться в пределах от значения кода

У. , соответствующего U -т- V,,

до значения Y , соответствующего

f5 и V, . В общем виде это условие записывается как 2(. Q . При значениях Q, близких к 2 , возможны случайные обратные переключения (динамически неустойчивый ре20 жим) по причине, например, флуктуации питаюодего напряжения, Увеличение числа Q ведет к появлению сдвига по фазе выходного напряжения (основной гармоники) от про граммного

25 сигнала, задаваемого кодом X, что не влияет на точность стабилизации выходного напряжения.

Преобразователь работает следующим образом.

30 В исходном состоянии реверсивный счетчик II (фиг,1), реверсивный счетчик 18 блока 1 формирования программного кодового сигнала и счетчик 13 (фиг.2) обнулены, триг35 гер 20 управления реверсивным счетчиком (фиг.2) находится в единичном состоянии, триггер 22 (фиг.2) управления инвертором находится в произ- .вольном, допустим в единичном, сос40 тоянии, при этом управляемые ключи инверторного блока 2 пропускают положительную полуволну выходного напряжения, управляемые ключи 26 и 28 (фиг,3) блока 3 (фиг.1) формирова45 ния мгновенного значения выходного напряжения закрыты, напряжение на выходе преобразователя отсутствует. В блоке 1 формирования программного кодового сигнала на выходе

50 ПЗУ 19 (фиг,2) значение кода Т соответствует значению t л ,т.е. ширине нулевой ступени кривой, формируемой в блоке I формирования программного кодового сигнала.

55 При включении преобразователя запускается задающий генератор 12 (фиг.2), тактовые импульсы поступают на счетный вход счетчика 13. Когда значение числа тактовых импуль713

сов в счетчике 13 совпадает с числом t jp на кодовом выходе ПЗУ 19, с выхода совпадения кодов цифрового компаратора 14 подается импуль с напряжения на обнуляющий вход счетчика 13 и на первые входы логических элементов И 15 и 16, и Н-НЕ 17. Так как на второй вход логического элемента И 15 поступает сигнал с единичного выхода триггера 20 управления реверсивным счетчиком, то при этом формируется импульс управления на суммирующем входе реверсивного счетчика 18 блока формирования nporpaMhffloro кодового сигнала 1, на кодовом выходе его устанавливается значение кода К 1 , в ПЗУ 19 выбирается адрес соответствующий К, а на кодовом выходе ПЗУ 19 устанавливается значение кода t 4 f соответствующее длительности первой ступени аппроксимируемой кривой, В то же время счетчик 13. обнуляется и в дальнейшем в нем снова производится счет, поступающих с выхода задающего генератора 12 импульсов. Когда значение кода на первом выходе счетчика 13 сравняется со значением кода t , кодовом выходе ПЗУ 19, на выходе цифрового компаратора 14 сформируется импульс напряжения и процесс повторится

Аналогично формируется код соответствия для всех последующих ступеней программной ступенчато-аппоокси- мированной синусоиды за исключением верхней ее ступени.

В адрес К 5 S ПЗУ 19 записывается число, соответствующее значению й Р - PS..

При достижении этого значения кода в счетчике 13 цифровой компаратор 14 выдает управляющий импульс как и в предыдущих случаях. Но в этом случае происходит переполнение реверсивного счетчика 18 блока формирования программного кодового сигнала, он переводится в состояние 00,,,О, с выхода переполнения прямого счета (+Р) поступает импульс переполнения на нулевой вход триггера 20 управления реверсивным счетчиком (триггер переводится в состояние О) и через логические элементы И-НЕ 17 и ИЛИ 21 этот импульс про ходит на вычитающий вход реверсивного счетчика 18 блока формирования программного кодового сигнала, воз68

вращая его задним фронтом в состояние 11....

Таким образом, после прохождения Р импульсов, что соответствует 1/4 периода или 1/2 полуволны аппроксимируемой синусоиды, реверсивньш счетчик 18 блока формирования программного кодового сигнала подключается к выходу цифрового компаратора

14 через логические элементы И 16 и ИЛИ 21 своим вычитающим входом, а его состояние - 11,..1, т.е. на его выходе присутствует сигнал, соответствующий максимальному значению

аппроксимируемой кривой.

Счетчик 13 после обнуления снова набирает число, равное записанному в К адресе ПЗУ 19 и соответствующее длительности второй половины верхней

ступени аппроксимируемой кривой,после чего импульс с выхода цифрового компаратора 14 поступает через логические элементы 16 и 21 на вычитаю щий вход реверсивного счетчика 18

блока формирования програм ного кодового сигнала, а значение кода на его выходе уменьшается на единицу и т.д.

Происходит формирование второй половины полуволны аппроксимирующей

кривой, при этом на нулевом выходе триггера 20 управления реверсивным счетчиком, являющимся выходом сигнала убывания полуволны блока 1 формирования программного кодового сигнала, формируется сигнал убывания полуволны.

0

5

0

5

Уменьшение кода на выходе реверсивного счетчика 18 блока формирования программного кодового сигнала происходит до значения 00...О, При переходе через О происходит его от- ;рицательное переполнение. Импульс переполнения с выхода переполнения обратного счета(-Р) перебрасывает в единичное состояние триггер 20 управления реверсивным счетчиком, поступает на выход нулевого сигнала (выход 5) блока формирования программного кодового сигнала и далее на обнуляющий вход реверсивного счетчика 11 (фиг,1), а также на счетный вход триггера 22 управления инвертором. При этом триггер 22 управления инвертором опрокидьшается и на выходе инверторного блока 2 (фиг,1) в дальнейшем формируется полуволна отрицательной полярности.

После опрокидывания триггера 20 управления реверсивным счетчиком с его единичного выхода через логический элемент И 16 импульс напряжения попадает на суммирующий вход реверсивного.счетчика 18 блока формирования программного кодового сигнала, возвращает его из режима отрицательного переполнения в нулевое состояние.

В дальнейшем работа схемы (фиг.2) аналогична за исключением того, что триггер 22 управления инвертором находится в противоположном состоянии, а в инверторном блоке 2 (фиг.1) открыта другая пара управляемых ключей.

Таким образом, в блоке 1 формирования программного кодового сигнала формируется сигнал в виде N-разряд- ного двоичного кода X, значение кото рого пропорционально программному мгновенному значению ступенчато-аппроксимированной синусоиды, а также в этом блоке на соответствующих выходах формируются сигналы: полярности полуволны выходного напряжения, нарастания или убывания полуволны, нулевой сигнал.

Напряжение с выхода инверторного блока 2 через измерительньй выпрямитель 4 поступает на вход аналого- цифрового блока 5, где преобразует- iCH в двоичный N-разрядньй код V, величина которого пропорциональна мгновенному значению напряжения. Этот код поступает на первый кодовый вход арифметического устройства 6, на второй кодовый вход которого поступает код X.

С выхода модуля разности кодов арифметического устройства 6 код, соответствуюЕ ий значению (X-Y), где X,Y - текущие значения кодов X и Y, поступает на первый кодовый вход схемы 8 сравнения кодов, на второй кодовый вход которой .поступает N-разрядное двоичное число Q с выхода задат- чика 7 ДОПУСТ1ГМОГО расхождения кодов. С выхода приоритета сигнала на первом входе, являющимся также выходом равенства сигналов на первом и втором входах, т.е. в том случае, когда /X - Y/7/ О, напряжение с выхода схемы 8 сравнение кодов поступает на первые входы элементов 9 и 10, на вторые входы которых поступают сигналы: на элемент 9 сигнал нарастания

1319206

10

O

5

0

5

5

полуволны, на элемент 10 сигнал убывания полуволны,

Таким образом, при появлении сигнала /X-Y/ Q происходит добавление единицы в реверсивном счетчике 11, если полуволна выходного напряжения нарастает, и вычитание, если полуволна убывает.

Так как число разрядов на выходе блока формирования программного кодового сигнала N больше числа сило- вьк ячеек блока -формирования мгновенного значения выходного напряжения (М), то с некоторой степенью приближения можно считать, что код X описывает идеальную, аппроксимируемую синусоиду (фиг.4, кривая U), а напряжение на выходе инверторного блока 2 и соответствующий ему код V.,

р

описывают ступенчатую аппроксимацию этой синусоиды (фиг.4, кривая U,j).

Тогда код на выходе модуля разности кодов арифметического устройства 6, равный /X-Y/, показывает насколько отличаются мгновенные значения аппроксимируемой и аппроксимирующей кривых. Как только это отличие превышает предельно допустимое значение, т.е. становится /X-Y/ - Q в реверсивном счетчике 1I добавляется (в первой и третьей четвертях периода) или вычитается (во второй и четвертой четвертях периода) единица и выходное напряжение блока 3 формирования мгновенного значения выходного напряжения возрастает (или уменьшается) на одну ступень. Соответствующее этому напряжению значение кода V отличается от кода менее, чем на величину допустимого рассогласования кодов, т.е. /X-Y/ Q, и на выходе приоритета сигнала первого входа схемы сравнения кодов 8 сигнал .в виде напряжения отсутствует.

Во избежание каких-либо сбоев по окончании каждой полуволны аппроксимируемой, т.е. программной кривой, реверсивный счетчик. 11 обнуляется.

0

0

5

Формулаизобретения

Устройство для управления преобразователем постоянного напряжения в многоступенчатое квазисинусоидаль- ное, содержащее последовательно соединенные блок формирования мгновенного значения выходного напряжения

и йнверторный блок с управляющим

1 113

входом, причем б.пгж формирования мгновенного значения выходного напряжения выполнен в виде М последовательно соединенных по выходу силовых ячеек, каждая из которых состоит из последовательно включенных источника напряжения, управляемого ключа и подключенного параллельно к ним диода, электроды которого образуют выход ячейки, при этом величины напряжений источников пропорциональны весам двоичных разрядов управляющего кода, а инверторный блок выполнен по схеме однофазного мостового инвертора с обратными диодами, один из входов и выход которого являются силовыми, а другой вход - управляющим, измерительный выпрямитель аналого-цифровой блок, блок формирования программного кодового сигнала в виде двоичного кода, значение которого пропорционально программному мгновенному значению ступенчато-аппроксимированной синусоиды, с выходом программного мгновенного значения ступенчато-аппроксимированной синусоиды и выходом полярности полуволны выходного напряжения, блок формирования программного кодового сигнала включает задающий генератор, счетчик, цифровой компаратор, первый реверсивный счетчик блока формирования программного кодового сигнала, программируемое запоминающее устройство (ПЗУ) триггер управления инвертором, триггер управления реверсивным счетчиком, два логических элемента И, логический элемент И-НЕ, причем выход задающего генератора подключен к счетному входу счетчика, кодовый выход которого подключен к первому кодовому входу цифрового компаратора, выход совпадения кодов которого соединен с обнуляющим входом счетчика и подключен к первым входам первого и второго логических элементов И и И-НЕ, кодовый выход первого реверсивного счетчика соединен с адресным входом ПЗУ, кодовый выход которого соединен с вторым кодовым входом цифрового компаратора, выход переполнения прямого счета первого реверсивного счетчика соединен с нулевым входом триггера управления реверсивным счетчиком блока формирования программного кодового сигнала и с вторым входом логического элемента И-НЕ, выход которого соединен с пер0

0

5

вым входом логического элемента И.Ш1, выход перепопнения обратного счета первого реверсивного счетчика соединен с счетным входом триггера управления инвертором и с един1гчньгм входом триггера управления реверсивным счетчиком блока формирования программного кодового сигнала, единичный выход которого соединен с вторым входом первого логического элемента И, а нулевой выход - с вторым входом второго логического элемента И, выход первого логического элемента И соединен с суммирующим вхо- дом реверсивного счетчика блока формирования программного кодового сигнала, а выход второго логического элемента И - с вторым входом логического элемента ИЛИ, вькод которого соединен с вычитающ1-п- входом первого реверсивного счетчика, при этом кодовый выход первого реверсивного счетчика является выходом программного мгновенного значения ступенчато-аппроксимированной синусоиды блока формирования пр ограммного кодового сигнала, выход триггера управления инвертором является выходом полярности полуволны выходного напряжения этого же блока, измерительный вьшрямитель входом подк.шочен к выходу инверторного блока, аналого-цифровой блок входом подключен к выходу измерительного выпрямителя, о т 5 личающее ся тем, что, с целью пЪвышения точности стабилизации выходного напряжения при сохранении массогабаритных показателей и гармонического состава выходного напряжения, оно снабжено арифметическим устройством, имеющим первый и второй кодовый входы и выход модуля разности кодов, задатчиком допустимого расхождения кодов, схемой сравнения кодов, вторым реверсивным счетчиком и двумя дополнительными элементами И, причем первый кодовый вход арифметического устройства под ключей к выходу аналого-цифрового блока, второй кодовый вход подключен к выходу программного мгновенного значения cтyпeнчaтo-aппpoкcIiмиpo- ванной синусоиды блока формирования программного кодового сигнала,, схемой сравнения кодов, первый кодовый вход которой подключен к выходу модуля разности кодов арифметического

0

0

5

5

13131

устройства, второй кодовый вход подключен к выходу задатчика допустимого расхождения кодов, первые входы дополнительных элементов И соединены с. выходом схемы сравнения кодов, суммирующий вход второго реверсивного счетчика соединен с выходом первого дополнительного элемента И, вычитающий вход соединен с выходом второго дополнительного элемента И, М- разрядный кодовый в ыход второго реверсивного счетчика поразрядно соединен с М управляющими входами силовых ячеек блока формирования мгновенного значения выходного напряжения, блок формирования программного кодового сигнала дополнительно снабжен выходом сигнала нарастания полуволны, являющимся единичным выходом

триггера управления реверсивным счет чиком блока формирования сигнала,под ключенного к второму входу первого дополнительного элемента И, выходом сигнала убывания полуволны, являющимся нулевым выходом триггера управ

О

1

2

3

4

5

6

7

8

9

10

11

12

13

20614

ления реверсивным счетчиком блока формирования сигнала, подключенного к второму входу второго дополнительного элемента И, выходом нулевого г сигнала, являющимся выходом переполнения обратного счета от первого реверсивного счетчика, подключенного к входу обнуления второго реверсивного счетчика, при этом число разря- JO дов кода на выходе аналого-цифрового блока и выходе программного мгновенного значения ступенчато-аппроксимированной синусоиды блока формирования программного кодового сигна- 15 ла равно N и превьшает число разрядов выхода реверсивного счетчика М, равное числу силовых ячеек блока формирования мгновенного значения выходного напряжения, задатчик допус- 20 тимого расхождения кодов выполнен вы- рабатьгоающим сигнал в виде двоичного числа Q, которое выбирается в пределах

25

.( Таблица

О

3

8

13

19

24

30

35

41

46

52

58

63

69

3 5 5 6 5 6 5 6 5 6

. 6 5 6 6

1

1

о о

ч

1 1

о о 1 1

о о 1 1

о о 1 1 о

о 1 1

о о 1 1

I

1

о о о о 1 1 1 1

о о о о 1 1 1 1 о

о о о 1 1 1 I

о о 1 I 1 1 1 1 1 1

о о о о о

0.

о о 1

о о о о о о о о о о 1 1 1 1

о 1

о 1 1

о 1 1 1 1 1 1 1 1 1

о 1

о о

о I I о

0.

1 1

1 1 1

о 1

о о

о о о 1

о 1 1

о о о о о о о о о о о о о о о 1

о 1 1

1 1 1

о о о 1

о о о о о о о о о о о о о о о о о о о

о о о о 1 I 1

Вы)(од 3 Bbiwd

м

ft

Ci

t$

о «Q

Bbiwd 1

Фиг. 2

Фиг. 5

,

oi{зл.гpaд)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления преобразователем | 1985 |

|

SU1246300A1 |

| Преобразователь постоянного напряжения в многоступенчатое квазисинусоидальное | 1986 |

|

SU1415380A1 |

| Устройство для управления преобразователем источника гарантированного питания | 1987 |

|

SU1603506A1 |

| Преобразователь постоянного напряжения в многоступенчатое квазисинусоидальное | 1981 |

|

SU991564A2 |

| Устройство регулирования компенсатора реактивной мощности | 1990 |

|

SU1830524A1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1984 |

|

SU1241177A1 |

| Формирователь синусоидальных сигналов | 1986 |

|

SU1429281A1 |

| Автоматическое устройство для поверки стрелочных электроизмерительных приборов | 1985 |

|

SU1320783A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ СИНУСОИДАЛЬНОГО НАПРЯЖЕНИЯ | 2015 |

|

RU2582880C2 |

| Задающее устройство для цифрового следящего привода | 1986 |

|

SU1411709A1 |

Изобретение относится к преобразовательной технике и может быть использовано в системах автономного электроснабжения. Целью изобретения является повьшение точности стабилизации выходного напряжения. С выхода модуля разности кодов арифметического устройства 6 код поступает на первый вход схемы 8 сравнения кодов,на второй вход которой поступает число с выхода задатчика 7 допустимого расхождения кодов. С выхода схемы 8 сравнения кодов сигнал поступает на первые входы элементов Pi 9 и 10, на вторые входы которых поступают сигналы: на элемент И 9 - сигнал нарастания полуволны, на элемент И 10 - сигнал убывания полуволны. Таким обра- зом, в реверсивном счетчике 11 происходит добавление единицы, если полуволна выходного напряжения нарастает, и вычитание, если полуволна убывает. Во избежании сбоев по окончании каждой полуволны, аппроксимируемой программной кривой, реверсивный счетчик И обнуляется. 4 ил,, 2 табл. 3 (Л ФигЛ

Редактор И.Шулла

Составитель В.Бунаков Техред Н, Глущенко

Заказ 2525/52 Тираж 660Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор Г.Решетник

| Статический преобразователь с выходным напряжением заданной величины и формы | 1971 |

|

SU505104A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь постоянного напряжения в многоступенчатое квазисинусоидальное | 1980 |

|

SU905962A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-06-23—Публикация

1983-12-20—Подача