11

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки цифровых данных, в частности в,цифровой звукозаписи.

Целью изобретения является повышение помехозащищенности устройства.

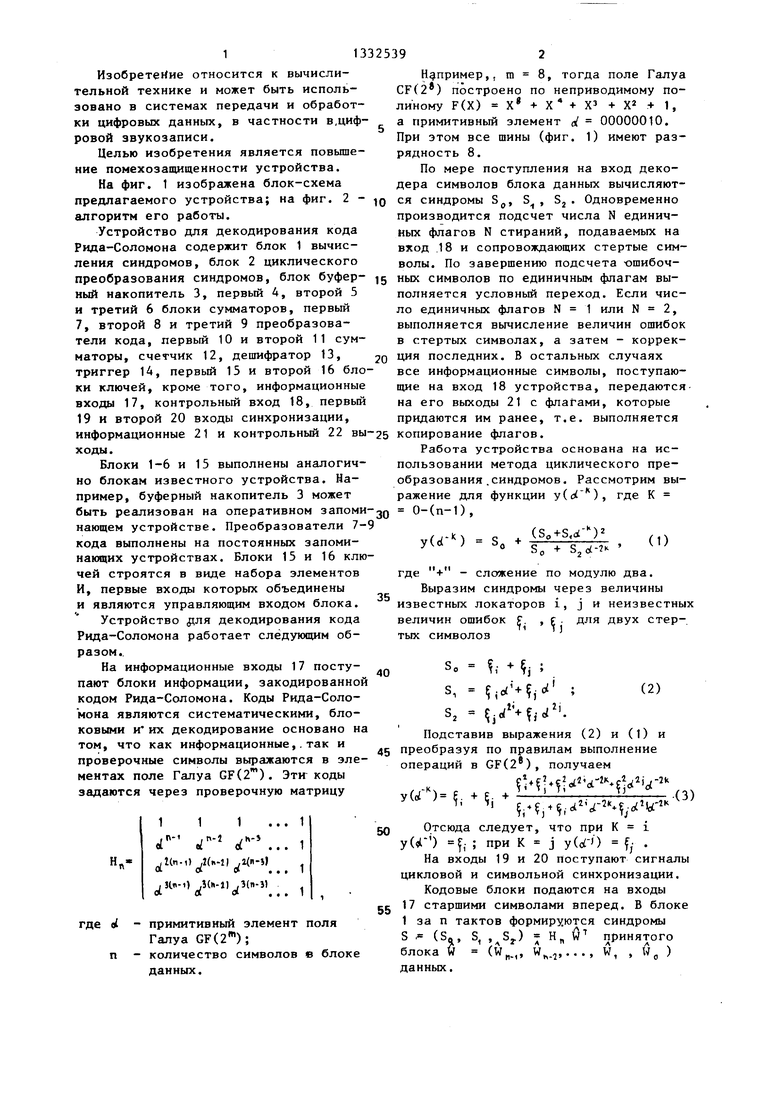

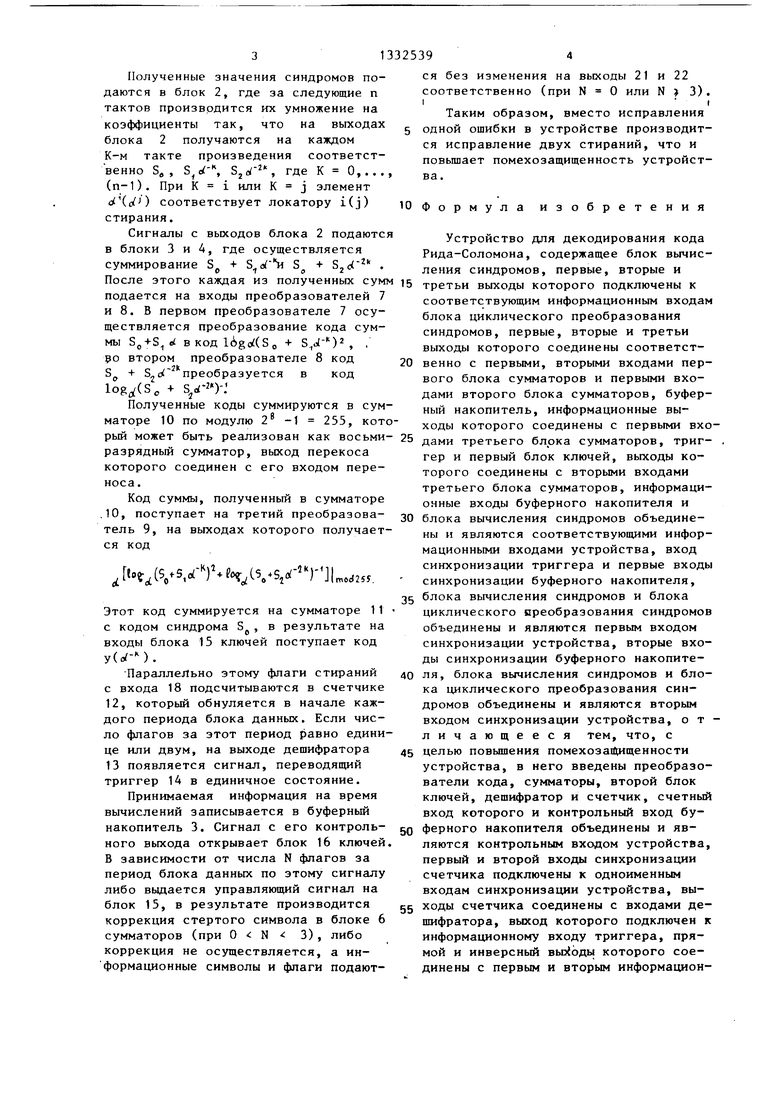

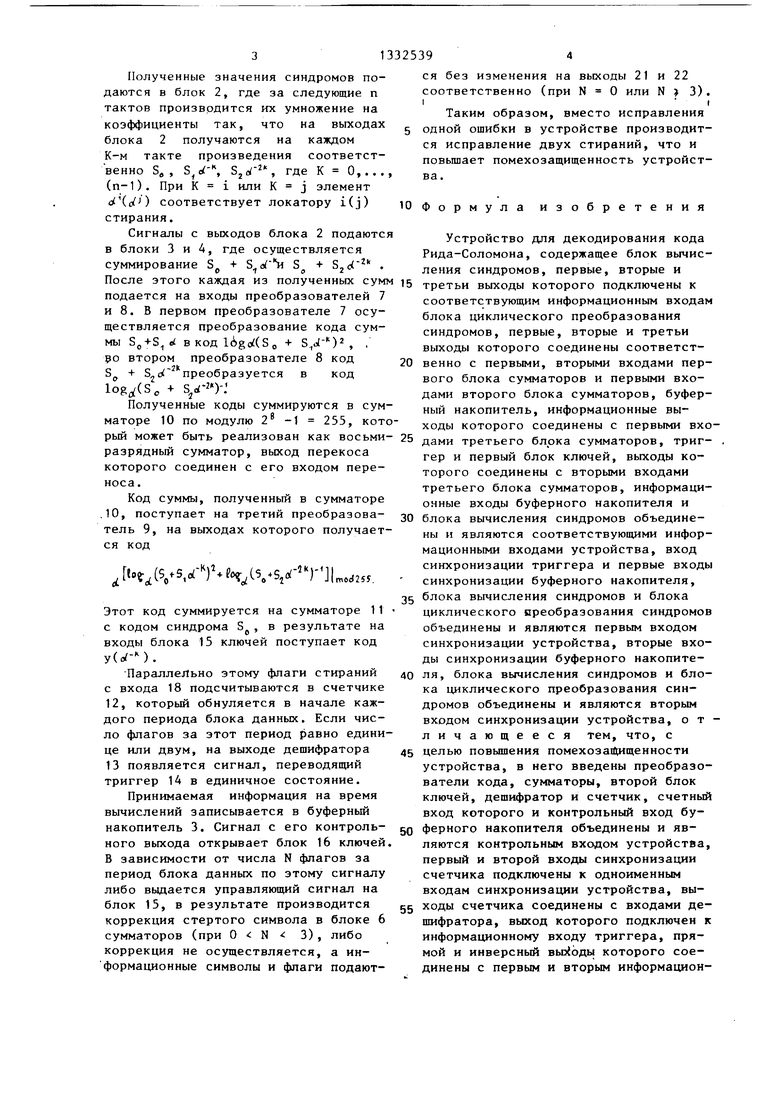

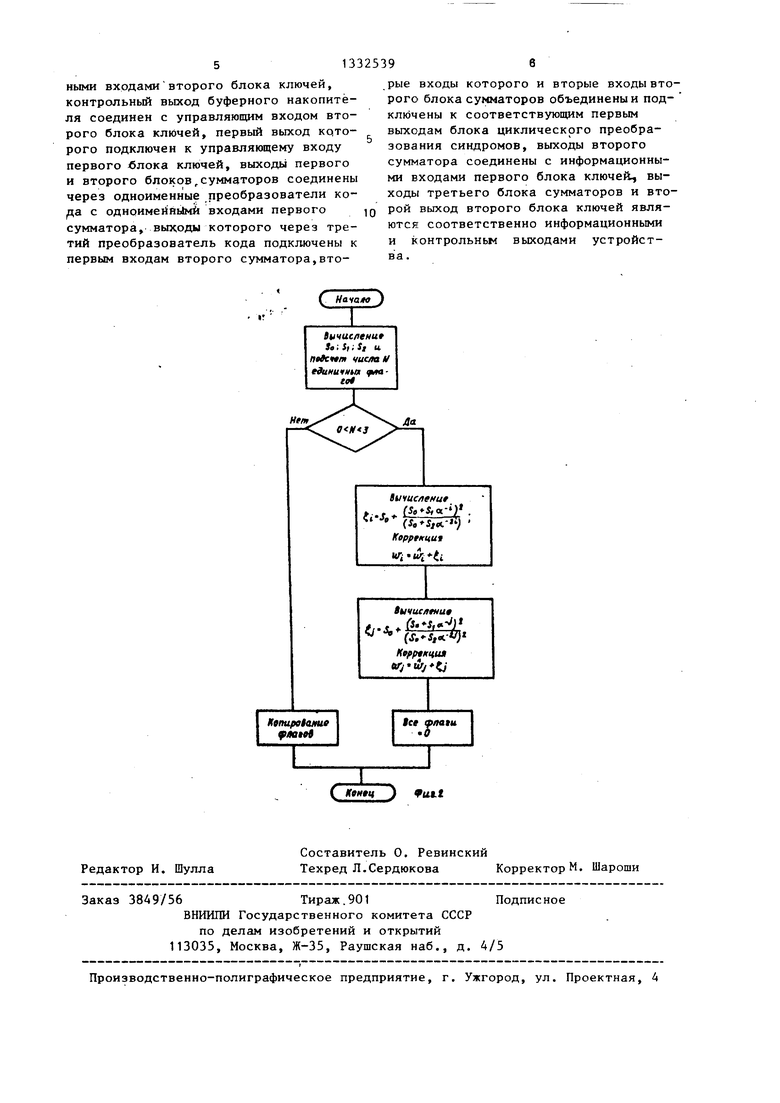

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 - алгоритм его работы.

Устройство для декодирования кода Рида-Соломона содержит блок 1 вычисления синдромов, блок 2 циклического

преобразования синдромов, блок буфер- ,5 ных символов по единичным флагам вы- ный накопитель 3, первый 4, второй 5 полняется условный переход. Если чис- и третий 6 блоки сумматоров, первый ло единичных флагов N 1 или N 2,

выполняется вычисление величин ошибок в стертых символах, а затем - коррек7, второй 8 и третий 9 преобразователи кода, первый 10 и второй 11 сум20

ция последних. В остальных случаях все информационные символы, поступающие на вход 18 устройства, передаются на его выходы 21 с флаГами, которые придаются им ранее, т.е. выполняется

маторы, счетчик 12, дешифратор 13, триггер 14, первый 15 и второй 16 блоки ключей, кроме того, информационные входы 17, контрольный вход 18, первый 19 и второй 20 входы синхронизации,

информационные 21 и контрольный 22 вы-25 копирование флагов, ходы.Работа устройства основана на неБлоки 1-6 и 15 выполнены аналогич- пользовании метода циклического пре- но блокам известного устройства. На- образования .синдромов. Рассмотрим вы- пример, буферный накопитель 3 может ражение для функции ), где К быть реализован на оперативном запоми- д 0-(п-1), нающем устройстве. Преобразователи 7-9 кода выполнены на постоянных запоминающих устройствах. Блоки 15 и 16 ключей строятся в виде набора элементов И, первые входы которых объединены и являются управляющим входом блока.

Устройство ;ля декодирования кода Рида-Соломона работает следующим образом..

На информационные входы 17 поступают блоки информации, закодированной кодом Рида-Соломона. Коды Рида-Солоу(о(-М

(So+S,i- )2

Sjci-

(1)

35

где + - сложение по модулю два.

Выразим синдромы через величины известных локаторов i величин ошибок f. , г . тых символов

, J и неизвестных для двух стер40

S, S,

- - i ;

Af.-ci

(2)

мона являются систематическими, блоковыми и их декодирование основано на том, что как информационные,. так и проверочные символы выражаются в элементах поле Галуа GF{2 ). Эти коды задаются через проверочную матрицу

1

1

, ПI

,h-i

Un-i) ;Кк-1| /( j JC«-0 ,J(n-l) ,3{n-J)

ti - примитивный элемент поля Галуа GF(2);

количество символов в блоке данных.

п

Например,, га 8, тогда поле Галуа CF(2) построено по неприводимому полиному F(X) X X + X + X + 1, а примитивный элемент d 00000010. При этом все шины (фиг. 1) имеют разрядность 8.

По мере поступления на вход декодера символов блока данных вычисляются синдромы S, S, Sj. Одновременно производится подсчет числа N единичных флагов N стираний, подаваемых на вход .18 и сопровождающих стертые символы. По завершению подсчета «шибоч

ция последних. В остальных случаях все информационные символы, поступающие на вход 18 устройства, передаются на его выходы 21 с флаГами, которые придаются им ранее, т.е. выполняется

ьзовании метода циклического пре- азования .синдромов. Рассмотрим вы ение для функции ), где К -(п-1),

у(о(-М

(So+S,i- )2

Sjci-

(1)

пользовании метода циклического пре- образования .синдромов. Рассмотрим вы- ражение для функции ), где К д 0-(п-1),

35

где + - сложение по модулю два.

Выразим синдромы через величины известных локаторов i величин ошибок f. , г . тых символов

, J и неизвестны для двух стер

S, S,

- - i ;

Af.-ci

(2)

Подставив выражения (2) и (1) и 5 преобразуя по правилам выполнение операций в GF(2), получаем

„г,-,,. 5,. ; Ь51- -ч1- /1и-1к

(3)

5

-,...l iОтсюда следует, что при К i ) f,. ; при К j yU-0 fy .

На входы 19 и 20 Поступают сигналы цикловой и символьной синхронизации.

Кодовые блоки подаются на входы 17 старшими символами вперед. В блоке 1 за п тактов формируются синдромы

S , (S«. S, ,S,) блока W (W, данных.

WИ-1

W

h-7

Принятого

л л ч

W, , и„ )

Полученные значения синдромов подаются в блок 2, где за следующие п тактов производится их умножение на коэффициенты так, что на выходах блока 2 получаются на каждом К-м такте произведения соответственно S, , Sjc/-, где К О,..., (п-1). При К i или К j злемент о1 ) соответствует локатору i(j) стирания.

Сигналы с выходов блока 2 подаются в блоки 3 и А, где осуществляется суммирование S,

+ S,

S,d

-2k

ся без изменения на вькоды 21 и 22

соответственно (при N О или N 3 I

Таким образом, вместо исправлени

5 одной ошибки в устройстве производи ся исправление двух стираний, что и повышает помехозащищенность устройс ва.

10 Формула изобретени

Устройство для декодирования код Рида-Соломона, содержащее блок вычи

ления синдромов, первые, вторые и После этого каждая из полученных сумм ig третьи выходы которого подключены к подается на входы преобразователей 7 и 8. В первом преобразователе 7 осуществляется преобразование кода сумсоответствующим информационным вход блока циклического преобразования синдромов, первые, вторые и третьи выходы которого соединены соответст 20 венно с первыми, вторыми входами пе вого блока сумматоров и первьпчи вхо дами второго блока сумматоров, буфе ный накопитель, информационные выходы которого соединены с первыми вх

мы , oi вкoдl6go(So + S,ci- )2, 90 втором преобразователе 8 код преобразуется в код

+

s,-)-:

соответствующим информационным входам блока циклического преобразования синдромов, первые, вторые и третьи выходы которого соединены соответст- 20 венно с первыми, вторыми входами первого блока сумматоров и первьпчи входами второго блока сумматоров, буферный накопитель, информационные выходы которого соединены с первыми вхоlog CS ,2Полученные коды суммируются в сумматоре 10 по модулю 2 -1 255, который может быть реализован как восьми- 25 дами третьего блока сумматоров, триг- , разрядный сумматор, выход перекоса которого соединен с его входом переноса.

Код суммы, полученный в сумматоре .10, поступает на третий преобразовагер и первый блок ключей, выходы которого соединены с вторыми входами третьего блока сумматоров, информационные входы буферного накопителя и

30 блока вычисления синдромов объединены и являются соответствующими информационными входами устройства, вход синхронизации триггера и первые входы синхронизации буферного накопителя,

тель 9, на выходах которого получается код

J4().s,- )JL.d25r

Этот код суммируется на сумматоре 11 с кодом синдрома S , в результате на входы блока 15 ключей поступает код у().

Параллельно этому флаги стираний с входа 18 подсчитываются в счетчике 12, который обнуляется в начале каждого периода блока данных. Если число флагов за этот период равно единице или двум, на выходе дешифратора 13 появляется сигнал, переводящий триггер 14 в единичное состояние.

Принимаемая информация на время вычислений записывается в буферный

накопитель 3. Сигнал с его коитроль- ферного накопителя объединены и явного выхода открывает блок 16 ключей. В зависимости от числа N флагов за период блока данных по этому сигналу либо выдается управляющий сигнал на блок 15, в результате производится коррекция стертого символа в блоке 6 сумматоров (при О N 3) , либо коррекция не осуществляется, а информационные символы и флаги подаютляются контрольным входом устройства первый и второй входы синхронизации счетчика подключены к одноимениым входам синхронизации устройства, вы- 55 ходы счетчика соединены с входами де шифратора, выход которого подключен информационному входу триггера, прямой и инверсный выз{одь1 которого соединены с первым и вторым информацион

,

я

ся без изменения на вькоды 21 и 22

соответственно (при N О или N 3). I I

Таким образом, вместо исправления

5 одной ошибки в устройстве производится исправление двух стираний, что и повышает помехозащищенность устройства.

10 Формула изобретения

Устройство для декодирования кода Рида-Соломона, содержащее блок вычисления синдромов, первые, вторые и третьи выходы которого подключены к

соответствующим информационным входам блока циклического преобразования синдромов, первые, вторые и третьи выходы которого соединены соответст- венно с первыми, вторыми входами первого блока сумматоров и первьпчи входами второго блока сумматоров, буферный накопитель, информационные выходы которого соединены с первыми входами третьего блока сумматоров, триг- ,

дами третьего блока сумматоров, триг-

гер и первый блок ключей, выходы которого соединены с вторыми входами третьего блока сумматоров, информационные входы буферного накопителя и

блока вычисления синдромов объединены и являются соответствующими информационными входами устройства, вход синхронизации триггера и первые входы синхронизации буферного накопителя,

блока вычисления синдромов и блока циклического преобразования синдромов объединены и являются первым входом синхронизации устройства, вторые входы синхронизации буферного накопителя, блока вычисления синдромов и блока циклического преобразования синдромов объединены и являются вторым входом синхронизации устройства, отличающееся тем, что, с

целью повышения помехозагЦищенности устройства, в него введены преобразователи кода, сумматоры, второй блок ключей, дешифратор и счетчик, счетный вход которого и контрольный вход буферного накопителя объединены и являются контрольным входом устройства, первый и второй входы синхронизации счетчика подключены к одноимениым входам синхронизации устройства, вы- ходы счетчика соединены с входами дешифратора, выход которого подключен к информационному входу триггера, прямой и инверсный выз{одь1 которого соединены с первым и вторым информацион513

ными BXpflaNm второго блока ключей, контрольный выход буферного накопителя соединен с управляющим входом второго блока ключей, первый выход KQTO- рого подключен к управляющему входу первого блока ключей, выходы первого и второго блоков сумматоров соединены через одноименные преобразователи ко- |Ца с одноимейяь1мй входами первого сумматора, выходы которого через третий преобразователь кода подключены к первым входам второго сумматора,вто

С

tv4uc/ieHuf Se.SiiS, и Пввсчвп числа и ifduHuima 9иа- ив

6

рые входы которого и вторые входы второго блока сумматоров объединены и под- ключены к соответствующим первым выходам блока циклического преобразования синдромов, выходы второго сумматора соединены с информационными входами первого блока ключей, выходы третьего блока сумматоров и второй выход второго блока ключей являются соответственно информационными и контрольные выходами устройст- в а.

KonupelaiHif fUttMt

I

С J «Puit

Редактор И, Шулла

Составитель О. Ревинский

Техред Л.Сердюкова Корректор М. Шароши

Заказ 3849/56Тираж.901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

9U4UC/lfHUf

t.s .

() Kopptirnui

Wi.

tU4uc/itnue

f:.S,bilh

fj.-jr,-v;« Kffpetrnia Vj iSf/

let 0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования кода Рида-Соломона | 1990 |

|

SU1718385A2 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ КОДА РИДА - СОЛОМОНА | 1991 |

|

RU2007040C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ КОДА РИДА - СОЛОМОНА | 1991 |

|

RU2007041C1 |

| Устройство обнаружения и исправления ошибок в кодах Рида-Соломона | 1986 |

|

SU1381719A1 |

| Устройство для декодирования кодов Рида-Соломона | 1985 |

|

SU1309317A1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Устройство для коррекции ошибок | 1984 |

|

SU1287295A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

Изобретение относится тс вычислительной технике. Его использование в системах передачи и обработки цифровой информации, в частности к цифровой звукозаписи, позволяет повысить помехоустойчивость устройства. Устройство содержит блок 1 вычисления синдромов, блок 2 циклического преобразования синдромов, буферный накопитель 3, блоки 4-6 сумматоров, триггер 14 и блок 15 ключей. Введение преобразователей 7-9 кода, сумматоров 10 и 11, счетчика 12, дешифратора 13 и блока 16 ключей обеспечивает исправление двух стертых символов взамен ошибочного. 2 ил. i СЛ со 00 ю ел со со Фиг/

| Цифровая звуковая система Компакт Диск | |||

| Стандарт МЭК | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Техника средств связи | |||

| Серия ТРПА, 1984, № 3, с | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-08-23—Публикация

1985-12-30—Подача