Изобретение относится к вычисли- стельной техники и может быть использова- но в устройствах декодирования информации, закодированной кодом Рида- Соломона.

Известно устройство для вычисления локаторов ошибок, в котором используется процедура Меня. Это устройство содержит регистр, каждый разряд которого содержит ячейку памяти, умножитель на обратный

элемент поля Галуа а и сумматор по модулю два.

Определение локаторов осуществляется путем последовательного занесения в регистр всех возможных элементов поля, сдвига содержимого регистра и проверки его состояния. Если содержимое регистра равно 0, то внесенный элемент поля являет- .ся локатором ошибки.

Недостатком устройства является его низкое быстродействие, так как на вычисление, например, четырех локаторов требуется 4255 сложений и 4255 умножений.

Известно устройство для нахождения двух локаторов ошибок, содержащее три блока постоянной памяти, элемент И, четыре регистра, три коммутатора, дешифратор, перемножитель, группу из пл триггеров, два блока оперативной памяти, три элемента НЕ и группу из т-2 сумматоров по модулю два.

Недостатком устройства является ограниченная кратность исправляемых ошибок.

Наиболее близким по технической сущности к предлагаемому является устройство для определения локаторов ошибок, в котором обеспечивается обнаружение четырех локаторов ошибок Xi - Х4 путем решения ключевого уравнения четвертой степени G(X) X4 + G1Х3 + G2X2 + G3X + G4,(1)

в котором

Gl Xl+X2 + X3 + X4;

G2 - Х1Х2 + XlX3 + XlX4 + Х2ХЗ + Х2Х4 + ХзХ/,1 G3 Х1Х2Хз + Х1Х2Х4 + Х1ХЗХ4 + Х2Х3Х4, (2) G4 Х1Х2ХзХ4.

Коэффициенты ключевого уравнения Gir т- G4 определяются по системе рекуррентных уравнений:

Ss + S4G1 + 8362 + 8263 + 8164 0;

Se + SsG 1 +8462+ 5зСз +8264 0; (3)

8 + SeG1 + 8562 + 8463 + 8364 0;

SB + 8761 + 8еСз + SsGg + 8464 0, где 81 - 83 - синдромы ошибок.

При этом процесс расчета и преобразований принятых символов, каждый из которых содержит m бит в поле Галуа GF(2m), осуществляется в нормальном базисе. Все элементы (символы) поля GF(2m) можно представить в виде степени примитивного

элемента а. Если примитивный элемент а удовлетворяет дополнительному условию: элементы а, а2, а4, а8 ..., являются линейно, независимыми над

GF(2m), то они образуют нормальный базис.

В таблицах неприводимых многочленов

можно выбрать примитивный многочлен со

ответствующей степени, корни которого

J

0 а линейно независимы, где i 0, 1, 2

m - 1. Тогда произвольный элемент у.Ј GF(2m) может быть представлен как некоторая степень аи в и виде разложения по нормальному базису

т-1i,

у 2 у,а2 о

Представление элемента у в виде разложения по нормальному базису удобно при возведении в степень вида 2 и извлечения корня степени 21. Например, если элемент

-a + yi а2 + у2а4 +

+ym- ram 1

возвести в квадрат, то получим

f-fatfwVW -- Г. +

так как a2(. a. Таким образом, возведение в квадрат означает циклический сдвиг элемента на один разряд вправо. Извлечение квадратного корня осуществляется сдвигом на один разряд влево. Это упрощает операции возведения в квадрат и извлечения квадратного корня, что увеличивает быстродействие.

Для нахождения локаторов ошибок необходимо преобразовать уравнение

X4 + X3Gi + X2G2 + XG3 + G4 0(4)

Лf -41

подстановкой X -h ) г у v G 1

5

0

5

0

5

0

urn,-,

.-Ifm-IJ

формула (4)

5

0

5

приводится к виду

1

АО

0.

(5)

где

Новая подстановка дает уравнение Z4 + Z2 + KiZ + К2 О,

Ao G4+lG2GA) + (G1)2

Gl1/9Gl

A2 G2 + (GiG3)1/2; Ki Gi(A|);

. AJ

(5)

(6)

(7) (8) (9)

(10)

Уравнение (б) можно представить в биквадратной форме

Z4 + Z2 + KiZ + K2 (Z2 + AZ + B) (Z2 + AZ+

+ C) 0,

где А2 + В + С 1 ;

A(B + C)Ki;

BC K2 ;

(11) (12)

(13)

Эти уравнения приводятся к следующим видам:

А3 + А + Ki 0;

В2 + (1 + А2) В + К2 О

С помощью подстановки

U+F

t

кубическое уравнение (14) приводится к ви- 15

ДУ ,

t2+Kn+1 0.

Заменой переменной t Ki у получаем

У2+У+- 0. К2

Обозначим h

1

М

, тогда

y2+y + .(18)

Для элементов поля Галуа GF(2m), пред-

ставленных в нормальном базисе, корень

уравнения (18)

у-(0, hi, hi + h2, hi + п2 + Ьзhi + ti2 +

...hm--l).(i$

где hi - i-й разряд символа h.

Приведем квадратное уравнение (15) к удобному для решения виду с помощью подстановки В Yi(1+A2). В результате получим

Y -f Y 1 +

К2

0

(1+А2)2 Для нахождения локаторов ошибочных комбинаций необходимо найти величины

КЗ

m

К2

(20) (21)

(1 +А2)2 Yi(0, mi, mi + rrt2,,..,mi + 012 + ... + mm-i).(2.2)

Решим квадратное уравнение, Z2 + AZ + +B 0.

Подставим Z Ae. . в результате получим

Ј2+Ј+ В 0 А2

п

Обозначим а)

А

В результате получим

Ј 2 + Ј + а) 0 .(24)

Корни уравнения (24) получают по выражениям

Ј., (0,, eJ1-cJ2,...a,«-a34...«cJrn-,); 5) Јг-Г1,11- .,..Mlt4 ЈV - - Jm-t; (26)

Приведем второе квадратное уравне-/2

5 ние Z + AZ + С 0 к каноническому виду

е2 +е +v Q,

(27)

(14) (15)

(16) (17)

ем

(23)

10

ви- 15

20

(18)

ред- 25

ень

ti2 +

(i$

5) к подчим

30

35

ных ы

20) 40 (21)

.(2.2)

AZ +

пол45

50

(24)

ыра55

где .

(28)

Соответствующие корням уравнения символы получают из выражений

e,ro,1,,);(29)

e/, (V V v v2 li+l v 2 M |) (5°)

Путем преобразования символов, соответствующих элементам поля Галуа, по выражениям (4) - (30) находятся локаторы ошибок Xi - Х4.

Однако данное устройство обладает низким быстродействием, так как на определение всех локаторов ошибок тратится 107 тактов.

Это затрудняет исправление ошибок в информации, принимаемой из высокоскоростных устройств, например оптических

эу

О .|

Цель изобретения -увеличение быстродействия вычисления локаторов ошибок в информации, защищенной циклическими кодами,

Поставленная цель достигается тем, что в устройство для вычисления локаторов ошибок, содержащее триггер, установочный вход которого является входом пуска устройства, выход триггера соединен с первым входом элемента И, второй вход которого является тактовым входом входом устройства, выход элемента И подключен к счетному входу счетчика импульсов, вход обнуления которого объединен с входом обнуления триггера и является входом обнуления устройства, выходы счетчика импульсов соединены со входами первого и второго формирователей адресов и формирователя управляющих сигналов, выходы которого подключены к соответствующим управляющим входам кольцевого регистра сдвига, первые и вторые выходы второго формирователя адресов соединены с адресными входами соответственно первого и второго мультиплексоров, выходы которых подключены к первым и вторым входам перемножителя, выходы которого соединены с первыми информационными входами третьего мультиплексора, выходы первого формирователя адресов подключены к адресным входам третьего мультиплексора

и первого и второго блоков оперативной памяти (60П), формирователь логической единицы, выход которого соединен с первыми информационными входами первого и второго мультиплексоров, вторые и третьи информационные входы которых являются соответственно первыми - четвертыми информационными входами устройства, выходы первого БОП соединены с четвертыми информационными входами первого мультиплексора, выходы второго БОП подключены к четвертым информационным входам второго мультиплексора и входам первого и второго преобразователей кодов, выходы которых соединены соответственно с пятыми и шестыми информационными входами второго мультплексора, накапливающий сумматор по модулю два, выходы которого подключены к вторым информационным входам третьего мультиплексора, дополнительно включены третий преобразователь кодов и четвертый мультиплексор, первые информационные входы которого объединены с входами накапливающего сумматора по модулю два и подключены к выходам перемножителя, адресные и вторые информационные входы четвертого мультиплексора подключены к выходам соответственно первого формирователя адресов и накапливающего сумматора по модулю два, выходы третьего мультплексора соединены с информационными входами первого БОП и кольцевого регистра сдвига, выходы которого подключены непосредственно и через третий преобразователь кодов соответственно к пятым и шестым информационным входам первого мультиплексора, выходы четвертого мультиплексора соединены с информационными входами второго БОП, выходы которого являются выходами устройства.

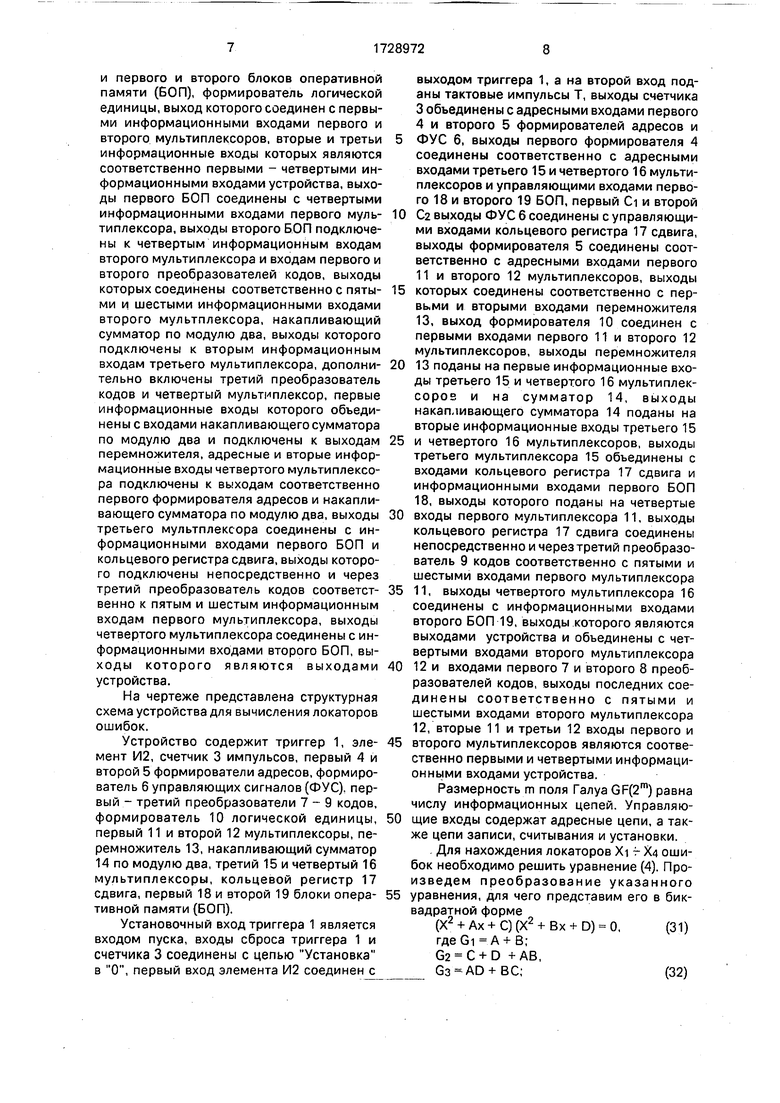

На чертеже представлена структурная схема устройства для вычисления локаторов ошибок.

Устройство содержит триггер 1, элемент И2, счетчик 3 импульсов, первый 4 и второй 5 формирователи адресов, формирователь 6 управляющих сигналов (ФУС), первый - третий преобразователи 7-9 кодов, формирователь 10 логической единицы, первый 11 и второй 12 мультиплексоры, перемножитель 13, накапливающий сумматор 14 по модулю два, третий 15 и четвертый 16 мультиплексоры, кольцевой регистр 17 сдвига, первый 18 и второй 19 блоки оперативной памяти (БОП).

Установочный вход триггера 1 является входом пуска, входы сброса триггера 1 и счетчика 3 соединены с цепью Установка в О, первый вход элемента И2 соединен с

выходом триггера 1, а на второй вход поданы тактовые импульсы Т, выходы счетчика

3объединены с адресными входами первого

4и второго 5 формирователей адресов и ФУС 6, выходы первого формирователя 4

соединены соответственно с адресными входами третьего 15 и четвертого 16 мультиплексоров и управляющими входами первого 18 и второго 19 БОП, первый Ci и второй

0 Са выходы ФУС 6 соединены с управляющими входами кольцевого регистра 17 сдвига, выходы формирователя 5 соединены соответственно с адресными входами первого 11 и второго 12 мультиплексоров, выходы

5 которых соединены соответственно с первыми и вторыми входами перемножителя 13, выход формирователя 10 соединен с первыми входами первого 11 и второго 12 мультиплексоров, выходы перемножителя

0 13 поданы на первые информационные входы третьего 15 и четвертого 16 мультиплексоров и на сумматор 14, выходы накапливающего сумматора 14 поданы на вторые информационные входы третьего 15

5 и четвертого 16 мультиплексоров, выходы третьего мультиплексора 15 объединены с входами кольцевого регистра 17 сдвига и информационными входами первого БОП 18, выходы которого поданы на четвертые

0 входы первого мультиплексора 11, выходы кольцевого регистра 17 сдвига соединены непосредственно и через третий преобразователь 9 кодов соответственно с пятыми и шестыми входами первого мультиплексора

5 11, выходы четвертого мультиплексора 16 соединены с информационными входами второго БОП 19, выходы которого являются выходами устройства и объединены с четвертыми входами второго мультиплексора

0 12 и входами первого 7 и второго 8 преобразователей кодов, выходы последних соединены соответственно с пятыми и шестыми входами второго мультиплексора 12, вторые 11 и третьи 12 входы первого и

5 второго мультиплексоров являются соотве- ственно первыми и четвертыми информационными входами устройства.

Размерность m поля Галуа GF(2m) равна числу информационных цепей. Управляю0 щие входы содержат адресные цепи, а также цепи записи, считывания и установки.

. Для нахождения локаторов Xi f X4 ошибок необходимо решить уравнение (4). Произведем преобразование указанного

5 уравнения, для чего представим его в биквадратной форме

(X2 + Ax + C)(X2 + Bx + D) 0,(31)

гдеСт А + В;

G2 C + D + АВ,

Ga-AD + BC;(32)

G4 CD. Обозначим

/г АВ.(33)

Тогда

/гл+ (GiGs + G22) + G2i 64 + G23 + 616263 0;

L G

„2.

163 + 62% / 61 64 + G + G162

/H3 + L i+M Q. Делаем замену /M dv.

где d ViT. Получим

v3 +v+ K 0, ГДё

M

т2Г i

Замена

V y У

дает у3+Аг + К

У3 Новая замена

y3 z .

-у

3

дает у +У+-I М

Обозначим

i 3

m

М

2

В результате получим у2 +у+ т 0;

у 1 (0, mi, mi + maгщ + ma + ...m); (44)

У2-1 + У1 (45)

Из выражений (32) и (33) можно пол- 40 учить

A + Gi A+ /4 0.

(46)

Заменим А U GL В результате получим

Lr + U + t 0,

где г

..JL

бГ

тогда

Ui (0, ti, ti + t2ti + Т2 + ... + t 7); (49)

. + IH.(50) 50

Из выражения (32)

B Gi + A;(51)

D 62 + С + ft.(52)

Тогда

G4 C(G2 + C+ ц).(53) 55

Отсюда С2 + (G2+/OC + G4 0. Заменим (G2+)w,(54)

В результате получим

,2

а) +ш+р 0 ,

5

10

15

20

где

(56)

(G2+/O2 Тогда

СО 1 (0,/01 ,/31 +р2pi +

+Р2+...+Р)(57)

Имеем X2 + АХ + С 0, с помощью подстановки

Xi А р(58)

получаем

р2+р+е 0,(59)

где

(60)

А2

vt ro1et,.l,..,,el V- Јf) 61)

25

30

X2 Xi + A.

Аналогично

X2 + BX + D 0

с помощью подстановки

получим

у2 + у + I О,

(62) (63) (64)

(65) (66)

(43)

35

(44)

(45)

пол- 40

(46)

чим

(47) 45 48)

(49)

(50) 50

(51)

(52)

(53) 55

ним (54)

(55)

У1 (0, fi, Ei + Г2,..Л 1 + fe + ... + ); (67)

Х4 Хз+В.(68)

Устройство работает следующим образом.

Программы работы устройства записаны в формирователях 4 и 5 адресов и формирователе 6 управляющих сигналов. Эти формирователи построены на основе блоков постоянной памяти. Они осуществляют управление мультиплексорами, выдают адреса и сигналы записи и считывания в БОП.

На основе блоков постоянной памяти построены преобразователи 7-9 кодов. С помощью третьего преобразователя 9 берется обратная величина 1//3, где /3- элемент поля Галуа GF(2-m), m - размерность поля. Первый преобразователь кодов 7 используется для ускорения решения уравнения второй степени, а второй преобразователь 8 - уравнения третьей степени.

При этом на входной мультиплексор 1 i подаются величины Gi и Сз, а на мультиплексор 12 - G2 и G4. Формирователи 4-6 работают по жесткому алгоритму.

Устройство работает с элементами поля Галуа GF(2m), поэтому каждая информационная шина имеет m цепей (разрядов). Число цепей в адресных шинах определяется

количеством символов, записывающих в соответствующий БОП, а число цепей в управ- ляющих шинах - числом адресов и количеством управляющих сигналов записи, считывания и установки.

Устройство работает в следующей последовательности. В начале определяются величины L выражениям (34) и (35). Работа начинается с подачи сигнала Пуск на вход устройства (триггера 1). Триггер 1 устанавливается в 1 и открывет элемент 1/12, через который на вход счетчика 3 начинают поступать тактовые импульсы Т. Счетчик начинает выдавать последовательность чисел, по которым из формирователей 4-6 выбираются необходимые команды для расчетов.

На первом такте на вторые входы перемножителя 13 формирователь 5 адресной шиной А2 подключает через мультиплексор 12 величину G2, а адресной шиной AI величину а° 1 с выхода формирователя 10 логической 1 на первые входы. В результате G2 с выхода перемножителя проходит через мультиплексор 15 и записывается в БОП 18. При этом на мультиплексор 15 и БОП 18 подаются соответствующие адреса и сигналы записи из формирователя 4.

На втором такте из БОП 18 на первые входы перемножителя 13 через мультиплексор 11 подается величина , а на вторые входы через мультиплексор 12 с входа устройства также подается величина G2. Полученная с выхода перемножителя величина G2 записывается на сумматор 14 по модулю 2 накапливающего типа.

Предварительно на первом такте накапливающий сумматор 14 устанавливается в О.

На третьем такте на входы перемножителя подаются аналогично предыдущему с входа устройства величины GI и Ga. Произведение СгСззаписывается в БОП 18 и складывается с С22на сумматоре 14, а затем полученная величина L на четвертом такте записывается через мультиплексор 16 и БОП 19 в кольцевой регистр 17 сдвига.

На пятом такте на первый вход перемножителя подается GI, а на второй а° . На этом же такте на регистр 17с ФУС 6 подается сигнал Сч Сдвиг вправо, в результате в регистре 17 будет получена величина L2 ,С выхода перемножителя через мультиплексор 16 записывается в БОП 19. На этом же такте стирается содержимое накапливающего сумматора 14.

На следующем такте на первый вход перемножителя 13 с входа устройства и на второй вход с выхода БОП 19 подается величина

0

5

0

5

0

5

0

5

0

5

G1. Произведение GI через мультиплексор 15 записывается в БОП 18.

о

На 7-м такте величина GI из БОП 18 подается на первый вход перемножителя 13, а на второй вход G4 с входа устройства. Полученное произведение записывается в сумматор 14. На 8-м такте на первый вход перемножителя 13 подается величина Gs с

входа устройства, а на второй вход а° . С выхода перемножителя 13 величина Сз записывается в БОП 19. На следующем такте величина Сз подается на входы перемножителя 13 с входа устройства и из БОП 19. Произведение Gs с выхода перемножителя 13 складывается с в сумматоре 14. На 10-м такте на первые входы перемножителя подается с выхода БОП 18 величина GrGa, a на вторые входы - с входа устройства величина G2. Произведение GI 62 Сз складывается с содержимым накапливающего сумматора 14. Полученная величина М переписывается на 11-м такте в БОП 19.

Дальше производится вычисление К по формуле (38), при этом вначале определена величина L . Напомним, что в регистре 17 записана величина L2, а в БОП 19 - L На 12-м такте из регистра 17 на первые входы перемножителя подается L , а на вторые из БОП 19 - L Величина L3 с выхода перемножителя 13 записывается на кольцевой регистр 17. На 13-м такте в регистр 17 из ФУС 6 подается сигнал С2 Сдвиг влево, в результате содержимое регистра циклически сдвигается на 1 разряд и в нем будет получена величина L . На 14-м также эта величина из регистра 17 подается в качестве адреса на вход преобразователя 9 кодов, по которому в нем записана обратная величина 1 / / . В данном случае / .

Величина 1/ / подается на первые входы перемножителя 13, на вторые входы которого подается величина /и из БОП 19. На выходе перемножителя 13 получают К, которую записывают в БОП 19.

Решение кубического уравнения (37) осуществляется с помощью преобразователя 8 кодов, при подаче на вход которого величины К на выходе получают величину v, поскольку эта величина зависит только от К. Таким образом, опускается целый ряд промежуточных преобразований, что увеличивает быстродействие вычислений. При этом необходимо для каждого К на ЭВМ рассчитать по формулам (39) - (44) свое значение v , которое затем записывается в преобразователь 8 кодов.

На 15-м такте определяют d по формуле (36). Для этого из БОП 19 списывается L и подается на вторые входы перемножителя i$

а на первые входы подается а° . Полученный результат а° L записывается в регистр 17 сдвига. На 16-м такте из ФУС 6 на этот регистр подается сигнал С2 Сдвиг влево, в результате чего в нем получают величину VTT.

На 17-м такте на первые входы перемножителя 13 подается с регистра 17 величина VL. При этом из БОП 19 списывается К и в качестве адреса подается на вход преобразователя 8 кодов , на выходе которого получают величину v, которая подается на вторые входы перемножителя 13.

Полученную на выходе величину /и за- писывают в накапливающий сумматор 14 и в БОП 19. После этого приступают к вычислению р по формуле (56).

Для этого вначале вычисляют знаменатель. На 18-м такте на первые входы пере-

множителя 13 подается величина а° , а на вторые - Ga с входа устройства. Величина Ga с выхода перемножителя 13 подается на сумматор 14, где складывается с /и. Полученная сумма на 19-м такте параллельно записывается на кольцевой регистр 17 сдвига и в БОП 18.

На 20-м такте регистр 17 из ФУС 6 подается сигнал Ci Сдвиг вправо, в результате в нем будет получена величина (G2f +/л )2. На 21-м такте эта величина в качестве адреса подается на вход преобразователя 9 кодов, по которому в нем записана обратная величина 1 / /3 . Здесь / (Ga + /и )2. Величина 1 / / подается на первые входы перемно- жителя 13, а на вторые входы подается G4 с входа устройства. На выходе перемножителя 13 будет получена величина р, которая записывается в БОП 19.

Дальше находится корень со квадратно- го уравнения (55). Поскольку он зависит только от р, то для нахождения его используется преобразователь 7 кодов. В нем по адресу, задаваемому величиной р, записан корень а). Поэтому на 22-м такте величина списывается из БОП 19 и подается на вход преобразователя 7. Полученная на его выходе величина через мультиплексор 12 подается на вторые входы перемножителя 13, на первые входы которого выдается величина Ga + /лиз БОП 18.

В результате в соответствии с выражением (54) на выходе перемножителя 13 получают величину С, которую записывают в БОП 19. Далее аналогично предыдущему решают квадратное уравнение (47). Для этого свободный член t находят по выражению (48). Отметим, что знаменатель Gi был рассчитан ранее и записан в БОП 18. Для пол9)

учения 1/Gi необходимо Gi переписать в кольцевой регистр 17 сдвига. На 23-м такте величина Gi2 подается на первые входы перемножителя 13, на вторые входы которого

подается а° .

С выхода перемножителя 13 величина Gi2 записывается в регистр 17. На 24-м такте величина Gi2 подается на вход преобразователя 9 кодов, с выхода которого величина 1/Gi2 подается на первые входы перемножителя 13, на вторые входы которого подается величина/ из БОП 19. Величина t с выхода перемножителя 13 записывается в БОП 19.

Затем определяют величину А по выражению (46). Для этого на 25-м такте на первые входы перемножителя 13 подается величина Gi с входа устройства, а на вторые входы - величина U, которая получается на выходе преобразователя 7 кодов при подаче на его вход величины t из БОП 19.

Полученную на выходе перемножителя 13 величину А записывают в накапливающий сумматор 14, кольцевой регистр 17 и в БОП 18. После этого определяют свободный член Ј квадратного уравнения (60). На 26-м такте на кольцевой регистр 17 подается сигнал Ci Сдвиг вправо, в результате в нем будет получена величина А2. На следующем такте эта величина подается на вход преобразователя 9 кодов, с выхода которого величина 1/А подается на первые входы перемножителя 13, а на вторые входы поступает величина С из БОП 19. Результат умножения е записывается в БОП 19.

На 28-м такте определяется первый локатор ошибок Xi по выражению (58). Для этого на первые входы перемножителя 13 подается величина А из БОП 18. Величина Ј списывается из БОП 19 и подается на вход преобразователя 7 кодов, с выхода которого полученную величину у подают на вторые входы перемножителя 13.

Таким образом, первый локатор ошибок, полученный на выходе перемножителя 13, записывают в БОП 19. Дальше определяют второй локатор Ха ошибок по (62). Отметим, что величина А уже записана в блоке 18. Поэтому на 29-м тракте на первые входы

перемножителя 13 подается величина а° , а на вторые входы локатор Xi из БОП 19. С выхода перемножителя 13 локатор Xi подается на сумматор 14, где складывается с А. В результате в блоке 14 будет получен локатор ошибок Х2, который на 30-м такте списывается в БОП 19.

Затем необходимо определить величину В по выражению (51). Для этого на 31-м такте на первые входы перемножителя 13

подается величина Gi с входа устройства, а

на вторые входы - а ° . С выхода перемножителя 13 Gi записывают в накапливающий сумматор 14. На 32-м такте на первые входы перемножителя 13 подается величина А из

БОП 18, а на вторые входы - а° . Величина А с выхода перемножителя 13 подается в накапливающий сумматор 14, где складывается с GL В результате будет получена величина В, которая на 33-м такте списывается в БОП 18 и кольцевой регистр 17.

Далее определяется величина D по формуле (52) . На 34-м такте на первые входы

перемножителя 13 подается а°, а на вторые входы - величина G2 с входа устройства.

G2 с выхода перемножителя 13 записывается в накапливающий сумматор 14. На следующем такте на первые входы перемножителя 13 подается а.0 , а на вторые- величина С из БОП 19.

С выхода перемножителя 13 величина С подается в накапливающий сумматор 14, где складывается с G2. Аналогично на 36-м такте в накапливающем сумматоре 14 происходит сложение Gz + С с величиной /и , которую списывают из БОП 19. В результате будет получена величина D, которая на 37-м такте записывается в БОП 19. Затем определяется свободный член f квадратного уравнения (65) по формуле (66). Для этого на 38-м такте из фУС 6 на кольцевой регистр 17 подается сигнал Ci Сдвиг вправо, в результате в нем будет получена величина В . На 39-м такте величина В подается на вход преобразователя 9 кодов, с выхода которого величина 1/В подается на первые входы перемножителя 13, на вторые входы которого подается величина D из БОП 19. Полученная величина Рзаписывается в БОП 19.

На 40-м такте на первые входы перемножителя 13 подается величина В из БОП 18. При этом величина (списывается из БОП 19 и подается на вход преобразователя 7 кодов, с выхода которого величину у подают на вторые входы перемножителя 13.

В результате на выходе перемножителя 13 в соответствии с выражением (64) получают третий локатор ошибок Хз, который параллельно записывают в накапливающий сумматор 14 и в БОП 19.

На 41-м такте на первые входы перемножителя 13 подается величина В из БОП

18, а на вторые входы - а° . С выхода перемножителя 13 величина В подается в накапливающий сумматор 14, где складывается с

Хз. В результате получают четвертый локатор Х4 ошибок, который на 42-м такте записывается в БОП 19, На этом заканчивается определение ошибок Xi т- Х4.

Таким образом, в предлагаемом устройстве для нахождения четырех локаторов ошибок требуется 107 тактов, а в предлагаемом - только 42, следовательно, предлагаемое устройство обеспечивает существенно

0 большее быстродействие.

Формула изобретения Устройство для вычисления локаторов ошибок, содержащее триггер, установочный вход которого является входом пуска уст5 ройства, выход триггера соединен с первым входом элемента И, второй вход которого является тактовым входом устройства, выход элемента И подключен к счетному входу счетчика импульсов, вход обнуления кото0 рого объединен с входом обнуления триггера и является входом обнуления устройства, выходы счетчика импульсов соединены с входам л первого и второго формирователей адресов и формирователя управляющих

5 сигналов, выходы которого подключены к соответствующим управляющим входам кольцевого регистра сдвига, первые и вторые выходы второго формирователя адресов соединены с адресными входами

0 соответственно первого и второго мультиплексоров, выходы которых подключены к первым и вторым входам перемножителя, выходы которого соединены с первыми информационными входами третьего мульти5 плексора, выходы первого формирователя адресов подключены к адресным входам третьего мультиплексора и первого и второго блоков оперативной памяти, формирователь логической единицы, выход которого

0 соединен с первыми информационными входами первого и второго мультиплексоров, вторые и третьи информационные входы которых являются соответственно первыми - четвертыми информационными

5 входами устройства, выходы первого блока оперативной памяти соединены с четвертыми информационными входами первого мультиплексора, выходы второго блока оперативной памяти подключены к четвертым

0 информационным входам второго мультиплексора и входам первого и второго пре- образователей кодов, выходы которых соединены соответственно с пятыми и шестыми информационными входами второго

5 мультиплексора, накапливающий сумматор по модулю два, выходы которого подключены к вторым информационным входам третьего мультипликатора, отличающееся тем, что, с целью повышения быстродействия, в устройство введены третий преобразователь кодов и четвертый мультиплексор, первые информационные входы которого объединены с входами накапливающего сумматора по модулю два и подключены к выходам перемножителя, адресные и вторые информационные входы четвертого мультиплексора подключены к выходам соответственно первого формирователя адресов и накапливающего сумматора по модулю два, выходы третьего мультипликатора соединены с информаци0

онными входами первого блока оперативной памяти и кольцевого регистра сдвига, выходы которого подключены непосредственно и через третий преобразователь кодов соответственно к пятым и шестым информационным входам первого мультиплексора выходы четвертого мультиплексора соединены с информационными входами второго блока оперативной памяти, выходы которого являются входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1985 |

|

SU1552381A1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Устройство для исправления искажений в системах передачи дискретной информации | 1987 |

|

SU1603532A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Преобразователь кода спектра звукового сигнала | 1990 |

|

SU1800618A1 |

| Устройство обнаружения и определения координат объекта на изображении | 1990 |

|

SU1737755A1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

Изобретение относится к вычислительной технике. Его использование в устройствах декодирования информации позволяет повысить быстродействие за счет сокращения в 2,5 раза числа тактов работы. Устройство содержит триггер 1, элемент И 2. счетчик 3 импульсов, формирователи 4, 5, 9 адресов, формирователь 6 управляющих сигналов, преобразователи 7 и 8 кодов, формирователь 10 логической единицы, мультиплексоры 11, 12,15 и 16, перемножитель 13, накапливающий сумматор 14 по модулю два, кольцевой регистр 17, блоки 18 и 19 оперативной памяти 1-2, -3-4-15-17-9-11-13- 14-16-19-7-12-13-15-18-11, 4-19-8-12, 3-5-11, 3-6-17, 14-15-17, 5-12, 10-11. 10-12, 13-16. 4-16,4-18, 19-12. 1 ил. (Л

| Блох Э.Л.и Зяблов В | |||

| В | |||

| Обобщенные каскадные коды | |||

| - М.: Связь, 1976, с.111 - 120 | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для исправления искажений в системах передачи дискретной информации | 1987 |

|

SU1603532A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-04-23—Публикация

1990-04-04—Подача