Изобретение относится к слециализи- рйванным средствам вычислительной тех- И1ки и предназначено для решения интегральных уравнений.

Цель изобретения - расширение функциональных возможностей путем решения интегральных уравнений общего вида.

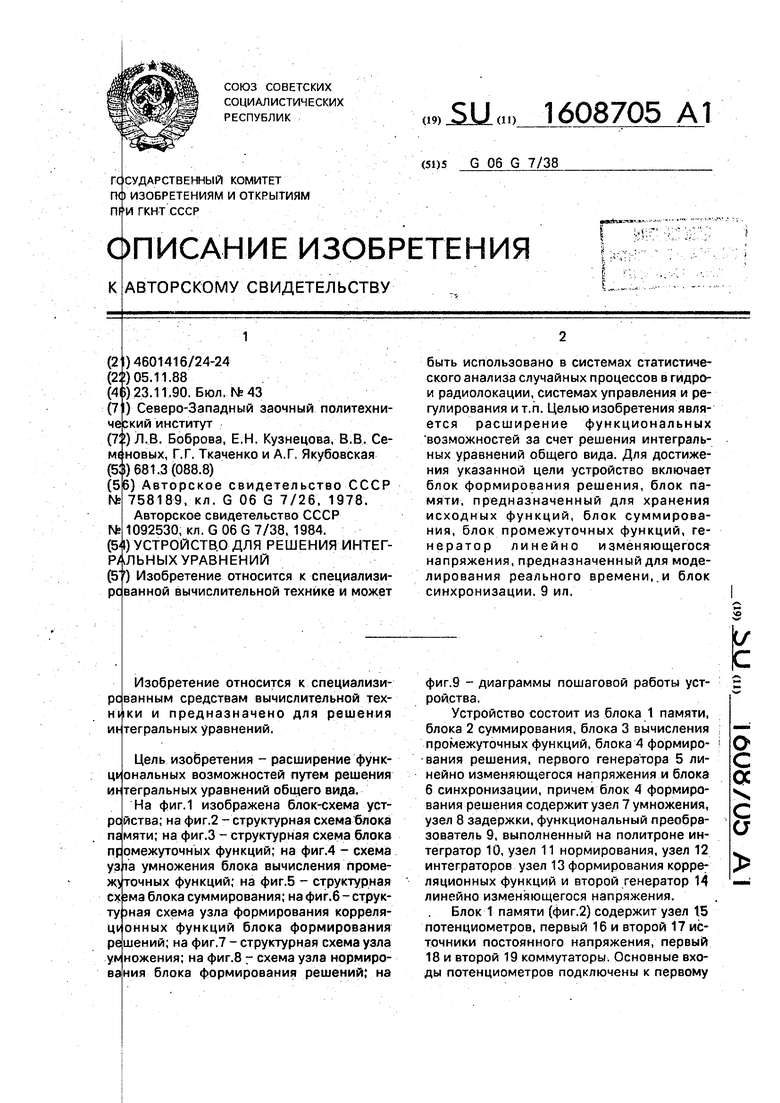

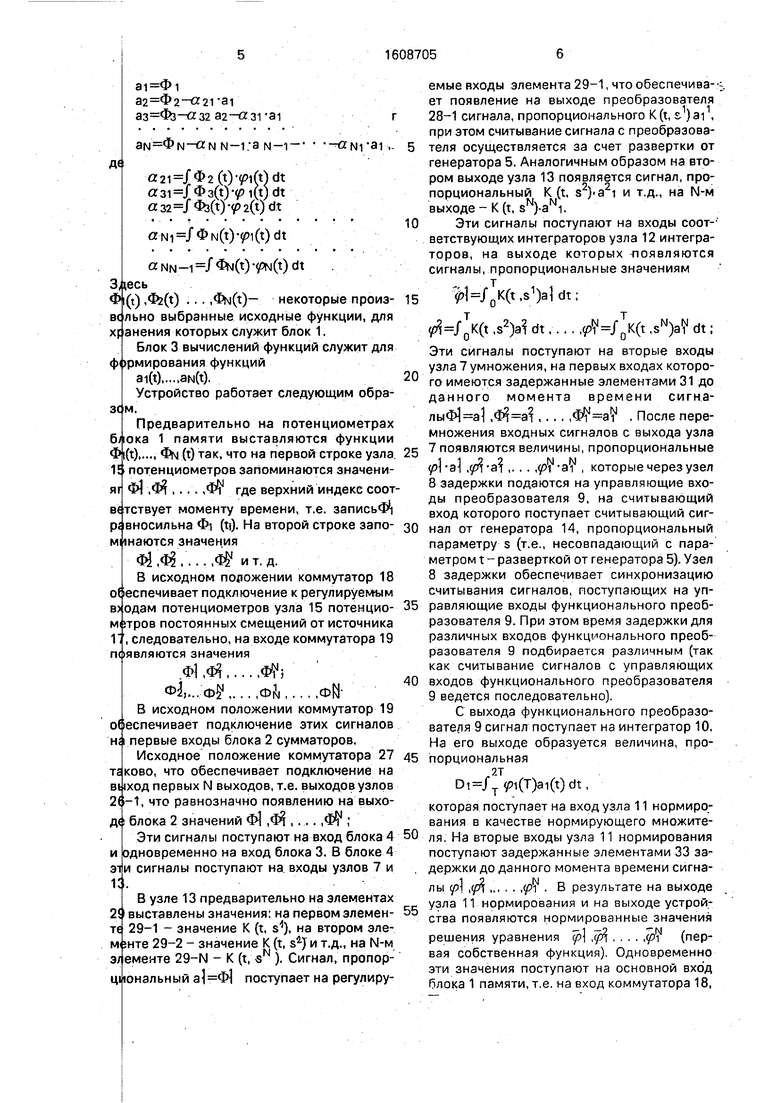

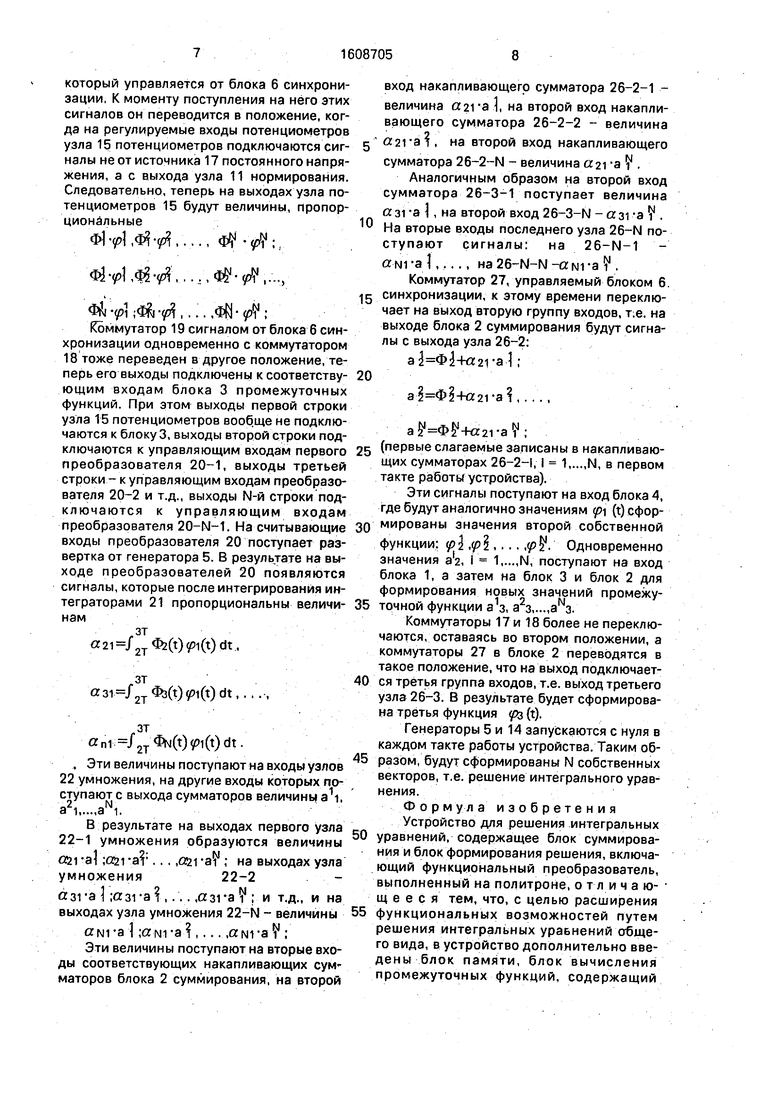

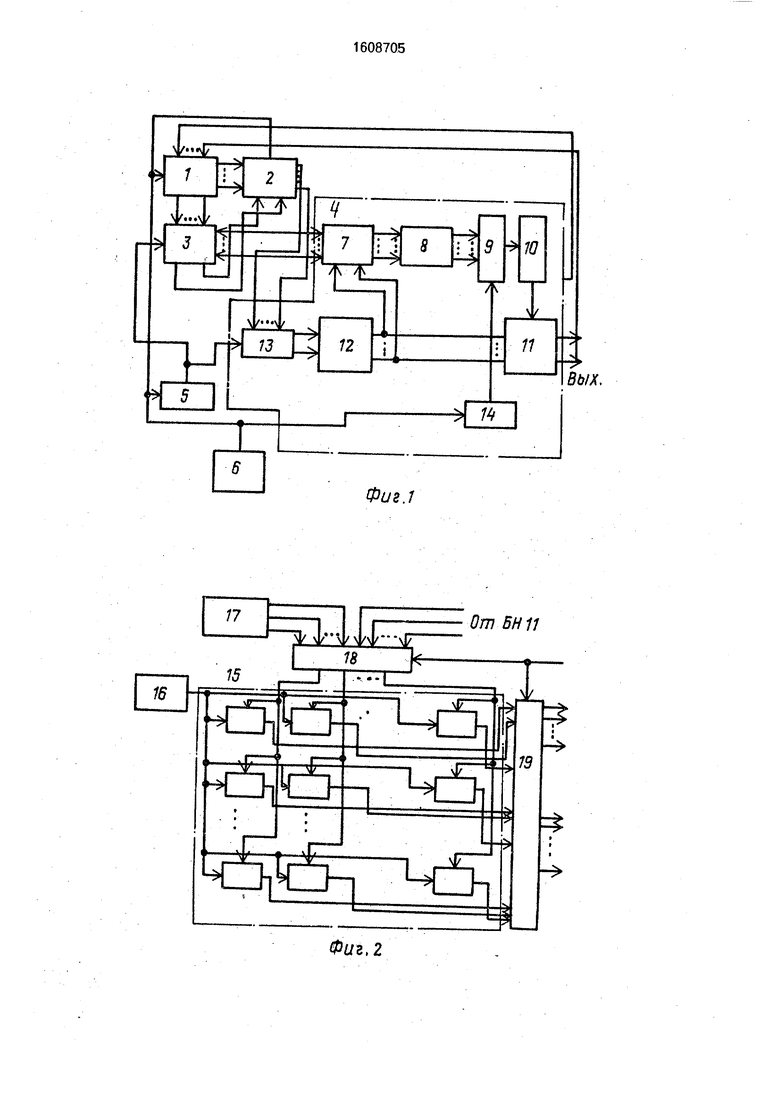

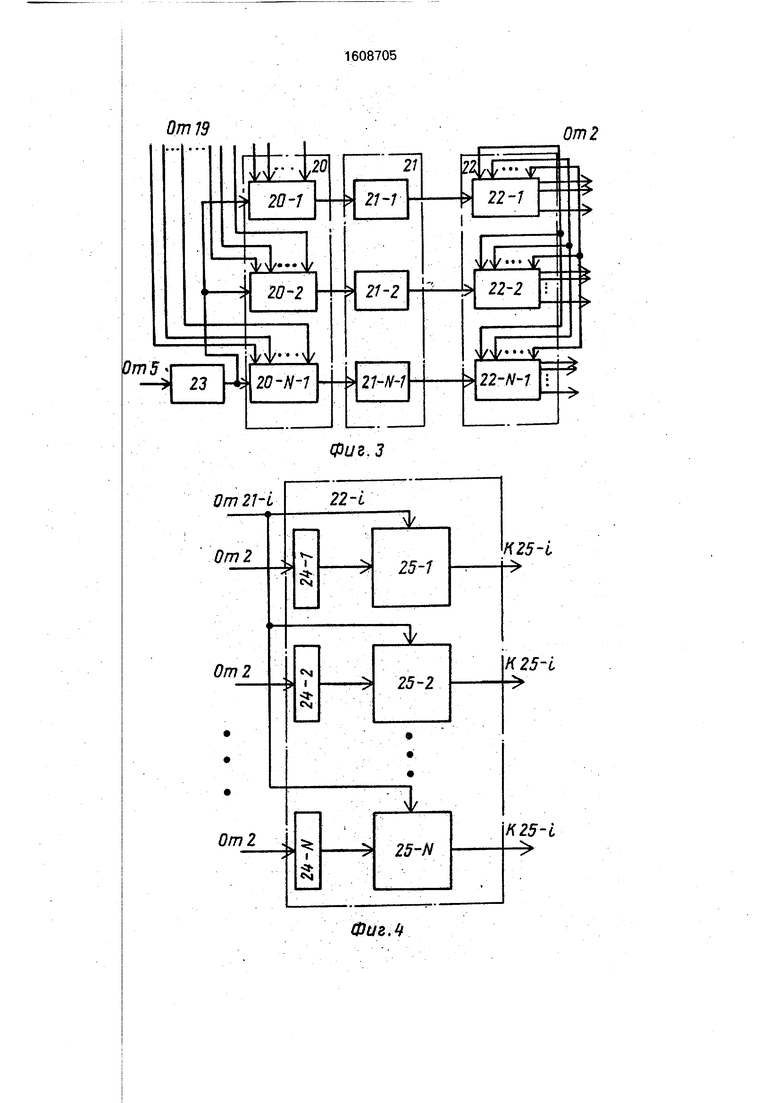

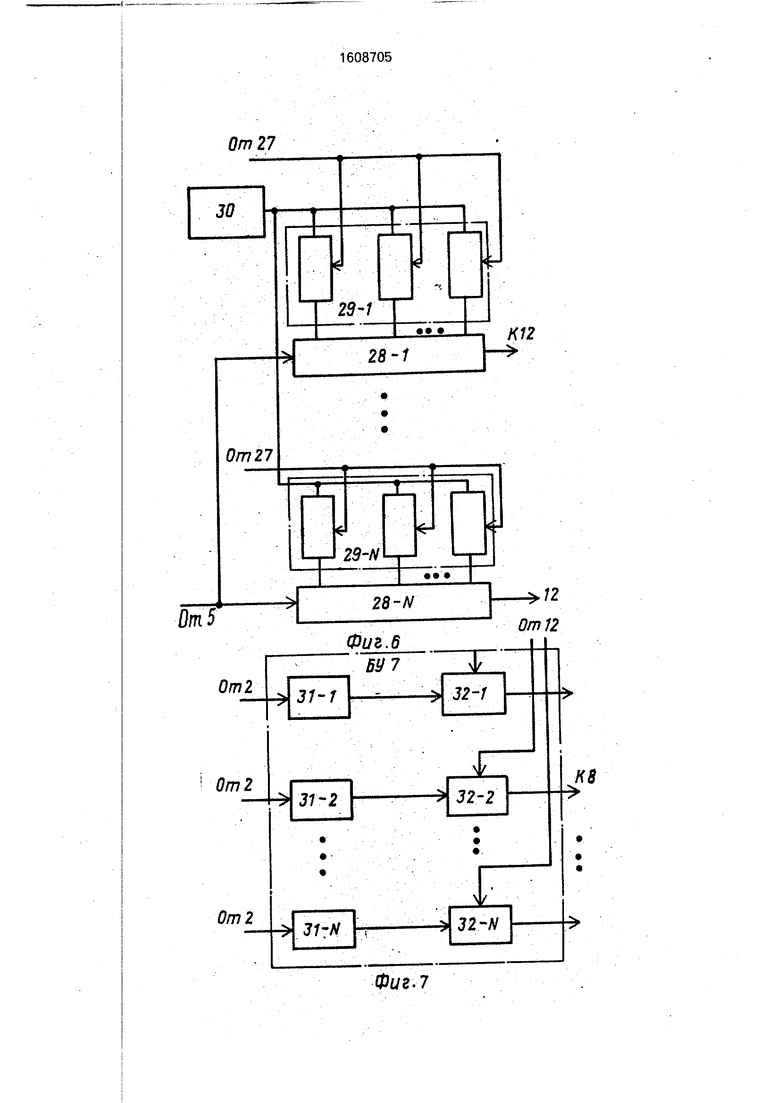

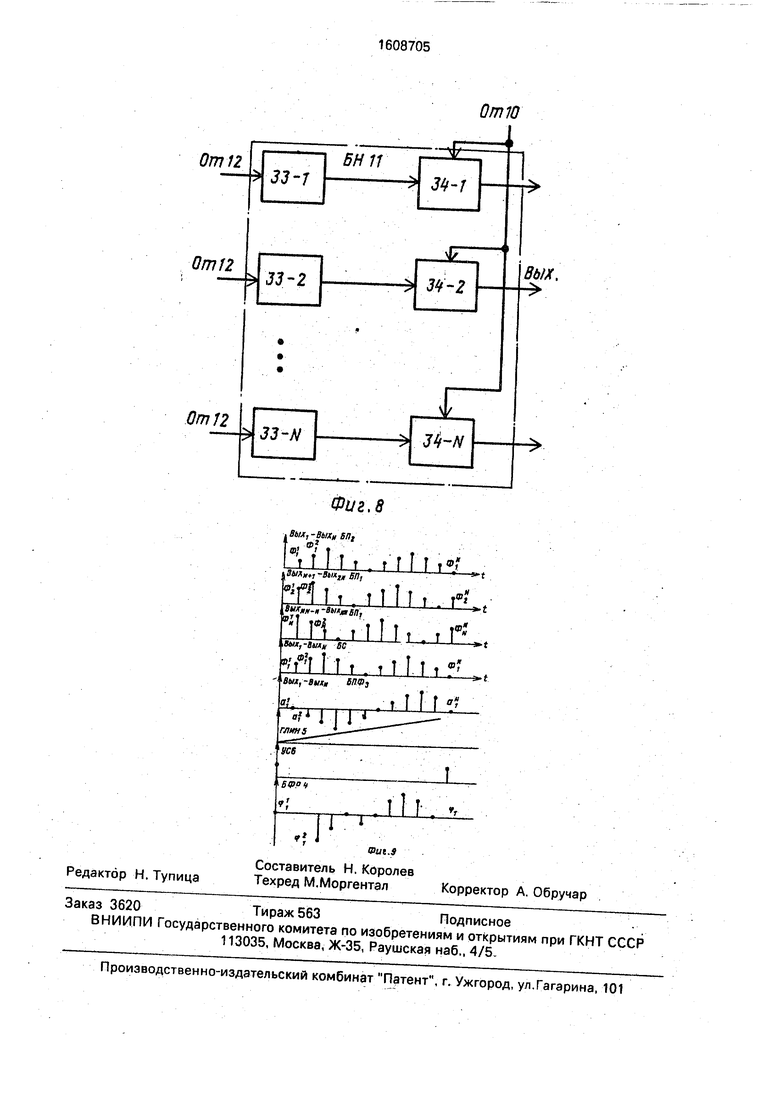

На фиг.1 изображена блок-схема устройства; на фиг.2 - структурная схема блока памяти; на фиг.З - структурная схема блока промежуточных функций; на фиг.4 - схема У31а умножения блока вычисления промежуточных функций; на фиг.5 - структурная схзма блока суммирования; нафиг.б-струк- ту )ная схема узла формирования корреля- Ционных функций блока формирования решений; на фиг.7 - структурная схема узла у ножения; на фиг.8 г схема узла нормирования блока формирования решений; на

фиг.9 - диаграммы пошаговой работы устройства.

Устройство состоит из блока 1 памяти, блока 2 суммирования, блока 3 вычисления промежуточных функций, блока 4 формирования решения, первого генератора 5 линейно изменяющегося напряжения и блока 6 синхронизации, причем блок 4 формирования решения содержит узел 7 умножения, узел 8 задержки, функциональный преобразователь 9, выполненный на политроне интегратор 10, узел 11 нормирования, узел 12 интеграторов узел 13 формирования корреляционных функций и второй генератор И линейно изменяющегося напряжения.

Блок 1 памяти (фиг.2) содержит узел 15 потенциометров, первый 16 и второй 17 источники постоянного напряжения, первый 18 и второй 19 коммутаторы. Основные входы потенциометров подключены к первому

а с а V

с а

источнику 16, а регулируемые входы объединены по столбцам и подключены к соответствующим выходам первого коммутатора 18. Выходы потенциометров группами построкам подключены к соответствующим входам второго коммутатора 19, первая группа выходов которого служит первыми выходами блока 1 памяти и связана с блоками 2 суммирования, а вторая группа выходов служит вторыми выходами блока 1 и подключена к вторым входам блока 3. Первая группа входов первого коммутатора 18 связана с соответствующими выходами второго источника 17, а вторая группа вх одов коммутатора 18 служит основным входом блока 1 и связана с выходом узла 11. Входы коммутаторов 18 и 19 объединены с выходом блока 6 и служат входом синхронизации блока 1.

Блок 3 вычисления промежуточных функций (фиг.З) состоит из (N-l)-ro функционального преобразователя 20, выполненного на политронах (например, типа ЭЛТ ЛФ9П) 20-1 - 20-N -1, (N-1)-ro интегратора 21-1 -21-N-1,(N-1)-ro узла 22-1 - 22-N-1 умножения и элемента 23 задержки. Управляющие входы преобразователя 20 связаны с выходом блока 1 и служат вторым входом блока 3, а их считывающие входы через элемент 23 объединены с выходом генератора и служат входом считывания блока 3, в то время как выходы преобразователя 20 через соответствующие интеграторы 21 связаны с первыми входами узлов 22, N вторых входов которых объединены по соответствующим группам, связанным с выходами блока 2 и служат вторыми входами блока 3, а их выходы представляют собой выходы блока 3.

Каждый узел 22-1 умножения (фиг.4) состоит из N последовательно срединенных элементов 2 --1-24-N задержки и элементов 25-1 - 25-N умножения на два входа, первые входы которых объединены и служат первым входом узла 22 умножения, а вторые входы через элементы 24 связаны с соответствующими выходами блока 2 и служат вторыми входами узла 22, при этом выходы элементов 25-1 (1 1,2N) служат выходами узла 22.

Блок 2 суммирования (фиг.5) состоит из узлов 26-1 - 26-1 суммирования. Первый узел 26-1 представляет собой N одновходо- вых накапливающих сумматоров, второй и все последующие узлы (26-2 - 26-N) состоят из N двухвхрдовых накапливающих сумматоров 26-i-1-26-l-N (I 2,3N).

При этом первые входы накапливающих сумматоров 26 являются первыми входами блока 2 суммирования и связаны с соответ

ствующими первыми выходами блока 1 (т.е., с первой группой выходов коммутатора 19), а все вторые входы накапливающих сумматоров 26 являются вторыми входами блока -5 2 и связаны с соответствующими выходами блока 3 (первая группа выходов блока 3 подключена к вторым входам узла 26-2, вторая группа - к вторым входам узла 26-3 и т.д.). Выходы узлов 26 группами подключены к 10 входам коммутаторов 27, N выходов которых служат выходами блока 2 и подключены к выходу блока 6.

Узел 13 формирования корреляционных функций (фиг.6) предназначен для запо-- 15 минания корреляционных функций вида K(t,s) и выполнен в виде N функциональных преобразователей, каждый из которых выполнен на политроне 28-1 - 28-N, входы считывания которых объединены с выходом 20 генератора 5 и служат одноименным входом узла 13, а управляющие входы связаны с запоминающими устройствами на потенциометрах 29-1 - 29-N. Основные входы по-,

тенциометров 29-1, где I 1N,

25 подключены к выходам источника 30 постоянных напряжений, а регулируемые входы связаны с соответствующими выходами блока 2 суммирования.

Выходы преобразователей 28-1, i 30 1N, служат соответствующими выходами узла 13 и связаны с входами узла 12.

Узел 7 умножения (фиг.7) состоит из N элементов 31-1 - 31-N задержки, входы которых являются первыми входами узла 7 35 умножения, а выходы связаны с первыми входами элементов 32-1 - 32-N умножения, вторые входы которых служат вторыми входами узла 7 умножения и связаны с выходом узла 12, а выходы являются выходами узла 0 7 умножения и подключены к узлу 8.

Узел 11 нормирования (фиг.8) выполнен в виде N элементов 33-1 - 33-N задержки, входы которых служат вторыми входами узла 11 нормирования, а выходы подключены 5 к первым входам соответствующих элементов 34-1 - 34-N деления, вторые входы которых объединены и служат первым входом узла 11 нормирования, а выходы являются выходами узла 11 нормирования, т.е. выхо- 0 дами устройства.

Устройство предназначено для решения интегрального уравнения с ядром K(t,s). Для моделирования ядра служит узел 13 формирования корреляционных функций.

Решение моделируется в виде 5 .(t)/K(t,s)aiCs)ds,

где a(s)-промежуточные функции, которые могут быть промоделированы следующим образом:

а2 Ф2-«21 31

аз Фз-«32 32-«31 31г

ам Фм-«м N-1;з N-1- ,. 5 (1)(От

(t)y)1(t)dt

(1)(1)61

(t)(t)dt

эти

а NN-1 (t)-fNCt) dt

Здесь

Ф|(1) (t) ... ,(t)- некоторые произ- всльно выбранные исходные функции, для xf анения которых служит блок 1.

Блок 3 вычислений функций служит для формирования функций

ai(t)ам(г).

Устройство работает следующим обра- 30м.

Предварительно на потенциометрах блока 1 памяти выставляются функции

Ф|(1) (t) так, что на первой строке узла,

1Е потенциометров запоминаются значенияг Ф ,Й ,... ,Ф где верхний индекс соответствует моменту времени, т.е. записьФ PC вносильна Ф1 (ti). На второй строке запо- минаются значен.ия

,Ф,....Ф ит.д.

В исходном положении коммутатор 18 обеспечивает подключение к регулируемым потенциометров узла 15 потенцио- MiJTpOB постоянных смещений от источника 1, следовательно, на входе коммутатора 19 появляются значения

Ф1,

Ф.Ф Ф|11,...,ФЙВ исходном положении коммутатор 19 о(|еспечивает подключение этих сигналов нз первые входы блока 2 сумматоров.

Исходное положение коммутатора 27 TalKOBO, что обеспечивает подключение на виход первых N выходов, т.е. выходов узлов 2(|-1, что равнозначно появлению на выхода блока 2 значений Ф ,Ф ,... ,Ф 1 ;

Эти сигналы поступают на вход блока 4 одновременно на вход блока 3. В блоке 4

сигналы поступают на входы узлов 7 и

и э

i:|

в узле 13 предварительно на элементах 20 выставлены значения: на первом элемен- те 29-1 - значение К (t, s ), на втором эле- Mi жте 29-2 - значение К (t, т.д., на N-M э/ементе 29-N - К (t, -s ). Сигнал, пропорциональный поступает на регулиру

0

5

0

5

о

5

5

0

0

5

емые входы элемента 29-1, что обеспечива-- ет появление на выходе преобразователя 28-1 сигнала, пропорционального K(t, . )ai , при этом считывание сигнала с преобразователя осуществляется за счет развертки от генератора 5. Аналогичным образом на втором выходе узла 13 появляется сигнал, пропорциональный К (t, s) и т.д., на Ы-м выходе-К (t, s ).

Эти сигналы поступают на входы соот- ветствующих интеграторов узла 12 интеграторов, на выходе которых появляются сигналы, пропорциональные значениям

( S)

(t ,s2)a dt,... ,(t ,s )aV dt;

Эти сигналы поступают на вторые входы узла 7 умножения, на первых входах которого имеются задержанные элементами 31 до данного момента времени сигналыФ1 а1 , ,. . . , . После перемножения входных сигналов с выхода узла

7появляются величины, пропорциональные

, , которые через узел

8задержки подаются на управляющие входы преобразователя 9, на считывающий вход которого поступает считывающий сигнал от генератора 14, пропорциональный параметру s (т.е., несовпадающий с параметром t - разверткой от генератора 5). Узел

8задержки обеспечивает синхронизацию считывания сигналов, поступающих на управляющие входы функционального преобразователя 9. При этом время задержки для различных входов функц 1онального преобразователя 9 подбирается различным (так как считывание сигналов с управляющих входов функционального преобразователя

9ведется последовательно).

С выхода функционального преобразователя 9 сигнал поступает на интегратор 10. На его выходе образуется величина, пропорциональная-Т

(T)ai(t)dt,

которая поступает на вход узла 11 нормирования в качестве нормирующего множителя. На вторые входы узла 11 нормирования поступают задержанные элементами 33 задержки до данного момента времени сигналы (р ,(f ,., . . ,(p . В результате на выходе узла 11 нормирования и на выходе устройства появляются нормированные значения

решения уравнения 1 (первая собственная функция). Одновременно эти значения поступают на основной вход блока 1 памяти, т.е. на вход коммутатора 18,

который управляется от блока 6 синхронизации, К моменту поступления на него этих сигналов он переводится в положение, когда на регулируемые входы потенциометров узла 15 потенциометров подключаются сигналы не от источника 17 постоянного напряжения, а с выхода узла 11 нормирования. Следовательно, теперь на выходах узла потенциометров 15 будут величины, пропорциональные

Ф1-И......У Vi :, ....,....,

,.:..

Коммутатор 19 сигналом от блока б синхронизации одновременно с коммутатором 18 тоже переведен в другое положение, теперь его выходы подключены к соответствующим входам блока 3 промежуточных функций. При этом выходы первой строки узла 15 потенциометров вооб.ще не подключаются к блоку 3, выходы второй строки подключаются к управляющим входам первого преобразователя 20-1, выходы третьей строки - к управляющим входам преобразователя 20-2 и т.д., выходы N-й строки подключаются к управляющим входам преобразователя 20-N-1. На считывающие входы преобразователя 20 поступает развертка от генератора 5. В результате на выходе преобразователей 20 появляются сигналы, которые после интегрирования интеграторами 21 пропорциональны величинам

зт

(t)i(t)dt,

зт (t)i(t)dt..,..

зт «п /2тФм(1)1(1)Ьг.

. Эти величины поступают на входы узлов 22 умножения, на другие входы которых поступают с выхода сумматоров величинь aS.

.

В результате на выходах первого узла 22-1 умножения образуются величины

О51 31 №1 ... , , на выходах узла умножения22-2«зга ;азга ,... ,a3ra i ; и т.д., и на выходах узла умножения 22-N - величины

аNi-a 1 ;аN1-а ,...,«N1-а ;

Эти величины поступают на вторые входы соответствующих накапливающих сумматоров блока 2 суммирования, на второй

10

вход накапливающего сумматора 26-2-1 - величина агга , на второй вход накапливающего сумматора 26-2-2 - величина 5 «21-а 7, на второй вход накапливающего сумматора 26-2-N - величина «21 -а .

Аналогичным образом на второй вход сумматора 26-3-1 поступает величина а 31 -а 1, на второй вход 26-3-N - а 31 -а V . На вторые входы последнего узла 26-N поступают сигналы: на 26-N-1 - « N1 -а 1,..., на 26-N-N -а N1 -а i .

Коммутатор 27, управляемый блоком 6. 5 синхронизации, к этому времени переключает на выход вторую группу входов, т;е. на выходе блока 2 суммирования будут сигналы с выхода узла 26-2:

а ф1-Ьа2га1 ; 0

а Ф -На:2га ,...,

а| Ф +а21;а :

5 (первые слагаемые записаны в накапливающих сумматорах 26-2-1, I 1N, в первом

такте работы устройства).

Эти сигналы поступают на вход блока 4, где будут аналогично значениям р (t) сфор0 мированы значения второй собственной

функции: ,(. Одновременно

значения а 2, I 1,...,N, поступают на вход блока 1, а затем на блок 3 и блок 2 для формирования новых значений промежу5 точной функции аЬ, аЧ...,а

Коммутаторы 17 и 18 более не переключаются, оставаясь во втором положении, а коммутаторы 27 в блоке 2 переводятся в такое положение, что на выход подключает0 ся третья группа входов, т.е. выход третьего узла 26-3. В результате будет сформирована третья функция tpz (t).

Генераторы 5 и 14 запускаются с нуля в каждом такте работы устройства. Таким об5 разом, будут сформированы N собственных векторов, т.е. решение интегрального уравнения.

Форм у л а изобретения Устройство для решения интегральных

0 уравнений, содержащее блок суммирования и блок формирования решения, включающий функциональный преобразователь, выполненный на политроне, отличаю- щ е е с я тем, что, с целью расширения

5 функциональных возможностей путем решения интегральных уравнений общего вида, в устройство дополнительно введены блок памяти, блок вычисления промежуточных функций, содержащий

элемент задержки, N-1 функциональных г реобразователей, каждый из которых вы- г олнен на политроне, N-1 интеграторов и fM узловумножения, первый генератор линейно изменяющегося напряжения и блок ( инхронизации, причем в блок формирования решения дополнительно введены узел умножения, второй генератор линейно изменяющегося напряжения, группа злемен- ов задержки, интегратор, узел формирования корреляционных функций ядер, группа интеграторов, узел нормирова- шя, включающий N элементов задержки и J делителей, причем выход каждого 1-го эле- лента задержки узла нормирования (1 1 ,...,N) подключен к первому входу каждого -го делителя узла нормирования, узел формирования корреляционных функций вклю- 4ает источник постоянного напряжения, N рупп по m потенциометров и N функциональных преобразователей, каждый из которых выполнен на политроне, первые выводы всех потенциометров объединены и юдключены к выходу источника постоянно- 0 напряжения, второй вывод каждого J-ro

потенциометра (где J 1т) 1-й группы

потенциометров (где i 1N) соединен с

-м входом каждого 1-го функционального преобразователя, N выходов узла формирования корреляционных функций ядра подключены соответственно к входам группы интеграторов, выходы которых соединены с информационными входами узла нормирования и с первыми информационными входами узла умножения, вторые информационные входы которого объединены с информационными входами узла формирования корреляционных функций ядра, выходы узла умножения через соответствующий элемент задержки группы подключены к входам функционального преобразователя, выход которого через интегратор соединен с вторыми входами делителей узла нормирования, выход второго генератора линейно изменяющегося напряжения подключен к входу считывания функционального преобразователя, выход блока синхронизации соединен с входами синхронизации блока суммирования, блока памяти, первого генератора линейно изменяю- - щегося напряжения и второго генератора линейно изменяющегося напряжения блока формирования решения, выход первого генератора линейно изменяющегося напряжения подключен к входам считывания блока промежуточных функций и входам считывания функциональных преобразователей узла формирования корреляционных

функций ядра блока формирования решения, выходы узла нормирования соединены с информационными входами блока памяти, первая группа выходов которого соединена с первой группой информационных входов

блока суммирования, каждый из N выходов которого соединен соответственно с m объединенными средними выводами каждой из N групп потенциометров узла формирования корреляционных функций ядра блока

формирования решений и с первой группой иформационных входов блока промежуточных функций, выходы которого подключены к второй группе информационных входов блока суммирования, вторая группа выходов блока памяти соединена с второй группой информационных входов блока промежуточных функций, считывающие входы функциональных преобразователей блока промежуточных функций объединены

и подключены к выходу элемента задержки блока промежуточных функций, а выход каждого 1-го функционального преобразователя (где .1 1,...,N-1) через 1-й интегратор блока промежуточных функций соединен с

первым информационным входом каждого 1-го узла умножения блока промежуточных функций, управляющие входь функциональных преобразователей блока промежуточных функций являются первой группой

информационных входов данного блока. Труппа входов узлов умножения блока промежуточных функций соответственно объединены и являются второй группой информационных входов этого блока, выходы узлов умножения блока промежуточных функций являются его выходами, а вход элемента задержки блока промежуточных функций является его входом считывания.

77

18

От BH11

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля аналоговых объектов | 1989 |

|

SU1718189A1 |

| Преобразователь напряжения в код | 1975 |

|

SU729839A1 |

| Устройство для моделирования стохастических объектов | 1984 |

|

SU1251096A1 |

| Устройство для распознавания образов | 1976 |

|

SU658579A1 |

| Устройство для сжатия информации | 1988 |

|

SU1536418A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АНАЛОГОВЫХ ОБЪЕКТОВ | 2004 |

|

RU2262128C1 |

| Устройство для вычисления нормированных статистических моментов случайных процессов | 1986 |

|

SU1385131A2 |

| Функциональный генератор | 1980 |

|

SU883931A1 |

| Управляемый вероятностный преобразователь | 1979 |

|

SU868771A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

Изобретение относится к специализированной вычислительной технике и может быть использовано в системах статистического анализа случайных процессов в гидро- и радиолокации, системах управления и регулирования и т.п. Целью изобретения является расширение функциональных возможностей за счет решения интегральных уравнений общего вида. Для достижения указанной цели устройство включает блок формирования решения, блок памяти, предназначенный для хранения исходных функций, блок суммирования, блок промежуточных функций, генератор линейно изменяющегося напряжения, предназначенный для моделирования реального времени, и блок синхронизации. 9 ил.

Фиг, 2

От 19

Фиг. 3

От 2

Фиг.

Фиг.5

От 27

30

Е

От 27

От 5

пи

Н12

28-1

28-/

72

/7/77/2

Фиг.7

Фиг, 8

Лмг,-й«4,5/7/

Г 7

SbtHxtT-BtUj, ВП,

.Su., .,

, .rlii L.

MW,-e«,jt, fi/ZflJjI

rr-r-r -.r- - LijLL.

Отю

Авторы

Даты

1990-11-23—Публикация

1988-11-05—Подача