ел

со

О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1982 |

|

SU1101872A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Анализатор спектра в ортогональном базисе | 1989 |

|

SU1615740A1 |

| Устройство для вычисления логарифмических функций | 1978 |

|

SU771672A1 |

| Анализатор спектра Фурье | 1984 |

|

SU1226486A1 |

| Устройство для обработки видеоинформации | 1990 |

|

SU1732354A1 |

| Устройство для передачи информации со сжатием | 1983 |

|

SU1091206A1 |

| ТЕЛЕВИЗИОННЫЙ АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1988 |

|

SU1623536A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1734102A1 |

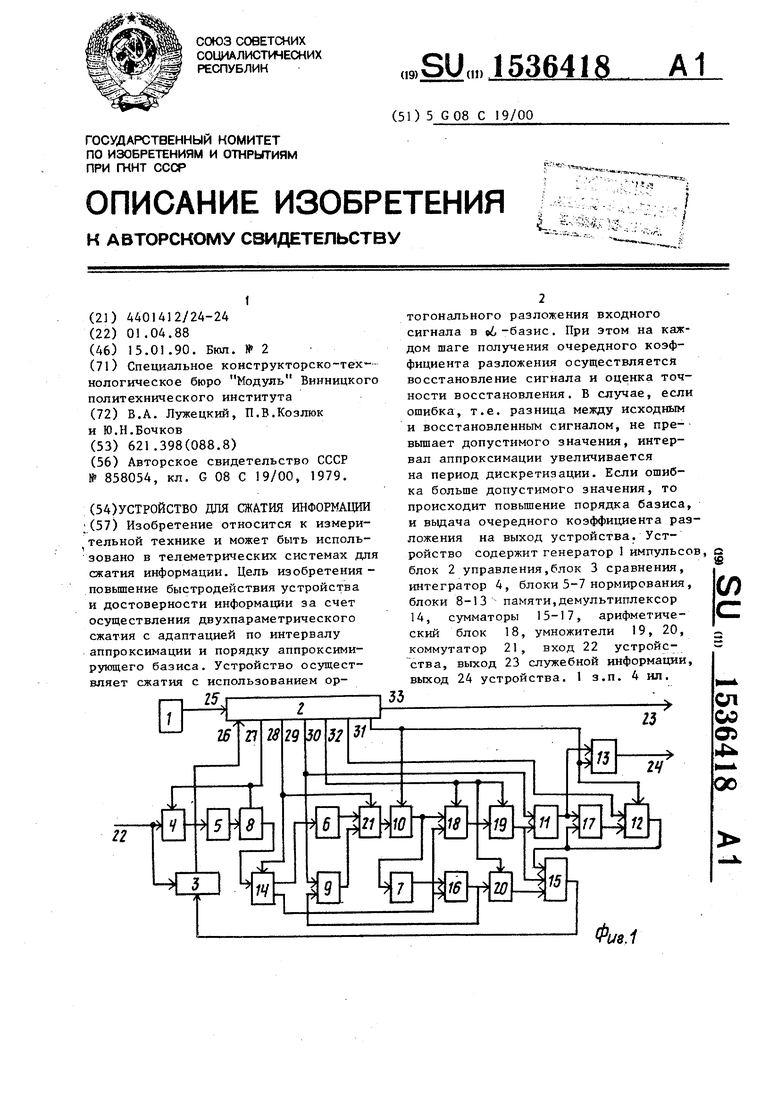

Изобретение относится к измерительной технике и может быть использовано в телеметрических системах для сжатия информации. Цель изобретения - повышение быстродействия устройства и достоверности информации за счет осуществления двухпараметрического сжатия с адаптацией по интервалу аппроксимации и порядку аппроксимирующего базиса. Устройство осуществляет сжатия с использованием ортогонального разложения входного сигнала в α = базис. При этом на каждом шаге получения очередного коэффициента разложения осуществляется восстановление сигнала и оценка точности восстановления. В случае, если ошибка, т.е.разница между исходным и восстановленным сигналом, не превышает допустимого значения интервал аппроксимации увеличивается на период дискретизации. Если ошибка больше допустимого значения, то происходит повышение порядка базиса и выдача очередного коэффициента разложения на выход устройства. Устройство содержит генератор 1 импульсов, блок 2 управления, блок 3 сравнения, интегратор 4, блоки 5, 6 и 7 нормирования, блоки 8-13 памяти, демультиплексор 14, сумматоры 15, 16, 17, арифметический блок 18, умножители 19, 20, коммутатор 21, вход 22 устройства, выход 23 служебной информации, выход 24 устройства. 1 з.п. ф-лы. 4 ил.

100

315

Изобретение относится к измерительной технике и может быть использовано в телеметрических системах для сжатия информации. „ i Цель изобретения - повышение быстродействия устройства и достоверности информации за счет осуществления двухпараметрического сжатия с адаптацией по интервалу аппроксимации и порядку аппроксимирующего базиса .

Поставленная цель достигается благодаря тому, что устройство осуществляет алгоритм двухпараметрического сжатия входного сигнала с адаптацией по интервалу аппроксимации и порядку аппроксимирующих функций на основе ортогонального разложения в об -базисе, определяемый следующим соотношением:

qiui,1 при з

;Ш

q; оС г

при 2 б i Ј i

при 3 i+1 25

при i -И j 6 N

(О де L (j) i-я функция Ј- Зазиса на 30

oi

3-м интервале времени}

ь 1,618 - иррациональное1 число, известное в литературе как золотое сечение11 или золотая пропор- 35 q. - нормировочный коэффициент,

определяемый соотношением

об

при 1 i . N

ч;

оГ при i N ,

где N - размерность базиса.

Матрица преобразования об -базиса 45 для N 5 имеет вид

лГЈ -i ооо

О О еГ 1 -1 О

ОС

оГ3 & оГ1 сГ 1 - ci 1

0

1

5

0

84

Основными свойствами данного ортогонального преобразования являктся:

1)наличие быстрого алгоритма преобразования при любой размерности базиса

2)возможность организации конвейерного режима вычисления коэффициентов разложения входного сигнала;

3)неизменность ранее вычисленных коэффициентов при добавлении новых

в процессе адаптации по порядку ортогонального разложенияi

4)очередной i-й отчет входного сигнала участвует в формировании лишь i-1-го и всех последующих коэффициентов разложения;

5)об-базис является оптимальным базисом для входного сигнала типа экспонент.

Предлагаемое устройство осуществляет вычисление коэффициентов разложения входного сигнала в соответствии с соотношением

F:

)q

(4)

s; -х,„

де Fj - i-й коэффициент разложения в ci-базис;

i-й промежуточный результат вычисления, определяемый соотношением

S-

4йС X; при i 1

35,

40

45

50

55

S S;, L + X;., при i 1 ,

(5)

где Х- - i-й интегральный отсчет

входного сигнала, определяемый выражением

Ч .

X; г ( X(t)dt,

-° i,

(6)

где Т - период дискретизации входно- ного сигнала,

t ; , с , 3 й интеРвал времени.

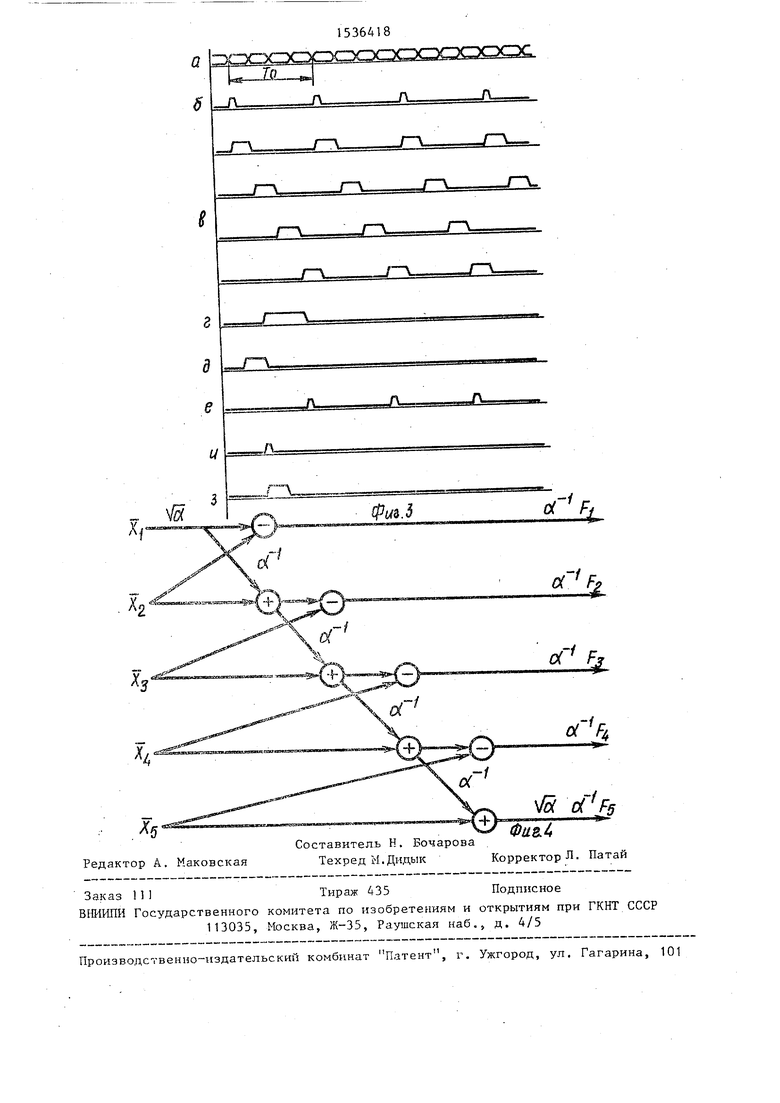

Граф вычисления для размерности базиса N 5 изображен на фиг.4.

Из соотношения (1) следует, что при увеличении размерности базиса N на единицу необходимо изменить лишь последний N-й коэффициент разложения и вычислить очередной N+1-й. Это позволяет просто осуществить переход от одной размерности базиса к другой, как следует из соотношения

1536418

ч FK при I i: k ь N-l

(FJ/-I5T -Х,)оГ при (Fk + Х() при ,

где - k-й коэффициент разложения входного сигнала в fci-базис размерности N-H .

Из соотношения (7) следует, что на каждом шаге вычисления очередного k-ro коэффициента разложения входного сигнала может быть получена оценка погрешности аппроксимации для размерности базиса, равной k. Это позволяет на каждом шаге цикла вычисления осуществлять увеличение интервала аппроксимации на величину времени, кратную Т , что по существу сводится к попытке аппроксимации входного сигнала, определенног k интегральными отсчетами k-1 функциями сб -базиса размерности k-1 при исключении из процедуры вычисления k-I-го интегрального отсчета.

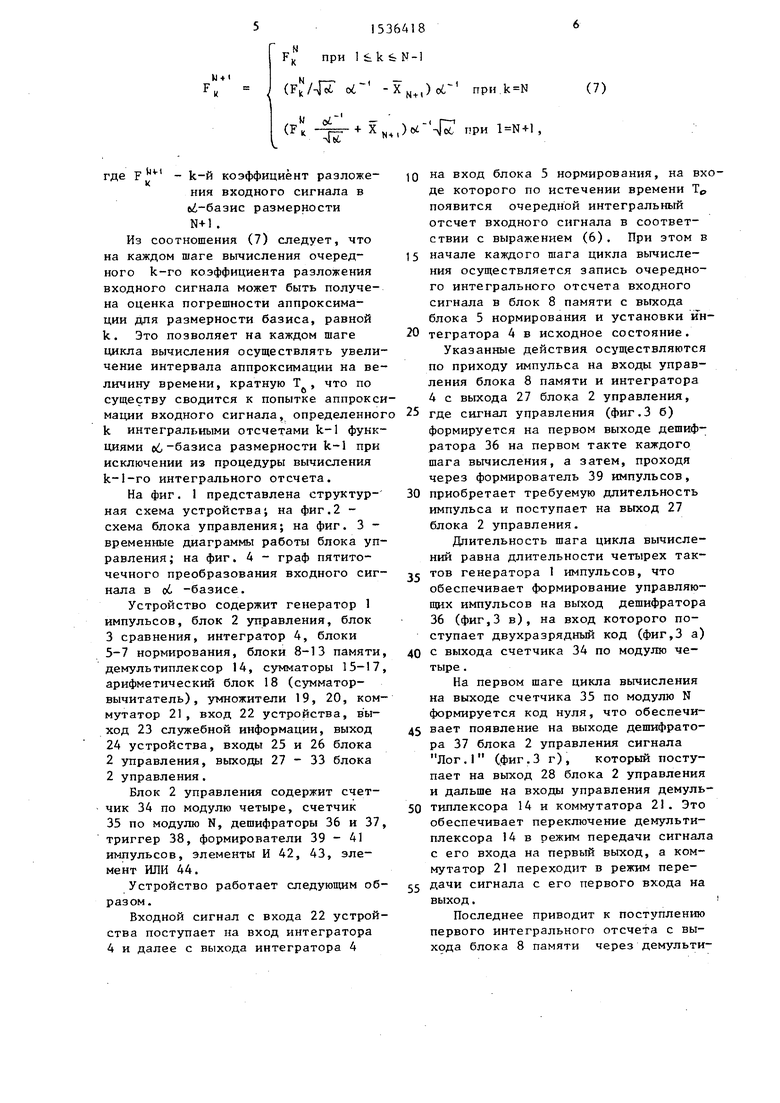

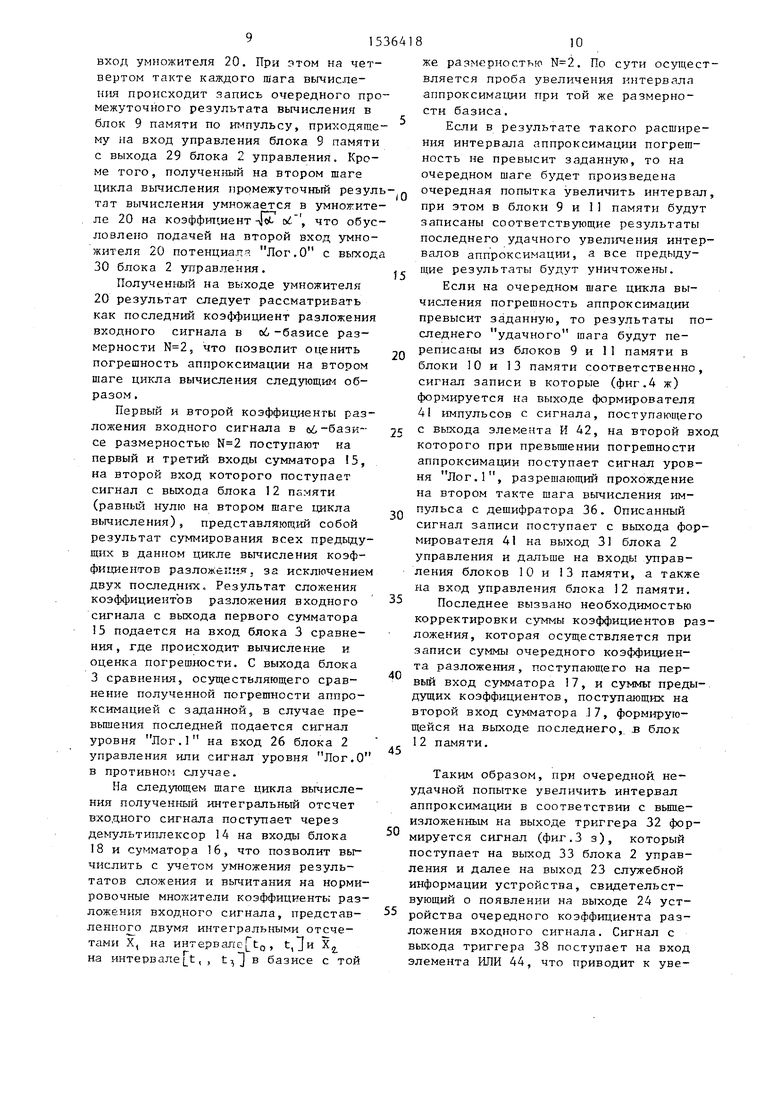

На фиг. 1 представлена структурная схема устройства; на фиг.2 - схема блока управления; на фиг. 3 - временные диаграммы работы блока управления; на фиг. 4 - граф пятиточечного преобразования входного сигнала в oi, -базисе.

Устройство содержит генератор I импульсов, блок 2 управления, блок

3сравнения, интегратор 4, блоки 5-7 нормирования, блоки 8-13 памяти, демультиплексор 14, сумматоры 15-17, арифметический блок 18 (сумматор- вычитатель), умножители 19, 20, коммутатор 21, вход 22 устройства, выход 23 служебной информации, выход 24 устройства, входы 25 и 26 блока

2 управления, выходы 27 - 33 блока 2 управления.

Блок 2 управления содержит счетчик 34 по модулю четыре, счетчик 35 по модулю N, дешифраторы 36 и 37, триггер 38, формирователи 39 - 41 импульсов, элементы И 42, 43, элемент ИЛИ 44.

Устройство работает следующим образом .

Входной сигнал с входа 22 устройства поступает на вход интегратора

4и далее с выхода интегратора 4

(7)

на вход блока 5 нормирования, на входе которого по истечении времени Т„ появится очередной интегральный отсчет входного сигнала в соответствии с выражением (6). При этом в

начале каждого шага цикла вычисления осуществляется запись очередного интегрального отсчета входного сигнала в блок 8 памяти с выхода блока 5 нормирования и установки интегратора 4 в исходное состояние.

Указанные действия осуществляются по приходу импульса на входы управления блока 8 памяти и интегратора 4 с выхода 27 блока 2 управления,

где сигнал управления (фиг.З б)

формируется на первом выходе дешифратора 36 на первом такте каждого шага вычисления, а затем, проходя через формирователь 39 импульсов,

приобретает требуемую длительность импульса и поступает на выход 27 блока 2 управления.

Длительность шага цикла вычислений равна длительности четырех тактов генератора 1 импульсов, что

обеспечивает формирование управляющих импульсов на выход дешифратора 36 (фиг.З в), на вход которого поступает двухразрядный код (фиг,3 а)

с выхода счетчика 34 по модулю четыре .

На первом шаге цикла вычисления на выходе счетчика 35 по модулю N формируется код нуля, что обеспечивает появление на выходе дешифратора 37 блока 2 управления сигнала Лог.1 (фиг.З г), который поступает на выход 28 блока 2 управления и дальше на входы управления демультиплексора 14 и коммутатора 21. Это обеспечивает переключение демульти- плексора 14 в режим передачи сигнала с его входа на первый выход, а коммутатор 21 переходит в режим передачи сигнала с его первого входа на выход.

Последнее приводит к поступлению первого интегрального отсчета с выхода блока 8 памяти через демультиплекгор 14 на вход блока 6 нормирования , где происходит умножение первого интегрального отсчета на коэффициент 4

Таким образом, на выход блока 6 поступает первый промежуточный ре- чультпт вычисления в соответствии с выражением (5) .

С выхода блока 6 первый промежу- точный результат вычисления через коммутатор 21 поступает на вход блока 10 памяти.

Запись первого промежуточного результата вычисления в блок 10 памяти осуществляется по приходу на его управляющий вход сигнала с выхода 31 блока 2 управления. Формирование данного сигнала п блоке 2 управления происходит при поступлении с выхода блока 3 сравнения на второй вход блока 2 управления сигнала превышения заданной погрешности аппроксимации (фиг.З д). Этот сигнал поступает на информационный вход триггера 38, на вход тактирования которого на втором такте шага вычисления поступает сигнал с дешифратора 36, что осуществляет установку триггера 38 в единичное состояние, разрешающее прохож денче импульса дешифратора 36 через элемент И 42 на вход формирователя 41 импульсов и дальше на выход 31 блока 2 управления.

Установка триггера 38 в исходное состояние осуществляется на третьем такте шага вычисления при поступлении на установочный вход триггера 38 сигнала уровня Лог.1 дешифратора 36

Кроме того, на первом шаге цикла вычисления сигнал уровня Лог.1 поступает с дешифратора 37 на вход элемента И 43, что разрешает прохождение импульса с дешифратора 36 через элемент И 43 на выход 32 блока 2 уп- равления. В свою очередь импульс, поступивший на четвертом такте первого шага цикла вычисления с выхода 32 блока 2 управления на вход управления элемента 12, устанавливает его в О, а поступление этого сигнала на вход элемента ИЛИ 44 и дальше на вход счетчика 35 по модулю N устанавливает его в единицу, что приводит к появлению на первом выходе дешифратора сигнала уровня Лог.О. Последнее приводит к установке де- мультиплексора 14 в режим передачи сигнала с входа на его второй выход,

$ 0 5 о

Q 5 -.

5

5

а коммутатора - в режим поррдпми сигнала с его второго входа на выход. Это обеспечивает на втором шаге цикла вычисления поступление второго интегрального отсчета, полученного по описанной выше процедуре, через демультиплексор 14 на входы суммато- ра-вычитателя 18 и сумматора 16. При этом на вход управления суммятора- вычитателя 18 поступает сигнал уровня Лог.О с выхода 30 блока 2 управления, формирующийся на втором выходе второго дешифратора 37, что переводит арифметический блок 16 в режим вычитания сигнала, поступающего на его второй вход, из сигнала, поступающего на его третий вход.

Очевидно, что на выход блока 18 в результате подачи на его третий вход первого промежуточного результата вычисления поступает значение выражения заключенного в скобки соотношения (4), а именно: ненормированный первый коэффициент разложения входного сигнала воЈ-базисе, нормировка которого и осуществляется в умножителе 19. Поступление на первый вход умножителя 19 сигнала уровня Лог.О с выхода 30 блока 2 управления переводит умножитель 19 в режим умножения сигнала, поступающего на второй вход, на , т.е. в соответствии с выражением (2).

С выхода умножителя 19 сигнал, пропорциональный первому коэффициенту разложения, записывается в блок 11 памяти, на вход управления которого поступает импульс -записи (фиг.З е) с выхода 29 блока управления. Сигнал управления формируется на выходе формирорателя 40 импульсов на четвертом такте каждого шага вычисления, что обусловлено соединением входа формирователя 40 импульсов с четвертым выходом первого дешифратора 36.

На выходе сумматора 16 формируется значение второго промежуточного результата вычисления в соответствии с выражением (5), при этом на первый вход второго сумматора 16 поступает промежуточный результат вычисления, полученный на первом шаге цикла вычисления и умноженный в блоке 7 на коэффициент .

Полученный промежуточный результат вычисления с выхода сумматора 16 поступает на вход блока 9 памяти и на

415

вход умножителя 20. При ч т ом на четвертом такте каждого :ьага вычиспе- пия происходит апись очередного промежуточного результата вычисления в блок Q памяти по нчпульсу, приводящему на вход управления блока 9 памяти с выхода 29 блока 2 управления. Кроме того, полученный на втором шагз цикла вычленения промежуточный резул тат вычисления умрожтется в умножителе 20 на коэффициент of , что обусловлено подл чей на второй вхоч умножителя 20 потенцисТ- Лог.О с выход 30 блекл 2 уг равнения.

Полученный на вкходе умнгжител 20 результат следует рассматривать как последний коэффициент разложения входного сигнала в об -базисе размерности , что позволит оценить погрешность -шпрсксимацни на втором шаге цикла вычисления следующим образом .

Первый и второй коэффициенты газ- ложения входного сигнала р ьб-бази- се размерностью поступают на первый и третий входы сумматора 5, на второй вход которого поступает сигнал с выхода блока 1 2 п. -(яти Сравним нулю на втором шат-е цикла вычисления), представляющий собой результат суммирования всех предыду- щн--- в данном цикпе вычисления коэффициентов разпо е;:: я. за исключением двух последних. Результат сложения коэффициентов разложения входного сигнала с выхода первого сумматора 15 подается на вход блока 3 сравнения, где происходит вычисление и опенка погрешности. С выхода блока 3 сравнения, осуществляющего срав- ненне полученной погрешности аппроксимацией с заданном, в глучас пре- пьпчения последней подается сигнал уровня Лог.1 на вход 26 блока 2 управления или нгнал уровня Лог.О в противно случае.

На следующем mare никла вычисления полученный интегральный отсчет входного сигнала поступает через

дгмулитиплсксор I 4 на входы блокл

IS и сумматора 6, что позволит вычислить с учетом умножения результатов сложения и вычитания на нормировочные множители коэффициенты раз- лож чия входного сигчмла, представ- пенного двумя интеграчьнымн отсче- Ч, на интернат i t0 , t, и Х нэ 4HTepB,,j e (t, , t-, в базисе с той

15

0

41;

,.

5 5

0

5

0

5

10

же ратмерностью . По сути осуществляется проба увеличения интервала аппроксимации при той же размерности базиса.

Если в результате такого расширения интервала аппроксимации погрешность не превысит заданную, то на очередном шаге будет произведена очередная попытка увеличить интервал, при этом в блоки 9 и 11 памяти будут записаны соответствующие результаты последнего удачного увеличения интервалов аппроксимации, а все предыдущие результаты будут уничтожены.

Если на очередном шаге цикла вычисления погрешность аппроксимации превысит заданную, то результаты последнего удачного шага будут переписав из блоков 9 и 11 памяти в блоки 10 и 13 памяти соответственно, сигнал записи в которые (фиг.4 ж) формируется нз выходе формирователя 41 импульсов с сигнала, поступающего с выхода элемента И 42, на второй вход которого при превышении погрешности аппроксимации поступает сигнал уровня Лог.1, разрешающий прохождение на втором такте шага вычисления импульса с дешифратора 36. Описанный сигнал записи поступает с выхода формирователя 41 на выход 31 блока 2 управления и дальше на входы управления блоков 10 и 13 памяти, а также на вход управления блока 12 памяти.

Последнее вызвано необходимостью корректировки суммы коэффициентов разложения, которая осуществляется при записи суммы очередного коэффициента разложения, поступающего на первый вход сумматора 17, и суммы предыдущих коэффициентов, поступающих на второй вход сумматора 17, формирующейся на выходе последнего, .в блок 12 памяти.

Таким образом, при очередной неудачной попытке увеличить интервал аппроксимации в соответствии с выше- изложеыЈым на выходе триггера 32 формируется сигнал (фиг.3 з), который поступает на выход 33 блока 2 управления и далее на выход 23 служебной информации устройства, свидетельствующий о появлении на выходе 24 устройства очередного коэффициента разложения входного сигнала. Сигнал с выхода триггера 38 поступает на вход элемента ИЛИ 44, что приводит к увеличеннп подсудимого счетчика 35 по гнлул) Ц па единицу.

Когда колимес г- о неудачных попыток превысит N-1 , на втором выходе дешиф- рптора 37 будет сформирован сигнал уровня Лог.1, который переключит умножитель 19 в режим умножения входного сигнала на коэффициент of -Jot , а умножитель 20 - в режим умножения на 0, что позволит сформировать последит N-й коэффициент разложения на выходе умножителя 19. N-я неудачная попытка увеличить интервал ап- прокспмацни приведен к выводу послед- него коэффициента разложения на выход 24 устройства и установке содержимого счетчика 35 по модулю N в О поело чего будет осуществлен очередной цикл вычисления.

Максимальная задержка поступления на выход устройства очередного 1-го коэффициента разложения входного сигнала по отношению к Бремени поступления г i вход устройства 1-го инте- трального отсчета составит при отсутствии сжатия

Ч 1 5 То

В то же гремя дЛя прототипа эта задержка составит

Сп™ NTo

что Б 2/1N раз больше, чем для заявляемого устройства.

KPOV.C того, лосу-оверпоотт- информации, передаваемой на выход устройства, для устройства-прототипа определяется величиной погрешности, вносимой аппаратными средствами и :ип о- ритмической погрешностью, причем, как сказано выше, последгчя значительно превосходит аппагк-м ну-о. ,Пля предлагаемого устройств.i алгоритмическая погрешность отсутствует.

Формула изобретения

входом блока управления, первый выход которого соединен с першл-i входом интегратора, блок сравнения, выход которого соединен с вторым входом блока управления, второй в т/сод которого соединен с первым PXO.IJMM первого умножителя, первым сумм,imp, выход которого соединен с первым

Q

,

о 5

0

входом блока сравнения, отличающееся тем, что, г целью повышения достоверности информации и быстродействия устройства, в него введены второй и третий сумматоры, коммутатор, блоки памяти, блоки нормирования, второй умножитель, демуль- типлексор и арифметический блок, первый вход которого и первый вход первого блока памяти подключены соответственно к второму и первому выходам блока управления, третий выход которого соединен с первыми входами коммутатора и демультиплексора, второй вход которого подключен к выходу первого блока памяти, выход интегратора через первый блок нормирования соединен с вторым входом первого блока памяти, первый выход демультиплексора через второй блок нормирования соединен с вторым входом коммутатора, выход которого соединен с первым входом второго блока памяти, выход которого соединен непосредственно с вторым входом арифметического блока и через третий блок нормирования с первым входом второго сумматора, , второй выход демультиплексора соединен с вторым входом второго сумматора и третьим входом арифметического блока, выход которого соединен с вторым входом первого умножителя ,выход которого соединен с первыми входами первого сумматора и третьего блока памяти, выход которого соединен с первыми входами четвертого блока памяти и третьего сумматора, выход которого соединен с первым входом пятого элемента памяти, выход которого соединен с вторыми входами первого и третьего сумматоров, выход второго гумматора соединен с первыми входами utcToro блога памяти и второ:г умножителя, второй вход и выход которого подключены соответственно к второму ьиходу блока управления и третьему входу первого сумматора, четвертый ьыход блока управления соединен с вторыми входами третьего блока памяти и шестого блока памяти, выход которого соединен с третьим входом коммутатора, пчтый и шестой выходы блока управления соединены соответственно с вторыми входами второго, четвертого и пятого б;к. ов памяти и третьим входом пятого блока памяти, вторые вхо- лы интегратора и блока сравнения объединены и являются входом устройства, выход четвертого блока памяти и седьмой выход блока управления являются соответственно первым и вторы -1 выходами устройства.

мента ИЛИ и вторым входом первого элемента И, выход которого соединен с входом третьего формирователя импульсов, выход элемента ИЛИ соединен с входом второго счетчика, выходы которого соединены с входами второго дешифратора, первый выход которого соединен с вторым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ, вход первого счетчика и третий вход триггера являются соответственно первым и вторым входами блока, выход первого формирователя импульсов, второй и первый выходы второго дешифратора, выходы второго и третьего формирователей импульсов, выход второго элемента И и выход триггера являются соответственно первым - седьмым выходами блока.

Фиг.2

г

J

/-

5

fo oCfF5

Фй&Јф

Составитель 1. Бочарова

Редактор Л. Маковская Техред И.Дндык Корректор Л. Патай

Заказ 111Тираж 435Подписное

ВШИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб,, д. 4/5

jv

Ј3

JZ

.гл.

/ZV

n

n

fo oCfF5

| Устройство для передачи информации со сжатием | 1979 |

|

SU858054A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1990-01-15—Публикация

1988-04-01—Подача