выход соединен с первым входом выходного элемента И положительных приращений и с первым входом выходного элемента И отрицательных приращений, вторые входы которых соединены соответственно с выходами положительного и отрицательного приращения интеграла цифрового интеграторе, а выходы с выходами положительных и отрицательных приращений процессора соответственно, единичный выход каждого разряда -го регистра адреса входных приращений группы со- дашен с первой группой входов -го блока сравнения адресов входных приращений группы, вторая группа входов которого соединена с группой единичных выходов счетчика тактов, а выход i -го блока сравнения адресов входных приращений группы соединен с первым входом -го входного элемента И положительных приращений группы и с первым входом а-го входного элемента И отрицательных приращений группы, втоpbie входы которых соединены соответственно с входом положительных приращений модуля и с входом отрицательных приращений модуля, а выходы соединены соответственно с единичным входом 1 -го триггера положительных приращений и с единичным входом 1 -го триггера отрицательных приращений группы, единичные выходы которых соединены соответственно с i-ми входами из групп входов положительных и отрицательных значений входных приращений цифрового интегратора, группа входов неполного дешифратора соединена с группой единичных выходов счетчика тактов, выходы состояния (N+1) (где N - количество модулой в интегрирующей вычислительной структуре), состояния (N +гп-1) и состояния (N+m+1) неполного дешифратора (где In - количество разрядов в регистре подынтегральной функции цифрового интегратора) соедине,ны соответственно с первьпч, вторым и третьим входами группы тактовых

1821

JBXo;tOB формирователя y итeльнocти HNmynbcoB, нулевой вход каждого триггера положительных приращений группы и каждого триггера отрицательных приращений группы соединен с выходом элемента ИЛИ, второй вход которого соединен с выходом состояния (t +tri+l) неполного дешифратора, выходы сигнала длительностью f тактов и сигнала длительностью (№-2) тактов формирователя длительности импульсов и выход состояния (},1 + П1+1) неполного дешифратора соединены соответственно с входом сигнала разрешения вычислений, с входом сигнапа выделения остатка интеграла и с входом сигнала конца итерации цифрового интегратора, счетный вход счетчика тактов подключен к входу разрешения счета модуля, а выход состояния (К+м+1) неполного дешифратора соединен также с выходом контроля тактов модуля.

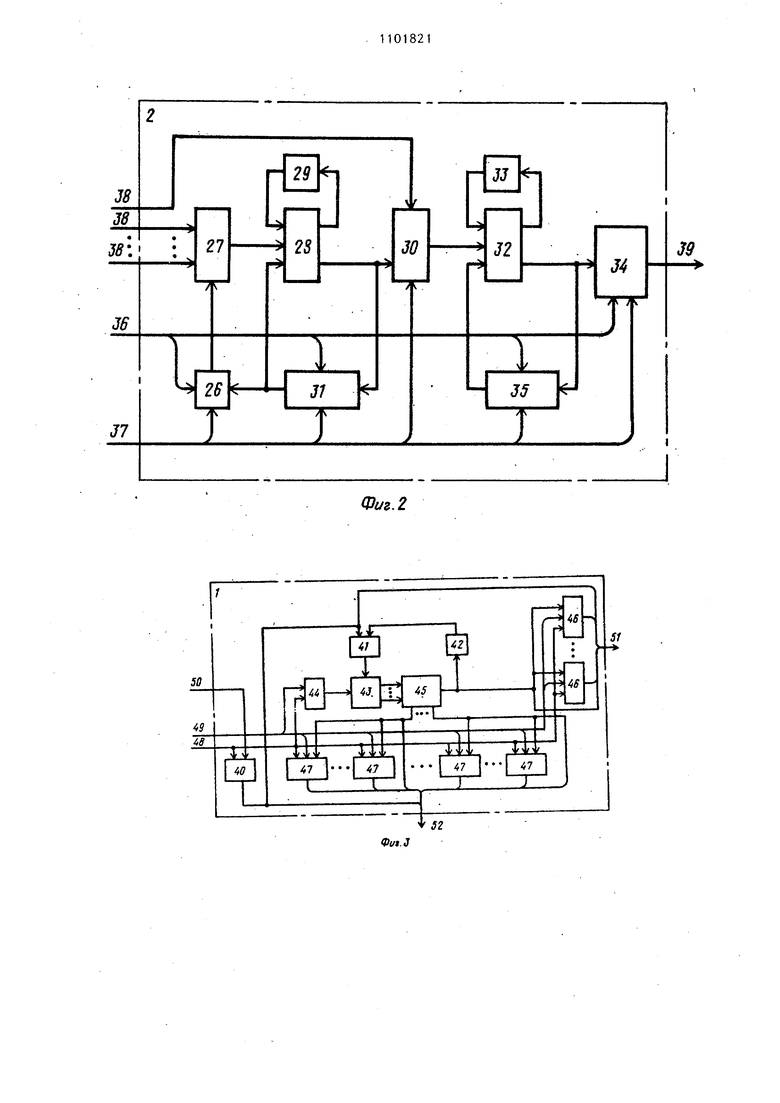

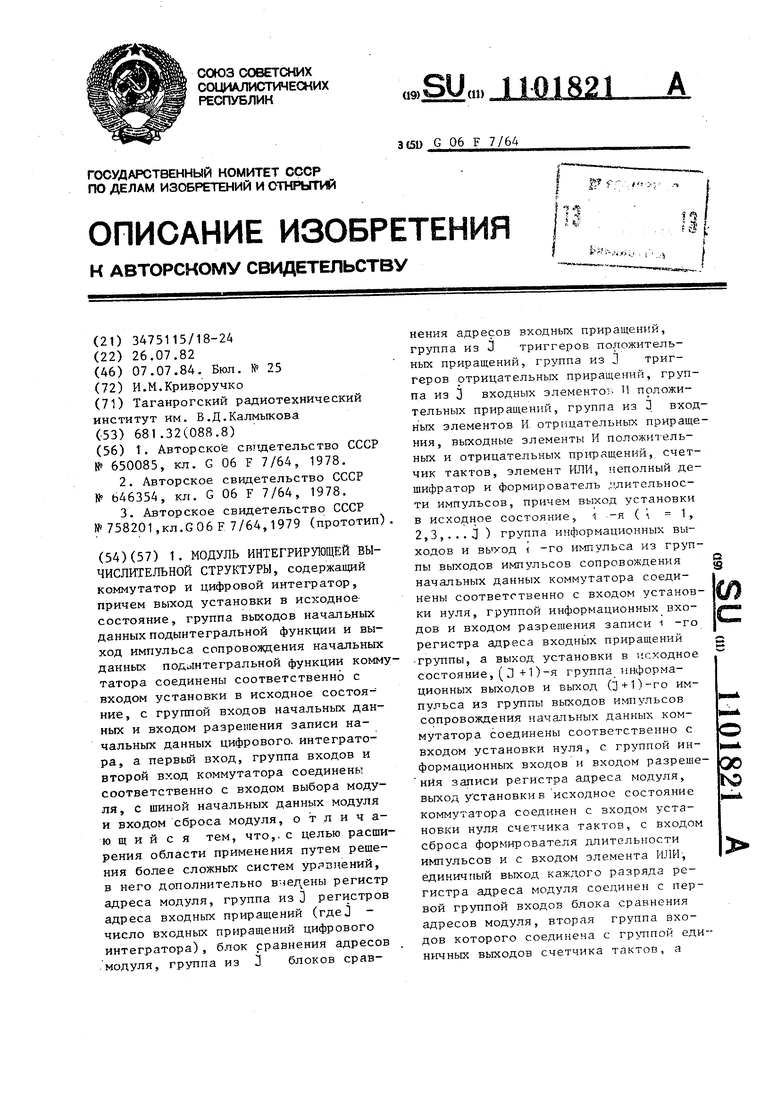

2. Модуль по п. 1,отличающ.и и с я тем, что формирователь длительности импульсов содержит два элемента ИЛИ и два триггера, причем выход первого элемента ИЛИ и выход второго элемента ИЛИ соединены соответственно с нулевым входом первого триггера и с нулевым входом второго триггера, первые входы первого элемента ИЛИ и второго элемента ИЛИ соединены с входом сброса формирователя, первый вход из группы тактовых входов фор шрователя соединен с единичными входами первого и второго триггеров, единичные вькоды которых соединены соответственно с выходом сигнала длительностью m тактов и с выходом сигнала длительностью (т-2) такта формирователя, вторые входы второго элемента ИЛИ и первого элемента ИЛИ соединены соответственно -с вторым и третьим входами из группы тактовых входов формирователя, первьй вход из группы тактовых входов формирователя соединен с единичными входами первого и второго триггеров .

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Устройство для диагностики неисправностей цифровых интеграторов | 1979 |

|

SU877551A1 |

| Устройство цифрового интегрирования | 1988 |

|

SU1532922A1 |

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

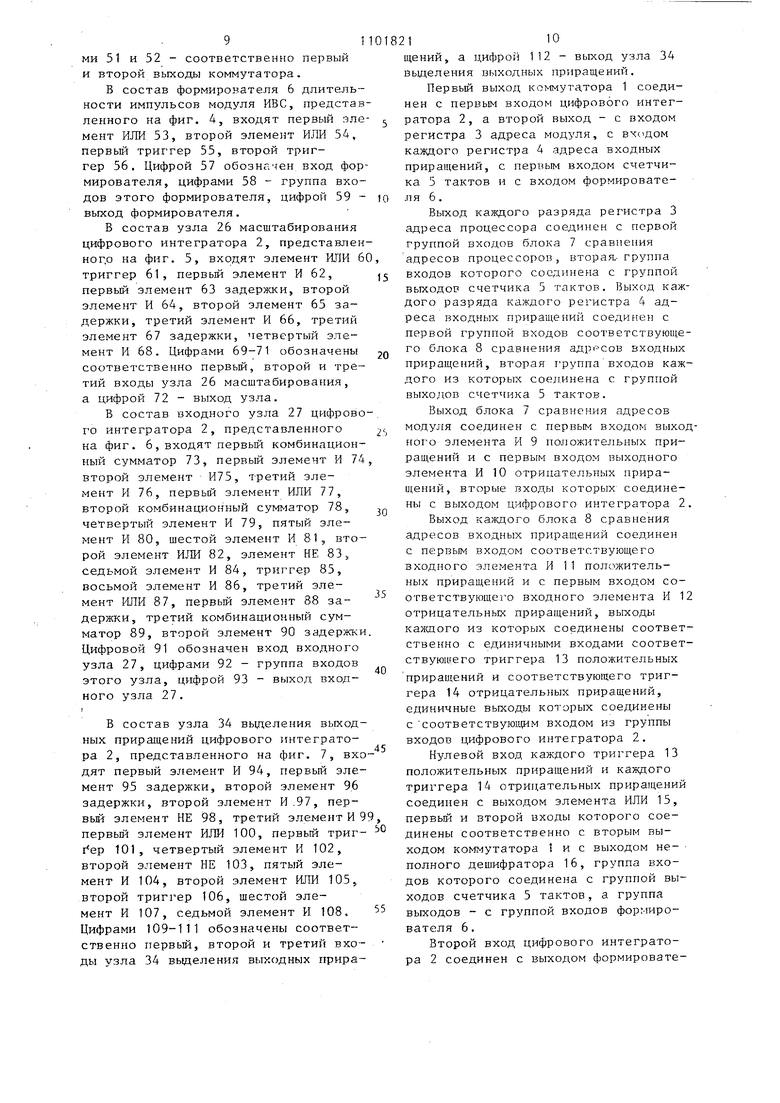

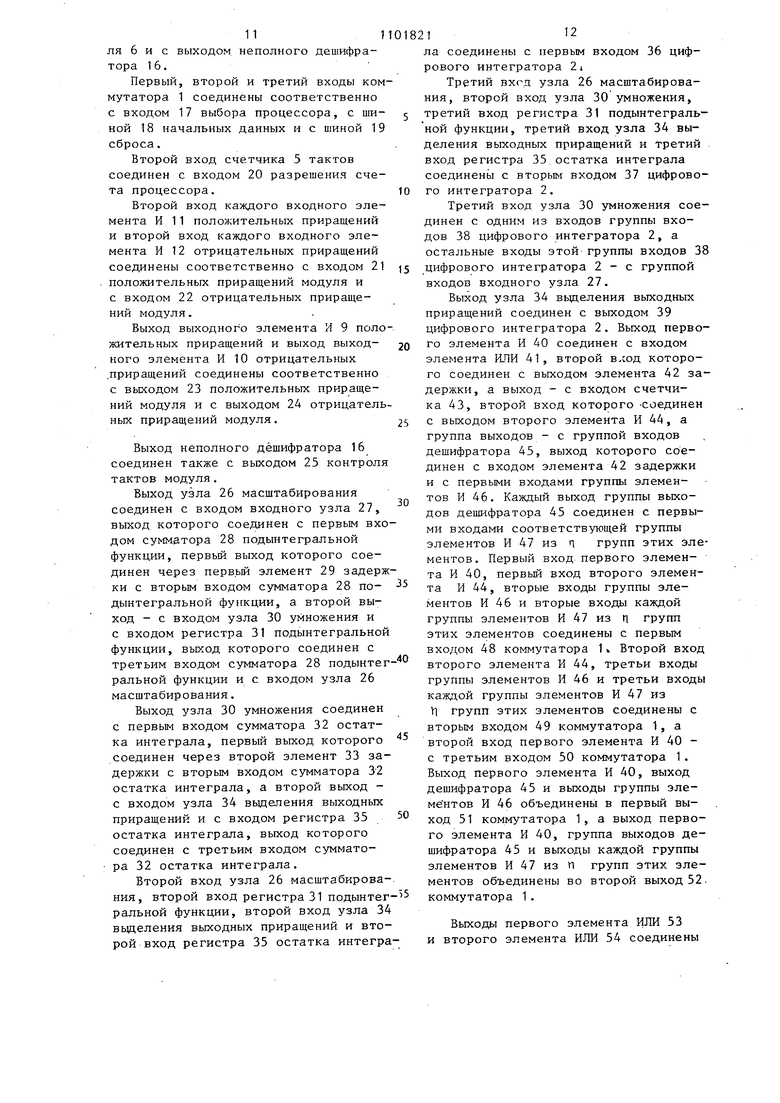

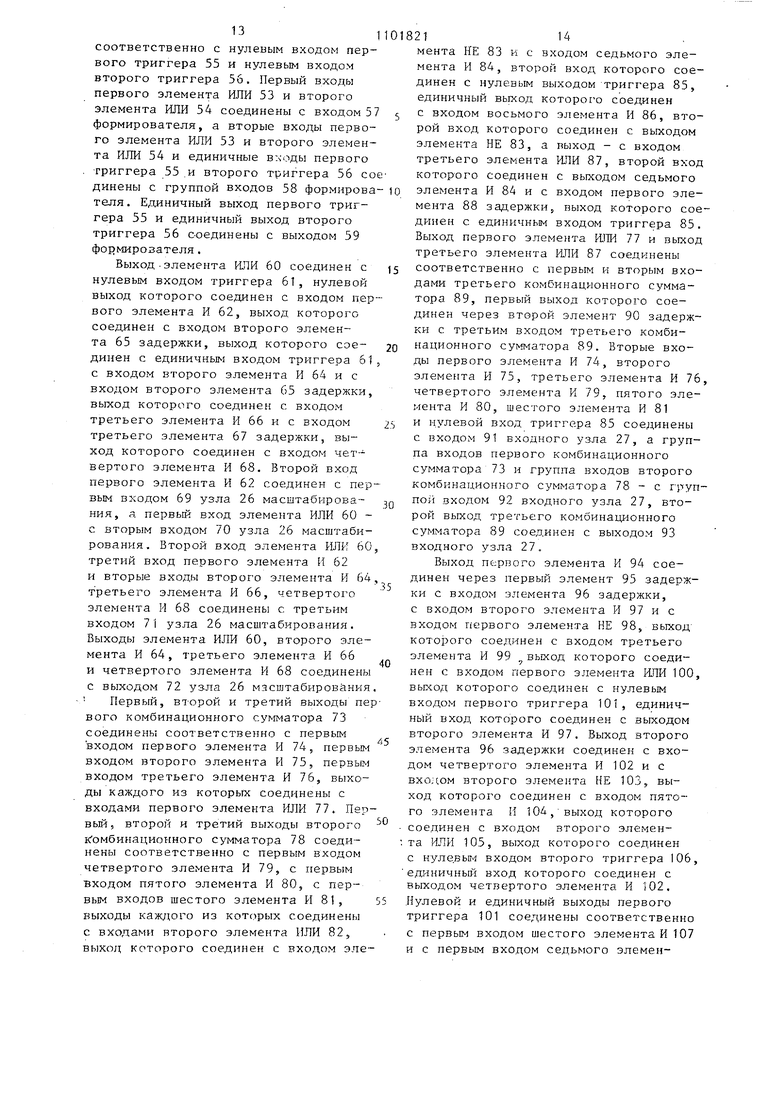

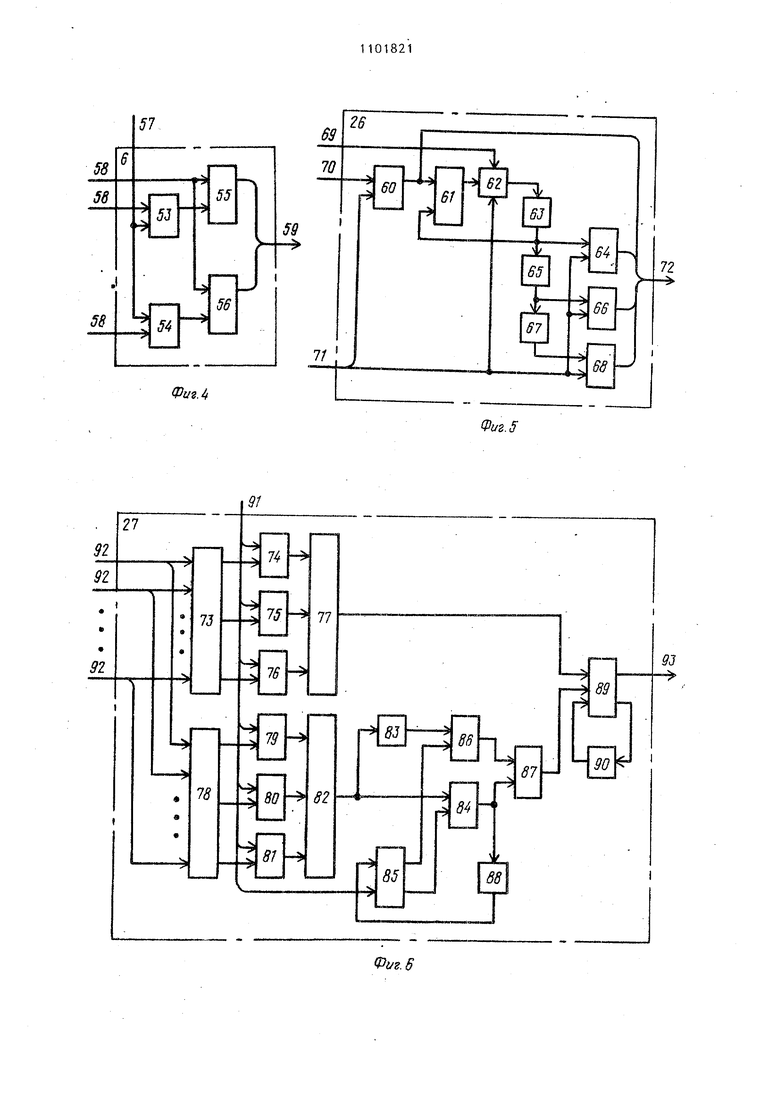

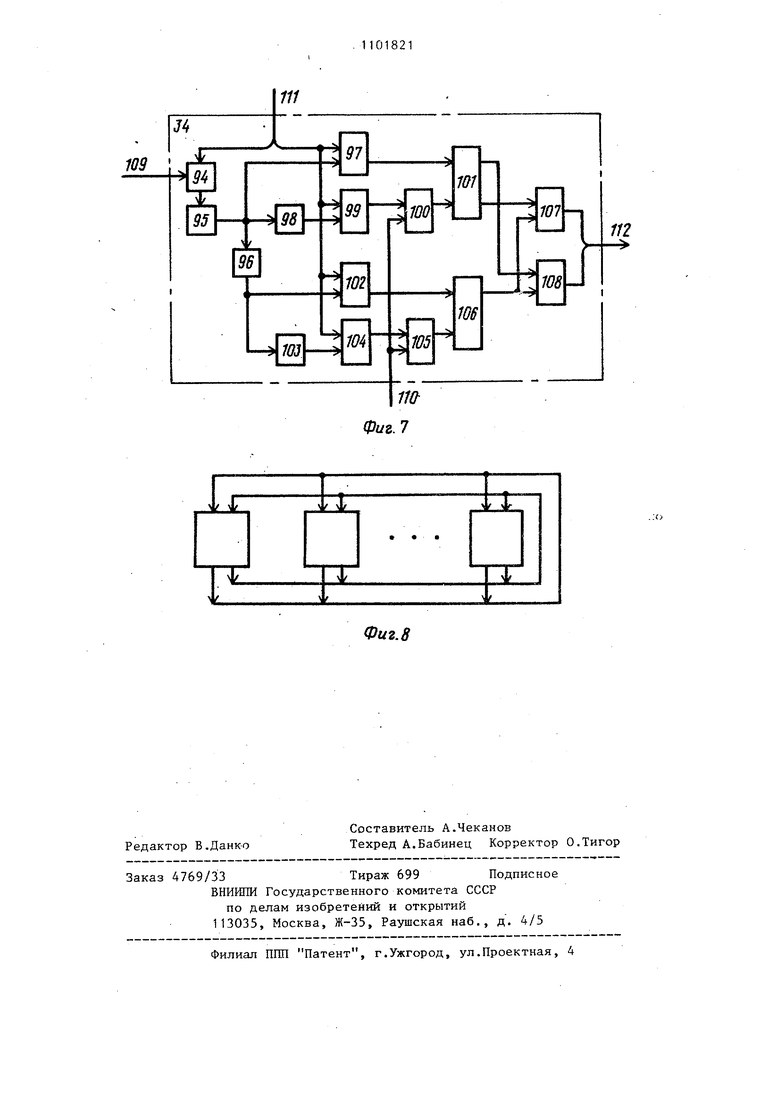

1. МОДУЛЬ ИНТЕГРИРУЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ, содержащий коммутатор и цифровой интегратор, причем выход установки в исходное состояние, группа выходов начальных данных подынтегральной функции и выход импульса сопровождения начальных данных под1 щтегральной функции коммутатора соединены соответственно с входом установки в исходное состояние, с группой входов начальных данHbFX и входом разрешения записи начальных данных цифрового, интегратора, а первый вход, группа входов и второй вход коммутатора соединены соответственно с входом выбора модуля, с шиной начальных данных модуля и входом сброса модуля, отличающийся тем, что,, с целью расширения области применения путем рещения более сложных систем урявиений, в него дополнительно регистр адреса модуля, группа из 3 регистров адреса входных приращений (гдej число входных приращений цифрового интегратора), блок сравнения адресов .модуля, группа из 3 блоков сравнения адресов входных приращений, группа из Л триггеров положительных приращений, группа из 3 триггеров отрицательных приращений, группа из 3 входных элементог. Ч положительных приращений, группа из 3 входных элементов И, отрицательных приращения, выходные элементы И положительных и отрицательных приращений, счетчик тактов, элемент ИЛИ, неполный дешифратор и формирователь длительности импульсов, причем выход установки в исходное состояние, 1 -я ( 1, 2,3,... Л ) группа информационных выходов и выход -го импульса из групi пы выходов импульсов сопровождения начальных данных коммутатора соединены соответственно с входом установки нуля, группой информационных входов и входом разрешения записи 1 -го регистра адреса входных приращений группы, а выход установки в исходное состояние, (Л -|-1)-я группа информационных выходов и выход

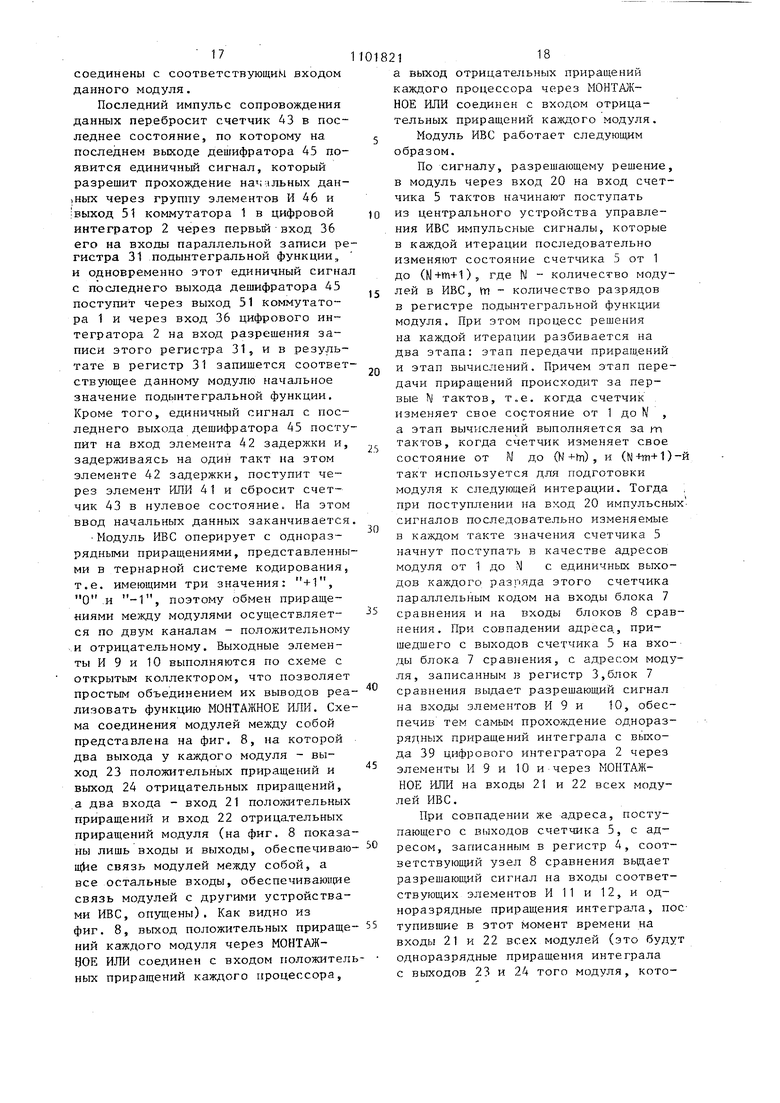

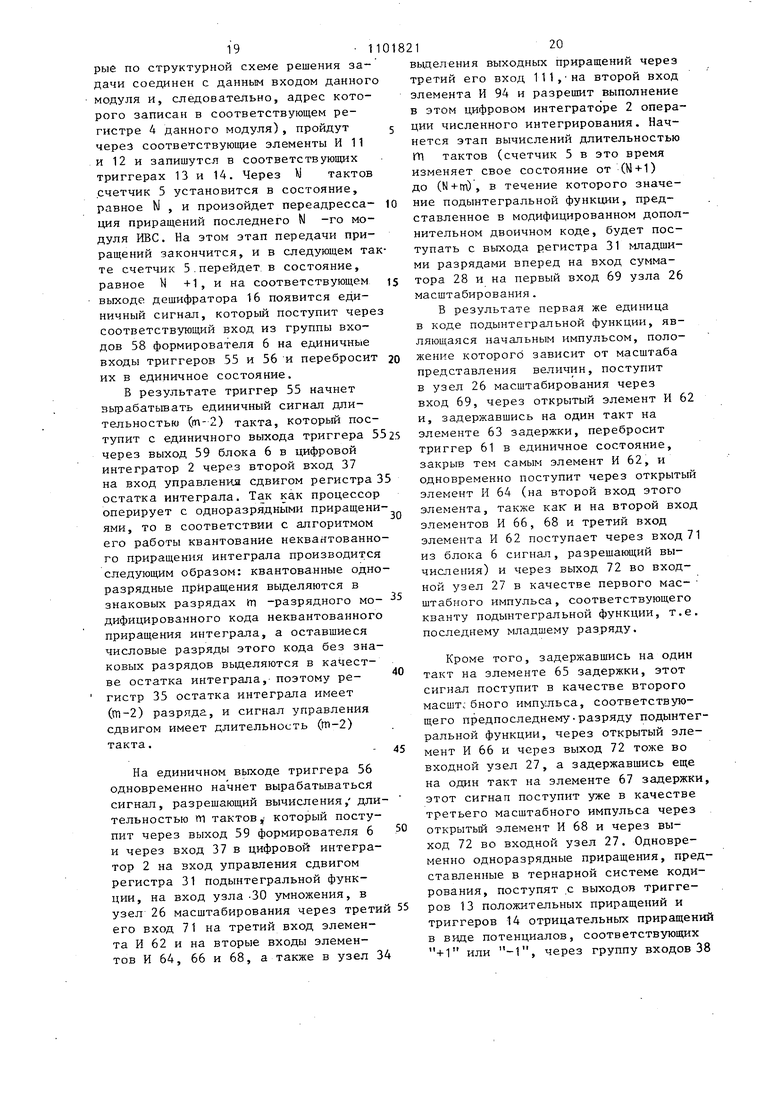

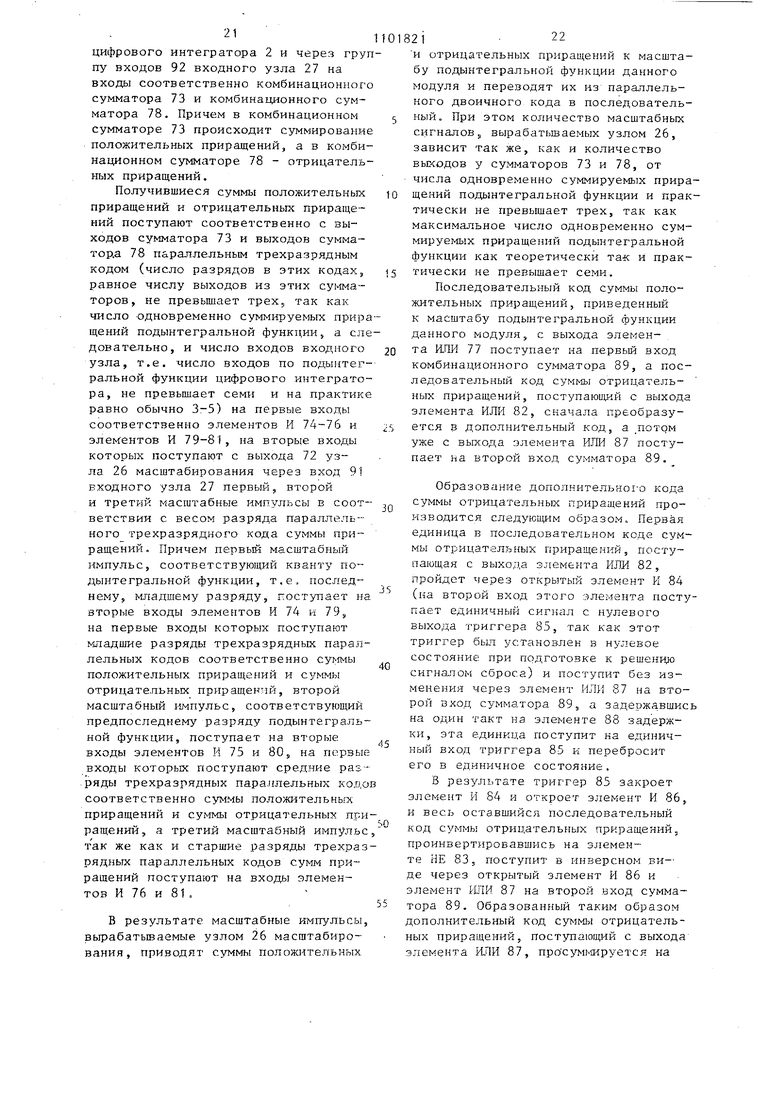

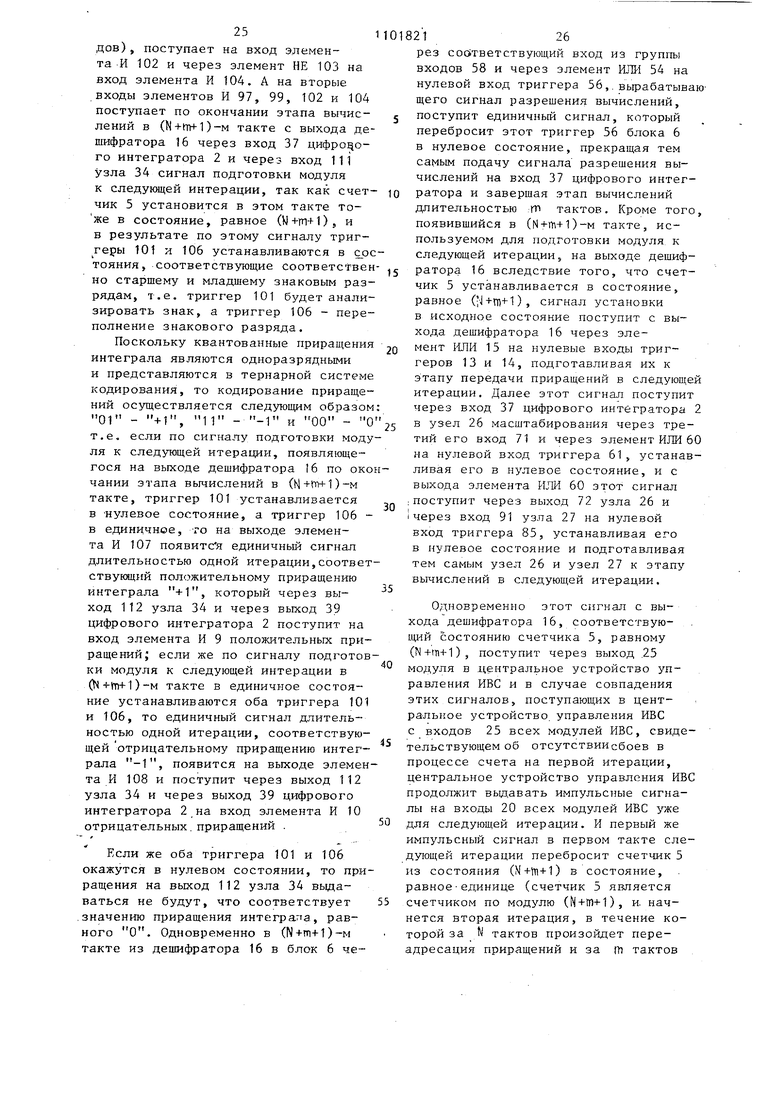

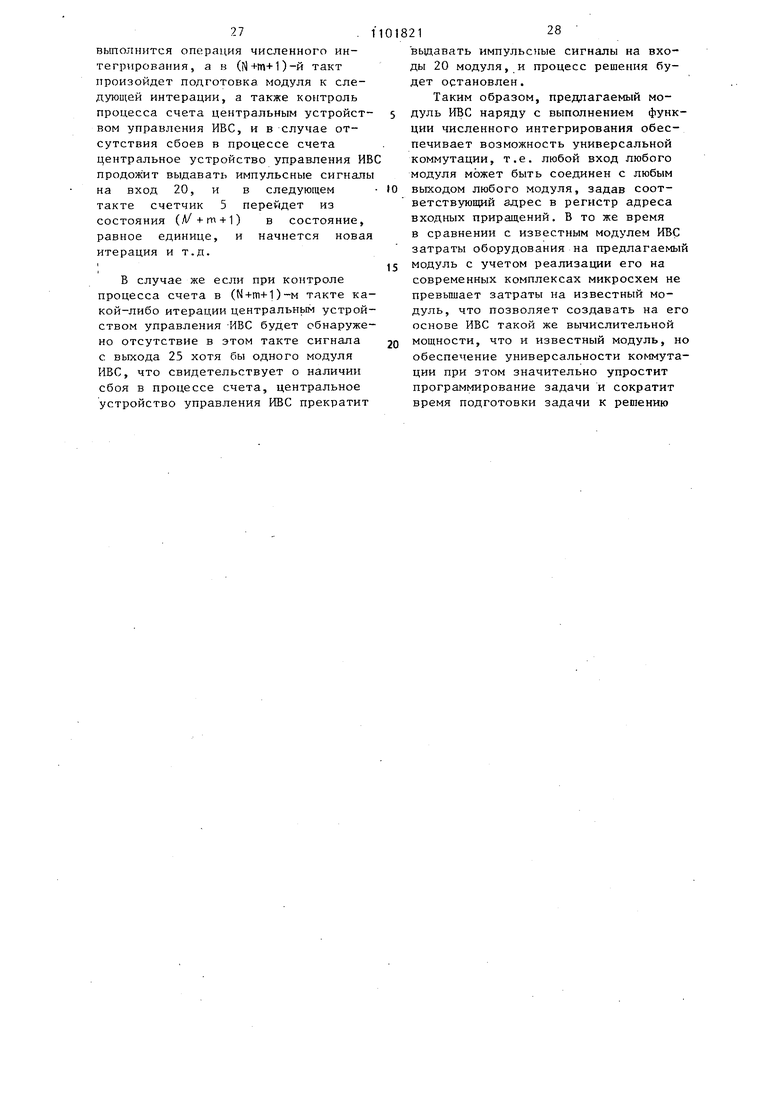

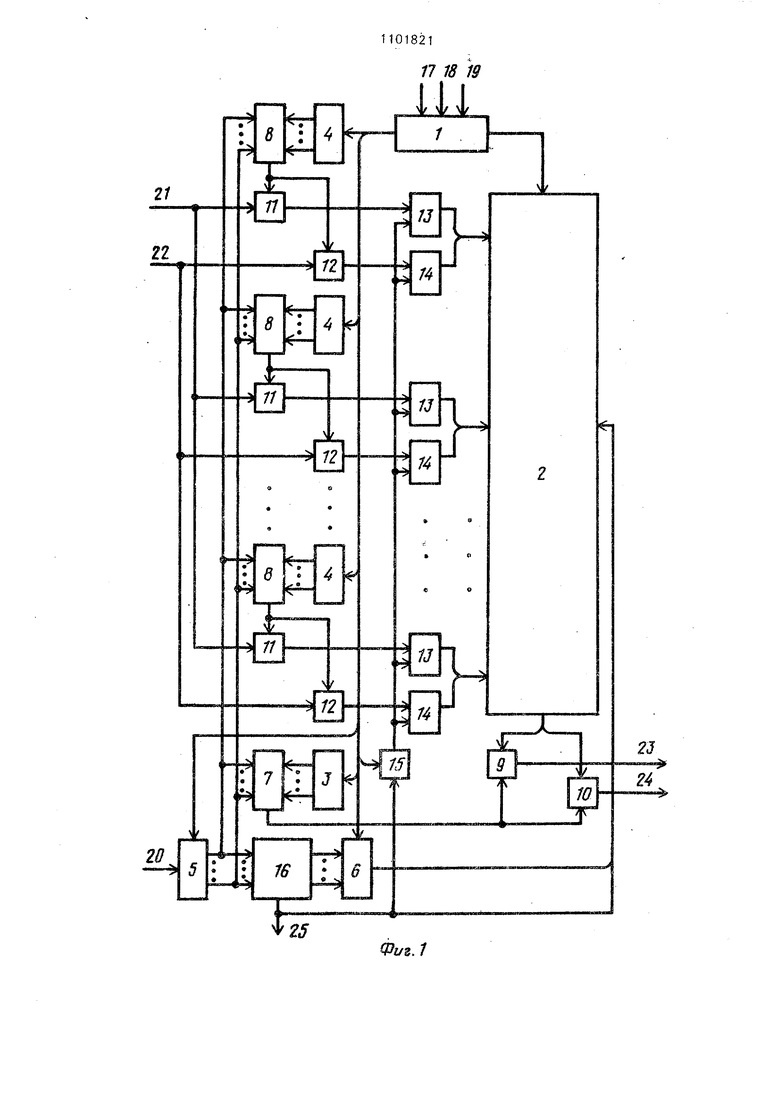

Изобретение относится к вычислительной технике и предназначено для

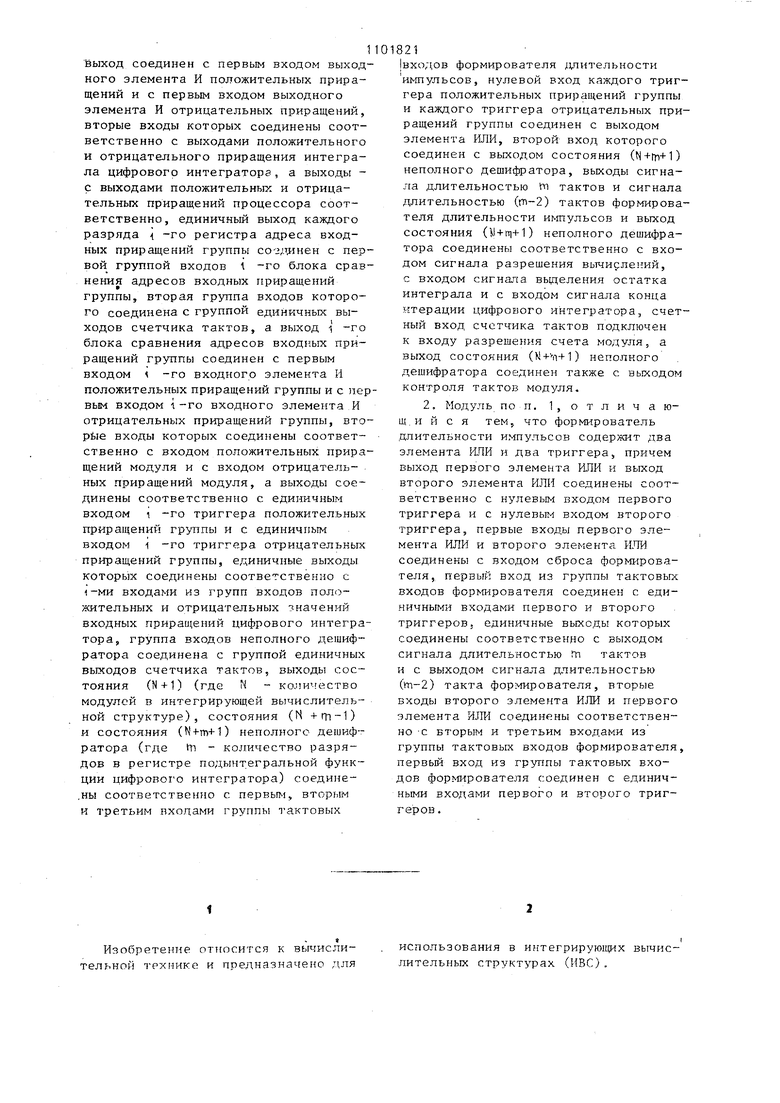

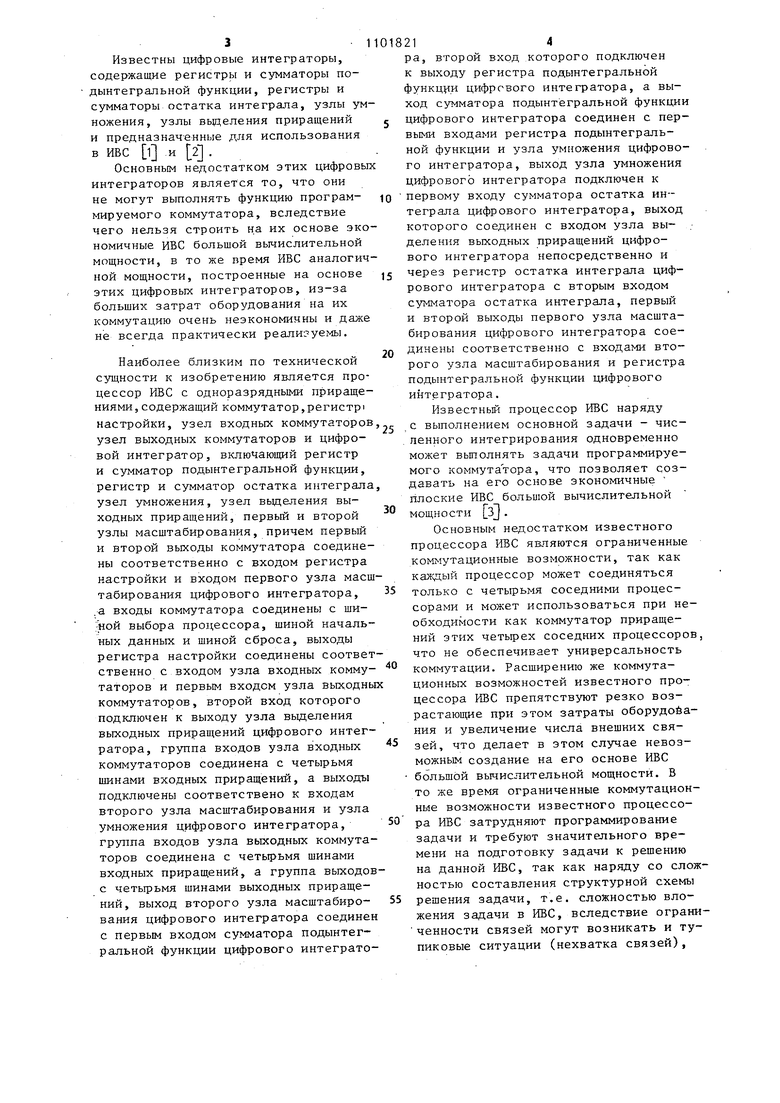

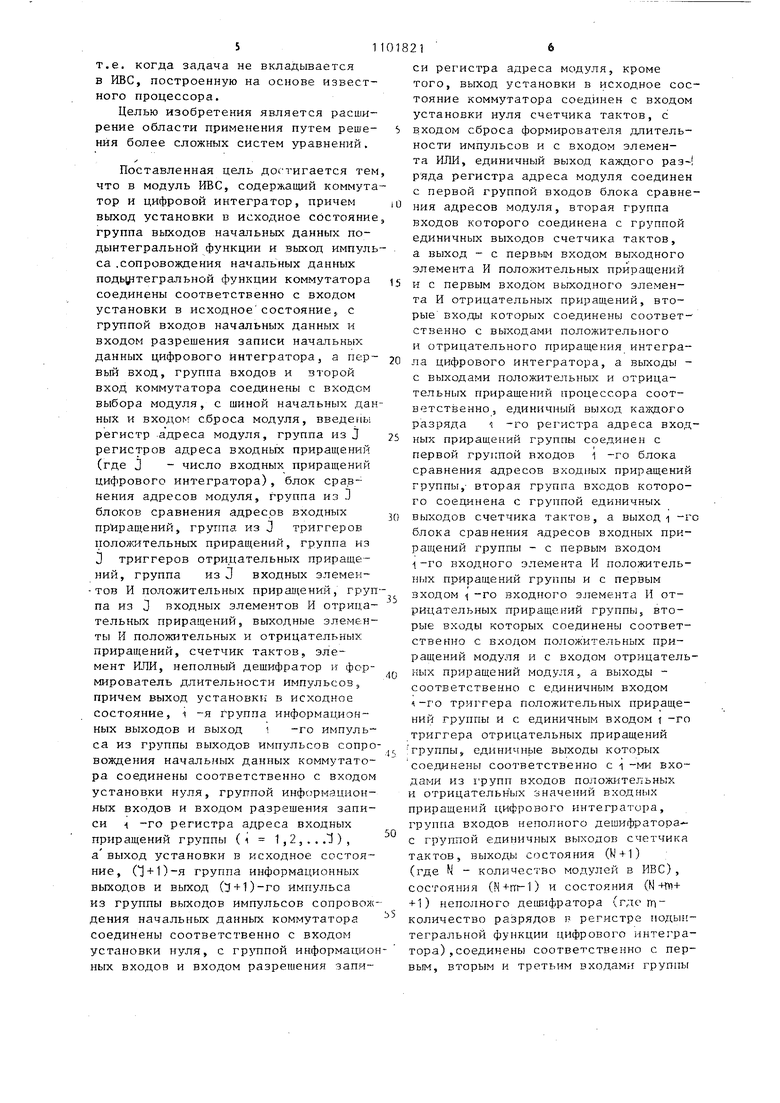

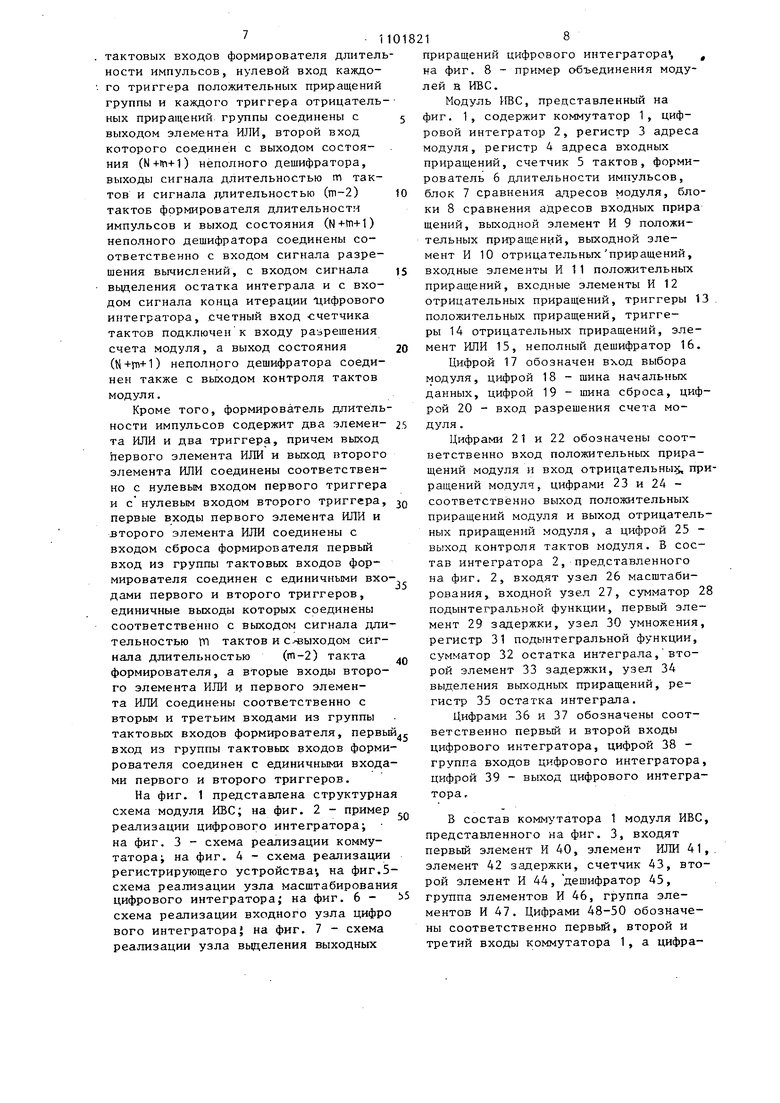

использования в интегрирую1щ х вычр1слительных структурах (ИВС). Известны цифровые интеграторы, содер жащие регистры и сумматоры подынтегральной функции, регистры и сумматоры остатка интеграла, узлы ум ножения, узлы вьделения приращений и предназначенные для использования в иве l и 2 . Основным недостатком этих цифровы интеграторов является то, что они не могут выполнять функцию программируемого коммутатора, вследствие чего нельзя строить ца их основе эко номичные иве большой вычислительной мощности, в то же время ИВС аналогич ной мощности, построенные на основе этих цифровых интеграторов, из-за больших затрат оборудования на их коммутацию очень неэкономичны и даже не всегда практически реали:уемы. Наиболее близким по технической сущности к изобретению является процессор ИВС с одноразрядными приращениями, содержащий коммутатор,регистр настройки, узел входных коммутаторов узел выходных коммутаторов и цифровой интегратор, включающий регистр и сумматор подынтегральной функции, регистр и сумматор остатка И1{теграла узел умножения, узел выделения выходных приращений, первый и второй узлы масштабирования, причем первый и второй выходы коммутатора соединены соответственно с входом регистра настройки и входом первого узла масш табирования цифрового интегратора, .а входы коммутатора соединены с ши;«ой выбора процессора, шиной начальных данных и шиной сброса, выходы регистра настройки соединены соответ ственно с входом узла входных коммутаторов и первым входом узла выходны коммутаторов, второй вход которого подключен к выходу узла вьщеления выходных приращений цифрового интегратора, группа входов узла входных коммутаторов соединена с четырьмя шинами входных приращений, а выходы подключены соответствено к входам второго узла масштабирования и узла умножения цифрового интегратора, группа входов узла выходных коммутаторов соединена с четырьмя шинами входных приращений, а группа выходов с четьфьмя шинами выходных приращений, выход второго узла масштабирования цифрового интегратора соединен с первым входом сумматора подынтегральной функции цифрового интегратора, второй вход которого подключен к выходу регистра подынтегральной функщ и цифрового интегратора, а выход сумматора подынтегральной функции цифрового интегратора соединен с первыми входами регистра подынтегральной функции и узла умножения цифрового интегратора, выход узла умножения цифрового интегратора подключен к первому входу сумматора остатка интеграла цифрового интегратора, выход которого соединен с входом узла выделения выходных приращений цифрового интегратора непосредственно и через регистр остатка интеграла цифрового интегратора с вторым входом сумматора остатка интеграла, первый и второй выходы первого узла масштабирования цифрового интегратора соединены соответственно с входами второго узла масштабирования и регистра подынтегральной функции цифрового интегратора. Известньй процессор ИВС наряду с выполнением основной задачи - численного интегрирования одновременно может выполнять задачи программируемого коммутатора, что позволяет создавать на его основе экономичные плоские иве большой вычислительной мощности sj . Основным недостатком известного процессора ИВС являются ограниченные коммутационные возможности, так как кайсдый процессор может соединяться только с четырьмя соседними процессорами и может использоваться при необходимости как коммутатор приращений этих четырех соседних процессоров, что не обеспечивает универсальность коммутации. Расширению же коммутационных возможностей известного процессора ИВС препятствуют резко возрастающие при этом затраты оборудобания и увеличение числа внешних связей, что делает в этом случае невозможным создание на его основе ИВС большой вычислительной мощности. В то же время ограниченные коммутационные возможности известного процессора ИВС затрудняют программирование задачи и требуют значительного времени на подготовку задачи к решению на данной ИВС, так как наряду со сложностью составления структурной схемы решения задачи, т.е. сложностью вложения задачи в ИВС, вследствие ограниченности связей могут возникать и тупиковые ситуации (нехватка связей). т.е. когда задача не вкладывается в иве, построенную на основе известного процессора. Целью изобретения является расширение области применения путем решения более сложных систем уравнен)1й. Поставленная цель достигается тем что в модуль liBC, содержащий коммута тор и цифровой интегратор, причем выход установки в исходное состояние группа выходов начальных данных подынтегральной функции и выход импуль са .сопровождения начальных данных подь ртегральной функции коммутатора соединены соответственно с входом установки в исходноесостояние5 с группой входов начальных данных и входом разрешения записи начальных данных цифрового интегратора, а первый вход, группа входов и второй вход коммутатора соединены с входом выбора модуля, с шиной начальных дан ных и входом сброса модуля, введеиь регистр адреса модуля, группа изj регистров адреса входных приращений (где J - число входных приращенир цифрового интегратора), блок сравнения адресов модуля, группа из 3 блоков сравнения адресов входных приращений, группа из J триггеров цололоттельных приращений, группа из J триггеров отрицательных приращений, группа из J входных элемен- тов И положительных приращений, груп па из 3 входных элементов И отрицательных приращений, выходные элементы И положительных и отрицательных приращений, счетчик тактов, элемент ИЛИ, неполный дешифратор и формирователь длительности импульсов, причем выход установки в исходное состояние, 1 -я группа информационных выходов и выход 1 -го импульса из группы выходов импульсов сопро вождения начальных данных коммутатора соединены соответственно с входом установки нуля, группой информационных входов и входом разрешения записи -го регистра адреса входных приращений группы (i 1, 2 , . . .1) , а выход установки в исходное состояние, (Т+1)-я группа информационных выходов и выход (3+1)-го импульса из группы выходов импульсов сопровож дения начальных данных коммутатора соединены соответственно с входом установки нуля, с информацио ных входов и входом разрешения запиСИ регистра адреса модуля, кроме того, выход установки в исходное состояние коммутатора соединен с входом установки нуля счетчика тактов, с входом сброса формирователя длительности импульсов и с входом элемента ИЛИ, единичный выход каждого разряда регистра адреса модуля соединен с первой группой входов блока сравнения адресов модуля, вторая группа входов которого соединена с группой единичных выходов счетчика тактов, а выход - с первым входом выходного элемента И положительных приращений и с первым входом выходного элемента И отрицательных приращений, вторые входа которых соединены соответ- ственно с выходами положительного и отрицательного приращения интеграла цифрового интегратора, а выходы с выходами положительных и отрицательных приращений процессора соответственно, единичный выход каждого разряда -го регистра адреса входных приращений группы соединен с первой группой входов 1 -го блока сравнения адресов входных приращений группы,- вторая группа входов которого соединена с группой единичных выходов счетчика тактов, а выход i -го блока сравнения адресов входных приращений группы - с первым входом -го входного элемента И положительHf.ix приращений группы и с первым входом 1 -го входного элемента И отрицательных приращений группы, вторые входы которых соединены соответственно с входом положительных приращений модуля и с входом отрицательных приращений модуля, а выходы соответственно с единичным входом 1-го триггера положительных приращений группы и с единичным входом t го триггера отрицательных приращений группы, единичные выходы которых соединены соответственно с 1 -ми входами из 1рупп входов положительных и отрицательных значений входных приращений цифрового интегратора, группа входов неполного дешифратора- с группой единичных выходов счетчика тактов, выходы состояния (J+1) (где N - количество модулей в ИВС), состояния (N-t-rrrO и состояния ( + 1) неполного денЕ фратора (где rriколичество ра:зрядов в регистре подынтегральной функции цифрового интегратора) , соединены соответственно с первым, вторым н третьим входами группы тактовых входов формирователя длител ности импульсов, нулевой вход каждого триггера положительных приращений группы и каждого триггера отрицатель ных приращений группы соединены с выходом элемента ИЛИ, второй вход которого соединен с выходом состояния (N+in+1) неполного дешифратора, выходы сигнала длительностью m тактов и сигнала длительностью (т-2) тактов формирователя длительности импульсов и выход состояния (N-HT1+1) неполного дешифратора соединены соответственно с входом сигнала разрешения вычислений, с входом сигнала вьщеления остатка интеграла и с входом сигнала конца итерации цифрового интегратора, счетный вход счетчика тактов подключен к входу разрешения счета модуля, а выход состояния (N+rn+1) неполного дешифратора соединен также с выходом контроля тактов модуля. Кроме того, формирователь длитель ности импульсов содержит два злемента ИЛИ и два триггера, причем выход первого элемента ИЛИ и выход пторого элемента ИЛИ соединены соответственно с нулевым входом первого триггера и с нулевым входом второго триггера, первые входы первого элемента ИЛИ и второго элемента ИЛИ соединены с входом сброса формирователя первый вход из группы тактовых входов формирователя соединен с единичными вхо дами первого и второго триггеров, единичные выходы которых соединены соответственно с выходом сигнала ;щи тельностью ЮП тактов и с ыходом сигнала длительностью (т-2) такта формирователя, а вторые входы второго элемента ИЛИ и первого элемента ИЛИ соединены соответственно с вторым и третьим входами из группы тактовых входов формирователя, первы вход из группы тактовых входов форми рователя соединен с единичными входа ми первого и второго триггеров. На фиг. 1 представлена структурна схема модуля ИВС; на фиг. 2 - пример реализации цифрового интегратора; на фиг, 3 - схема реализации коммутатора i на фиг. 4 - схема реализации регистрирующего устройства, на фиг.5 схема реализации узла масштабировани цифрового интегратора; на фиг. 6 схема реализации входного узла цифро вого интегратора} на фиг. 7 - схема реализации узла вьщеления выходных приращений цифрового интегратора, , на фиг. 8 - пример объединения модулей в ИБС. Модуль РГВС, представленный на фиг. 1, содержит коммутатор 1, цифровой интегратор 2, регистр 3 адреса модуля, регистр 4 адреса входных приращений, счетчик 5 тактов, формирователь 6 длительности импульсов, блок 7 сравнения адресов модуля, блоки 8 сравнения адресов входных прира щений, выходной элемент И 9 положительных приращений, выходной элемент И 10 отрицательныхприращений, входные элементы И 11 положительных приращений, входные элементы И 12 отрицательных приращений, триггеры 13 положительных приращений, триггеры 14 отрицательных приращений, элемент ИЛИ 15, неполный дешифратор 16. Цифрой 17 обозначен вход выбора модуля, цифрой 18 - шина начальных данных, цифрой 19 - шина сброса, цифрой 20 - вход разрешения счета модуля . Цифрами 21 и 22 обозначены соответственно вход положительных приращений модуля и вход отрицательны}}, приращений модуля, цифрами 23 и 24 соответственно выход положительных приращений модуля и выход отрицательных приращений модуля, а цифрой 25 выход контроля тактов модуля. В состав интегратора 2, представленного на фиг. 2, входят узел 26 масштабирования, входной узел 27, сумматор 28 подынтегральной функции, первый элемент 29 задержки, узел 30 умножения, регистр 31 подынтегральной функции, сумматор 32 остатка интеграла,второй элемент 33 задержки, узел 34 выделения выходных приращений, регистр 35 остатка интеграла. Цифрами 36 и 37 обозначены соответственно первый и второй входы цифрового интегратора, цифрой 38 группа входов цифрового интегратора, цифрой 39 - выход цифрового интегратора, В состав коммутатора 1 модуля ИВС, редставленного на фиг. 3, входят ервый элемент И 40, элемент ИЛИ 41,. лемент 42 задержки, счетчик 43, втоой элемент И 44, дешифратор 45, руппа элементов И 46, группа элеентов И 47. Цифрами 48-50 обозначеы соответственно первьй, второй и ретий входы коммутатора 1, а цифрами 51 и 52 - соответственно первый и второй выходы коммутатора. В состав формирователя 6 длитель ности импульсов модуля иве, предста ленного на фиг. 4, входят первый зл мент ИЛИ 53, второй элемент ИЛИ 54, первьш триггер 55, второй триггер 56. Цифрой 57 обозначен вход фор мирователя, цифрами 58 - группа вхо дов этого формирователя, цифрой 59 выход формирователя. В состав узла 26 масштабирования цифрового интегратора 2, представлен ного на фиг. 5, входят элемент ИЛИ триггер 61, первьй элемент И 62, первый элемент 63 задержки, второй элемент И 64, второй элемент 65 задержки, третий элемент И 66, третий элемент 67 задержки, четвертый элемент И 68. Цифрами 69-71 обозначены соответственно первьм, второй и третий входы узла 26 масштабирования, а цифрой 72 - выход узла. В состав входного узла 27 цифрово го интегратора 2, представленного на фиг. 6, входят первый комбинационный сумматор 73, первый элемент И 74 второй элемент И75, третий элемент И 76, первый элемент ИЛИ 77, второй комбинационный сумматор 78, четвертый элемент И 79, пятый элемент И 80, шестой элемент И 81, второй элемент ИЛИ 82, элемент НЕ 83, седьмой элемент И 84, триггер 85, восьмой элемент И 86, третий элемент ИЛИ 87, первьм элемент 88 задержки, третий комбинационный сумматор 89, второй элемент 90 задержки Цифровой 91 обозначен вход входного узла 27, цифрами 92 - группа входов этого узла, цифрой 93 - выход входного узла 27. В состав узла 34 выделения выходных приращений цифрового интегратора 2, представленного на фиг. 7, вхо дят первый элемент И 94, первый элемент 95 задержки, второй элемент 9.6 задержки, второй элемент И.97, первьй элемент НЕ 98, третий элемент И 9 первый элемент ИЛИ 100, первьм триггер 101, четвертый элемент И 102, второй элемент НЕ 103, пятый элемент И 104, второй элемент ИЛИ 105., второй триггер 106, шестой элемент И 107, седьмой элемент И 108. Цифрами 109-111 обозначены соответственно первьм, второй и третий входы узла 34 вьщеления выходных приращений, а цифрой 112 - выход узла 34 выделения выходных приращений. Первьй выход коммутатора 1 соединен с первым входом цифрового интегратора 2, а второй выход - с входом регистра 3 адреса модуля, с вхсдом каждого регистра 4 адреса входных приращений, с первым входом счетчика 5 тактов и с входом формирователя 6. Выход каждого разряда регистра 3 адреса процессора соединен с первой группой входов блока 7 сравнения адресов процессоров, вторая- группа входов которого соединена с группой выходов счетчика 5 тактов. Выход каждого разряда каждого регистра 4 адреса входных приращений соединен с первой группой входов соответствующего блока 8 сравнения адр|- сов входных приращений, вторая группа входов каждого из которых соединена с группой выходов счетчика 5 тактов. Выход блока 7 сравнения адресов модуля соединен с первым входом выходного элемента И 9 положительных приращений и с первым входом БЕ)1ХОДНОГО элемента И 10 отрицательных приращений, вторые входы которых соединены с выходом цифрового интегратора 2. Выход каждого блока 8 сравнения адресов входных приращений соединен с первым входом соответствующего входного элемента И 11 положительных приращений и с первым входом соответствующего входного элемента И 12 отрицательных приращений, выходы каищого из которых соединены соответственно с единичными входами соответствую1цего триггера 13 положительных приращений и соответствующего триггера 14 отрицательных приращений, единичные выходы которых соединены с соответствую1цим входом из группы входов цифрового интегратора 2. Нулевой вход каждого триггера 13 положительных приращений и каждого триггера 14 отрицательных приращений соединен с выходом элемента РШИ 15, первый и второй входы которого соединены соответственно с вторым выходом коммутатора 1 и с выходом неполного дешифратора 16, группа входов которого соединена с группой выходов счетчика 5 тактов, а группа выходов - с группой входов формирователя 6. Второй вход цифрового интегратора 2 соединен с выходом формировате11ля 6 и с выходом неполного дешифратора 16. Первый, второй и третий входы ком мутатора 1 соединены соответственно с входом 17 выбора процессора, с шиной 18 начальных данных и с шиной 19 сброса. Второй вход счетчика 5 тактов соединен с входом 20 разрешения счета процессора. Второй вход каждого входного элемента И 11 положительных приращений и второй вход каждого входного элемента И 12 отрицательных приращений соединены соответственно с входом 21 положительных приращений модуля и с входом 22 отрицательных приращений модуля. Выход выходного элемента И 9 поло жительных приращений и выход выходного элемента И 10 отрицательных .приращений соединены соответственно с выходом 23 положительных приращений модуля и с выходом 24 отрицатель ных приращений модуля. Выход неполного дешифратора 16 соединен также с выходом 25 контроля тактов модуля. Выход узла 26 масштабирования соединен с входом входного узла 27, выход которого соединен с первым вхо дом сумматора 28 подынтегральной функции, первый выход которого соединен через первьй элемент 29 задерж ки с вторым входом сумматора 28 подынтегральной функции, а второй выход - с входом узла 30 умножения и с входом регистра 31 подынтегральной функции, выход которого соединен с третьим входом сумматора 28 подынте ральной функции и с входом узла 26 масштабирования. Выход узла 30 умножения соединен с первым входом сумматора 32 остатка интеграла, первый выход которого соединен через второй элемент 33 за держки с вторым входом сумматора 32 остатка интеграла, а второй выход с входом узла 34 выделения выходных приращений и с входом регистра 35 остатка интеграла, выход которого соединен с третьим входом сумматора 32 остатка интеграла. Второй вход узла 26 масштабирова ния, второй вход регистра 31 подынтег ральной функции, второй вход узла 3 вьщеления выходных приращений и вто рой вход регистра 35 остатка интегр 112 ла соединены с первым входом 36 цифрового интегратора 2i Третий вход узла 26 масштабирования, второй вход узла 30 умножения, третий вход регистра 31 подынтегральной функции, третий вход узла 34 выделения выходных приращений и третий вход регистра 35 остатка интеграла соединены с вторым входом 37 цифрового интегратора 2. Третий вход узла 30 умножения соединен с одним из входов группы входов 38 цифрового интегратора 2, а остальные входы этой группы входов 38 цифрового интегратора 2-е группой входов входного узла 27. Выход узла 34 вьщеления выходных приращений соединен с выходом 39 цифрового интегратора 2. Выход первого элемента И 40 соединен с входом элемента ИЛИ 41, второй в,сод которого соединен с выходом элемента 42 задержки, а выход - с входом счетчика 43, второй вход которого -соединен с выходом второго элемента И 44, а группа выходов - с группой входов дешифратора 45, выход которого соединен с входом элемента 42 задержки и с первыми входами группы элементов И 46. Каждый выход группы выходов дешифратора 45 соединен с первыми входами соответствующей группы элементов И 47 из а групп этих элементов. Первый вход первого элемента И 40, первьй вход второго элемента И 44, вторые входы группы элементов И 46 и вторые входы каждой группы элементов И 47 из п групп этих элементов соединены с первым входом 48 коммутатора 1. Второй вход второго элемента И 44, третьи входы группы элементов И 46 и третьи входы каждой группы элементов И 47 из VI групп этих элементов соединены с вторым входом 49 коммутатора 1, а второй вход первого элемента И 40 с третьим входом 50 коммутатора 1. Выход первого элемента И 40, выход дешифратора 45 и выходы группы элементов И 46 объединены в первый выход 51 коммутатора 1, а выход первого элемента И 40, группа выходов дешифратора 45 и выходы каждой группы элементов И 47 из л групп этих элементов объединены во второй выход 52. коммутатора 1. Выходы первого элемента ИЛИ 53 и второго элемента ИЛИ 54 соединены 13 соответственно с нулевым входом пер вого триггера 55 и нулевым входом второго триггера 56. Первый входы первого элемента ИЛИ 53 и второго элемента ИЛИ 54 соединены с входом 5 формирователя, а вторые входы перво го элемента ИЛИ 53 и второго элемен та ИЛИ 54 и единичные первого триггера 55,и второго триггера 56 с динены с группой входов 58 формиров теля. Единичный выход первого триггера 55 и единичный выход второго триггера 56 соединены с выходом 59 формирователя. Выход-элемента ИЛИ 60 соединен с нулевым входом триггера 61, нулевой выход которого соединен с входом пер вого элемента И 62, выход которого соединен с входом второго элемента 65 задержки, выход которого соединен с единичным входом триггера 6 с входом второго элемента И 64 и с входом второго элемента 65 задержки выход которого соединен с входом третьего элемента И 66 и с входом третьего элемента 67 задержки, выход которого соединен с входом четвертого элемента И 68. Второй вход первого элемента И 62 соединен с пер вым входом 69 узла 26 масштабироваНИН, а первый вход элемента ИЛИ 60 с вторым входом 70 узла 26 масштабирования. Второй вход элемента ИЛИ 60 третий вход первого элемента И 62 и вторые входы второго элемента И 64 третьего элемента И 66, четвертого элемента И 68 соединены с третьим входом 71 узла 26 масштабирования. Выходы элемента ИЛИ 60, второго элемента И 64, третьего элемента И 66 и четвертого элемента И 68 соединены с выходом 72 узла 26 масштабирования Первый, В7Орой и третий выходы пе вого комбинационного сумматора 73 соединень соответственно с первым входом первого элемента И 74, первьЕм входом второго элемента И 75, первым входом третьего элемента И 76, выходы каждого из которьк соединены с входами первого элемента ИЛИ 77. Пер „ - выи, второй и третий выходы второго комбинационного сумматора 78 соединены соответственно с первым входом четвертого элемента И 79, с первым входом пятого элемента И 80, с первым входов шестого элемента И 81, выходы каждого из которых соединены с входами второго элемента ИЛИ 82, выход которого соединен с входом эле 2114 мента НЕ 83 и с входом седьмого элемента И 84, второй вход которого соединен с нулевым выходом триггера 85, единичный выход которого соединен с входом восьмого элемента И 86, второй вход которого соединен с выходом элемента НЕ 83, а выход - с входом третьего элемента ИЛИ 87, второй вход которого соединен с выходом седьмого элемента И 84 и с входом первого элемента 88 задержки выход которого соединен с единичным входом триггера 85. Выход первого элемента ИЛИ 77 и выход третьего элемента ИЛИ 87 соединены соответственно с первым и вторым входами третьего комбинационного сумматора 89, первый выход которого соединен через второй элемент 90 задержки с третьим входом третьего комбинационного сумматора 89. Вторые входы первого элемента И 74, второго элемента И 75, третьего элемента И 76, четвертого элемента И 79, пятого элемента И 80, шестого элемента И 81 и нулевой вход триггера 85 соединены с входом 91 входного узла 27, а группа входов первого комбинационного сумматора 73 и группа входов второго комбинационного сумматора 78 - с группой входом 92 входного узла 27, второй выход третьего комбинационного сумматора 89 соединен с выходом 93 входного узла 27. Выход первого элемента И 94 соединен через первый элемент 95 задержки с входом элемента 96 задержки, с входом второго элемента И 97 и с входом первого элемента НЕ 98, выход которого соединен с входом третьего элемента И 99 ,, выход которого соединен с входом первого элемента ИЛИ 100, выход которого соединен с нулевым входом первого триггера 101, единичный вход которого соединен с выходом второго элемента И 97. Выход второго элемента 96 задержки соединен с входом четвертого элемента И 102 и с входом второго элемента НЕ 103, которого соединен с входом пятого элемента И 104, выход которого соединен с входом второго элемента ИЛИ 105, выход которого соединен с нуле.вьм входом второго триггера 106, единичный вход которого соединен с выходом четвертого элемента И 102. .Нулевой и единичный выходы первого триггера 101 соединены соответственно с первым входом шестого элемента И 107 и с первым входом седьмого элемента И 108, второй вход каждого из которых соединен с единичным выходом второго триггера 106. Первый вход первого элемента И 94 соединен с первым входом 109 узла ЗА выделения выходных приращений, а второй вход первого элемента ИЛИ 100 и второй вход второго элемента ИЛИ 105 соединены с вторым входом 110 узла 34 вьщеления выходных приращений. Вторые входы первого элемента И 94, второго элемента И 97, третьего элемента И 99, четвертого элемента И 10 и пятого элемента И 104 соединены с третьим входом 111 узла 34 вьщелеНИН выходных приращений, а выходы шестого элемента И 107 и седьмого элемента И 108 соединены с. выходом 112 узла 34 выделения вь;ходных приращений. Перед началом работы производится установка модуля дас в исходное состояние. При этом на вход 17 выбора модуля подается единичный сигнал, который, пройдя через вход 48 коммутатора 1, откроет элемент И 40, и при подаче сигнала сброса через вход 19 модуля на вход 50 коммутатора 1 этот сигнал пройдет через открытый элемент И 40 и поступит через выход 52 на входы установки нуля регистров 3 и 4 и счетчика 5, устанавливая их в нулевое состояние, а пройдя через элемент ИЛИ 15, этот сигнал установит в нулевое состояние триггеры 13 и 14. Кроме того, сигнал сброса с выхода 52 коммутатора 1 пос тупит на вход 57 блока 6 и, пройдя через элементы ИЛИ 53 и ИЛИ 54, сбро сит в нулевое состояние триггеры 55 и 56. Одновременно сигнал сброса поступит с выхода элемента И 40 чере выход 51 коммутатора 1 в цифровой интегратор 2 через первый его вход на входы установки нуля регистров 3 и 35, устанавливая их в нулевое состояние, а пройдя с входа 36 цифрового интегратора 2 через вход 70 узла 26 масштабирования и через элемент ИЛИ 60, установит в нулевое состояние триггер 61. Кроме того, с выхода элемента ИЛИ 60 сигнал сбр са пройдет через выход 72 узла 26 масштабирования и вход 91 входного узла 27 на нулевой вход триггера 85 и установит его в нулевое состояние Одновременно сигнал сброса с входа 36 цифрового интегратора поступи на вход 110 узла 34 выделения выходных приращений и, пройдя через элементы, ИЛИ 100 и ИЛИ 105, сбросит в нулевое состояние соответственно три1- гер 101 и триггер 106. Кроме того, сигнал сброса с выхода элемента И 40 пройдет через элемент ИЛИ 41 и сбросит в нулевое состояние счетчик 43. Затек производится ввод начальных данных. При этом через вход 17 на вход 48 коммутатора 1 подается потенциал, поступающий на вход элемента И 44, на вторые входы группы элементов И 46 и на вторые входы каждой группы элементов И 47 из И групп этих элементов, а по шине 18 на шину 49 коммутатора 1 подаются параллельным кодом начальные данные, которые поступают с шины 49 на третьи входы группы элементов И 46 и на третьи входы каждой группм элементов И 47 из П групп этих элементов. Одновременно по одной из линий связи шины 18 начальных данньк (обычно по последней линии связи) в коммутатор 1 на второй вход элемента И 44 поступают импульсы сопровождения данных, которые проходят через этот элемент И 44 (на второй его вход поступает потенциал с входа 17) на суммирующий вход счетчика 43, состояние которого расшифровьшается дешифратором 45. Дричем при поступлении каждого нового импульса сопровождения данных состояние счетчика 43 увеличивается на единицу, и на соответствующем выходе дешифратора 45 появляется единичный сигнал,который разрешает прохождение начальных данных через соответствующую группу злементов И 47 из 1 групп этих элементов и через выход 52 коммутатора 1 на входы параллельной записи регистра 3 или соответствующего регистра 4 адреса входных приращений. Одновременно этот единичный сигнал с соответствующего выхода дешифратора 45 поступит через выход 52 коммутатора 1 на вход разрешения записи соответствующего регистра 3 или 4, обеспечивая тем самым ввод начальной информации в соответствующий регистр. При этом в регистр 3 запишется адрес, соответств тощий номеру модуля на структурной схеме решения задачи, а в регистры 4 - соответствующие этому модулю адреса входных приращений, т.е. номера тех модулей, которые по структурной схеме решения, задачи

- 17

соединены с соответствующим входом данного модуля.

Последний импульс сопровождения данных перебросит счетчик A3 в последнее состояние, по которому на последнем выходе дешифратора 45 появится единичньй сигнал, который разрешит прохождение на гнльных дан)Ных через группу элементов И 46 и ;выход 51 коммутатора 1 в цифровой интегратор 2 через первьй вход 36 его на входы параллельной записи регистра 31 подынтегральной функции, и одновременно этот единичный сигна с последнего выхода дешифратора 45 поступит через выход 51 коьмутатора 1 и через вход 36 цифрового интегратора 2 на вход разрешения записи этого регистра 31, и в результате в регистр 31 запишется соответствующее данному модулю начальное значение подынтегральной функции. Кроме того, единичный сигнал с последнего дешифратора 45 поступит на вход элемента 42 задержки и, задерживаясь на один такт на этом элементе 42 задержки, поступит через элемент ИЛР 41 и сбросит счетчик 43 в нулевое состояние. На этом ввод начальных данных заканчивается

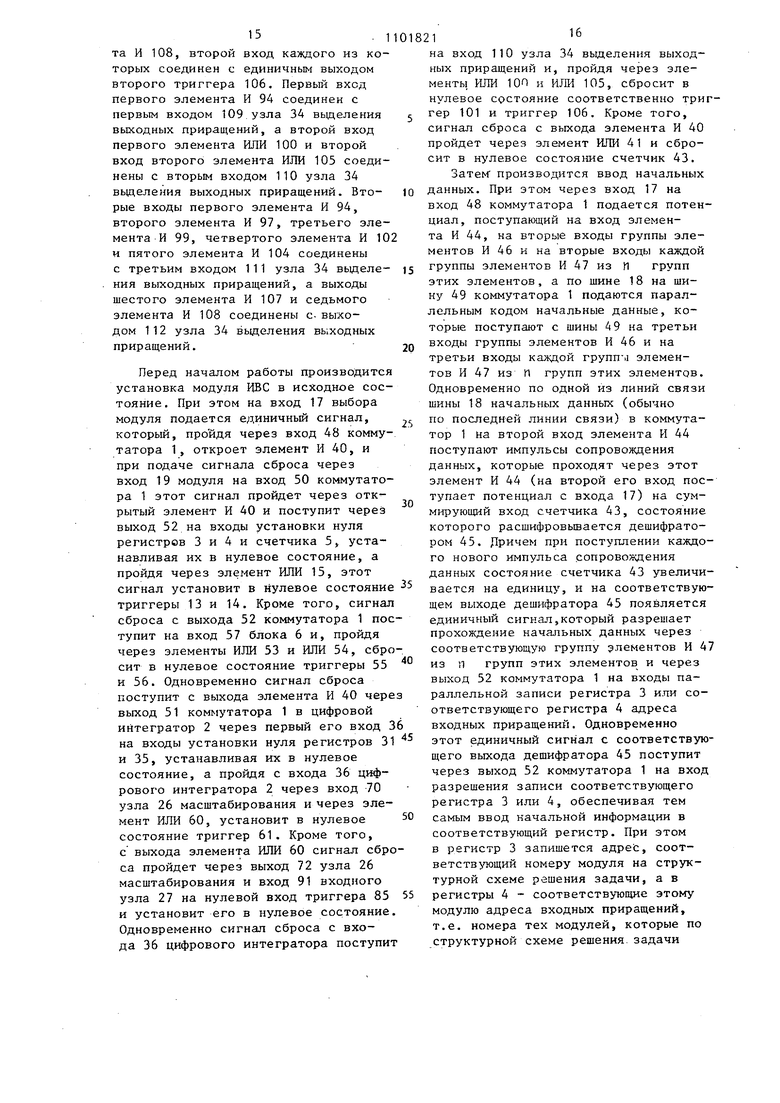

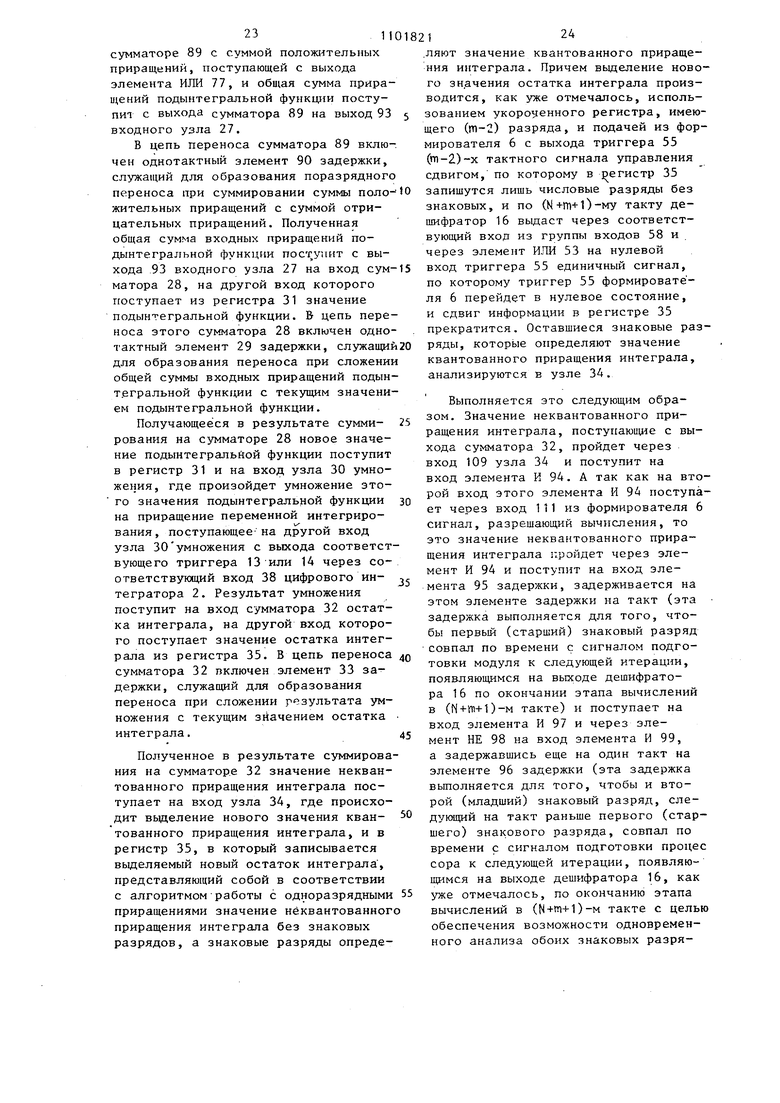

Модуль иве оперирует с одноразрядными приращениями, представленными в тернарной системе кодирования, т.е. имеющими три значения: +1, О ,и -1, поэтому обмен приращениями между модулями осуществляется по двум каналам - положительному ,и отрицательному. Выходные элементы И 9 и 10 выполняются по схеме с открытым коллектором, что позволяет простым объединением их вьшодов реализовать функцию МОНТАЖНОЕ ИЛИ. Схема соединения модулей между собой представлена на фиг. 8, на которой два выхода у каждого модуля - выход 23 положительных приращений и выход 24 отрицательных приращений, .а два входа - вход 21 положительных приращений и вход 22 отрицательных приращений модуля (на фиг. 8 показаны лишь входы и выходы, обеспечивающие связь модулей между собой, а все остальные входы, обеспечивающие связь модулей с другими устройствами иве, опущены). Как видно из фиг. 8, выход положительных приращений каждого модуля через МОНТАЖНОР ИЛИ соединен с входом положителных приращений каждого процессора.

182118

а выход отрицательных приращений каждого процессора через МОНТАЖНОЕ ИЛИ соединен с входом отрицательных приращений каждого модуля. 5 Модуль иве работает следующим образом.

По сигналу, разрешающему решение, в модуль через вход 20 на вход счетчика 5 тактов начинают поступать

)0 из центрального устройства управления иве импульсные сигналы, которые в каждой итерации последовательно изменяют состояние счетчика 5 от 1 до (N+m+l), где N - количество моду)5 лей в иве, W - количество разрядов в регистре подынтегральной функции модуля. При этом процесс решения на каж,п,ой итерации разбивается на два этапа: этап передачи приращений

2Q и этап вычислений. Причем этап передачи приращений происходит за первые N тактов, т.е. когда счетчик изменяет свое состояние от 1 до N , а этап вычислений выполняется за m

-. тактов, когда счетчик изменяет свое состояние от М до (N+Гл) , и (М+т+1)-й такт используется для подготовки модуля к следующей интерации. Тогда , при поступлении на вход 20 импульсных

сигналов последовательно изменяемые 0с

в каждом такте значения счетчика 5

начнут поступать в качестве адресов модуля от 1 до М с единичных выходов каждого разряда этого счетчика параллельным кодом на входы блока 7

5 сравнения и на входы блоков В сравнения. При совпадении адреса., пришедшего с выходов счетчика 5 на входы блока 7 сравнения, с адресом модуля, записанным в регистр 3,блок 7 сравнения выдает разрешающий сигнал на входы элементов И 9 и 10, обеспечив тем самым прохождение одноразрядных приращений интеграла с выхода 39 цифрового интегратора 2 через

элементы И 9 и 10 и через МОНТАЖНОЕ ИЛИ на входы 21 и 22 всех модулей иве.

При совпадении же адреса, поступающего с выходов счетчика 5, с ад0 ресом, записанным в регистр 4, соответствующий узел 8 сравнения вьдает разрешаюшд й сигнал на входы соответствующих элементов И 11 и 12, и одноразрядные приращения интеграпа, пос5 тупившие в этот Момент времени на

входы 21 и 22 всех модулей (это будут одноразрядные приращения интеграла с вькодов 23 и 24 того модуля, которыб по структурной схеме решения задачи соединен с данным входом данног модуля и, следовательно, адрес которого записан в соответствующем регистре 4 данного модуля), пройдут через соответствующие элементы И 11 и 12 и запишутся в соответствующих триггерах 13 и 14. Через W тактов счетчик 5 установится в состояние, равное W , и произойдет переадрессадня приращений последнего N -го модуля иве. На этом этап передачи приращений закончится, и в следующем та те счетчик 5.перейдет в состояние, равное Н +1, и на соответствующем выходе дешифратора 16 появится единичный сигнал, который поступит чере соответствующий вход из группы входов 58 формирователя 6 на единичные входы триггеров 55 и 56 и перебросит их в единичное состояние. В результате триггер 55 начнет вырабатьшать единичный сигнал длительностью (т-2) такта, который поступит с единичного выхода триггера 5 через выход 59 блока 6 в цифровой интегратор 2 через второй вход 37 на вход управления сдвигом регистра остатка интеграла. Так как процессор оперирует с одноразрядными приращени ями, то в соответствии с алгоритмом его работы квантование неквантованно го приращения интеграла производится следующим образом: квантованные одно разрядные приращения выделяются в знаковых разрядах In -разрядного мо дифицированного кода неквантованного приращения интеграла, а оставшиеся числовые разряды этого кода без зна ковых разрядов вьщеляются в качестве остатка интеграла, поэтому регистр 35 остатка интеграла имеет (т-2) разряда, и сигнал управления сдвигом имеет длительность (fn-2) такта. На единичном выходе триггера 56 одновременно начнет вырабатываться сигнал, разрешающий вычисления, дли тельностью гп тактов который поступит через выход 59 формирователя 6 и через вход 37 в цифровой интегратор 2 на вход управления сдвигом регистра 31 подынтегральной функции, на вход узла -30 умножения, в узел 26 масштабирования через трети его вход 71 на третий вход элемента И 62 и на вторые входы элементов И 64, 66 и 68, а также в узел 3 выцеления выходных приращений через третий его вход 111,на второй вход элемента И 94 и разрешит выполнение в этом цифровом интеграторе 2 операции численного интегрирования. Начнется этап вычислений длительностью m тактов (счетчик 5 в это время изменяет свое состояние от Ш + 1) до (N+tri), в течение которого значение подынтегральной функции, представленное в модифицированном дополнительном двоичном коде, будет поступать с выхода регистра 31 младшими разрядами вперед на вход сумматора 28 и на первый вход 69 узла 26 масштабирования. В результате первая же единица в коде подынтегральной функции, являющаяся начальным импульсом, положение которого зависит от масштаба представления величин, поступит в узел 26 масштабирования через вход 69, через открытый элемент И 62 и, задержавшись на один такт на элементе 63 задержки, перебросит триггер 61 в единичное состояние, закрыв тем самым элемент И 62, и одновременно поступит через открытый элемент И 64 (на второй вход этого элемента, также как и на второй вход элементов И 66, 68 и третий вход элемента И 62 поступает через вход 71 из блока 6 сигнал, разрешающий вычисления) и через выход 72 во входной узел 27 в качестве первого мае- штабного импульса, соответствующего кванту подынтегральной функции, т.е. последнему младшему разряду. Кроме того, задержавшись на один такт на элементе 65 задержки, этот сигнал поступит в качестве второго масшт;бного импульса, соответствующего предпоследнему.разряду подынтегральной функции, через открытый элемент И 66 и через выход 72 тоже во входной узел 27, а задержавшись еще на один такт на элементе 67 задержки, этот сигнал поступит уже в качестве третьего масштабного импульса через открытый элемент И 68 и через выход 72 во входной узел 27. Одновременно одноразрядные приращения, представленные в тернарной системе кодирования, поступят .с выходов триггеров 13 положительных приращений и триггеров 14 отрицательных приращений в виде потенциалов, соответствующих +1 или -1, через группу входов 38 21 цифрового интегратора 2 и через груп пу входов 92 входного узла 27 на входы соответственно комбинационного сумматора 73 и комбинационного сумматора 78, Причем в комбинационном сумматоре 73 происходит суммирование положительнь х приращений, а в комбинационном сумматоре 78 - отрицательных приращений. Получившиеся суммы положительных приращений и отрицательных приращений поступают соответственно с вь ходов сумматора 73 и выходов сумматор.а 78 параллельным трехразрядным кодом (число разрядов в этих кодах, равное числу выходов из этих cyi iMaторов, не превьппает трех, так как число одновременно суммируемых прира щений подынтегральной функцииj а сле дов а теп ьн о, и число входов входного узла, т.е. число входов по подынтегральной функции цифрового интегратора, не превьпдает семи и на практике равно обычно 3-5) на первые входы соответственно элементов И 74-76 и элементов И 79-81, на вторые входы которых поступают с выхода 72 узла 26 масштабирования через вход 91 входного узла 27 первый, второй и третий масштабные импульсы в соответствии с весом разряда параллельного трехразрядного кода суммы при-ращений. Причем первый масштабный импульс, соответствующий кванту подынтегральной функции, т.е. последнему, младшему разряду, поступает на вторые входы элементов И 74 и 79, на первые входы которых поступают младшие разряды трехразрядных параллельных кодов соответственно положительных приращений и суммы отрицательных приращении, второй масштабный импульс, соответствующий предпоследнему разряду подынтегральной функции, поступает на вторые входы элементов И 75 и 80, на первые входы которых поступают средние раз .ряды трехразрядных параллельных кодо соответственно суммы положительньгх приращений и суммы отрицательных при ращений, а третий масштабный импульс так же как и старшие разряды трехраз рядных параллельных кодов сумм прирашений поступают на входы элементов И 76 и 81. В результате масштабные импульсы вырабатьшаемые узлом 26 масштабирования, приводят суммы положительных 21 22 и отрицательных приращений к масштабу подынтегральной функции данного модуля и переводят их из параллельного двоичного кода в последовательный. При этом количество масштабных сигналов,, вырабатьшаемых узлом 26, зависит так же, как и количество вькодов у сумматоров 73 и 78, от числа одновременно суммируемых приращений подынтегральной функции и практически не превышает трех, так как максимальное число одновременно суммируемых приращений подынтегральной функции как теоретически так И практически не превышает семи. Последовательный код суммы положительных приращений, приведенный к масштабу подынтегральной функции данного модуля, с выхода элемента ИЛИ 77 поступает на первьш вход комбинационного сумматора 89, а последовательный код суммы отрицательных приращений, поступаюи ий с выхода элемента ИЛИ 82, сначала преобразуется в дополнительный код, а ,потрм уже с выхода элемента ИЛИ 87 поступает на второй вход сумматора 89. Образование дополнительногчэ кода суммы отрицательньк приращений производится следующим образом. Первая единица в последовательном коде суммы отрицательных приращений, поступающая с выхода элемента ИЛИ 82, пройдет через открытый элемент И 84 (на второй вход этого элемента поступает единичный сигнал с нулевого выхода триггера 85, так как этот триггер был установлен в нулевое состояние при подготовке к решенню сигналом сброса) и поступит без изменения через элемент ИЛИ 87 на второй вход сумматора 89, а задержа.вщись на один такт на элементе 88 задержки, эта единица поступит на единичный вход триггера 85 и перебросит его в единичное состояние. В результате триггер 85 закроет элемент И 84 и откроет элемент И 86, и весь оставшийся последовательный код суммы отрицательных приращений, проинвертировавшись на элементе НЕ 83; поступит в инверсном виде через открытый элемент И 86 и элемент ШШ 87 на второй вход сумматора 89. Образованный таким образом ополнительный код суммы отрицательых приращений, поступающий с выхода элемента ИЛИ 87, просумьшруется на сумматоре 89 с суммой положительных приращении, поступающей с выхода элемента ИЛИ 77, и общая сумма прира щений подынтегральной функции поступит с выхода сумматора 89 на выход 93 входного узла 27. В цепь переноса сумматора 89 вклю чен однотактный элемент 90 задержки, служащий для образования поразрядног переноса при суммировании суммы поло жительных приращений с суммой отрицательных приращений. Полученная общая сумма входных приращений подынтегральной функции с выхода 93 входного узла 27 на вход сум матора 28, на другой вход которого поступает из регистра 31 значение подынтегральной функции. Б цепь пере носа этого сумматора 28 включен одно тактный элемент 29 задержки, служащи для образования переноса при сложени общей суммы входных приращений подын тегральной функции с текущим значени ем подынтегральной функции. Получающееся в результате суммирования на сумматоре 28 новое значение подынтегральной функции поступит в регистр 31 и на вход узла 30 умножения, где произойдет умножение этого значения подынтегральной функции на приращение переменной интегрирования, поступающее-на другой вход узла 30умножения с выхода соответст вующего триггера 13 или 14 через соответствующий вход 38 цифрового интегратора 2. Результат умножения поступит на вход сумматора 32 остатка интеграла, на другой вход которого поступает значение остатка интеграла из регистра 35. В цепь переноса сумматора 32 включен элемент 33 задержки, служаЕций для образования переноса при сложении р зультата умножения с текущим зйачением остатка интеграла, Полученное в результате суммирова ния на сумматоре 32 значение неквантованного приращения интеграла поступает на вход узла 34, где происходит вьщеление нового значения квантованного приращения интеграла, и в регистр 35, в который записывается выделяемый новый остаток интеграла, представляющий собой в соответствии с алгоритмомработы с одноразрядными приращениями значение нёквантованног приращения интеграла без знаковых разрядов, а знаковые разряды опреде,ляют значение квантованного приращения интеграла. Причем ВЕзщеление нового зн.ачения остатка интеграла производится, как уже отмечалось, использованием укороченного регистра, имеющего (т-2) разряда, и подачей из формирователя 6 с выхода триггера 55 (гп-2)-х тактного сигнала управления сдвигом, по которому в регистр 35 запишутся лишь числовые разряды без знаковых, и по (N+m+O-My такту дешифратор 16 выдаст через соответствующий вход из группы входов 58 и через элемент ИЛИ 53 на нулевой вход триггера 55 единичный сигнал, по которому триггер 55 формирователя 6 перейдет в нулевое состояние, и сдвиг информации в регистре 35 прекратится. Оставшиеся знаковые разряды, которые определяют значение квантованного приращения интеграла, анализируются в узле 34. Выполняется это следующим образом. Значение неквантованного приращения интеграла, поступаюище с выхода сумматора 32, пройдет через вход 109 узла 34 и поступит на вход элемента И 94. А так как на второй вход этого элемента И 94 поступает через вход 111 из формирователя 6 сигнал, разрешающий вычисления, то это значение неквантованного приращения интеграла пройдет через элемент И 94 и поступит на вход элемента 95 задержки, задерживается на этом элементе задержки на такт (эта задержка выполняется для того, чтобы первьш (старший) знаковый разряд совпал по времени с сигналом подготовки модуля к следующей итерации, появляющимся на выходе дешифратора 16 по окончании этапа вычислений в (Н+Пн-1)м такте) и поступает на вход элемента И 97 и через элемент НЕ 98 на вход элемента И 99, а задержавшись еще на один такт на элементе 96 задержки (эта задержка выполняется для того, чтобы и второй (младший) знаковый разряд, следующий на такт раньше первого (старшего) знакового разряда, совпал по времени с сигналом подготовки процес сора к следующей итерации, появляюШ5 мся на выходе дешифратора 16, как уже отмечалось, по окончанию этапа вычислений в (N+ni+1)-M такте с целью обеспечения возможности одновременного анализа обоих знаковых разрядов), поступает на вход элемента И 102 и через элемент НЕ 103 на вход элемента И 104, А на вторые входы элементов И 97, 99, 102 и 104 поступает по окончании этапа вычислений в (N+tn+-1)-M такте с выхода де шифратора 16 через вход 37 цифро ого интегратора 2 и через вход 111 узла 34 сигнал подготовки модуля к следующей интерации, так как счет чик 5 установится в этом такте тоже в состояние, равное (W+m+Oj и Б результате по этому сигналу триг геры 101 и 106 устанавливаются в ср тояния, соответствующие соответсТве но старшему и младшему знаковым раз рядам, т.е. триггер 101 будет анали зировать знак, а триггер 106 - пере полнение знакового разряда. Поскольку квантованные приращения интеграла являются одноразрядными и представляются в тернарной системе кодирования, то кодирование приращений осуществляется следующим образом 01 - +1, 11 - -1 и 00 - 0 т.е. если по сигналу подготовки моду ля к следующей итерации, появляющегося на выходе дешифратора 16 по око чании этапа вычислений в (Н+Гп+1)-м такте, триггер 101 устанавливается в Нулевое состояние, а триггер 106 в единичное, то на выходе элемента И 107 появится единичный сигнал длительностью одной итерации,соответ ствуклций положительному приращению интеграла +1, который через выход 112 узла 34 и через выход 39 цифрового интегратора 2 поступит на вход элемента И 9 положительных приращений; если же по сигналу подготов ки модуля к следующей интерации в (N+KD+D-M такте в единичное состояние устанавливаются оба триггера 101 и 106, то единичный сигнал длительностью одной итерации, соответствующей отрицательному приращению интеграла -1, появится на выходе элемен та И 108 и поступит через выход 112 узла 34 и через выход 39 цифрового интегратора 2 на вход элемента И 10 отрицательных.приращений . Если же оба триггера 101 и 106 окажутся в нулевом состоянии, то при ращения на выход 112 узла 34 выдаваться не будут, что соответствует .значению приращения интеграла, равного О. Одновременно в (N+m+1)-M такте из дешифратора 16 в блок 6 че2126рез соответствующий вход из группы входов 58 и через элемент ИЛИ 54 на нулевой вход триггера 56,. вьфабатывающего сигнал разрешения вычислений, поступит единичный сигнал, который перебросит этот триггер 56 блока 6 в нулевое состояние, прекращая тем подачу сигнала разрешения вычислений на вход 37 цифрового интегратора и завершая этап вычислений длительностью ,гп тактов. Кроме того, появившийся в ()-M такте 5 используемом для подготовки модуля к следующей итерации, на выходе дешифратора 16 вследствие того, что счетчик 5 устанавливается в состояние, равное (l+m+l), сигнал установки в исходное состояние поступит с выхода дешифратора 16 через элемент ИЛИ 15 на нулевые входы триггеров 13 и 14, подготавливая их к этапу передачи приращений в следующей итерации. Далее этот сигнал поступит через вход 37 цифрового интегратора 2 в узел 26 масштабирования через третий его вход 71 и через элемент ИЛИ 60 на нулевой вход триггера 61, устанавливая его в нулевое состояние, и с выхода элемента ИЛИ 60 этот сигнал поступит через выход 72 узла 26 и через вход 91 узла 27 на нулевой вход триггера 85, устанавливая его в нулевое состояние и подготавливая тем самым узел 26 и узел 27 к этапу вычислений в следующей итерации. Одновременно этот сигнал с выхода дешифратора 16, соответствующий состоянию счетчика 5, равному (N+tTi+1), поступит через выход .25 модуля в .центральное устройство управления иве и в случае совпадения этих сигналов, поступающих в центральное устройство управления ИВС с входов 25 всех модулей ИВС, свидетельствующем об отсутствиисбоев в процессе счета на первой итерации, центральное устройство управления ИВС продолжит выдавать импульсные сигналы на вхо.ды 20 всех модулей ИВС уже для следующей итерации. И первый же импульсный сигнал в первом такте следующей итерации перебросит счетчик 5 из состояния (M-(-tTi+1) в состояние, равное-единице (счетчик 5 является счетчиком по модулю (N+m+1), и. начнется вторая итерация, в течение которой за W тактов произойдет переадресация приращений и за № тактов 27. выполнится операция численного интегрирования, а в (N+in+1)-ft такт произойдет подготовка модуля к следующей интерации, а также контроль процесса счета центральным устройстном управления ИВС, и в случае отсутствия сбоев в процессе счета центральное устройство управления ИВ продожит выдавать импульсные сигналы на вход 20, и в следующем такте счетчик 5 перейдет из состояния (Л/+-т + 1) в состояние, равное единице, и начнется новая итерация и т.д. В случае же если при контроле процесса счета в (N+m+1)-M такте какой-либо итерации центральньй устройством управления -ИВС будет обнаружено отсутствие в этом такте сигнала с выхода 25 хотя бы одного модуля ИВС, что свидетельствует о наличии сбоя в процессе счета, центральное устройство управления ИВС прекратит 21 вьщавать импульсные сигналы на входы 20 модуля, и процесс решения будет остановлен. Таким образом, предлагаемый модуль ИВС наряду с выполнением функции численного интегрирования обеспечивает возможность универсальной коммутации, т.е. любой вход любого модуля может быть соединен с любым выходом любого модуля, задав соответствующий адрес в регистр адреса входных приращений. В то же время в сравнении с известным модулем ИВС затраты оборудования на предлагаемый модуль с учетом реализации его на современных комплексах микросхем не превышает затраты на известный модуль, что позволяет создавать на его основе ИВС такой же вычислительной мощности, что и известный модуль, но обеспечение универсальности коммутации при этом значительно упростит программирование задачи и сократит время подготовки задачи к решению

25

/7 18 W

Фг/з. 7

Фиг. 2

Фиг. 8

| Т | |||

| Решающий блок цифровой интегрирующей структуры | 1976 |

|

SU650085A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

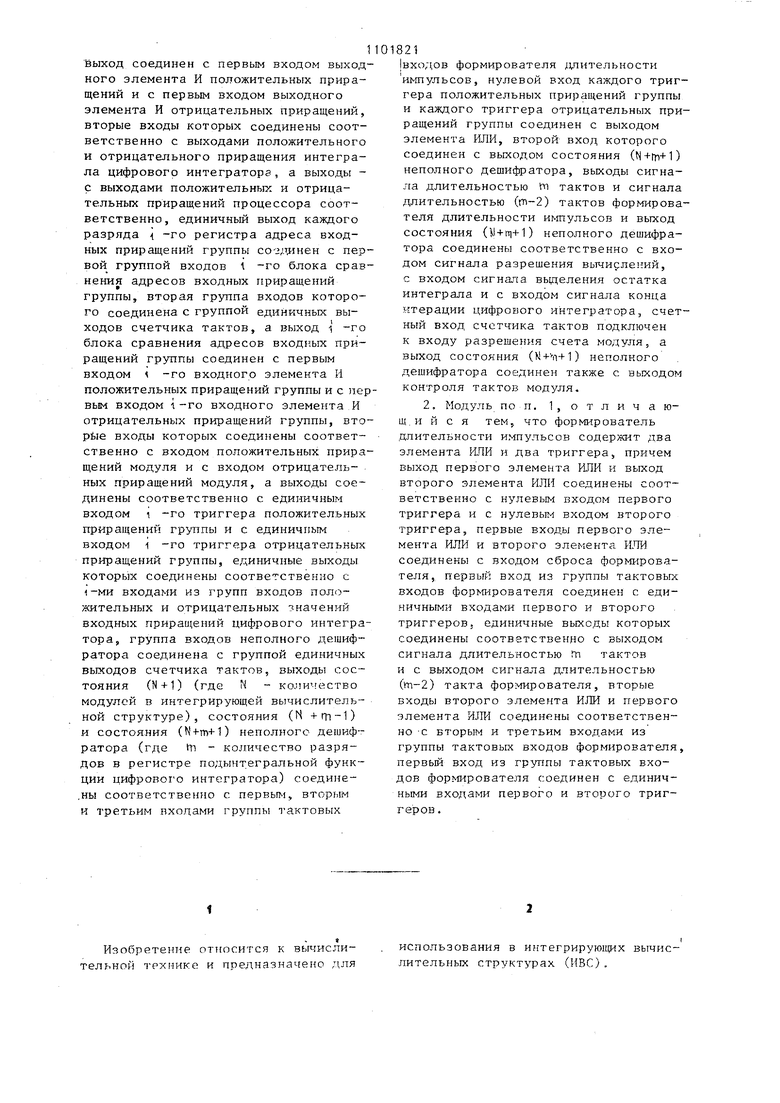

Авторы

Даты

1984-07-07—Публикация

1982-07-26—Подача