Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для решения обратных задач, и может быть использовано для восстановления сигналов методом обратной фильтрации.

Цель изобретения - повышение точности восстановления сигналов.

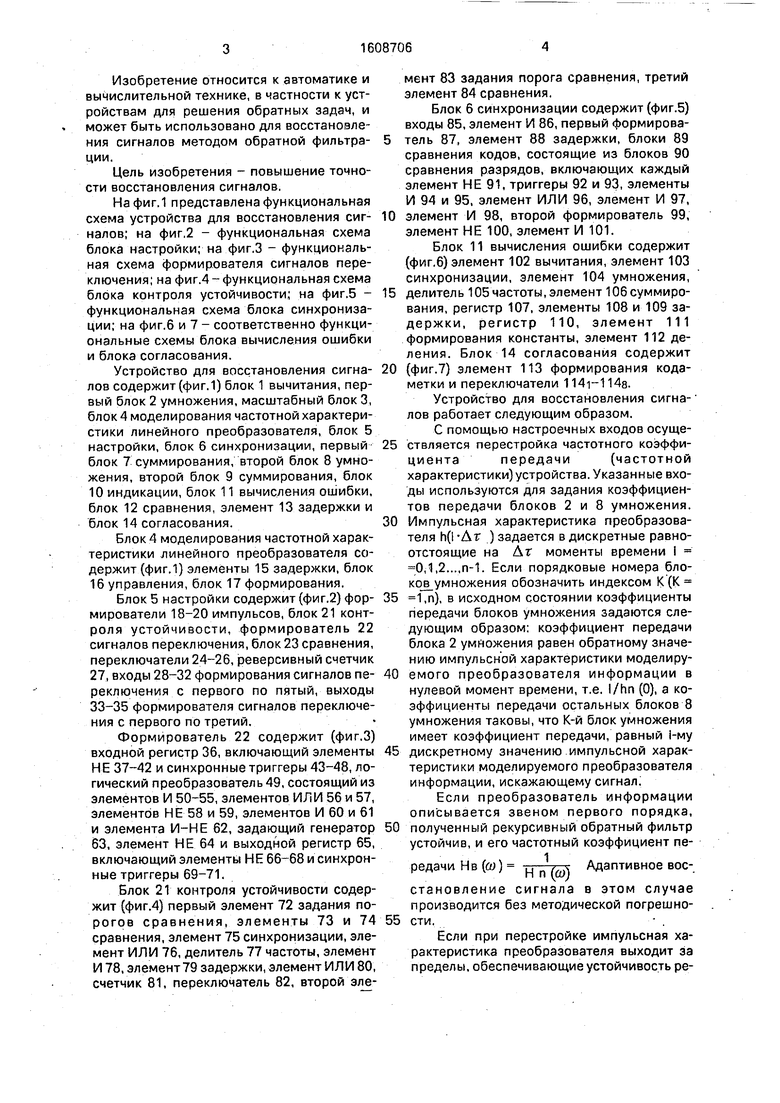

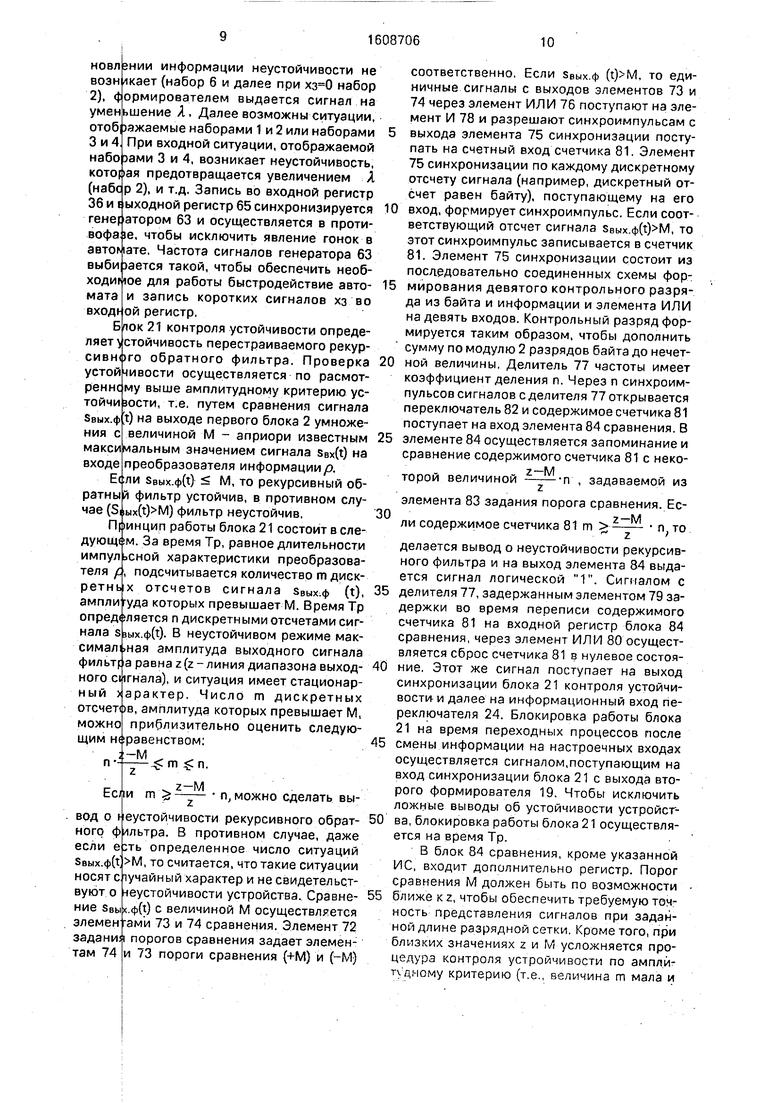

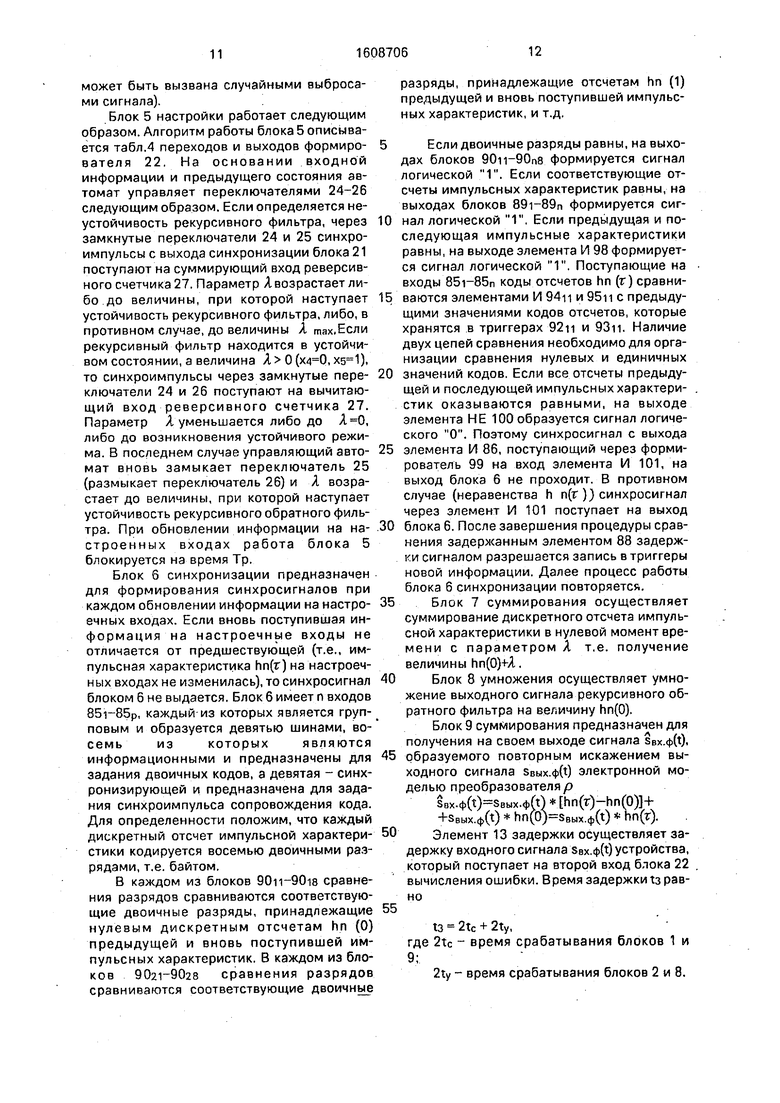

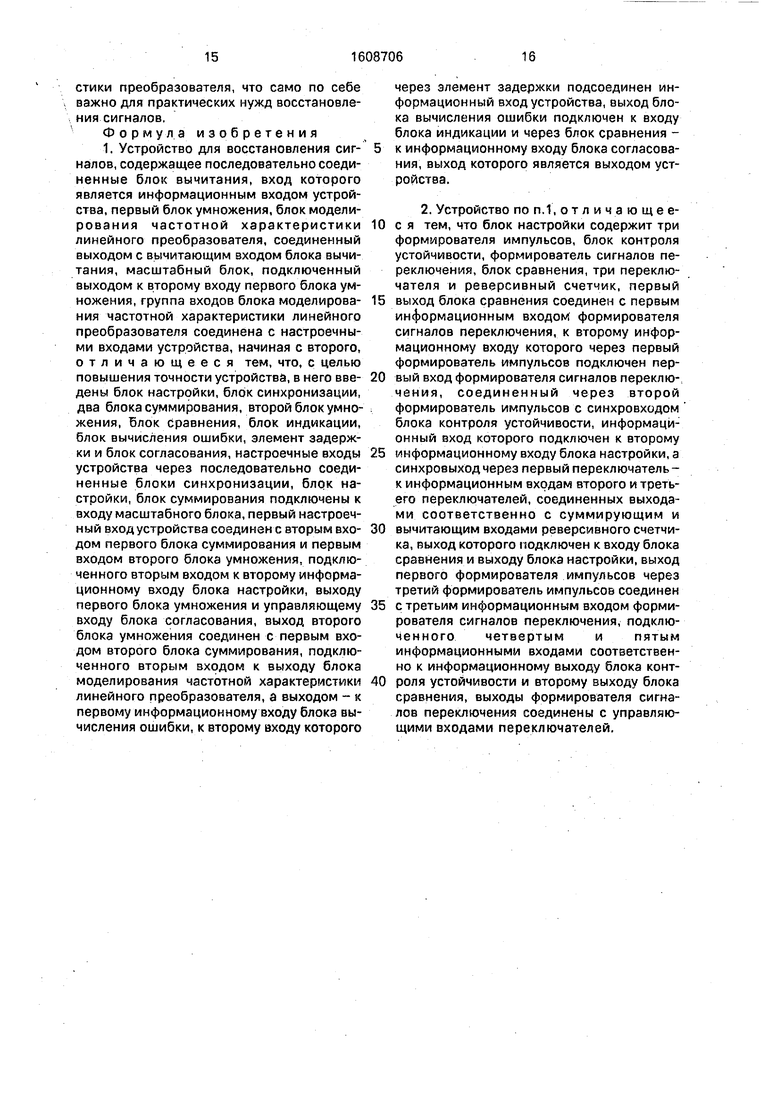

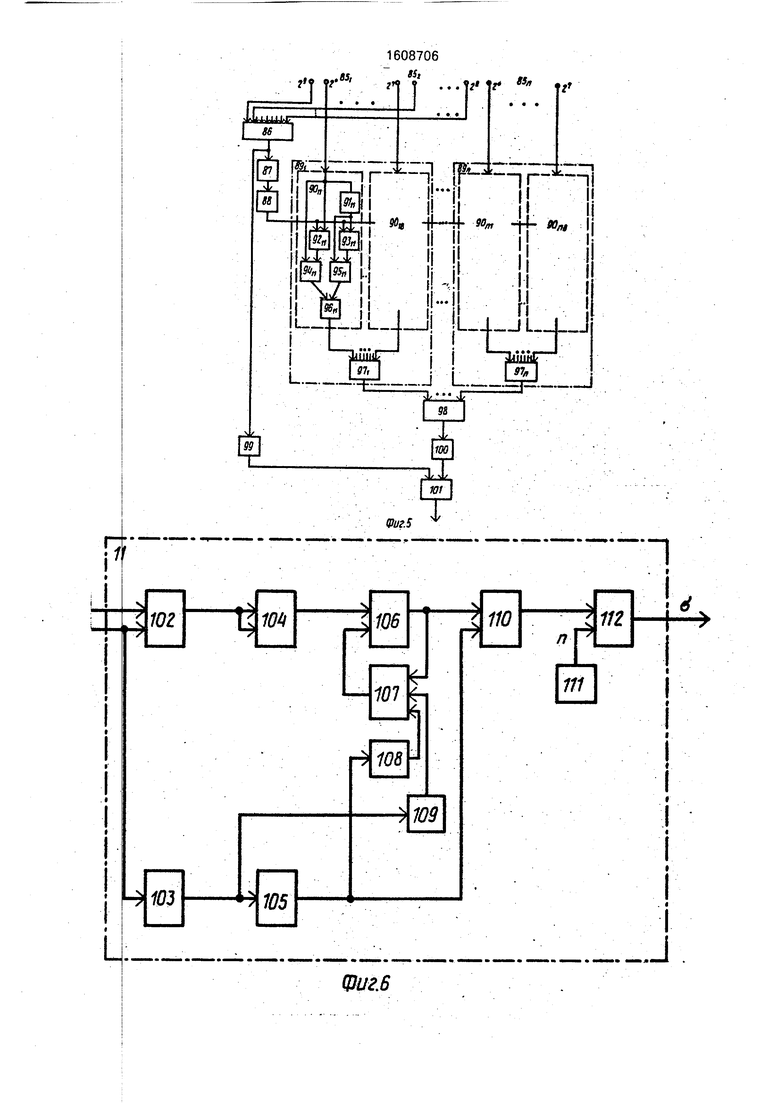

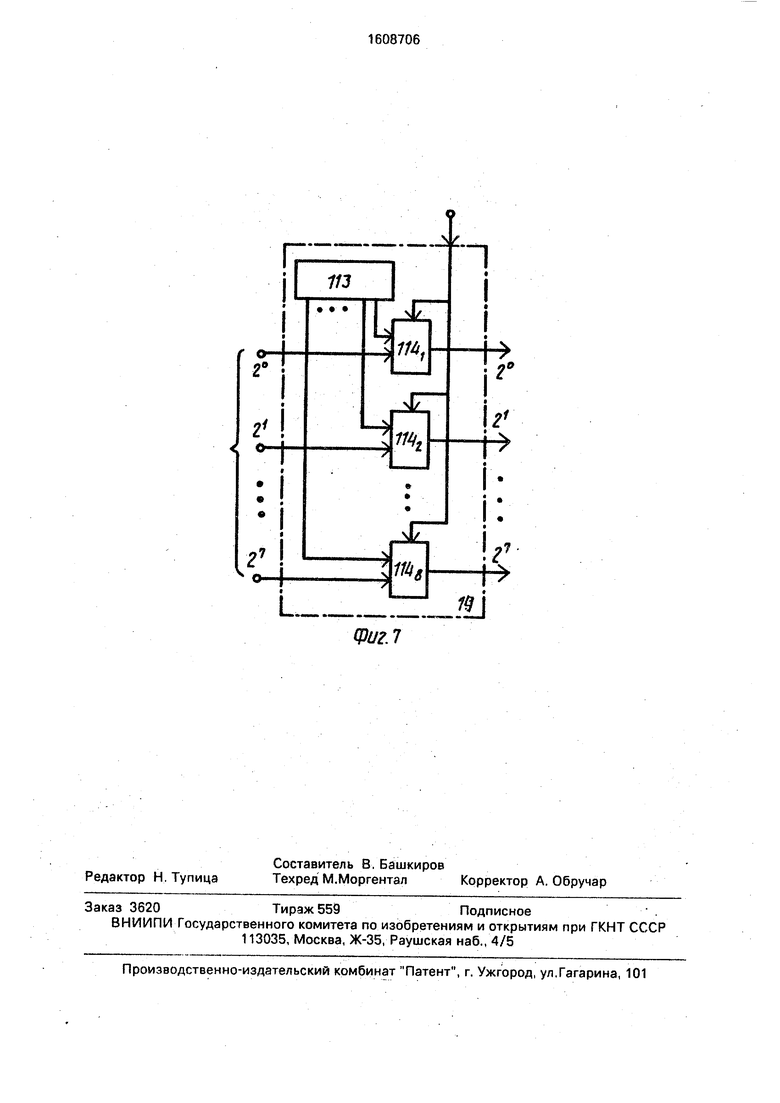

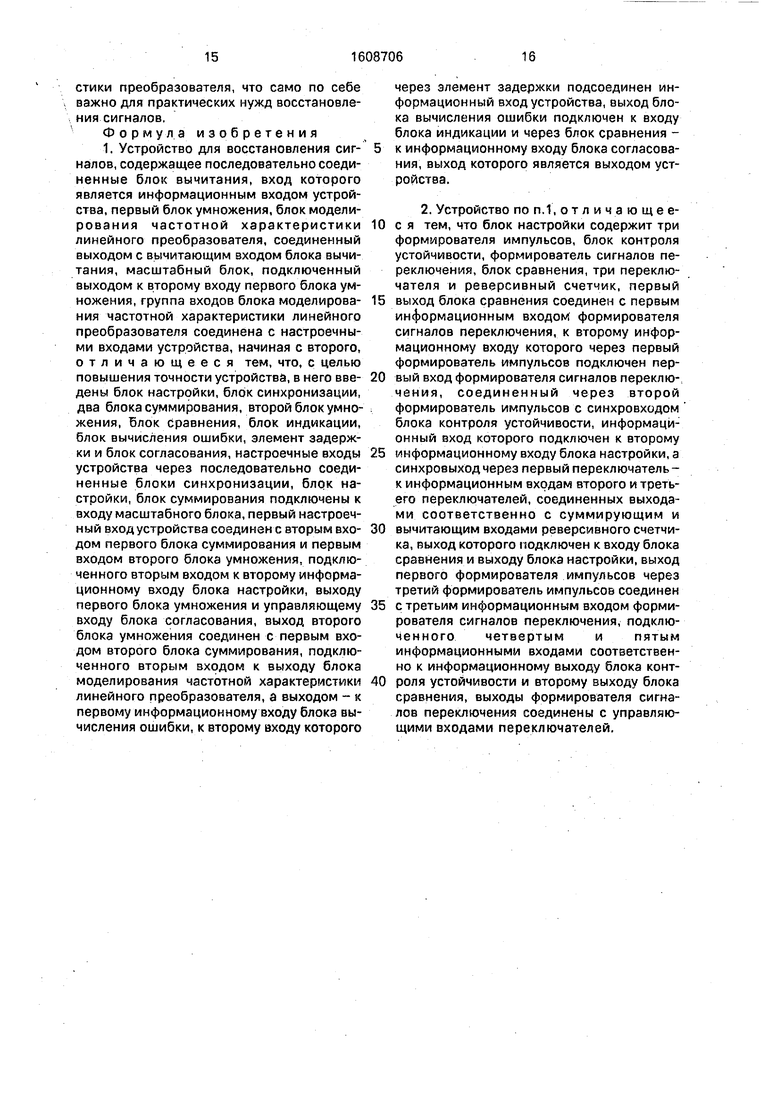

На фиг.1 представлена функциональная схема устройства для восстановления сигналов; на фиг.2 - функциональная схема блока настройки; на фиг.З - функциональная схема формирователя сигналов переключения; на фиг.4 - функциональная схема блока контроля устойчивости; на фиг.5 - функциональная схема блока синхронизации; на фиг.6 и 7 - соответственно функциональные схемы блока вычисления ошибки и блока согласования.

Устройство для восстановления сигналов содержит (фиг.1) блок 1 вычитания, первый блок 2 умножения, масштабный блок 3, блок 4 моделирования частотной характеристики линейного преобразователя, блок 5 настройки, блок 6 синхронизации, первый блок 7 суммирования, второй блок 8 умножения, второй блок 9 суммирования, блок 10 индикации, блок 11 вычисления ошибки, блок 12 сравнения, элемент 13 задержки и блок 14 согласования.

Блок 4 моделирования частотной характеристики линейного преобразователя содержит (фиг.1) элементы 15 задержки, блок 16 управления, блок 17 формирования.

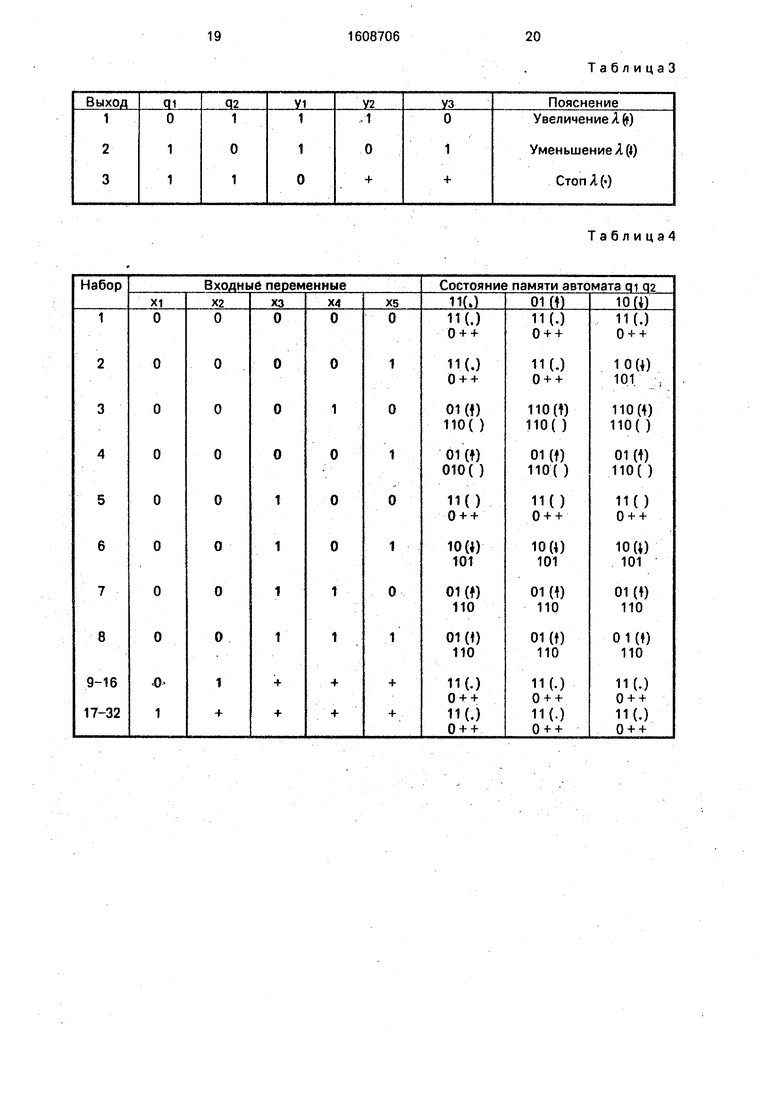

Блок 5 настройки содержит (фиг.2) формирователи 18-20 импульсов, блок 21 контроля устойчивости, формирователь 22 сигналов переключения, блок 23 сравнения, переключатели 24-26, |эеверсивный счетчик 27, входы 28-32 формирования сигналов переключения с первого по пятый, выходы 33-35 формирователя сигналов переключения с первого по третий. Формирователь 22 содержит (фмг.З) входной регистр 36, включающий элементы НЕ 37-42 и синхронные триггеры 43-48, логический преобразователь 49, состоящий из элементов И 50-55, элементов ИЛИ 56 и 57, элементов НЕ 58 и 59, элементов И 60 и 61 и элемента И-НЕ 62, задающий генератор 63, элемент НЕ 64 и выходной регистр 65, включающий элементы НЕ 66-68 и синхронные триггеры 69-71.

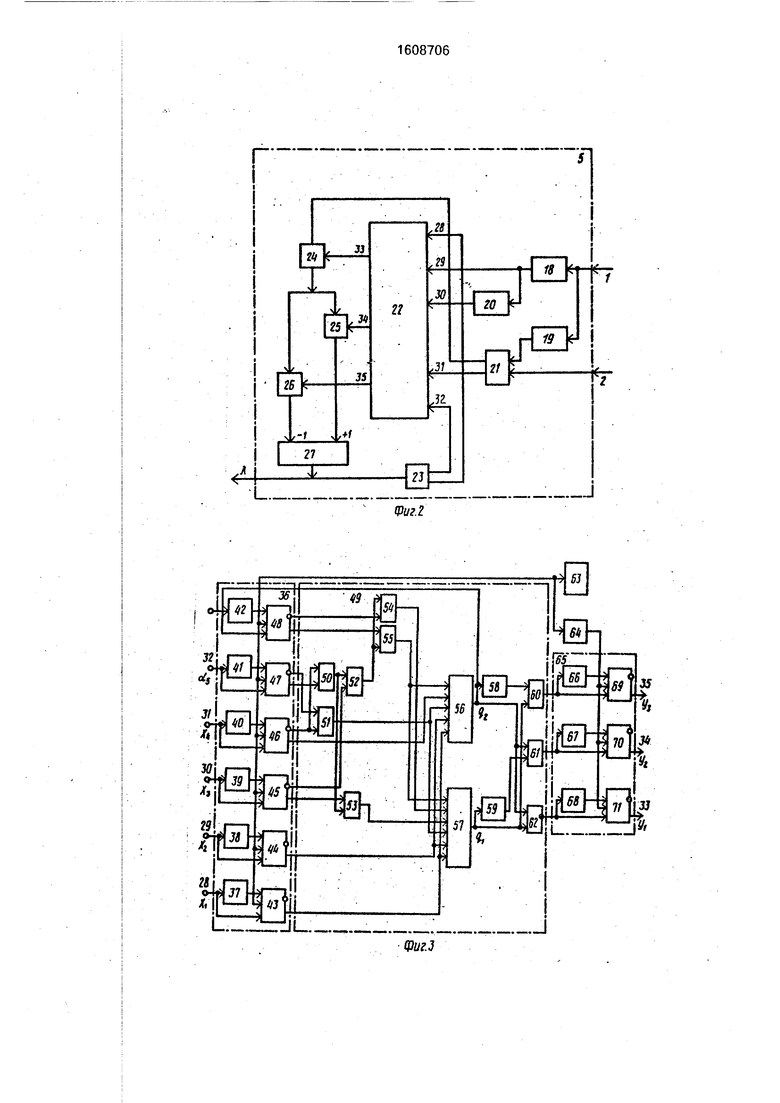

Блок 21 контроля устойчивости содержит (фиг.4) первый элемент 72 задания порогов сравнения, элементы 73 и 74 сравнения,элемент 75 синхронизации,элемент ИЛИ 76, делитель 77 частоты, элемент И 78, элемент 79 задержки, элемент ИЛИ 80, счетчик 81, переключатель 82, второй элемент 83 задания порога сравнения, третий элемент 84 сравнения.

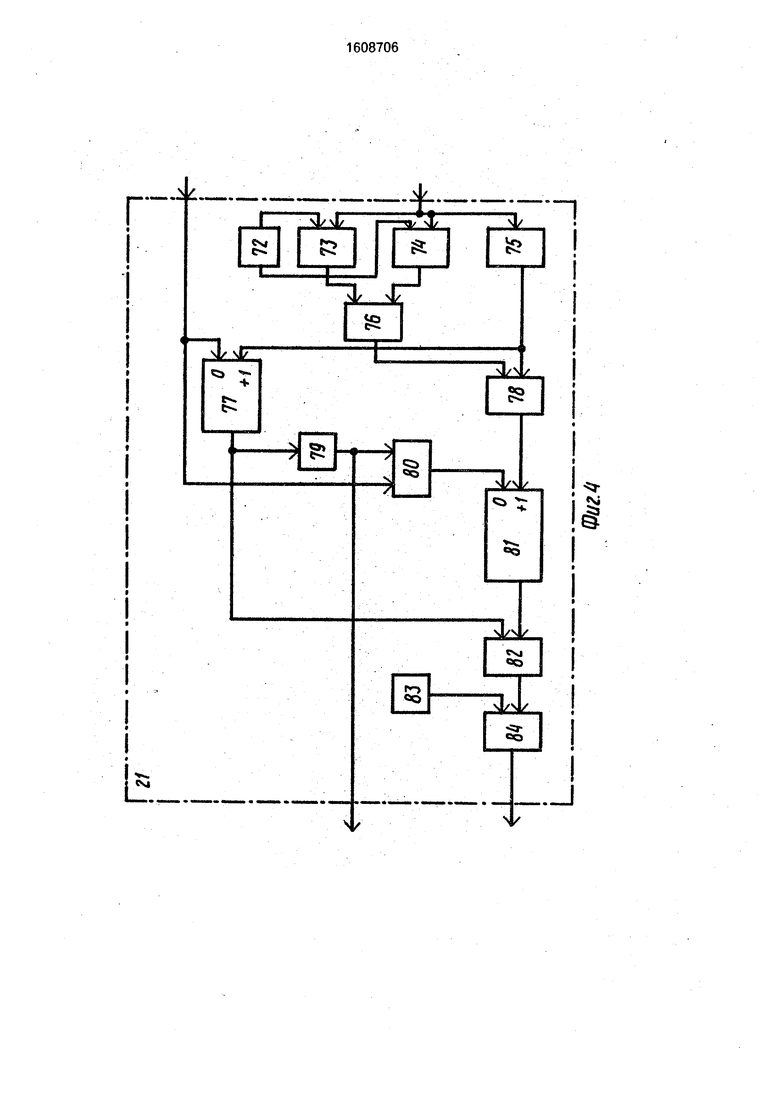

Блок 6 синхронизации содержит (фиг.5) входы 85, элемент И 86, первый формирователь 87, элемент 88 задержки, блоки 89 сравнения кодов, состоящие из блоков 90 сравнения разрядов, включающих каждый элемент НЕ 91, триггеры 92 и 93, элементы И 94 и 95, элемент ИЛИ 96, элемент И 97,

элемент И 98, второй формирователь 99, элемент НЕ 100, элемент И 101.

Блок 11 вычисления ошибки содержит (фиг.6) элемент 102 вычитания, элемент 103 синхронизации, элемент 104 умножения,

делитель 105 частоты, элемент 106 суммирования, регистр 107, элементы 108 и 109 задержки, регистр 110, элемент 111 формирования константы, элемент 112 деления. Блок 14 согласования содержит

(фиг.7) элемент 113 формирования кода- метки и переключатели 114i-1148.

Устройство для восстановления сигна- лов работает следующим образом.

С помощью настроечных входов осуществляется перестройка частотного коэффициентапередачи(частотной характеристики)устройства. Указанные входы используются для задания коэффициентов передачи блоков 2 и 8 умножения.

Импульсная характеристика преобразователя h(l -Лт ) задается в дискретные равноотстоящие на Аг моменты времени I 0,1,2...,п-1. Если порядковые номера бло- ко в умножения обозначить индексом К (К

1,п), в исходном состоянии коэффициенты передачи блоков умножения задаются следующим образом: коэффициент передачи блока 2 умножения равен обратному значению импульсной характеристики моделируемого преобразователя информации в нулевой момент времени, т.е. l/hn (0), а коэффициенты передачи остальных блоков 8 умножения таковы, что К-й блок умножения имеет коэффициент передачи, равный 1-му

дискретному значению импульсной характеристики моделируемого преобразователя информации, искажающему сигнал;

Если преобразователь информации описывается звеном первого порядка,

полученный рекурсивный обратный фильтр устойчив, и его частотный коэффициент пе1

редачи Нв (w) ., /ч Адаптивное восстановление сигнала в этом случае производится без методической погрешно- сти.

Если при перестройке импульсная характеристика преобразователя выходит за пределы, обеспечивающие устойчивость рекурсивного

вость

тойч

настройки

погрешность

неустойчивом

Бюк

обратного фильтра, устойчи- фильтра нарушается. Факт потери ус- 1ВОСТИ определяется блоком 5 В этом случае резко возрастает а восстановления, так как в 1 фильтре нарушается связь выходных и входных сигналов.

14 выдает на выход устройства тку, свидетельствующую о нерабо- ;обности устройства. Блок 5 настрой- чинает .корректировать частотную харак|геристику блока 4 моделирования, ее на параметр А Далее возможны С1/|туации, При первой увеличение пара- приводит к возникновению устой- дальнейшее увеличение Я . При возникновении устойчиво- решность а уменьшается и если ста- равной сг С где С - допустимая восстановления, блок 17 раз- передачу выходных сигналов филь- выход устройства. Производится явление сигналов с некоторой мето- ой ошибкой. Частотная характери- 5(|стройства в этом случае равна

) нЯ-да

рой ситуации увеличение не прикод-мтоспоЬ ки нг ак смещс1Я две метра чивос

ги,

прекрг щается. сти по новится погреьжость решае тра нг восста дическ|ой стика

Нв

При втс водит к достиж

ТрОЙСТЕ о

тех пор, рактер / пределы ность

Есл устойчи зость стройки процесс

Если вом ции на потере уменьш ситуации ся napaN нулю,

бе

|И

мож

ится

том

меньше 1ие араметр има, чтс стойчивости и устойчивости

.-J-.ч..ж.ч -VllV tl (Jrl

возникновению устойчивости и при ении Д значения Я Я ах блок 5 настро(11ки блокирует работу устройства. Ус- переходит в режим ожидания до пока изменяющаяся частотная ха- рактер1 стика преобразователя не войдет в обеспечивающие работоспособ- устройства.

1 при перестройке характеристики 4ость вновь нарушается, блок 5 на- снова дает приращение Я и далее происходит, как описано выше, I устройство находится в устойчи- режлме работы и обновление информа- настроечных входах не приводит к устойчивости, блок 5 настройки 4етЯ При этом также возможны две 1. При первой, если уменьшающий- етрЯ достигнет значения, равного блок 5 прекращает дальнейшее меньшение Я Восстановление произво- J методической погрешности, второй ситуации при уменьшении гт возникнуть неустойчивость. В слу|1ае блок 5 настройки прекращает Я и начинает увеличивать этот до возникновения устойчивого ре- определяется блоком 21 контроля - блока 5. Во всех случаях поте- ;ти передача выходных сигна- на выход устройства

40

45

50

55

10

15

20

5

0

5

запрещается, и выходными сигналами уст-- ройства является последовательность кодов меток. Указанные помеченные бракованные массивы информации легко исключаются из дальнейшей обработки например, в ЭВМ.

Формирователь 22 реализует алгоритм вычисления параметра Я на основании информации, поступающей на его входы с выходов первого 18, второго 19 и третьего 20 формирователей, блока 21 контроля устойчивости и блока 23 сравнения.

Выходные сигналы формирователя 22 управляют процессом заполнения реверсивного счетчика 27 с помощью переключателей 24-26. Код, получаемый в счетчике 27 является параметром Яи поступает раллельным кодом на выход блока 5 настройки. По сигналам, поступающим на первый вход блока 5 из блока 6 синхронизации, формирователи 18 и 19 формируют импульсные сигналы заданной длительности Сигнал с выхода второго формирователя 19 блокирует работу блока 21 контроля устойчивости на время, в течение которого в основном завершаются переходные процессы в рекурсивном обратном фильтре, вызванные сменой кодов на настроечных входах (т.е., перестройкой фильтра).

Положим, что переходный процесс практически завершается (выходной сигнал фильтра принимает практически установившееся значение) за время, равное Длительности импульсной характеристики Тр блока 4 моделирования частотной характеристики преобразователя, т.е. Тр (п-1) -Дг где Лт- 1/fg, а fg - частота дискретизации во времени импульсной характеристики hn(r) преобразователя и входного сигнала устройства. Возможность такого ограничения следует из сделанного допущения, что динамические характеристики преобразователя р являются квазистационарными, т.е. медленно изменяющимися во времени Поэтому hn(r) можно считать неизменными на интервалах времени, соизмеримыми с Тр Если информация на настроечных входах устройства обновляется достаточно часто например через время Тс, равное

Тс дТр, 1 д 3...5...10, то последующие импульсные характеристики преобразователя будут сравнительно мало отличаться от импульсных характеристик преобразователя в предыдущие моменты времени. По этой причине погрешность вносимая переходными процессами в выходной сигнал устройства, будет также небольшой, и через время Тр будем считать эту погрешность несущественной. Поэтому по

каждому сигналу с выхода блока 6 синхронизации, свидетельствующему о смене информации на входах, второй формирователь 19 вырабатывает импульсный сигнал длительностью Тр, запрещающий работу блока 21 контроля устойчивости на время Тр, Эта процедура предотвращает появление ложного сигнала на выходе блока 21 о нарушении устойчивости. Блок 21 вырабатывает сигнал об устойчивости фильтра через время Тр после снятия сигнала запрета на входе синхронизации. Импульсный сигнал длительностью 2 Тр с выхода первого формирователя 18 запрещает работу формирователя 22 на время 2Тр после смены информации на настроечных входах устройства. Это время складывается из времени длительности переходного процесса и времени работы блока 21. Третий формирователь 20 вырабатывает импульсный сигнал по заднему фронту запрещающего импульса с выхода формирователя 18. Этот сигнал поступает на третий вход формирователя 22 и указывает на факт смены информации на настроечных входах устройства. Это короткий импульсный сигнал длительностью, достаточной для записи во входной регистр.

С помощью переключателей 24-26 формирователь 22 управляет процессом заполнения реверсивного счетчика 27 импульсами с выхода синхронизации блока

21контроля устойчивости. Переключатель 24, управляемый сигналом с первого выхода управляющего автомата, разрешает или запрещает передачу сигналов на вычитающий и суммирующий входы реверсивного счетчика 27. Переключателем 25 формирователь

22управляет поступлением импульсов на суммирующий вход реверсивного счетчика 27. Управляющий вход переключателя 25 подключен к второму входу формирователя 22. Переключатель 26 формирователя 22 управляет поступлением импульсов на вцчи- тающий вход реверсивного счетчика 27.

На первом выходе блока 23 сигнал логической 1 вырабатывается при А А max и сигнал логического О - в противном случае. На втором выходе блока 23 сигнал логической 1 вырабатывается при А О и сигнал логического О - в противном случае. Для описания работы блока 5 настройки предварительно рассмотрим функциональные схемы формирователя 22 и блока 21 контроля устойчивости. Формирователь 22 является синхронным конечным автоматом. Работа формирователя синхронизируется задающим генератором.

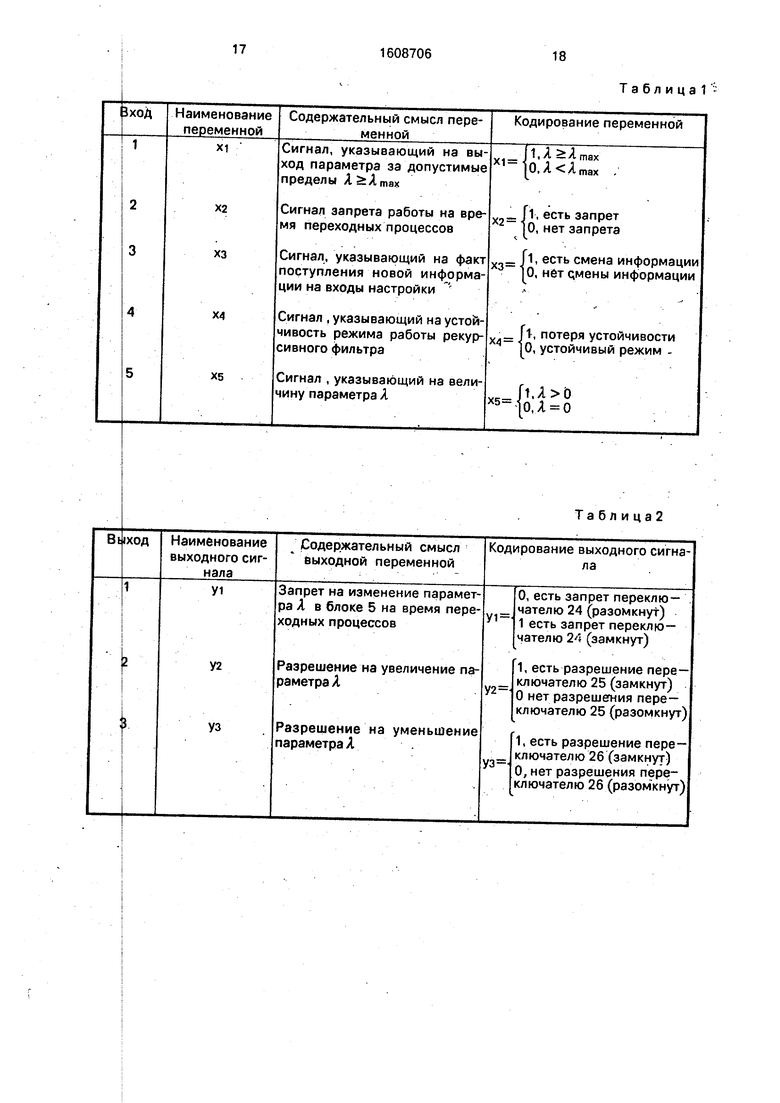

Входные переменные Х1-Х5 формирователя 22 определяют следующим образом (табл.1).

Состояние формирователя обозначим переменными qi и q2, которые могут принимать два значения: О и 1.

Выходные переменные (сигналы) у1, у2, уз формирователя 22 определяют следующим образом (табл.2)

Выходные сигналы yi, У2, уз связаны с промежуточными выходами переменными 91 и 92 следующим образом (табл.3). Функционирование формирователя 22 описано в табл.4, где для каждого набора входных переменных xi-x5 и состояний автомата qi и q2 указаны: состояния, в которые автомат переходит (верхняя часть клетки), 5 условное обозначение этих состояний и выходные сигналы (нижняя часть клетки).

В табл.4 приняты следующие обозначения: (+) любое значение О или 1, (.) стоп, изменение АДг) увеличение А, () уменьше0 ние А

Схема формирователя 22 синтезирована на основе табл.4. Как видно из табл.4, от состояния памяти зависят выходные сигналы только набора 2, причем от сигнала Р2.

5 Поэтому емкость памяти -1 бит (Тг 48).

Формирователь 22 работает следующим образом. При обновлении информации на настроечных входах по сигналу (наборы 9-16) блокируется работа, значение А

0 не изменяется. При поступлении сигнала (сигнал обновления информации на входах 6i-6n), если возникла неустойчивость (набор 7), выдается сигнал на увеличение А, Этот сигнал продолжает действовать

5 и при (набор 3). Увеличение А продолжается до получения устойчивого состояния (набор 2), при котором увеличение А прекращается (если предыдущее состояние автомата было А (i). Погрешность восстановления сг

0 вычисляемая блоком 11, в неустойчивом режиме велика (выходной сигнал устройства Звых.ф (t) практически не определяется входным сигналов Звх.ф (t)), но при достижении устойчивости погрешность ст существенно

5 уменьшается. Но увеличение А не всегда может вернуть устройству устойчивость, поэтому, если возрастающий параметр А становится

А А max Т.е. XI 1,

50 дальнейшая работа формирователя 22 блокируется (наборы 17-32), так как в дальнейшем увеличении А нет смысла; поскольку о превышает допустимое значение. Если снова при обновлении информации возник55 ла неустойчивость (набор 8), выдается сигнал на дальнейшее увеличение А, далее входная ситуация отображается набором 4, затем набором 2, на котором вьгдается сигнал запрета на изменение А Если при обновле

возн

2).

ото б Зи4 набоЬами

(набо 36 и Е гене вофа

мата аходь

вых.ф ния с

входе Е(

ратны|й чае (Si

импул теля /: ретнь

ампли

нала

симал

фильт|;

ного

ный

отсчетов

можно

щим

п1НИИ информации неустойчивости не 1кает (набор 6 и далее при набор (} 0рмирователем выдается сигнал на

уменьшение Я, Далее возможны ситуации )ажаемые наборами 1 и 2 или наборами При входной ситуации, отображаемой )ами 3 и 4, возникает неустойчивость

KOTOfj)aH предотвращается увеличением Л . 2), и т.д. Запись во входной регистр ыходной регистр 65 синхронизируется атором 63 и осуществляется в проти- 5е, чтобы исключить явление гонок в

автомате. Частота сигналов генератора 63 )ается такой, чтобы обеспечить необходифое для работы быстродействие авто-

запись коротких сигналов хз во ой регистр.

21 контроля устойчивости определяет устойчивость перестраиваемого рекурсивного обратного фильтра. Проверка ycтoй ивocти осуществляется по расмот- му выше амплитудному критерию ус- тойчизости, т.е. путем сравнения сигнала t) на выходе первого блока 2 умноже- величиной М - априори известным максимальным значением сигнала SBx(t) на преобразователя информации/. ;ли 8вых.ф(т) М, то рекурсивный об- фильтр устойчив, в противном слу- ibix(t)M) фильтр неустойчив. П инцил работы блока 21 состоит в сле- . За время Тр, равное длительности .сной характеристики преобразова- подсчитывается количество m диск- X отсчетов сигнала 8вых;ф (t), уда которых превышает М. Время Тр опредфляется п дискретными отсчетами сиг- :.ф(г). В неустойчивом режиме мак- ная амплитуда выходного сигнала а равна z (z - линия диапазона выход- сигнала), и ситуация имеет стационар- арактер. Число m дискретных , амплитуда которых превышает М, приблизительно оценить следую- н равенством:

.

SBBIXJ

Если m

z-M

n, можно сделать вывод о

ного

если

Звых.

Звык

вуют о ние

элемен задаНИЛ там 74

.ф(t носят случайный:

fеустойчивости рекурсивного обрат- ф/1льтра. В противном случае, даже ;ть определенное число ситуаций М, то считается, что такие ситуации характер и не свидетельст- eycтoйчивocти устройства. Сравне- к.ф(1) с величиной М осуществляется ами 73 и 74 сравнения. Элемент 72 порогов сравнения задает элемен- и 73 пороги сравнения (+М) и (М)

5

10

15

20

5

соответственно. Если 8вых.ф (t)M, то единичные сигналы с выходов элементов 73 и

74через элемент ИЛИ 76 поступают на элемент И 78 и разрешают синхроимпульсам с выхода элемента 75 синхронизации поступать на счетный вход счетчика 81. Элемент

75синхронизации по каждому дискретному отсчету сигнала (например, дискретный отсчет равен байту), поступающему на его вход, формирует синхроимпульс. Если соот- ветствующий отсчет сигнала 5вых.ф(г)М, то этот синхроимпульс записывается в счетчик 81. Элемент 75 синхронизации состоит из посяедовательно соединенных схемы формирования девятого контрольного разряда из байта и информации и элемента ИЛИ на девять входов. Контрольный разряд формируется таким образом, чтобы дополнить сумму по модулю 2 разрядов байта до нечетной величины. Делитель 77 частоты имеет коэффициент деления п. Через п синхроимпульсов сигналов с делителя 77 открывается переключатель 82 и содержимое счетчика 81 поступает на вход элемента 84 сравнения В элементе 84 осуществляется запоминание и сравнение содержимого счетчика 81 с некоторой величиной ---п

задаваемой из

30

элемента 83 задания порога сравнения. Если содержимое счетчика 81 m

35

40

5

0 5

п то

делается вывод о неустойчивости рекурсивного фильтра и на выход элемента 84 выдается сигнал логической 1. Сигналом с делителя 77, задержанным элементом 79 задержки во время переписи содержимого счетчика 81 на входной регистр блока 84 сравнения, через элемент ИЛИ 80 осуществляется сброс счетчика 81 в нулевое состояние. Этот же сигнал поступает на выход синхронизации блока 21 контроля устойчивости и далее на информационный вход переключателя 24. Блокировка работы блока 21 на время переходных процессов после смены информации на настроечных входах осуществляется сигналом,поступающим на вход синхронизации блока 21 с выхода второго формирователя 19. Чтобы исключить ложные выводы об устойчивости устройства, блокировка работы блока 21 осуществляется на время Тр.

В блок 84 сравнения, кроме указанной ИС, входит дополнительно регистр. Порог сравнения М должен быть по возможности ближе к Z, чтобы обеспечить требуемую точность представления сигналов при заданной длине разрядной сетки. Кроме того, при близких значениях z и М усложняется процедура контроля устройчивости по амплитудному критерию (т.е., величина m мала и

может быть вызвана случайными выбросами сигнала).

Блок 5 настройки работает следующим образом. Алгоритм работы блока 5 описывается табл.4 переходов и выходов формирователя 22. На основании входной информации и предыдущего состояния автомат управляет переключателями 24-26 следующим образом. Если определяется неустойчивость рекурсивного фильтра, через замкнутые переключатели 24 и 25 синхроимпульсы с выхода синхронизации блока 21 поступают на суммирующий вход реверсивного счетчика 27. Параметр Л возрастает либо до величины, при которой наступает устойчивость рекурсивного фильтра, либо, в противном случае, до величины Я тах.Если рекурсивный фильтр находится в устойчивом состоянии, а величина Я О (, ), то синхроимпульсы через замкнутые переключатели 24 и 26 поступают на вычитающий вход реверсивного счетчика 27. Параметр Я уменьшается либо до , либо до возникновения устойчивого режима. В последнем случае управляющий автомат вновь замыкает переключатель 25 (размыкает переключатель 26) и Я возрастает до величины, при которой наступает устойчивость рекурсивного обратного фильтра. При обновлении информации на настроенных входах работа блока 5 блокируется на время Тр.

Блок 6 синхронизации предназначен для формирования синхросигналов при каждом обновлении информации на настроечных входах. Если вновь поступившая информация на настроечные входы не отличается от предшествующей (т.е., импульсная характеристика hn(r) на настроечных входах не изменилась), то синхросигнал блоком 6 не выдается. Блок 6 имеет п входов 85i-85p, каждый из которых является групповым и образуется девятью шинами, восемь из которых являются информационными и предназначены для задания двоичных кодов, а девятая - синхронизирующей и предназначена для задания синхроимпульса сопровождения кода. Для определенности положим, что каждый дискретный отсчет импульсной характеристики кодируется восемью двоичными разрядами, т.е. байтом.

В каждом из блоков 90ii-90i8 сравнения разрядов сравниваются соответствующие двоичные разряды, принадлежащие нулевым дискретным отсчетам hn (0) предыдущей и вновь поступившей импульсных характеристик. В каждом из блоков 9021-9028 сравнения разрядов сравниваются соответствующие двоичнь1е

азряды, принадлежащие отсчетам hn (1) редыдущей и вновь поступившей импульсых характеристик, и т.д.

Если двоичные разряды равны, на выхоах блоков 90ii-90n8 формируется сигнал огической 1. Если соответствующие отчеты импульсных характеристик равны, на выходах блоков 89i-89n формируется сигнал логической 1. Если предыдущая и последующая импульсные характеристики равны, на выходе элемента И 98 формируется сигнал логической 1. Поступающие на входы 85i-85n коды отсчетов hn (т) сравниваются элементами И 94ii и 95ii с предыдущими значениями кодов отсчетов, которые хранятся в триггерах 92ii и 93ii. Наличие двух цепей сравнения необходимо для организации сравнения нулевых и единичных

значений кодов. Если все отсчеты предыдущей и последующей импульсных характеристик оказываются равными, на выходе элемента НЕ 100 образуется сигнал логического О. Поэтому синхросигнал с выхода

элемента И 86, поступающий через формирователь 99 на вход элемента И 101, на выход блока 6 не проходит. В противном случае (неравенства h n(r )} синхросигнал через элемент И 101 поступает на выход

блока 6. После завершения процедуры сравнения задержанным элементом 88 задержки сигналом разрешается запись в триггеры новой информации. Далее процесс работы блока 6 синхронизации повторяется.

Блок 7 суммирования осуществляет

суммирование дискретного отсчета импульсной характеристики в нулевой момент вре- мени с параметром Я т.е. получение величины hn(0)+Я.

Блок 8 умножения осуществляет умножение выходного сигнала рекурсивного обратного фильтра на величину hn(0).

Блок 9 суммирования предназначен для получения на своем выходе сигнала Sвx.ф(t),

образуемого повторным искажением выходного сигнала SBbix.t(t) электронной моделью преобразователяр

5вх..ф(0 hn(r)-hn(0)+ +5вых.ф(г) hn(0)sвыx.ф(t) Ьп(т

Элемент 13 задержки осуществляет задержку входного сигнала Sвx.ф(t) устройства, который поступает на второй вход блока 22 вычисления ошибки. Время задержки ta равно

гз 2tc + 2ty,

где 2tc - время срабатывания блоков 1 и 9;

2ty - время срабатывания блоков 2 и 8.

11 на

Задержка во времени введена с целью исключения методической ошибки в блоке несинхронном появлении сигналов входах этого блока.

Блок 11 вычисления ошибки предназна- 5 чен для вычисления погрешности при восстановлении сигналов из-за неточного гствия частотной характеристики ре- курс1иБного обратного фильтра обратной ча- 3, cтoт| oй характеристике преобразователя у9,10

т.е.

-1в(й))

В к вать киа его

ка h

к

хрои

вует

этом базе то в капл

тота Коэф 105р, сов н теля

3

с

ется. 110 ки. Да мaдe

1

1

Нп.(й;)+Я Hri((w)

честве погрешности будет использовеличину средней квадратичной ошибсигнала Звх.фМ на выходе устройства от

вычисленного образца s вых. ф (t), т. е.

7 /о (SBb.x.(t) - SBb)x.(t)) dt Т/о (8вх.ф.(1) - 2вх.ф.(г)) dt

1 т

у/о (5вх.ф(г)-8вых.ф(г)М ff(Т))2 dt.

Сигнал Sax. ф(1) получается на выходе блока 9 су| |мирования. Импульсная характеристи(г) звена в обратной связи равна

h ff (г) (hn (г) - hn (0)) 4-я + hn (0)

hn(T) + A .

лемент 103 синхронизации подключен второму входу блока 11 и формирует син1пульсы, каждый из которых соответстпоступлению байта информации (с контрольным девятым разрядом) на второй вход блока 11. Такие 9-разрядные коды об- лада1рт свойством самосинхронизации, по- элемент 103 можно выполнить на

1-входовой схемы ИЛИ. Сумма квадра- р зностей сигналов Звх.фМ и Звх.фМ навается в накапливающем сумматоре, выполненном на основе элемента 106 сум- и регистра 107 в обратной связи, Запись в регистр 107 осуществляется по

синхр осигналам, задержанным на Ат эле1

ментс|м 109 задержки ( где fg - час- дискретизации сигналов). Коэффициент деления частоты в делителе вен п. Поэтому через п синхроимпуль- копленная сумма по сигналу из дели- 05 переписывается в регистр 110, а задержанным на время переписи сигналом выхода делителя 105 регистр 107 обнуля- Задержка на время записи в регистр о( уществляется элементом 108 задерж- лее в элементе 112 накопленная сум- ится на константу, равную п, которая поступает из элемента 111 формирования константы. Если п кратно степени двойки.

5 ,10

15

20

25

30

35

0

5

0

5

деление можно осуществить сдвигом впра- во на 1од2П разрядов. Через п синхроимпульсов значение а обновляется.

Блок 10 индикации отображает величину а средствами визуализации для контроля процесса восстановления оператором.

Блок 12 сравнения осуществляет сравнение погрешности на его входе с заданным допустимым значением С. Сигнал на его выходе равен логической 1, если ст С, и логическому О в противном случае,

Блок 14 согласования предназначен для управления передачей кодов с выхода рекурсивного обратного фильтра на выход устройства.

Если (7 С, сигналом логической 1 переключатели 114i-1 Ms переводятся в состояние, при котором выходные сигналы (отсчеты) рекурсивного фильтра передаются на выход устройства. Если а С, сигналом логического О переключатели 114i-1148 переводятся в состояние, при котором на выход устройства передаются определенные код-метки, которые не принадлежат множеству кодов, которые используются для отображения сигналов (например, код 11111111), Код-метки указывают на неработоспособность устройства.

Применение предлагаемого устройства выгодно как с технической, так и с экономической точек зрения. Текущий контроль погрешности восстановления и исключение передачи на выход устройства бракованной информации (т.е., высокая достоверность информации) позволяют увеличить достоверность результатов последующей обработки (например, результатов диагностирования объектов). Указание бракованной информации исключает время на ее обработку, например, на ЭВМ, что позволяет более эффективно использовать дорогостоящее машинное время.

Устройство обладает структурной надежностью. Например, при сбоях при определении параметра Я в дальнейшем параметр Я автоматически устанавливается нужной величины.

Если известное устройство возможно использовать только после предварительного исследования объектов (преобразователь информации), предлагаемое устройство допустимо применять, когда априорная неопределенность о свойствах объекта высока. За счет сокращения средств и времени на исследование объекта возраста ет экономическая эффективность применения устройства.

Измеряя п,араметр Я, можно оценить пределы изменения частотной характеристики преобразователя, что само по себе важно для практических нужд восстановления сигналов,

Формула изобретения 1. Устройство для восстановления сиг- налов, содержащее последовательно соединенные блок вычитания, вход которого является информационным входом устройства, первый блок умножения, блок модели- рования частотной характеристики линейного преобразователя, соединенный выходом с вычитающим входом блока вычитания, масштабный блок, подключенный выходом к второму входу первого блока умножения, группа входов блока моделирова- ния частотной характеристики линейного преобразователя соединена с настроечными входами устройства, начиная с второго, отличающееся тем, что, с целью повышения точности устройства, в него вве- дены блок настройки, блЬк синхронизации, два блока суммирования, второй блок умно- жения, блок Сравнения, блок индикации, блок вычисления ошибки, элемент задержки и блок согласования, настроечные входы устройства через последовательно соединенные блоки синхронизации, блок настройки, блок суммирования подключены к входу масштабного блока, первый настроечный вход устройства соединен с вторым вхо- дом первого блока суммирования и первым входом второго блока умножения, подключенного вторым входом к второму информационному входу блока настройки, выходу первого блока умножения и управляющему входу блока согласования, выход второго блока умножения соединен с первым входом второго блока суммирования, подключенного вторым входом к выходу блока моделирования частотной характеристики линейного преобразователя, а выходом - к первому информационному входу блока вычисления ошибки, к второму входу которого

через элемент задержки подсоединен информационный вход устройства, выход блока вычисления ошибки подключен к входу блока индикации и через блок сравнения - к информационному входу блока согласования, выход которого является выходом устройства.

2. Устройство по П.1, о т л и ч а ю щ е е- с я тем, что блок настройки содержит три формирователя импульсов, блок контроля устойчивости, формирователь сигналов переключения, блок сравнения, три переключателя и реверсивный счетчик, первый выход блока сравнения соединен с первым информационным входом формирователя сигналов переключения, к второму информационному входу которого через первый формирователь импульсов подключен первый вход формирователя сигналов переклю-. чения, соединенный через второй формирователь импульсов с синхровходом блока контроля устойчивости, информационный вход которого подключен к второму информационному входу блока настройки, а синхровыход через первый переключатель- к информационным входам второго и третьего переключателей, соединенных выходами соответственно с суммирующим и вычитающим входами реверсивного счетчика, выход которого подключен к входу блока сравнения и выходу блока настройки, выход первого формирователя импульсов через третий формирователь импульсов соединен с третьим информационным входом формирователя сигналов переключения, подключенного четвертым и пятым информационными входами соответственно к информационному выходу блока контроля устойчивости и второму выходу блока сравнения, выходы формирователя сигналов переключения соединены с управляющими входами переключателей.

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| Цифровое устройство для измерения фазы сигнала | 1989 |

|

SU1679405A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗАДЕРЖКИ ДИСКРЕТИЗАЦИИ В ВЫБОРКАХ ПОЛУЧЕННОГО СИГНАЛА В СИСТЕМЕ СОТОВОЙ СВЯЗИ | 1996 |

|

RU2165676C2 |

| Устройство адаптивной коррекции в частотной области с отображением характеристик | 1984 |

|

SU1298928A2 |

| Устройство для измерения параметров частотных датчиков | 1989 |

|

SU1705757A1 |

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 2013 |

|

RU2560204C2 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для решения обратных задач, и может быть использовано для восстановления сигналов методом обратной фильтрации. Цель изобретения - повышение точности восстановления сигналов. Устройство для восстановления сигналов содержит блок 1 вычитания, первый блок 2 умножения, масштабный блок 3, блок 4 моделирования частотной характеристики линейного преобразователя, блок 5 настройки, блок 6 синхронизации, блок 7 суммирования, второй блок 8 умножения, третий блок 9 суммирования, блок 10 индикации, блок 11 вычисления ошибки, блок 12 сравнения, элемент 13 задержки и блок 14 согласования. Цель изобретения достигается за счет введения блоков 5 - 14. 1 з.п. ф-лы, 7 ил., 4 табл.

Таблица2

ТаблицаЗ

Таблица4

1риг.2

«Л

J

if

I-MlII

I III

4-41- 90„ -fl- « . Ij Ij

ipaf.S

(Ригл

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цель изобретения - повышение точности восстановления сигналов | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| с; ON О 00 VJ О О ЧЖг | |||

Авторы

Даты

1990-11-23—Публикация

1988-12-21—Подача