сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения центральнойчАСТОТы СпЕКТРА СигНАлА | 1979 |

|

SU813290A1 |

| ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2000 |

|

RU2178894C1 |

| РАДИОМОДЕМ | 2010 |

|

RU2460215C1 |

| Измеритель отношения переменных напряжений | 1986 |

|

SU1357855A1 |

| ИНТЕГРИРОВАННЫЙ ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1999 |

|

RU2146378C1 |

| Анализатор активности непрерывных сигналов | 1989 |

|

SU1658386A1 |

| ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 2013 |

|

RU2541856C2 |

| Многоканальный фазовый демодулятор | 1988 |

|

SU1555900A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Нерекурсивный цифровой фильтр-дециматор | 1989 |

|

SU1698953A2 |

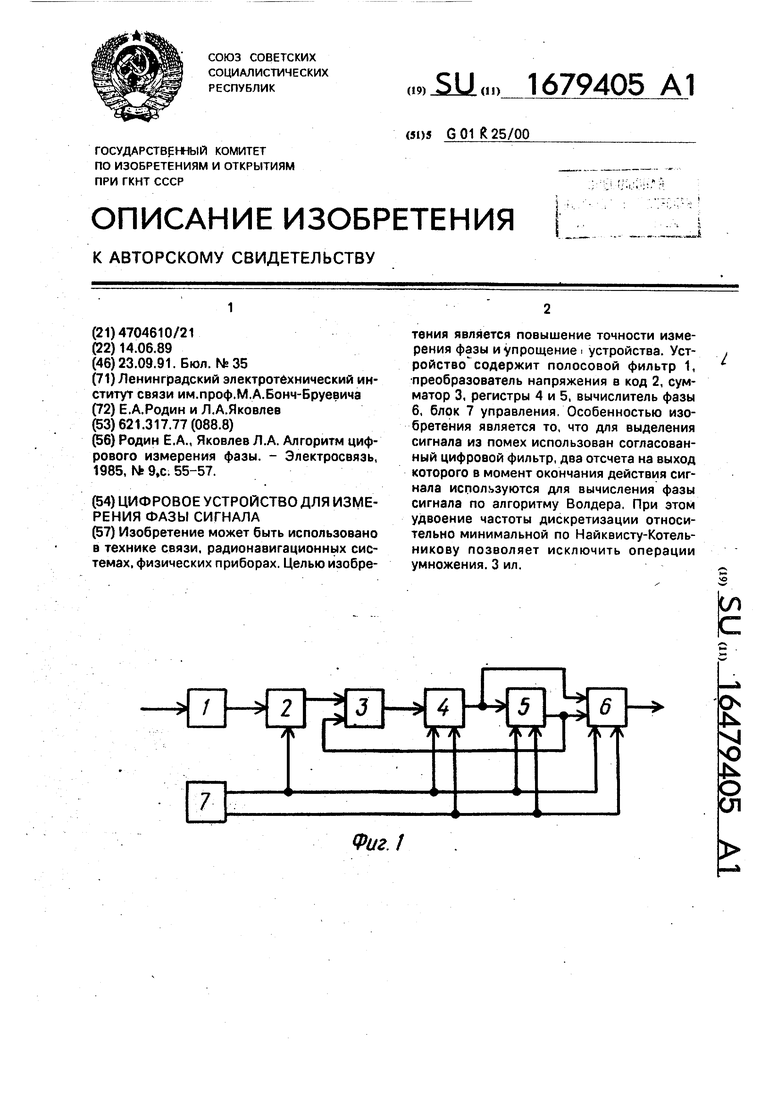

Изобретение может быть использовано в технике связи, радионавигационных системах, физических приборах. Целью изобретения является повышение точности измерения фазы и упрощение i устройства. Устройство содержит полосовой фильтр 1, преобразователь напряжения в код 2, сумматор 3, регистры 4 и 5, вычислитель фазы 6, блок 7 управления. Особенностью изобретения является то, что для выделения сигнала из помех использован согласованный цифровой фильтр, два отсчета на выход которого в момент окончания действия сигнала используются для вычисления фазы сигнала по алгоритму Волдера. При этом удвоение частоты дискретизации относительно минимальной по Найквисту-Котель- никову позволяет исключить операции умножения. 3 ил.

Os

4 VI О Јь О СП

Фиг. /

Изобретение относится к радиоизмерениям, может быть использовано в технике связи, радионавигационных системах, физических приборах.

Цель изобретения - повышение точности и упрощение устройства при измерении синусоидальных сигналов.

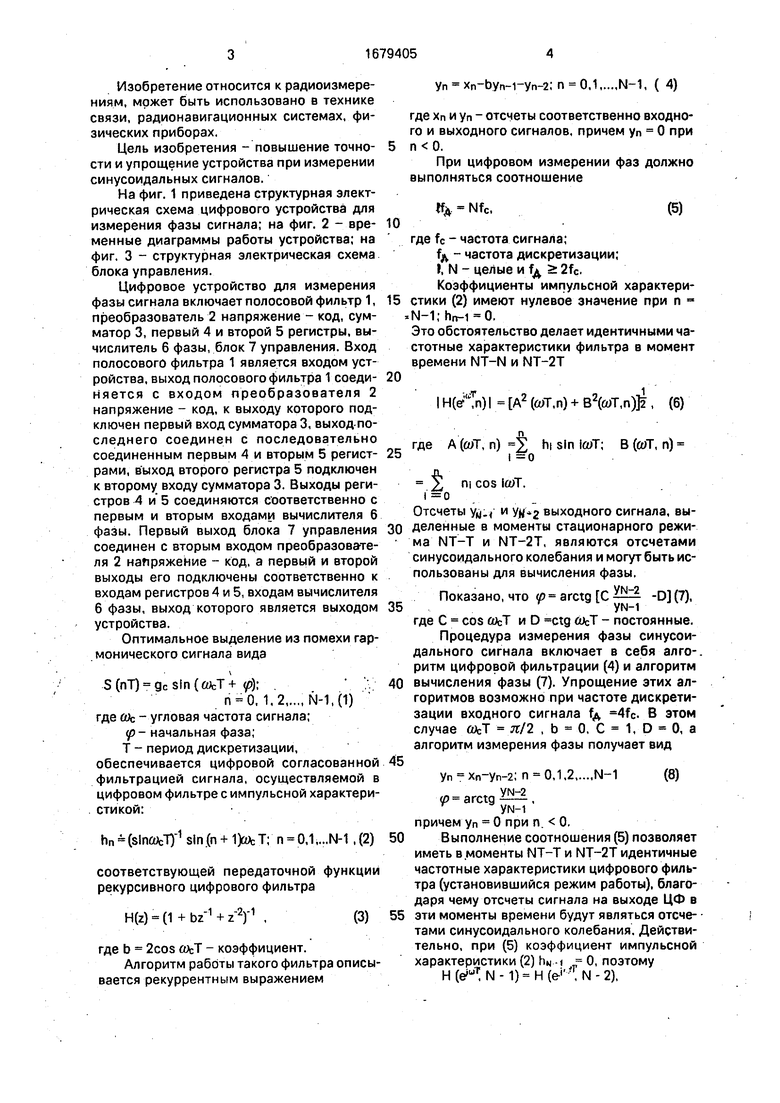

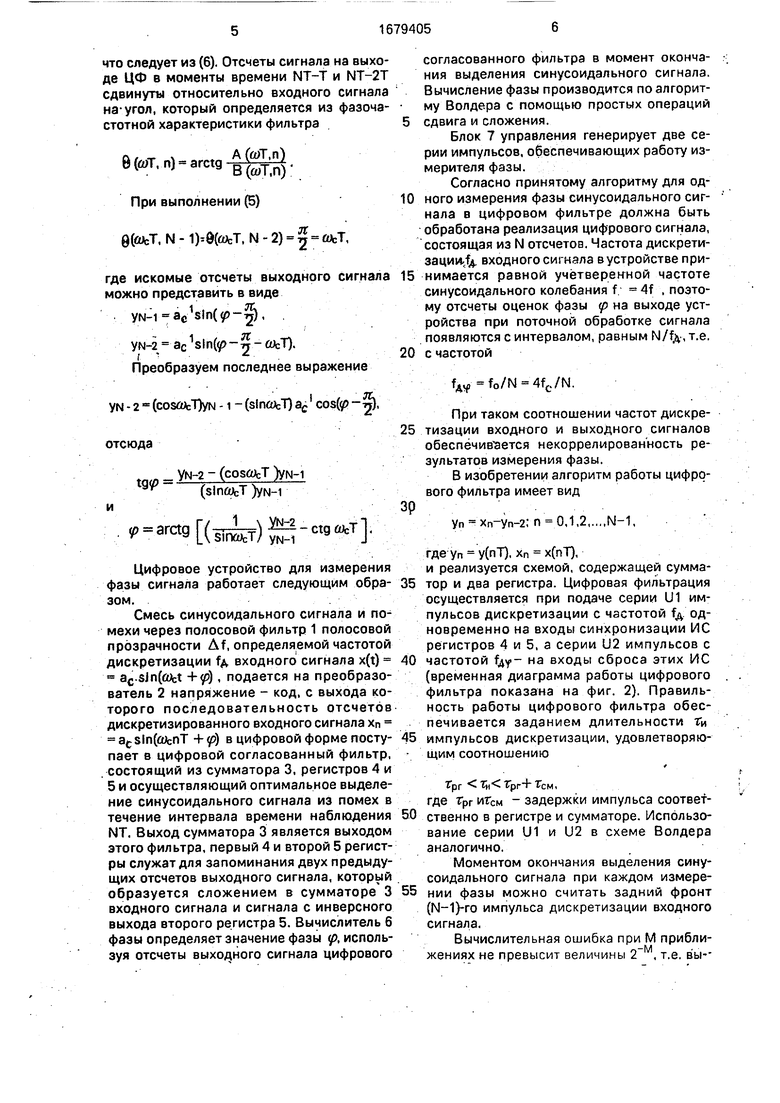

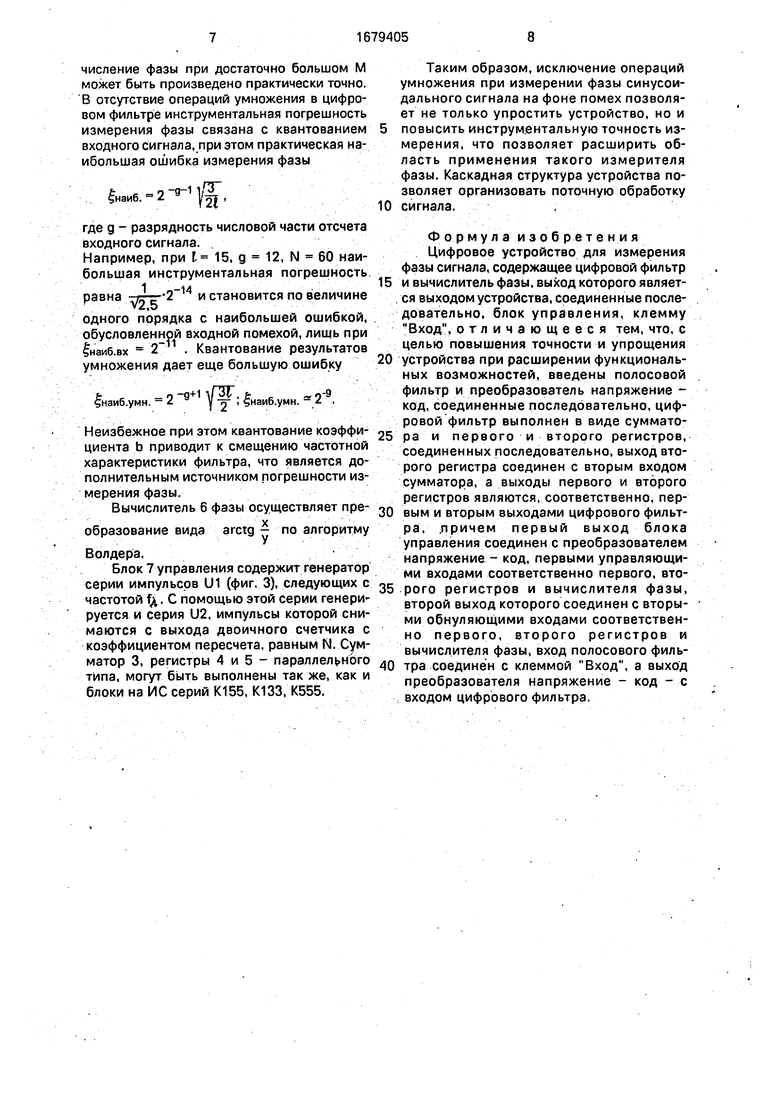

На фиг. 1 приведена структурная электрическая схема цифрового устройства для измерения фазы сигнала; на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - структурная электрическая схема блока управления.

Цифровое устройство для измерения фазы сигнала включает полосовой фильтр 1, преобразователь 2 напряжение - код, сумматор 3, первый 4 и второй 5 регистры, вычислитель 6 фазы, блок 7 управления. Вход полосового фильтра 1 является входом устройства, выход полосового фильтра 1 соединяется с входом преобразователя 2 напряжение - код, к выходу которого подключен первый вход сумматора 3, выход последнего соединен с последовательно соединенным первым 4 и вторым 5 регистрами, выход второго регистра 5 подключен к второму входу сумматора 3. Выходы регистров 4 и 5 соединяются соответственно с первым и вторым входами вычислителя 6 фазы. Первый выход блока 7 управления соединен с вторым входом преобразователя 2 напряжение - код, а первый и второй выходы его подключены соответственно к входам регистров 4 и 5, входам вычислителя 6 фазы, выход которого является выходом устройства.

Оптимальное выделение из помехи гармонического сигнала вида

S(nT) gcsln(WcT+ p);

п 0,1,2N-1,(1)

где (Ос угловая частота сигнала;

р- начальная фаза;

Т - период дискретизации, обеспечивается цифровой согласованной фильтрацией сигнала, осуществляемой в цифровом фильтре с импульсной характеристикой:

hn (slncocT)1 sin (n + 1)tyc Т; п 0,1 ,...N-1, (2)

соответствующей передаточной функции рекурсивного цифрового фильтра

H(z) (1 + + z 2r1

где b 2cos (UcT - коэффициент.

Алгоритм работы такого фильтра описывается рекуррентным выражением

уп хп-Ьуп-1-уп-2; п 0.1N-1, ( 4)

где хп и уп - отсчеты соответственно входного и выходного сигналов, причем уп 0 при п 0.

При цифровом измерении фаз должно выполняться соотношение

10

If Nfc,

(5)

где fc - частота сигнала;

f& - частота дискретизации; I, N - целые и fA 2fc. Коэффициенты импульсной характери- стики (2) имеют нулевое значение при п N-1;hn-i 0.

Это обстоятельство делает идентичными частотные характеристики фильтра в момент времени NT-N и NT-2T

I ) I A2 (ft/T.n) + B2(u/r,n)Ј , (6)

25

где A (wT, n) У hi sin IcuT; В (еыТ, n):

m cos kuT.

о

Отсчеты у, и выходного сигнала, вы- Зо деленные в моменты стационарного режима NT-T и NT-2T, являются отсчетами синусоидального колебания и могут быть использованы для вычисления фазы.

Показано, что p arctg С t2- -D(7), 35УМ-1

где С cos OfcT и D ctg ufcT - постоянные. Процедура измерения фазы синусоидального сигнала включает в себя алго-. ритм цифровой фильтрации (4) и алгоритм

40 вычисления фазы (7). Упрощение этих алгоритмов возможно при частоте дискретизации входного сигнала Тд 4fc. В этом случае ftfcT л/2 , b О, С 1, D 0, а алгоритм измерения фазы получает вид

45

Уп хп-уп-2; n 0,1,2N-1(8)

arctg t2-,

УМ-1

причем уп 0 при п. 0. 50 Выполнение соотношения (5) позволяет иметь в моменты NT-T и NT-2T идентичные частотные характеристики цифрового фильтра (установившийся режим работы), благодаря чему отсчеты сигнала на выходе ЦФ в 55 эти моменты времени будут являться отсче- тами синусоидального колебания. Действительно, при (5) коэффициент импульсной характеристики (2) hn - 0, поэтому

Н ( N -1) Н (е-1 ,N-2),

что следует из (6). Отсчеты сигнала на выходе ЦФ в моменты времени NT-T и NT-2T сдвинуты относительно входного сигнала на-угол, который определяется из фазоча- стотной характеристики фильтра

- «-&$$.

При выполнении (5) 9(fiJfcT, N - (, N - 2) 5 ftfcT,

где искомые отсчеты выходного сигнала можно представить в виде

yN-i ac1sln(),

ум-2 ас 1sln(p - тт - ufcT). i

Преобразуем последнее выражение

W 2 (cosft cT)yN -1 - (slncutT) ac cos(p -т), отсюда

VN-2 (cQSUfcT )ум-1 W (SlnftfcT)yN-1

и ()

Цифровое устройство для измерения фазы сигнала работает следующим образом.

Смесь синусоидального сигнала и помехи через полосовой фильтр 1 полосовой прозрачности Af, определяемой частотой дискретизации 1д входного сигнала x(t) ac.sjn(ufct ), подается на преобразователь 2 напряжение - код, с выхода которого последовательность отсчетов дискретизированного входного сигнала хп - ас sln(ftfcnT + p) в цифровой форме поступает в цифровой согласованный фильтр, состоящий из сумматора 3, регистров 4 и 5 и осуществляющий оптимальное выделение синусоидального сигнала из помех в течение интервала времени наблюдения NT. Выход сумматора 3 является выходом этого фильтра, первый 4 и второй 5 регистры служат для запоминания двух предыдущих отсчетов выходного сигнала, который образуется сложением в сумматоре 3 входного сигнала и сигнала с инверсного выхода второго регистра 5. Вычислитель 6 фазы определяет значение фазы р, используя отсчеты выходного сигнала цифрового

согласованного фильтра в момент окончания выделения синусоидального сигнала. Вычисление фазы производится по алгоритму Волдера с помощью простых операций

5 сдвига и сложения.

Блок 7 управления генерирует две серии импульсов, обеспечивающих работу измерителя фазы.

Согласно принятому алгоритму для од0 ного измерения фазы синусоидального сигнала в цифровом фильтре должна быть обработана реализация цифрового сигнала, состоящая из N отсчетов. Частота дискрети- зации/Рд входного сигнала вустройстве при5 нимается равной учетверенной частоте синусоидального колебания f 4f , поэтому отсчеты оценок фазы (р на выходе устройства при поточной обработке сигнала появляются с интервалом, равным N/f, т.е.

0 с частотой

тдч, fo/N 4fc/N.

При таком соотношении частот дискре- 5 тизации входного и выходного сигналов обеспечивается некоррелированность результатов измерения фазы.

В изобретении алгоритм работы цифрового фильтра имеет вид

р

Уп хп-уп-2: п 0,1,2N-1,

где уп у(пТ), хп х(пТ),

и реализуется схемой, содержащей сумма5 тор и два регистра. Цифровая фильтрация осуществляется при подаче серии U1 импульсов дискретизации с частотой Тд одновременно на входы синхронизации ИС регистров 4 и 5, а серии U2 импульсов с

0 частотой тду- на входы сброса этих ИС (временная диаграмма работы цифрового фильтра показана на фиг. 2). Правильность работы цифрового фильтра обеспечивается заданием длительности Ти

5 импульсов дискретизации, удовлетворяющим соотношению

/

Трг Ти Трг4 Тем,

где ГрГ игсм - задержки импульса соответ- 0 ственно в регистре и сумматоре. Использование серии U1 и U2 в схеме Волдера аналогично.

Моментом окончания выделения синусоидального сигнала при каждом измере- 5 нии фазы можно считать задний фронт (N-1)-ro импульса дискретизации входного сигнала.

Вычислительная ошибка при М приближениях не превысит величины , т.е. вы-числение фазы при достаточно большом М может быть произведено практически точно. В отсутствие операций умножения в цифровом фильтре инструментальная погрешность измерения фазы связана с квантованием входного сигнала, при этом практическая наибольшая ошибка измерения фазы

$наиб.

гҐгде g - разрядность числовой части отсчета входного сигнала.

Например, при 1 15, g 12, N 60 наибольшая инструментальная погрешность

равна I- и становится по величине

одного порядка с наибольшей ошибкой, обусловленной входной помехой, лишь при Јнаиб.вх - 2 . Квантование результатов умножения дает еще большую ошибку

Јнаиб.умн. - 2 Q | Т §наиб.умн. я 2 .

Неизбежное при этом квантование коэффициента b приводит к смещению частотной характеристики фильтра, что является дополнительным источником погрешности измерения фазы.

Вычислитель 6 фазы осуществляет преобразование вида arctg по алгоритму

Вол дера.

Блок 7 управления содержит генератор серии импульсов U1 (фиг. 3), следующих с частотой тд. С помощью этой серии генерируется и серия U2, импульсы которой снимаются с выхода двоичного счетчика с коэффициентом пересчета, равным N. Сумматор 3, регистры 4 и 5 - параллельного типа, могут быть выполнены так же, как и блоки на ИС серий К155, К133, К555.

Таким образом, исключение операций умножения при измерении фазы синусоидального сигнала на фоне помех позволяет не только упростить устройство, но и

повысить инструментальную точность измерения, что позволяет расширить область применения такого измерителя фазы. Каскадная структура устройства позволяет организовать поточную обработку

сигнала.

Формула изобретения Цифровое устройство для измерения фазы сигнала, содержащее цифровой фильтр

и вычислитель фазы, выход которого является выходом устройства, соединенные после- довательно, блок управления, клемму Вход, отличающееся тем, что, с целью повышения точности и упрощения

устройства при расширении функциональных возможностей, введены полосовой фильтр и преобразователь напряжение - код, соединенные последовательно, цифровой фильтр выполнен в виде сумматора и первого и второго регистров, соединенных последовательно, выход второго регистра соединен с вторым входом сумматора, а выходы первого и второго регистров являются, соответственно, первым и вторым выходами цифрового фильтра, .причем первый выход блока управления соединен с преобразователем напряжение - код, первыми управляющими входами соответственно первого, второго регистров и вычислителя фазы, второй выход которого соединен с вторыми обнуляющими входами соответственно первого, второго регистров и вычислителя фазы, вход полосового фильтра соединён с клеммой Вход, а выход преобразователя напряжение - код - с входом цифрового фильтра.

An. 2.

Фиг. J

| Родин Е.А., Яковлев Л.А | |||

| Алгоритм цифрового измерения фазы | |||

| - Электросвязь, 1985, № 9,с | |||

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

Авторы

Даты

1991-09-23—Публикация

1989-06-14—Подача