Изобретение относится к вычислительной технике и может быть применено в цифровых вычислительных машинах и устройствах.

Цель изобретения - сокраще}1ие оборудования.

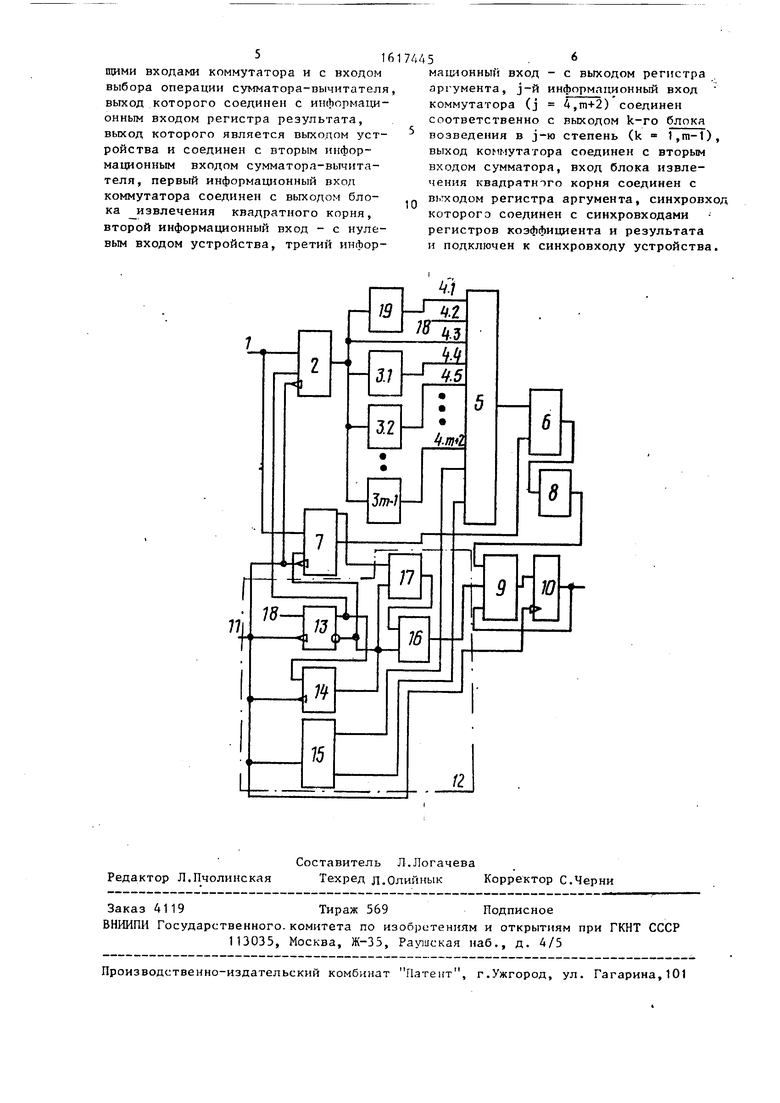

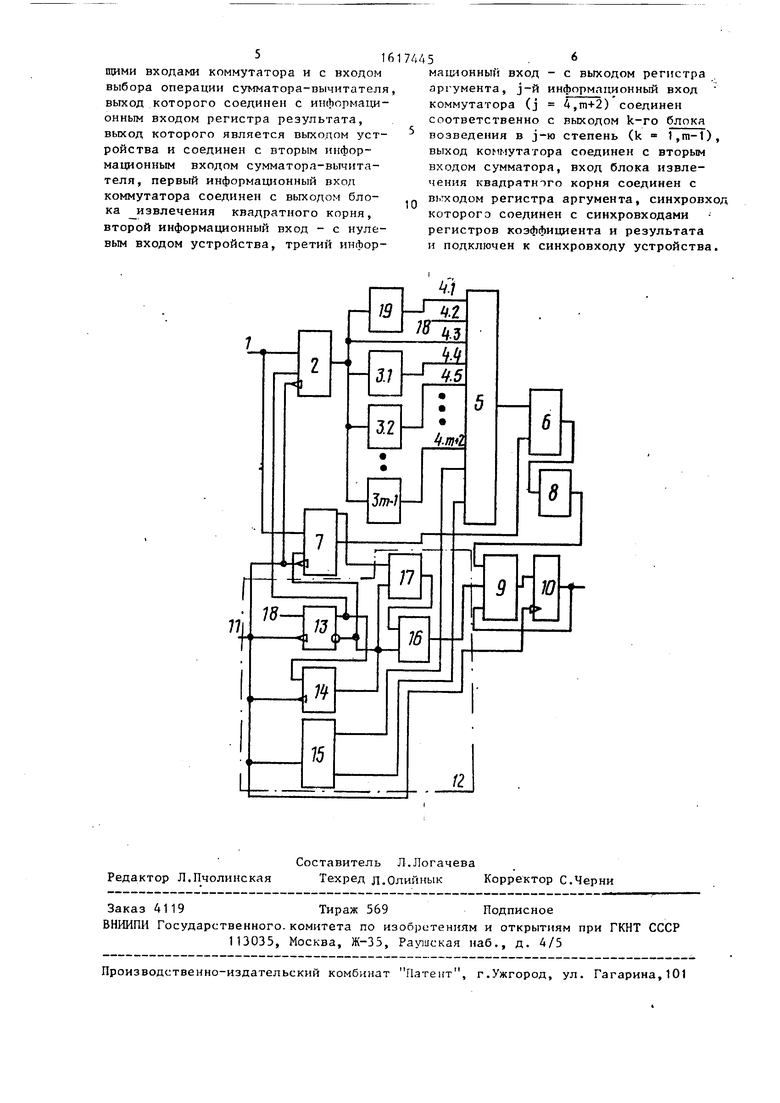

На чертеже представлена структурная схема устройства.

Устройство содержит вход 1 устрой-i ства, регистр 2 аргумента, (т-1) блоп ков возведения в i-ю степень (,т, m - степень многочлена), входы 4.1- 4.т+2 коммутатора 5, коммутатор 5, сумматор 6, регистр 7 коэффициента, квадратор 8, сумматор-вычитатель 9, регистр 10 результата, синхровход 11 устройства и узел 12 управления, состоящий из триггеров 13 и 14, счет-,

чика 15, элемента ИЛИ 16, элемента И 1 У,нулевого входа, 18 устройства и блока 19 извлечения квадратного корня .

Устройство работает следующим образом.

Перед началом вычислений триггеры 13 и 14 устанавливаются в единичное состояние, регистры 2, 7 и 10, а также счетчик 15 обнуляются.

В блоке 19, выполненном на постоян.- ной памяти,хранится значение функции

F(x) л|х + .y + ...+ х, в блоках 3.1 (i 2,m) записаны таблицы для возведения чисел в степень i. В квадраторе 8 записана таблица возведения чисел в квадрат.

О)

vl

u

4 Ol

Вычисление многочлена выполняется в (т+2) тактах. В первом такте на вход 1 устройства поступает аргумент. Затем поступает синхросигнал на вход 11 устройства. По положительному перепаду синхросигнала значение х записывается в регистр 2. Указанное значение поступает на входы блоков 3.1, на выходах которых формируются значения соответствующих функций. Так как счетчик 15 обнулен, на выход коммутатора 5 передается информация с входов 4.1. Таким образом на выходе коммутатора 5 формируется значе- ние функции -л1г(х), а на выходе квадратора 8 - величина F(x).

Единичный сигнал с выхода элемента ИЛИ 16 определяет операцию вычитания сумматора-вычитателя 9, который вы- читает из содержимого регистра 10 результата значение F(x). По отрицательному перепаду синхросигнала на входе 11 информация на выходах сум- матора-вычитателя 9, т.е. значение O-F(X) ,,фиксируется в регистре 10. Кроме того, прибавляется единица к содержимому счетчика 15, а также устанавливается в нулевое состояние триггер 13. Во втором такте на вхо 1 устройства поступает значение- |oil

где 0. 2ао- аГ - а, - а. -...а„. а

2 2 г „2 о (2 ...а,

также знак оС. По положительному перепаду синхросигнала значение-лЦ записывается в регистр 7. Знаковый разряд об поступает на первый вход элемента И 17, и если (Х О, на выходе элемента ИЛИ 16 формируется единичный сигнал, определяющий операцию вычитания сумматору - вычита- телю 9. В противном случае на выходе элемента ИЛИ 16 присутствует О и сумматор-вычитатель 9 выполняет операцию суммирования. Так как в счечике 15 записана 1, то на выход коммутатора передается нулевая информация с входа 4.2. На выходе сум матора 6 формируется значение -ЦЩ , а на выходах квадратора 8 - . По отрицательному перепаду синхросигнала в регистре 10 фиксируется информация (-F(x)+Oi). Кроме того, прибавляется единица к содержимому счетчика 15, а также сбрасьшается триггер 14 и на выходе элемента ИЛИ 16 устанавливается нулевое значение.

В третьем цикле на вход 1 устройства поступает значение коэффициента многочлена а, которое по положи

тельному перепаду синхросигнала записывается в регистр 7.

Информация с входа 4.3 коммутатора 5, т.е. значение аргумента, передается на вход сумматора 6, на другой вход поступает коэффициент а, на выходе сумматоре формируется значение (). В третьм и остальных до (т+2)-го тактах, на выходе элемента ИЛИ 16 присутствует О, т.е. сумматор-вычита- тель 9 выполняет операцию сложения. По. отрицательному перепаду синхросигнала в регистре 10 фиксируется значение ((-F(x) + ot)-t-(a 1 + х)). Кроме того, к содержимому счетчика 15 прибавляется единица. Далее в каждом следующем такте на вход 1 устройства поступают значения коэффициентов, а в регистре 10 формируется значение:

YI

Р(х) -F(x)+ cL ; + )-

х).

После окончания (т+2)-го такта в регистре результата 10 формируется значение, которое равно удвоенному значению многочлена Р(х) а „ + а + + ... +

Формула изобретения

Устройство для вычисления многочленов, содержащее регистр аргумента, выход которого соединен с входами т-1 блоков возведения в i-ю степень (i 2,m, где m - порядок многочлена) сумматор, выход которого соединен с входом квадратора, выход которого соединен с первым информационным входом сумматора-вычитателя, регистр коэффициента, информационный вход которого соединен с информащ- онным входом регистра аргумента и является входом устройства, первый вход сумматора соединен с выходом регистра аргумента, отличающ

е е с я тем, что, с целью сокра

щения количества оборудования, оно содержит блок извлечения квадратного корня, коммутатор, регистр результата и узел управления, первый вход которого соединен с синхровходом устройства, второй вход - с выходом- знака регистра коэффициента, а первый, второй, третий, четвертый и пятый выходы узла управления соединены.соответственно с управляющими входами регистра аргумента, регистра коэффициента, первым и вторым управляю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

| Устройство для вычисления многочленов | 1982 |

|

SU1048481A1 |

| Устройство для вычисления многочленов | 1984 |

|

SU1160431A2 |

| Устройство для вычисления полиномов | 1982 |

|

SU1067509A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Устройство для вычисления значений группы функций | 1988 |

|

SU1656532A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления синдромов кода Рида-Соломона | 1990 |

|

SU1751860A1 |

Изобретение относится к вычислительной технике, в частности к устройствам для вычисления многочленов и может быть использовано в качестве арифметического расширителя ЭВМ. Цель изобретения - сокращение количества оборудования. Устройство содержит регистры аргумента, коэффициента и результата, M - 1 блоков возведения в I-ю степень (I=2,M,M - степень многочлена), блок извлечения квадратного корня, коммутатор, сумматор, сумматор-вычитатель, узел управления и квадратор. В процессе функционирования устройства операнды последовательно поступают на вход устройства. Тактирование работы устройства осуществляется внешним синхросигналом, по положительному перепаду которого операнд записывается во входном регистре, а по отрицательному - промежуточный результат фиксируется в регистре результата. 1 ил.

| Устройство для вычисления значения полинома @ -й степени | 1983 |

|

SU1134947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления многочленов | 1982 |

|

SU1048481A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-30—Публикация

1988-12-02—Подача