выходом первого блока памяти, выходом второго блока памяти, выходом сумматора, входом первой константы устройства и входом второй констант устройства, выходы первого и второг коммутаторов соединены с соотвйтствуюпщми информационными входами узл умножения, выход которого соединен с первыми информационными входами третьего коммутатора и сумматора, . второй информационный вход которого соединен с выходом четвертого коммутатора, первый и второй информационные входы которого соединены с выходами соответственно первого и второго блоков памяти, выход сумматора соединен с вторым информационным входом третьего коммутатора, выход которого соединен с информационным входом регистра результата, выход которого соединен с выходом устройства, выходы сумматора и узла умножения соединены соответственно с вторыми и третьими информационными входами первого и второго входны коммутаторов, управляющие входы всех коммутаторов соединены с управляющим входом блока вычисления многочлена, подключенного к входам

5329

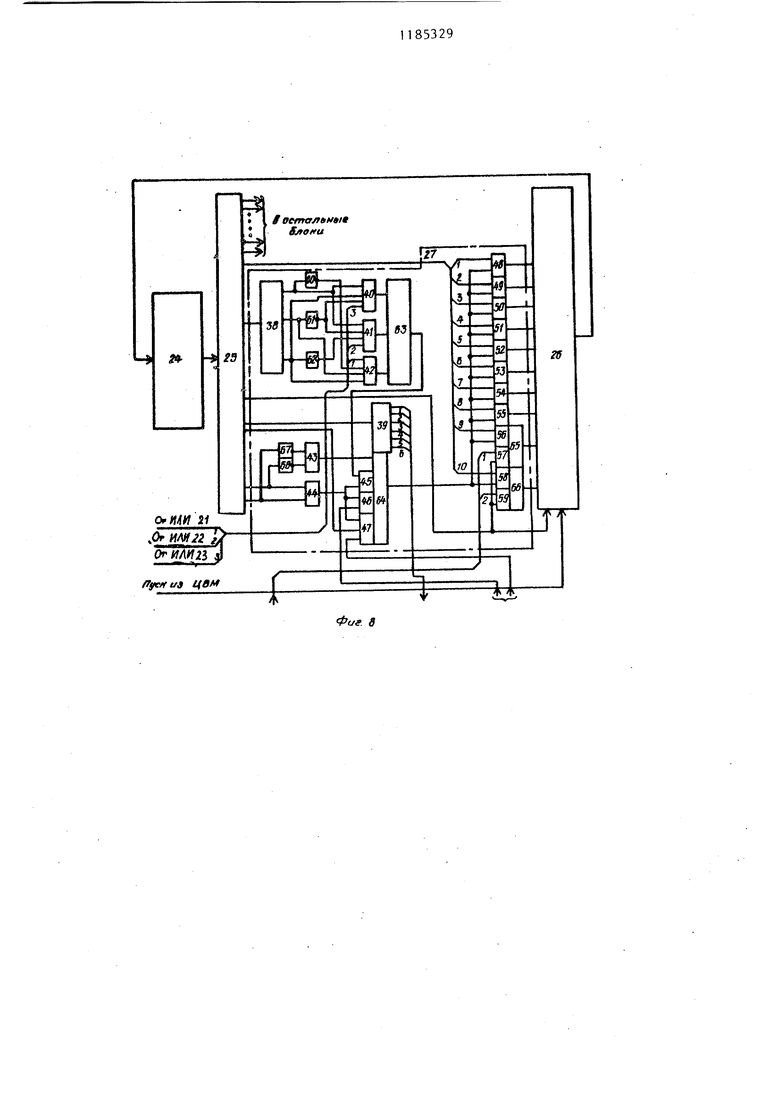

разрешения узла умножения, сумматора и регистра результата, блок управления содержит схему сравнения аргумента, регистр, счетчик, шифратор и узел памяти, выход которого соединен с информационным входом регистра, выход первой группы разрядов которого соединен с первым входом шифратора, второй вход которого соединен с четвертым входом блока, выход шифратора соединен с установочным входом счетчика адреса, вход разрешения записи которого соединен с вторым входом блока, выход счетчика адреса соединен с адресным входом узла памяти, первый и второй информационные входы схемы сравнения аргумента соединены соответственно с первым и третьим входами блока, управляющий вход и выход схемы сравнения аргумента соединеIны соответственнб с выходом шифратора и седьмым и одиннадцатым выходами блока, выходы с первого по шестой которого соединены с выходами с второй по седьмую групп разрядов регистра, выходы с восьмой по десятую групп разрядов которого соединены с соответствующими выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для вычисления тригонометрических функций с плавающей запятой | 1986 |

|

SU1425661A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Устройство для вычисления корня @ -степени | 1986 |

|

SU1381494A1 |

УСТРОЙСТВО ДЛЯ ВЬИИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНЮЩЙ, содержащее счетчик порядка, входной регистр, сдвигатель, первый и второй блоки памяти и блок управления, причем выход счетчика порядка соединен с первой группой входов, сдвигателя, вторая группа входов которого соединена с выходами входного регистра, адресными входами первого блока памяти и первым входом блока управления первый выход которого соединен со счетным входом счетчика по-: рядка, выход сдвигателя соединен с адресным входом второго блока памяти, отличающееся тем, что, с целью повьшения быстродействия, в него введены первый и второй входные коммутаторы, блок определения степени многочлена и блок вычисления многочлена, причем выходы первого и второго входных коммутаторов соединены с информационными входами соответственно счетчика порядка и входного регистра. .первые информационные входы первого и второго входных коммутаторов соединены с информационным входом устройства, вход пуска которого соединен с вторым входом блока управления, выходы с третьего по одиннадцатый которого соединены соответственно с управляющими входами первого входного коммутатора, второго входного коммутатора, входного регистра, сдвигателя, блока определения степени многочлена, блока вычисления многочлена первого блока памяти, второго блока памяти и выо S ходом устройства, третий и четвертый входы блока управления соеди(Л нены соответственно с выходом сдвигателя и выходом блока определения степени многочлена, содержащего три шифратора и три элемента ИШ, выходы с первого по Третий разрядов с первого по третий шифраторов соединены соответственно с первого по третий :входами каждого элемента ИЛИ, выхо- . ел .ды которых являются выходом блока определения степени многочлена, информационные и управляющие входы каждого шифратора соединены соответственно с выходом сдвигателя и управ- ляющим входом блока определения степени многочлена, блок вычисления многочлена содержит четыре коммутатора, узел умножения, сумматор и регистр результата, причем первый и второй информационные входы первого коммутатора соединены с выходами соответственно счетчика порядка и входного регистра, информационные входы с первого по пятый второго коммутатора соединены соответственно с

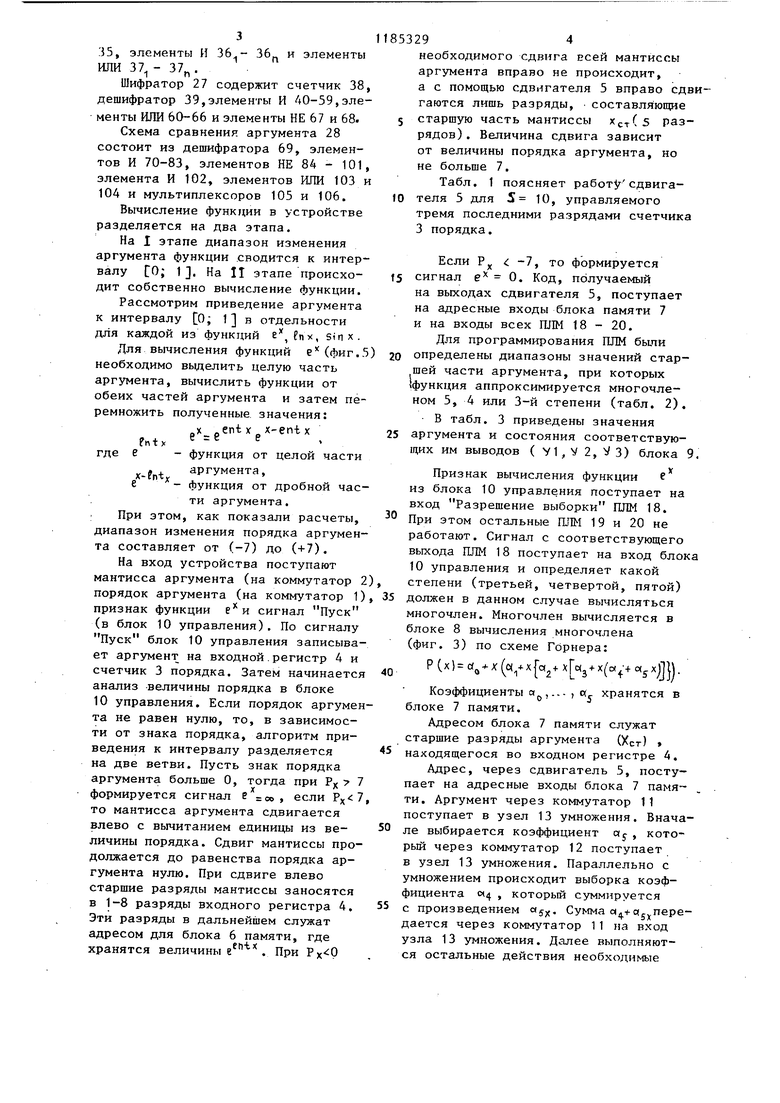

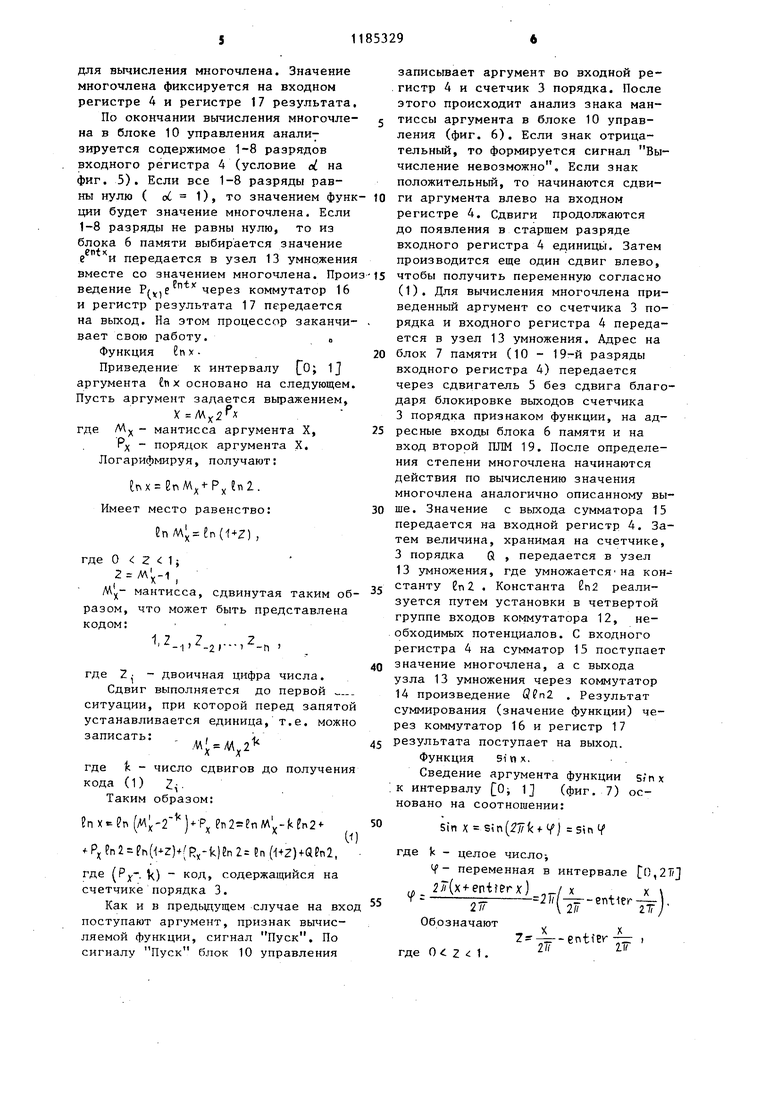

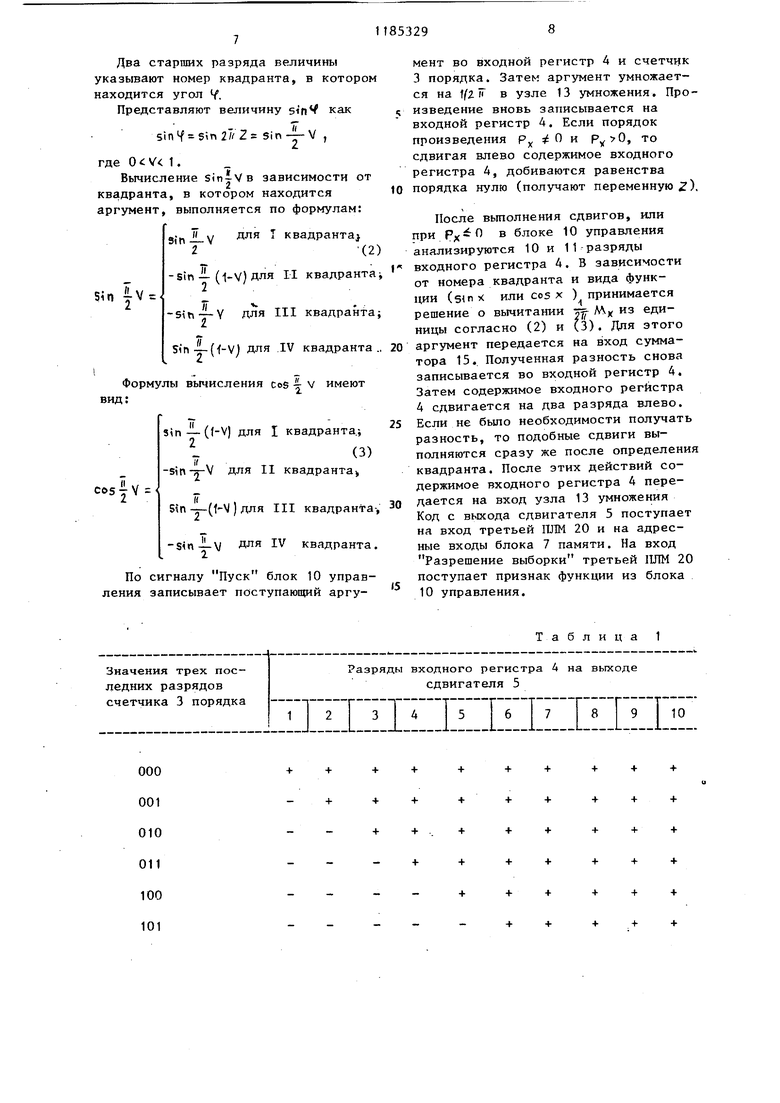

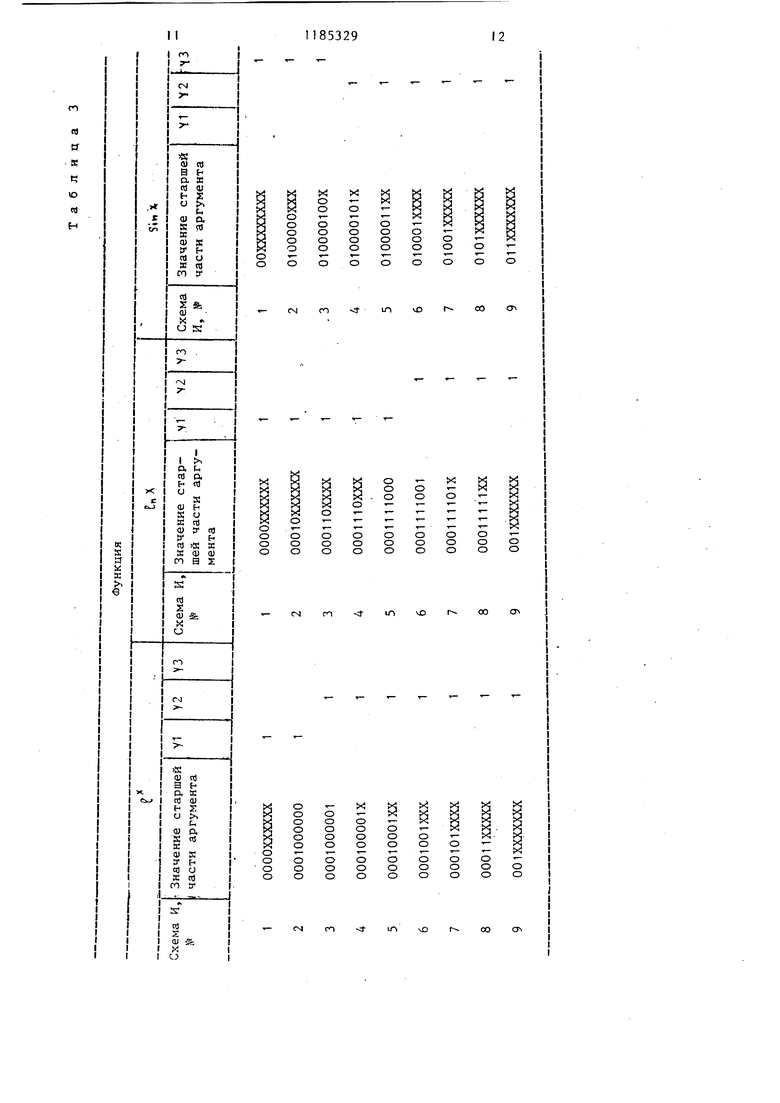

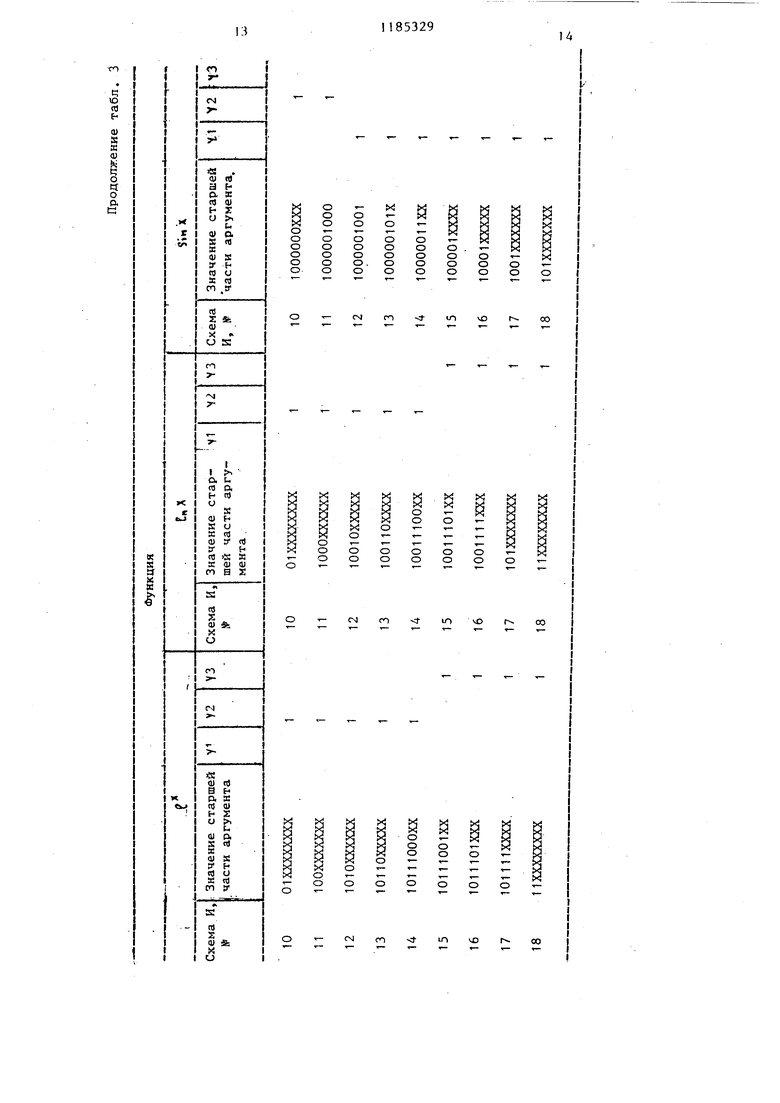

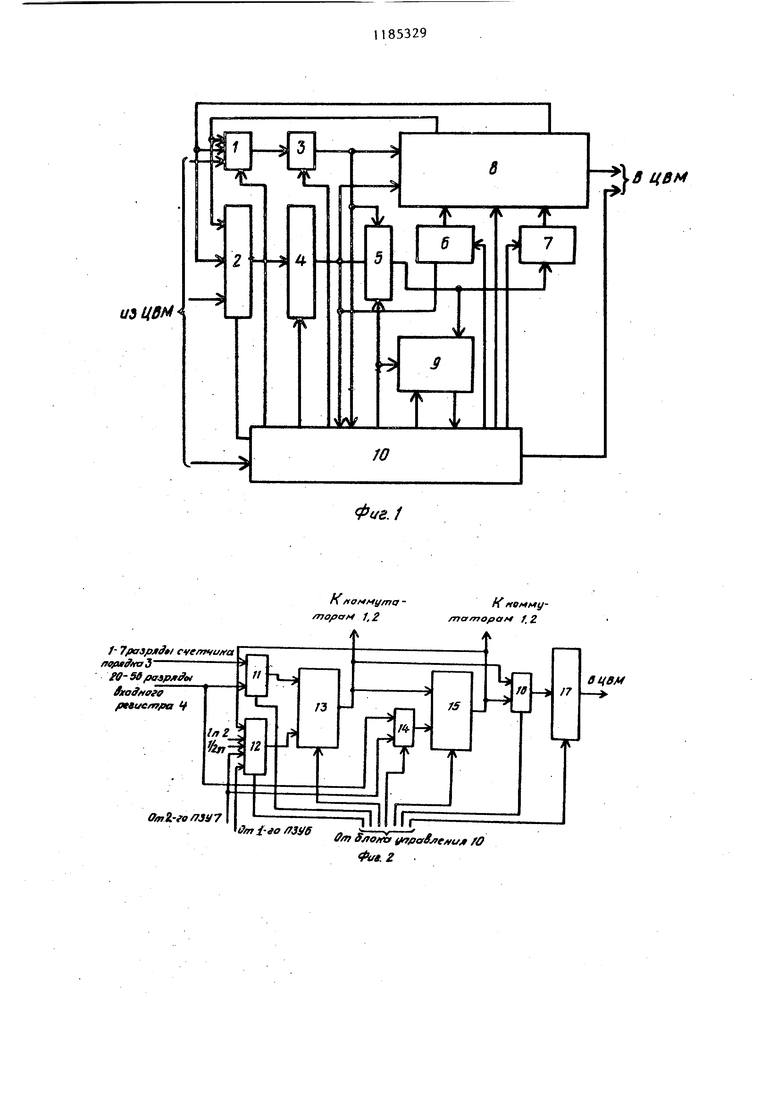

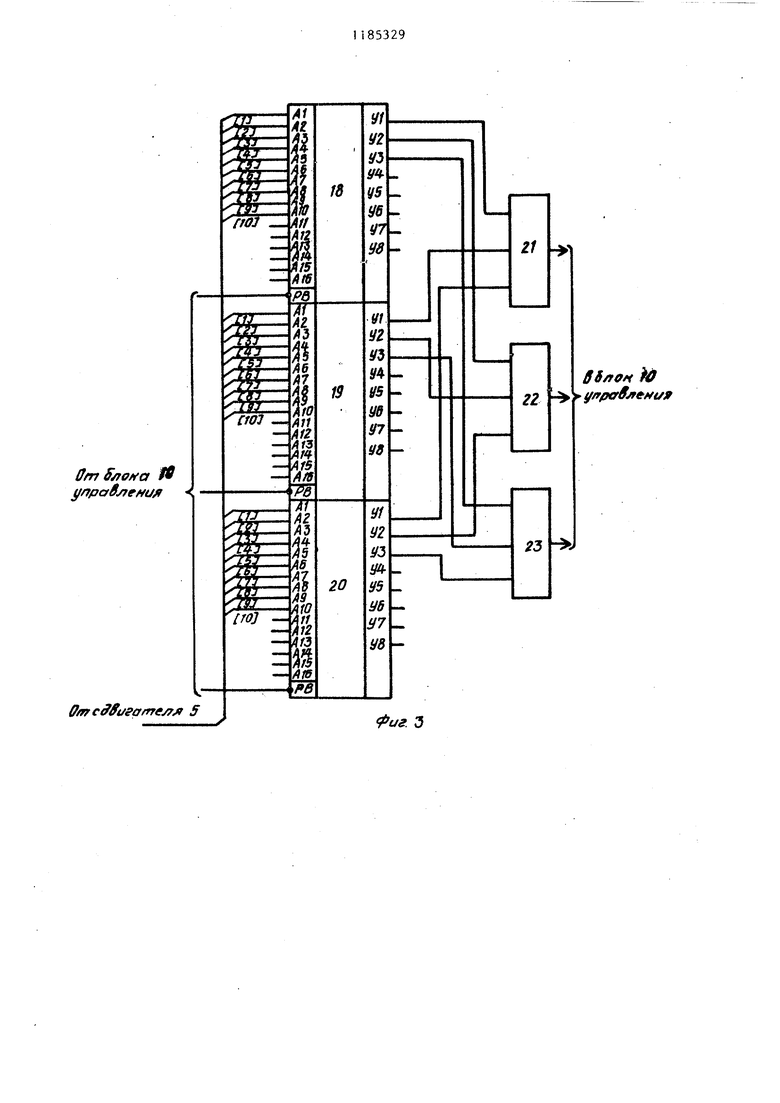

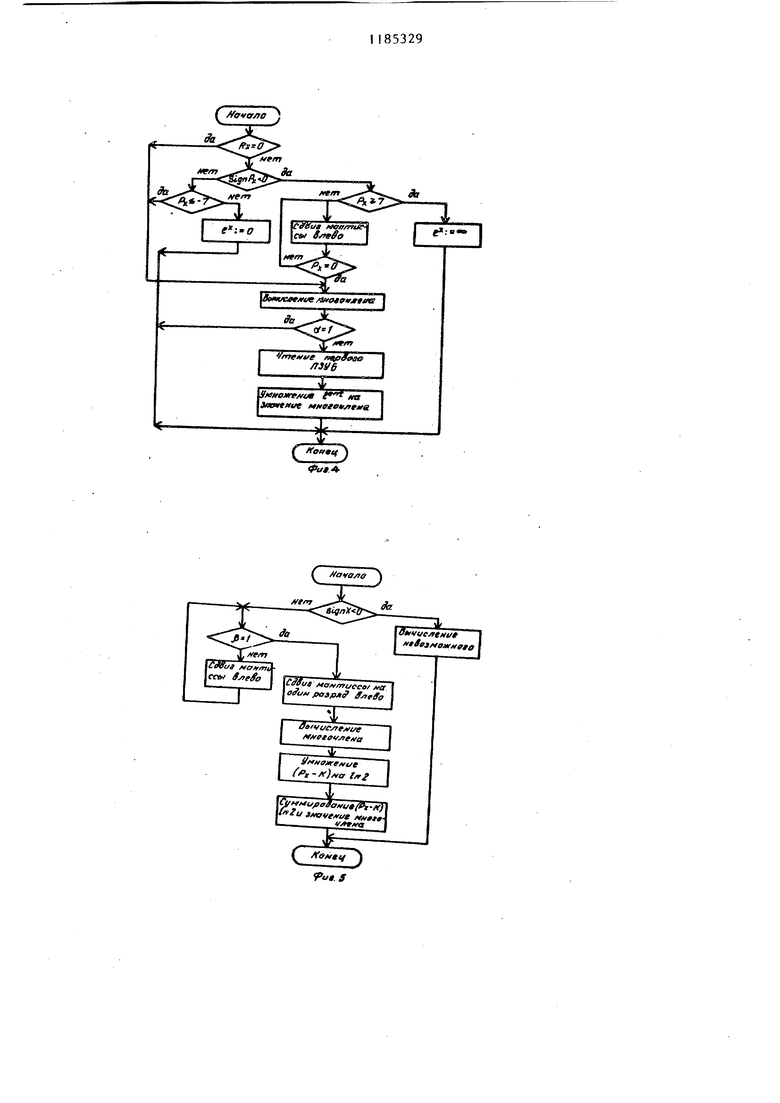

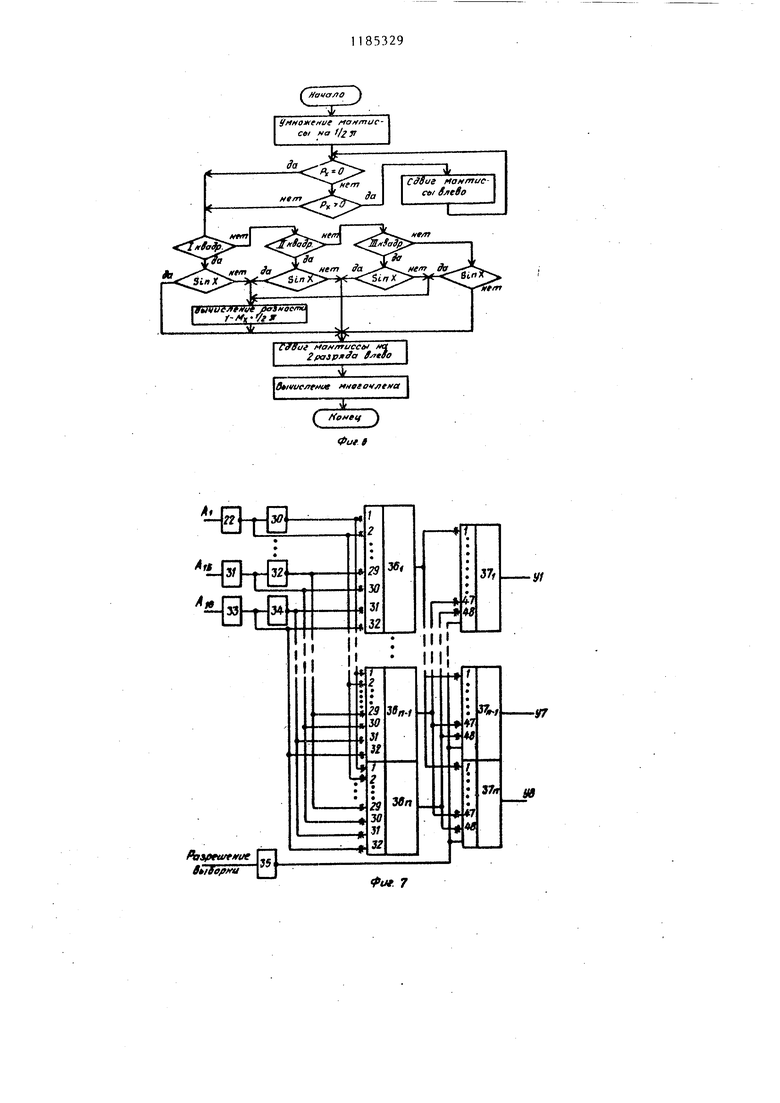

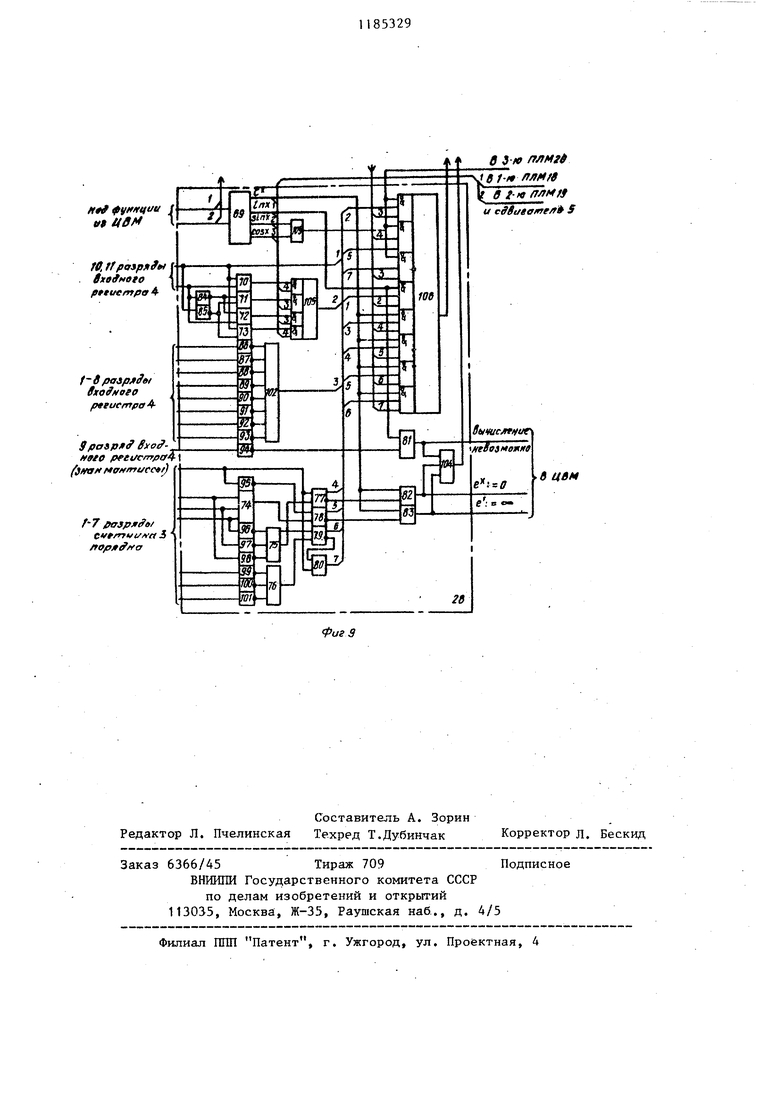

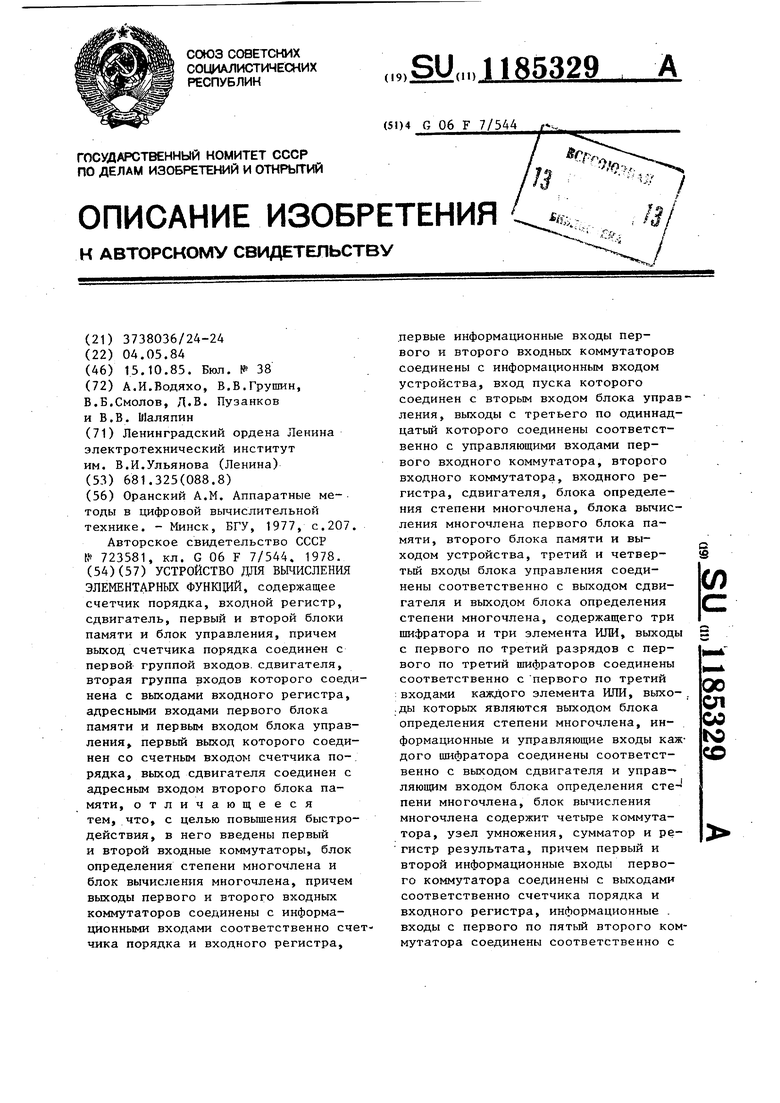

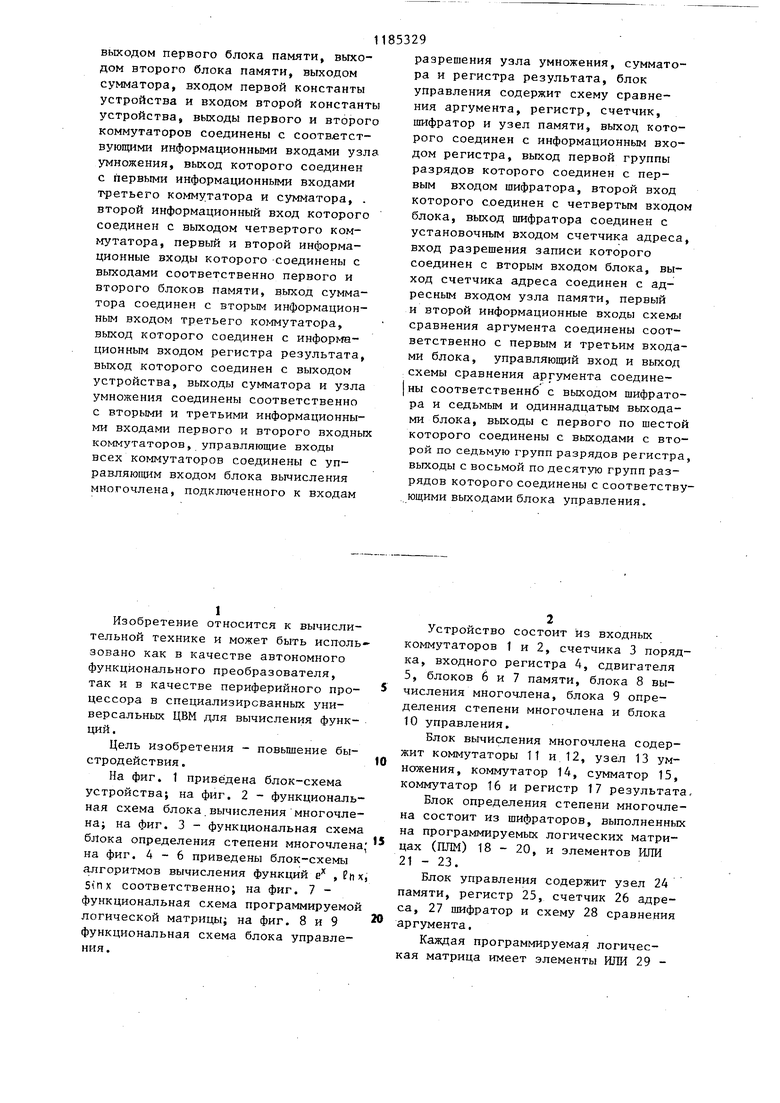

Изобретение относится к вычислительной технике и может быть исполь зовано как в качестве автономного функционального преобразователя, так и в качестве периферийного процессора в специализированных универсальных ЦВМ для вычисления функций . Цель изобретения - повышение быстродействия . На фиг. 1 приведена блок-схема устройства; на фиг. 2 - функциональ ная схема блока.вычисления многочле на; на фиг. 3 - функциональная схем блока определения степени многочлен на фиг. 4-6 приведены блок-схемы алгоритмов вычисления функций е , ц соответственно; на фиг. 7 функциональная схема программируемой логической матрицы; на фиг. 8 и 9 функциональная схема блока управления. Устройство состоит из входных коммутаторов 1 и 2, счетчика 3 порядка, входного регистра 4, сдвигателя 5, блоков 6 и 7 памяти, блока 8 вычисления многочлена, блока 9 определения степени многочлена и блока 10 управления. Блок вычисления многочлена содержит коммутаторы 11 и 12, узел 13 умножения, коммутатор 14, сумматор 15, коммутатор 16 и регистр 17 результата. Блок определения степени многочлена состоит из шифраторов, выполненных на программируемых логических матрицах (ПЛМ) 18 - 20, и элементов ИЛИ 21-23. Блок управления содержит узел 24 памяти, регистр 25, счетчик 26 адреса, 27 шифратор и схему 28 сравнения аргумента. Каждая программируемая логическая матрица имеет элементы ИЛИ 29 35, элементы И 36 и элементы ИЛИ 37 - 37. Шифратор 27 содержит счетчик 38 дешифратор 39,элементы И tO-59,элементы ИЛИ 60-66 и элементы НЕ 67 и 68. Схема сравнения аргумента 28 состоит из дешифратора 69, элементов И 70-83, элементов НЕ 84 - 101 элемента И 102, элементов ИЛИ 103 и 104 и мультиплексоров 105 и 106. Вычисление функции в устройстве разделяется на два этапа. На I этапе диапазон изменения аргумента функции .сводится к интервалу 0; 1. На II этапе происходит собственно вычисление функции. Рассмотрим приведение аргумента к интервалу 0 1 в отдельности для каждой из функций е, пх, sinx. Для вычисления функций е(фиг.5 необходимо выделить целую часть аргумента, вычислить функции от обеих частей аргумента и затем перемножить полученные значения: X -entjf x-en-tx «tx где е - функция от целой части аргумента, е - функция от дробной час ти аргумента. При этом, как показали расчеты, диапазон изменения порядка аргумен та составляет от (-7) до (+7). На вход устройства поступают мантисса аргумента (на коммутатор порядок аргумента (на коммутатор 1 признак функции е и сигнал Пуск (в блок 10 управления). По сигналу Пуск блок 10 управления записыва ет аргумент на входной.регистр 4 и счетчик 3 порядка. Затем начинаетс анализ величины порядка в блоке 10 управления. Если порядок аргуме та не равен нулю, то, в зависимости от знака порядка, алгоритм приведения к интервалу разделяется на две ветви. Пусть знак порядка аргумента больше О, тогда при РХ формируется сигнал е оо , если Рх то мантисса аргумента сдвигается влево с вычитанием единицы из величины порядка. Сдвиг мантиссы про должается до равенства порядка аргумента нулю. При сдвиге влево старшие разряды мантиссы заносятся в 1-8 разряды входного регистра 4. Эти разряды в дальнейшем служат адресом для блока 6 памяти, где хранятся величины . При 294 необходимого сдвига всей мантиссы аргумента вправо не происходит, а с помощью сдвигателя 5 вправо сдвигаются лишь разряды, составляющие старшую часть мантиссы разрядов) . Величина сдвига зависит от величины порядка аргумента, но не больше 7. Табл. 1 поясняет работусдвигателя 5 для 5 10, управляемого тремя последними разрядами счетчика 3 порядка. Если Р -7, то формируется сигнал е 0. Код, получаемый на выходах сдвигателя 5, поступает на адресные входы блока памяти 7 и на входы всех ПЛМ 18 - 20. Для программирования ПЛМ бьши определены диапазоны значений старшей части аргумента, при которых (функция аппроксимируется многочленом 5, 4 или 3-й степени (табл. 2). В табл. 3 приведены значения аргумента и состояния соответствующих им выводов ( Y1,V 2, V 3) блока 9. Признак вычисления функции Р из блока 10 управления поступает на вход Разрешение выборки ПЛМ 18. При этом остальные ПЛМ 19 и 20 не работают. Сигнал с соответствующего выхода ПЛМ 18 поступает на вход блока 10 управления и определяет какой степени (третьей, четвертой, пятой) должен в данном случае вычисляться многочлен. Многочлен вычисляется в блоке 8 вычисления многочлена (фиг. 3) по схеме Горнера: Р (х) с(((( «jxjjjj. Коэффициенты dp,..., о хранятся в блоке 7 памяти. Адресом блока 7 памяти служат старшие разряды аргумента (Хст) находящегося во входном регистре 4. Адрес, через сдвигатель 5, поступает на адресные входы блока 7 памяти. Аргумент через коммутатор 11 поступает в узел 13 умножения. Вначале выбирается коэффициент oij , который через коммутатор 12 поступает в узел 13 умножения. Параллельно с умножением происходит выборка коэффициента «4 , который суммируется с произведением «5х- Сумма o +qjj передается через коммутатор 11 на вход узла 13 умножения. Далее выполняются остальные действия необходимые для вычисления многочлена. Значение многочлена фиксируется на входном регистре 4 и регистре 17 результата По окончании вычисления многочле на в блоке 10 управления анали7 зируется содержимое 1-8 разрядов входного регистра 4 (условие oi на фиг. 5). Если все 1-8 разряды равны нулю ( oi 1), то значением фун ции будет значение многочлена. Если 1-8 разряды не равны нулю, то из блока 6 памяти выбирается значение е и передается в узел 13 умножени вместе со значением многочлена. Про ведение Р/,е через коммутатор 16 и регистр результата 17 передается на вькод. На этом процессор заканчи вает свою работу.„ Функция 2п X Приведение к интервалу fO; 1j аргумента ч х основано на следующем Пусть аргумент задается выражением )(Мх2 где Mj( - мантисса аргумента X, Р - порядок аргумента X. Логарифмируя, получают: Ьх Епм(-|-р evil. Имеет место равенство: En M|(fn(1+Z) , где О 2 1; 2 xМ)(- мантисса, сдвинутая таким о разом, что может быть представлена кодом: -1 -2Г--1 -Г| где 2 - двоичная цифра числа. Сдвиг выполняется до первой ситуации, при которой перед запят устанавливается единица, т.е. мож записать: .MJ; где If. - число сдвигов до получен кода (1) 2i. Таким образом: en х Рп (AAl2)-P, к j X X (z)+(R,-k)()+aPn2, где (Pjc. К) код, содержащийся на счетчике порядка 3. Как и в предыдущем случае на вх поступают аргумент, признак вычисляемой функции, сигнал Пуск, По сигналу Пуск блок 10 управления записьгоает аргумент во входной регистр 4 и счетчик 3 порядка. После этого происходит анализ знака мантиссы аргумента в блоке 10 управления (фиг. 6). Если знак отрицательный, то формируется сигнал Вычисление невозможно. Если знак положительный, то начинаются сдвиги аргумента влево на входном регистре 4. Сдвиги продолжаются до появления в старшем разряде входного регистра 4 единицы. Затем производится еще один сдвиг влево, чтобы получить переменную согласно (1). Для вычисления многочлена приведенный аргумент со счетчика 3 порядка и входного регистра 4 передается в узел 13 умножения. Адрес на блок 7 памяти (10 - 19-й разряды входного регистра 4) передается через сдвигатель 5 без сдвига благодаря блокировке выходов счетчика 3 порядка признаком функции, на адресные входы блока 6 памяти и на вход второй ПЛМ 19. После определения степени многочлена начинаются действия по вычислению значения многочлена аналогично описанному выше. Значение с выхода сумматора 15 передается на входной регистр 4. Затем величина, хранимая на счетчике, 3 порядка Q , передается в узел 13умножения, где умножаетсяна константу 2п2 . Константа Sn2 реализуется путем установки в четвертой группе входов коммутатора 12, необходимых потенциалов. С входного регистра 4 на сумматор 15 поступает значение многочлена, а с выхода узла 13 умножения через коммутатор 14произведение (п2 . Результат суммирования (значение функции) через коммутатор 16 и регистр 17 результата поступает на выход. Функция sinx. Сведение аргумента функции sfnх к интервалу О; 1 (фиг. 7) основано на соотношении: Sin X Sin(fy7(cf V) sin V где ) - целое число-, f- переменная в интервале 0,2)/ 2J{xf eniferx) X X ),(-entier-J, 21Т Обозначают 7 -eatfEv-, где О 2 ; 1. Два старших разряда величины указывают номер квадранта, в которо находится угол V. Представляют величину sin как sinf Sin 27/2 sin-y-V , где О : V 1. Вычисление sinjVB зависимости от квадранта, в котором находится аргумент, выполняется по формулам: Sin-V квадранта 242 -sin - d-v) для II квадрант 2 Sin LM. -Sin -Y для III квадранта Sin ((-V) для .IV квадранта Формулы вычисления cos V имеют вид: sin-(t-V) для I квадранта.; I(3) -sin-s-V для II квадранта) cosfV Sin-y-(1-vj) для III квадранта для IV квадранта По сигналу Пуск блок 10 управления записывает поступающий аргу000001 010 011 100 101

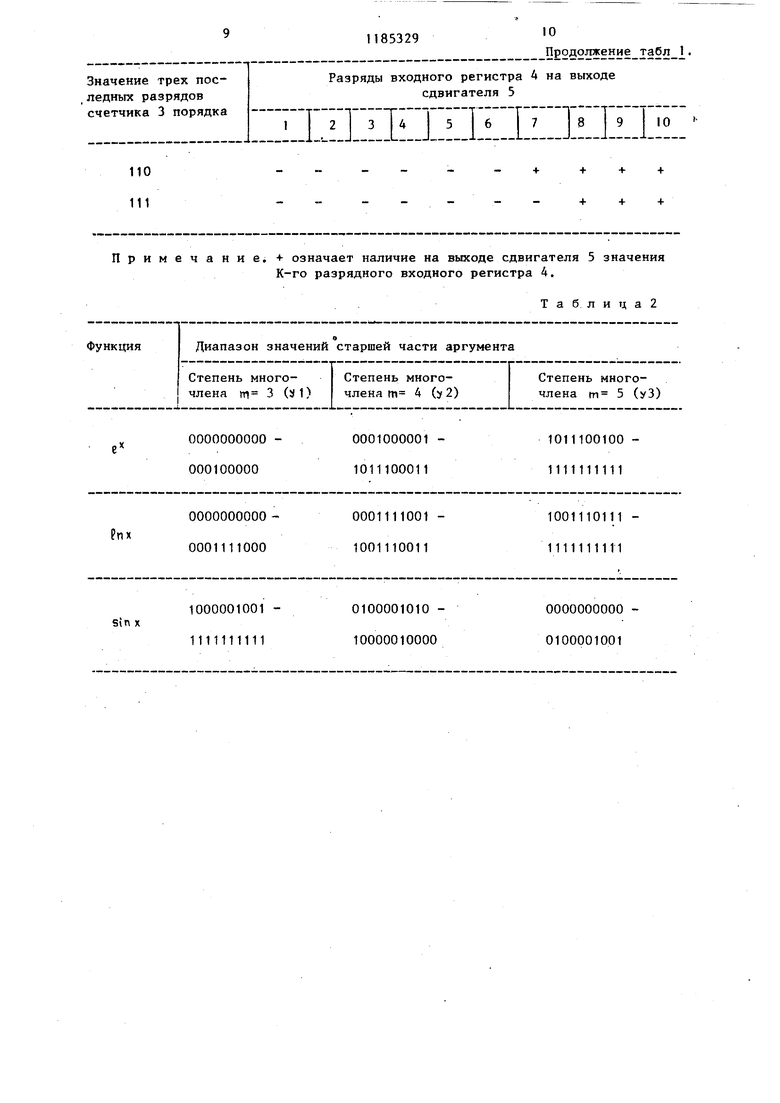

Таблица 1

+ +

ч- 4+

+

+ + ц+-t- + +

+ мент во входной регистр 4 и счетчик 3порядка. Затем аргумент умножается на м в узле 13 умножения. Произведение вновь записывается на входной регистр А. Если порядок произведения р О и , то сдвигая влево содержимое входного регистра 4, добиваются равенства порядка нулю (получают переменную 2), После вьтолнения сдвигов, или при РХ в блоке 10 управления анализируются 10 и 11 разряды входного регистра 4. В зависимости от номера квадранта и вида функции (51п5 или cos X ) принимается решение о вычитании jf MX из единицы согласно (2) и (3). Для этого аргумент передается на вход сумматора 15. Полученная разность снова записывается во входной регистр 4. Затем содержимое входного регистра 4сдвигается на два разряда влево. Если не быпо необходимости получать разность, то подобные сдвиги выполняются сразу же после определения квадранта. После этих действий содержимое входного регистра 4 передается на вход узла 13 умножения Код с выхода сдвигателя 5 поступает на вход третьей Ш1М 20 и на адресные входы блока 7 памяти. На вход Разрешение выборки третьей ПЛМ 20 поступает признак функции из блока 10 управления.

110 111 Примечание. + означает наличие на выходе сдвигателя 5 значения К-го разрядного входного регистра 4. Т а б л и ч а 2

X

о о

о о о о

т-CN

о о о

о о о

о о о о о о

о о о о о

о о о

о о о

и

ооо

оо

оо

о оо

CT

со

vO

т-IXJМ

о -- и о о -о о о

о о о

о о о

00

о-sxJ

оо ооо

ооо

о о о

о о о

о о о

о

о о

о о о о

о

X ооXо- о- -т-,.-.-т-гооооо

ооооо о

X X

g X

CNсо tlO vOГ

оо

g и

о о о о

о

о

см со

Ю4D

00

u3UBf LJ

HfOH yma-К HOf i y/Tjopan }, 2/namopof f. 2

J- 7fla3flJt f cvemwAa ffejOf/ffoS 10-5дразрл

Aof fffff / t ue/f7fla ff

taZ

1Z

ОтЗ.-гоЛЗУ7

ffmi-foffSye

0m Saoffo f florSjreMujt /O

И ЦВМ

.1

6Ц8М

re

17

IS

Ify Фив. Z

От tf управ е и/1

fffff cffft/eafrre 5

ffS/rfff y/rpcrejt fft/9

ifetfOMrf t f на

aaorntut Mnaeo etfe

f ffOffttf)

.A

C Hova/ o у

Унномгмие fto/fmuccti на 1/2 It

6 iwc/fftat f ttotov/гена

r offetf

(tf

y

Фut.f

У1

flo9flfa/fwe e /7opffa

Фм. 7

H«f u9 ном

fO, ffpospftfu pttuempo 4

1-6 раарл о p«euempa49 ,. Moeo f eei/crrrf)o fsvaf r affntffctf)

{кгзря л/ cvffrtHu a J ftop/tfffa

| Оранский A.M | |||

| Аппаратные ме- | |||

| тоды в цифровой вычислительной технике | |||

| - Минск, БГУ, 1977, с.207 | |||

| Авторское свидетельство СССР t, 723581, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1985-10-15—Публикация

1984-05-04—Подача