Изобретение относится к вычислительной технике и может быть использовано в ЭВМ и системах потокового типа для аппаратной реализации функционально-полного класса элементарных функций.

Существуют различные методы воспроизведения функций: полимиальные.таблично-полимиальные; таблично-алгоритмические.

Известно устройство, реализующее таблично-полимиальные алгоритмы, содержащее блок памяти, регистры младшей и старшей части аргумента, два регистра слагаемых, мультиплексор, сумматор и блок управления.

Недостатком устройства является низкая точность.

Известно Toke устройство содержащее блок постоянной памяти, четыре регистра и сумматор.

Это устройство реализует полимиальный алгоритм, однако имеет очень низкое быстродействие из-за большого числа операций умножения и последовательно-параллельного метода умножения, который характеризуется значительным временем умножения.

Наиболее близким по технической сущности является устройство, содержащее два блока памяти, счетчик адреса, два коммутатора, два регистра, два сумматора, элемент задержки, два умножителя, дешифратор, схему сравнения, элемент И и генератор импульсов, причем генератор импульсов через,элемент И соединен с входом счетчика, выход которого соединен с входом дешифратора и схемы сравнения, первый выход дешифратора соединен с первым входом первого коммутатора, а второй с входом первого и второго блоков памяти и первым входом второго коммутатора, первый и второй выходы первого коммутатора соединеныс первым и вторым выходами первого умножителя,, выход которого соединен с входом первого сумматора, второй вход кр торого соединен с третьим выходом первого коммутатора, а третий выход с первым выходом второго коммутатора, второй и третий выходы которого соединены с первым и вторым входами второй схемы умножения, выход которой соединен с первым входом второго сумматора, а второй вход соединен с четвертым выходом второго коммутатора, выход второго сумматора соединен с входом второго блока памяти.

Недостатком устройства является большой расход оборудования и малое быстродействие, обусловленное невозможностью работы в токовом режиме. Цель изобретения - сокращение аппаратурных затрат.

Цель достигается тем, что в устройство, содержащее блок памяти, сумматор, регистр, введены квадратор и три блока умножения и возведения в степень и шесть

элементов задержки, причем вход аргумента соединен с входом регистра и входом квадратора, выход квадратора соединен с первым входом первого и через первый элемент задержки с первым входом второго

0 блоков умножения и возведения в степень, второй вход первого блока умножения и возведения в степень соединен с первым выходом регистра, третий вход первого блока умножения и возведения в степень соединен с выходом квадратора, второй вход второго блока умножения и возведения в степень соединен с первым выходом первого блока умножения и возведения в степень, второй выход которого соединен с третьим

0 входом второго блока умножения и возведения в степень, первый и второй входы третьего блока умножения и возведения в степень соединены с первым и вторым выходами первого блоха умножения и возве5 деиия в степень, а третий вход с вторым выходом второго блока умножения и возведения 8 степень, второй выход регистра, выход квадратора, первый и второй выходы первого и второго блоков умножения и возведения в степень соответственно через первую, вторую, третью, четвертую и пятую линии задержки, а первый и второй выходы третьего блока умножения и возведения в степень непосредственно соединены с первым, втооым, третьим, четвертым, пятым, шестым, седьмым и восьмым входами блока памяти, выход которого соединен с входом сумматора.

В устройстве для. вычисления функций

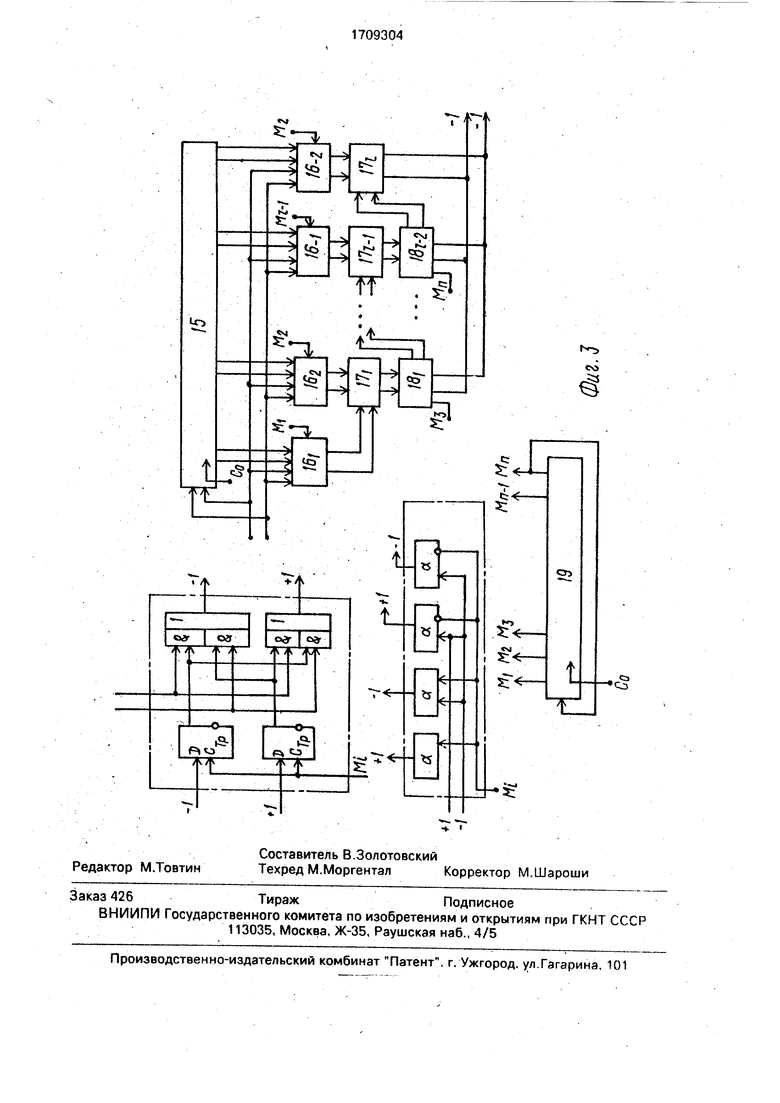

0 блок умножения и возведения в степень содержит два квадратора, вычитатель, сумматор-вычитатель и линию задержки, причем первый и второй выходы блока соединены с первыми и вторыми входами квадратора,

5 входы кйторых соединены соответственно с первыми и вторыми входами вычитателя и сумматора-вычитателя, а третий вход сумматора-вычитателя соединен через линию задержки с третьим входом устройства.

0 В известных устройствах используется параллельный код и для возведения в степень и умножения приходится использовать матричные умножители. В зависимости от требуемого быстродействия их число может

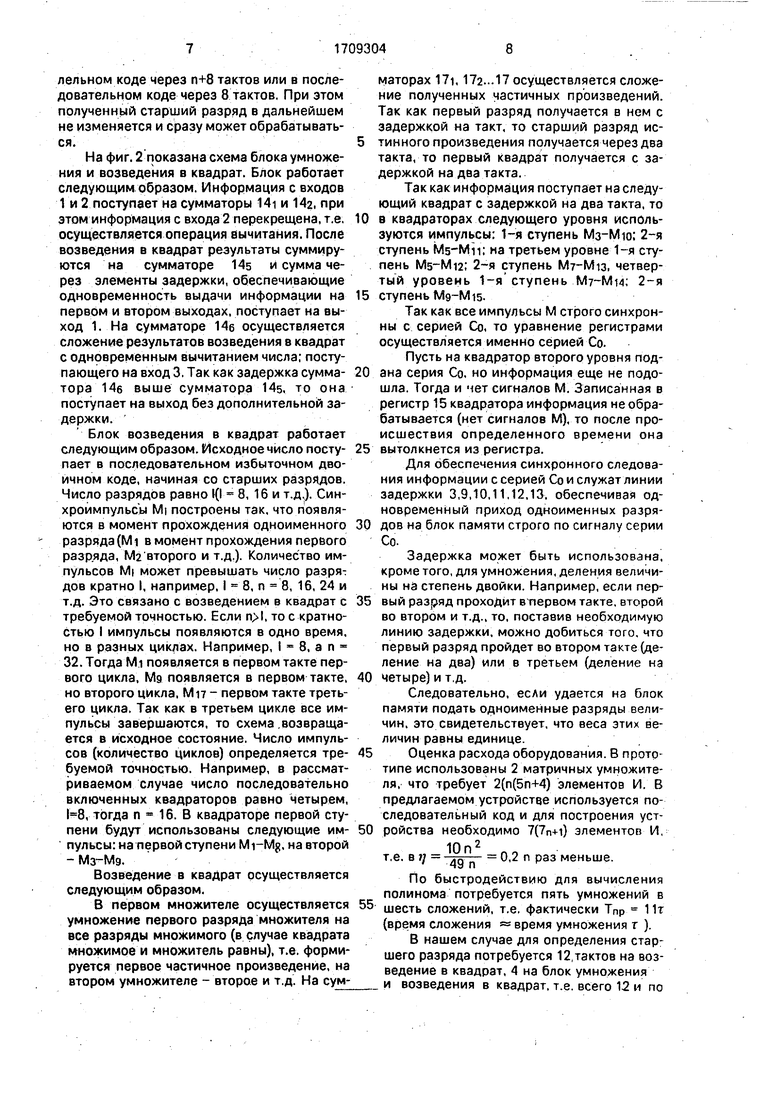

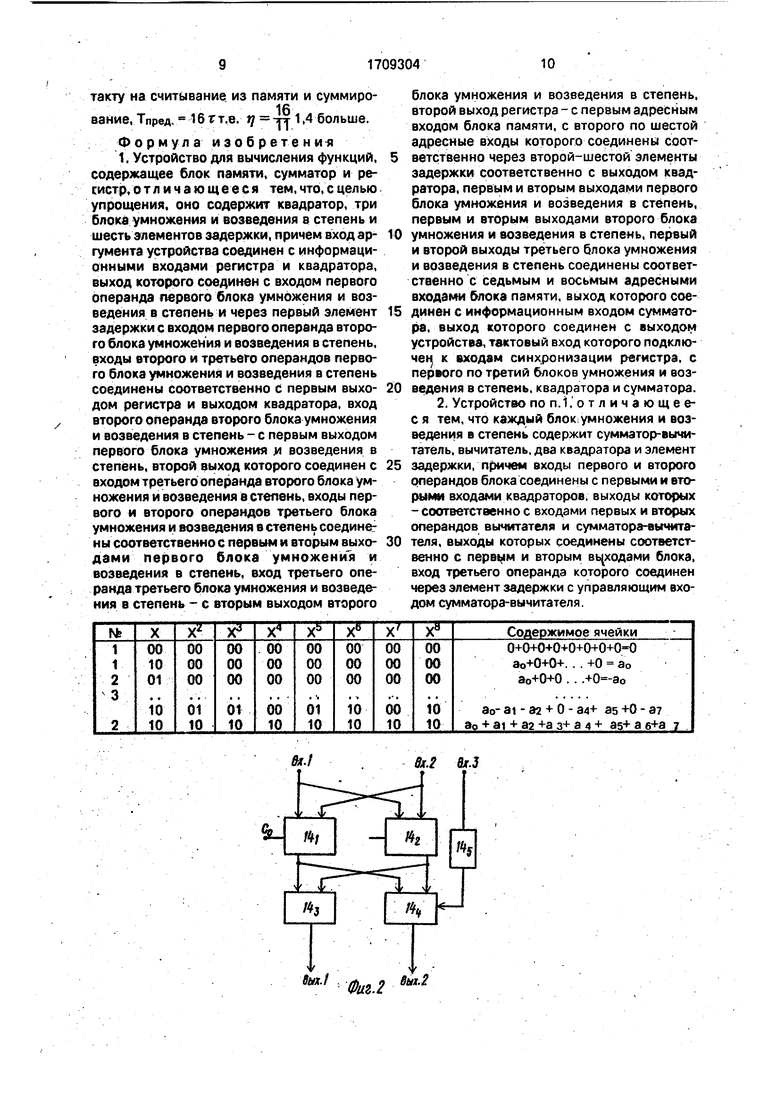

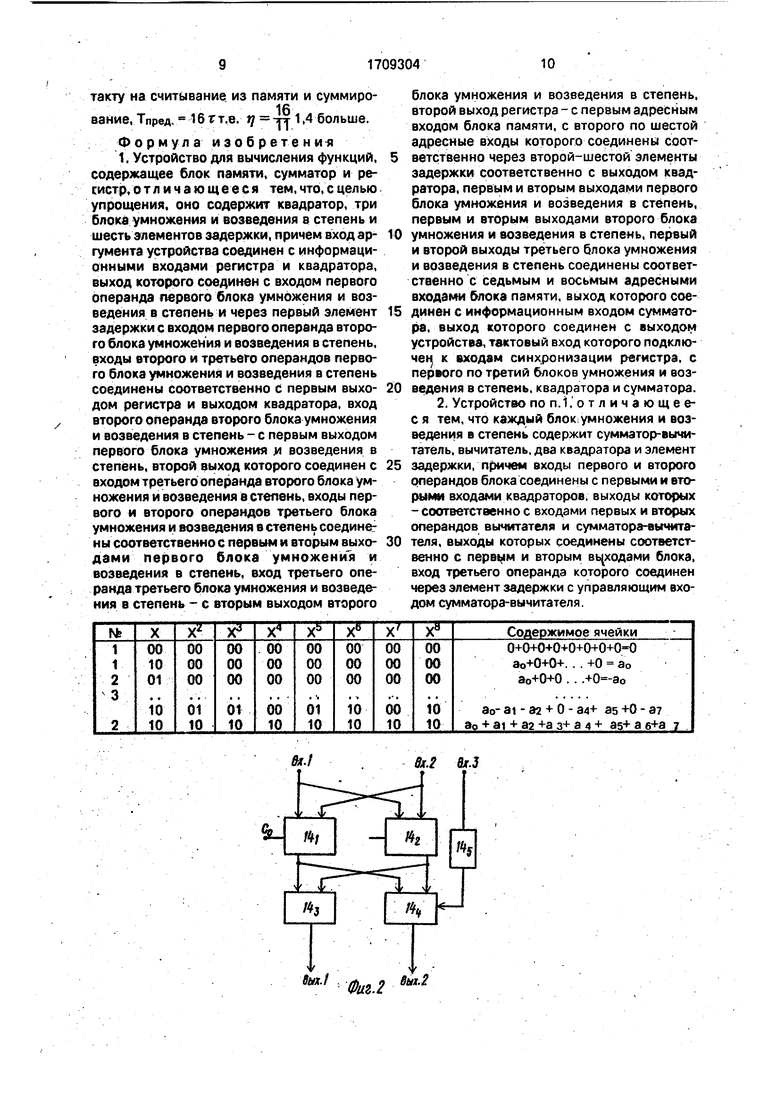

5 меняться. В прототипе полином разбивается на две группы, что требует два матричных умножителя, т.е. 2/п/5п+4// элементов И. В предлагаемом устройстве используется последовательный код и для построения ус,тройства необходимо 7х/7п+1/, т.е. в rj - -тд- U,2 n раз меньше. В то же время быстродействие устройства в целом оказывается не ниже чем в прототипе; Например для (степень полинома) имеют4tvM + 2tcvM 6 Б 8 предлагаемом устройстве результат будет 14 формироваться через 14 г. т.е. т} -- 2 3 раз меньше. На фиг 1 приведена схема устройства где обозначены регистр 1, квадратор 2, элементы задержки 3.9.10,11,12,13, блок 4,5,6 умножения и возведения в квадрат, блок 7 памяти, сумматор 8. При этом вход 1 устройства соединен с входами регистра 1 и блока возведения в квадрат 2, выход блока возведения в квадрат соединен свходом элемента задержки 3, входами 2 и 3 блока умножения и возведения в квадрат 4, вход 1, которого соединен с первым выходом регистра 1, и элементом задержки 9, вь1ход элемента задержки 3 соединен с первым входом блока умножения и возведения в квадрат 5, второй и третий входы которого соединены с первым и вторым выходом блока умножения и возведения в квадрат, которые дополнительно подсоединены к первому и второму блоку умножения и возведения в квадрат 6, к элементам задержки 10 Ч1 11, первый и второй выходы блока умножения и возведения в квадрат 5 соединены с входами элементов задержки 12 и 13, второй выход дополнительно соединен с третьим входом блока умножения и возведения в степень 6, второй выход регистра 1, выходы элементов задержек 10-13 и первый, второй выходы блока умножения и возведения в степень 6 соединены соответственно с первым и так до восьми входов блока памяти 7, выход которого соединен с входом сумматора 8, управляющие входы узлов соединены с входом Со устройства.V. На фиг. 2 изображена схема блока умножения и возведения в квадрат. Блок содержит квадраторы 14i и 142, вычислитель 14з, сумматор-вычислитеяь 144, элемент задержки 145. На фиг. 3 изображена схема возведения в квадрат, которая включает регистр 15, n однозарядных умножителей 16, п комбинационных сумматора в двоичном избыточном коде. 17 и t)-l коммутирующих ячейки 18. Устройство работает следующим образом. Аргумент X последовательным кодом старшими разрядами вперед поступает на вход регистра 1 и квадратора 2. На выходе квадратора формируется значение х, Выдача результата осуществляется после овальным двоичным знакоразрядным кодом, начиная со старших разрядов. Для .представления разряда используются цифры {1, О, 1}. Кодирование отрицательной и положительной единицы пространственное, т.е. отрицательная единица передается по одной шине, а положительная по другой, нуль кодируется отсутствием сигналов на обоих проводах. На фиг. 1 выходы для упрощения схемы однопроводные. И так сформированное значение х поступает на первый вход блока умножения и возведения в квадрат 4 (фиг.2), на второй вход поступает аргумент. Так как в квадраторе результат формируется с задержкой, то и аргумент х на вход блока 4 поступает не с входа, а с первого выхода регистра 1, что и обеспечивает требуемую задержку. На первом квадраторе формируется квадрат суммы входных аргументов. В нашем случае (х+х) + х . В котором квадрат разности (х-х) + х . На выходе вычислителя соответственно формируется (х + 2х + х - х + 2х -х 4x, а на выходе сумматора-вычислителя формируется-величина (х + 2х + х + х - 2х + х ) - 2х 2х.. Элемент задержки 145 обеспечивает поступление разрядов х синхронно с формированием результатов на выходах квадраторов 14i и 142 и умножение х на 2. Во втором блоке умножения и возведения в квадрат 5 организуется вычисление (х + х + 2х + х и ( х - 2х + х, т.е. формируются величины 4х и 2х. В третьем блоке б формируется соответственно величины 4х и 2х . Текущие разряды величин X, х, х, х, х, х, х, х поступают на входы блока памяти 17 через элементы задержки, которые обеспечивают поступление разрядов с одинаковыми весами и в совокупности образуют адрес ячейки. В каждую ячейку записана следующая информацияИными словами в каждой ячейке записана сумма коэффициентов полинома L аох + aix + а2х + азх + а4х + авх + абх + атх , каждый из которых умножен на текущий разряд аргумента х , равного {-1,0, 1}. После суммирования значения ячейки с содержимым сумматора результат сдвигается по заднему фронту сигнала Со и вычисляются следующие разряды степеней аргумента. После вычисления все 9разрядов на сумматоре образуется значение полинома L Выдача может производиться в параллельном коде через п+8 тактов или в последовательном коде через 8 тактов. При этом полученный старший разряд в дальнейшем не изменяется и сразу может обрабатываться.

На фиг. 2 показана схема блока умножения и возведения в квадрат. Блок работает следующим образом. Информация с входов 1 и 2 поступает на сумматоры 14i и 142, при зтом информация с входа 2 перекрещена, т.е. осуществляется операция вычитания. После возведения в квадрат результаты суммируются на сумматоре 145 и сумма через элементы задержки, обеспечивающие одновременность выдачи информации на первом и втором выходах, поступает на выход 1. На сумматоре 14б осуществляется сложение результатов возведения в квадрат с одновременным вычитанием числа: поступающего на вход 3. Так как задержка сумматора 14б выше сумматора 145. то она поступает на выход без дополнительной задержки.

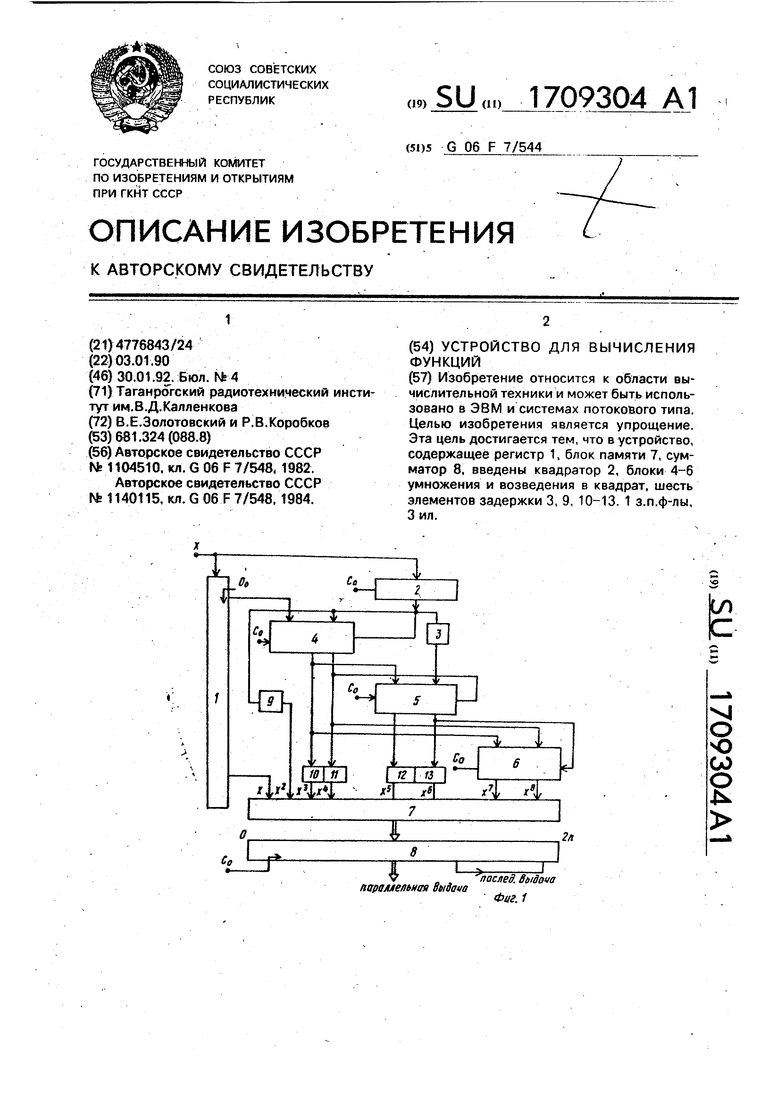

Блок возведения в квадрат работает следующим образом. Исходное число поступает в последовательном избыточном двоичном коде, начиная со старших разрядов. Число разрядов равно ( 8, 16 и т.д.,). Синхроимпульсы Ml построены так. что появляются в момент прохождения одноименного разряда (Ml в момент прохождения первого разряда. Mlвторого и т.д.). Количество импульсов М| может превышать число разрядов кратно I, например, I 8, п 8, 16, 24 и т.д. Это связано с возведением в квадрат с требуемой точностью. Если , то с кратностью I импульсы появляются в одно время, но в разных циклах. Например, I 8, а п 32. Тогда MI появляется в первом такте первого цикла. Мэ появляется в первом такте, но второго цикла, Мп - первом такте третьего цикла, Так как в третьем цикле все импульсы завершаются, то схема .возвращается в исходное состояние. Число импульсов (количество циклов) определяется требуемой точностью. Например, в рассматриваемом случае число пocлeдoвateльнo включенных квадраторов равно четырем, , тогда п 16. В квадраторе первой ступени будут использованы следующие импульсы: на первой ступени Mi-Mj, на второй - .

Возведение в кваДрат осуществляется следующим образом.

В первом множителе осуществляется умножение первого разряда множителя на все разряды множимого (в случае квадрата множимое и множитель равны), т.е. формируется первое частичное произведение, на втором умножителе - второе и т.д. На сумматорах 17i, 172...17 осуществляется сложение полученных частичных произведений. Так как первый разряд получается в нем с задержкой на такт, то старший разряд истинного произведения получается через два такта, то первый квадрат получается с задержкой на два такта.

Так как информация поступает на следующий квадрат с задержкой на два такта, то

в квадраторах следующего уровня используются импульсы: 1-я ступень Мз-Мю; 2-я ступень MS-MIi: на третьем уровне 1-я ступень M5-Mi2: 2-я ступень My-Mia, четвертый уровень 1-яступень М7-М14; 2-я

ступень Мд-М 15.

Так как все импульсы М строго синхронны с серией Со, то уравнение регистрами осуществляется именно серией Со.

Пусть на квадратор второго уровня подана серия Со, но информация еще не подошла. Тогда и чет сигналов М. Записанная в регистр 15 квадратора информация не обрабатывается (нет сигналов М), то после происшествия определенного времени она

вытолкнется из регистра.

Для обеспечения синхронного следования информации с серией Со и служат линии задержки 3,9,10,11,12,13. обеспечивая одновременный приход одноименных разрядов на блок памяти строго по сигналу серии Со.

Задержка может быть использована, кроме того, для умножения, деления величины на степень двойки. Например, если первый разряд проходит впервом такте, второй во втором и т.д.. то, поставив необходимую линию задержки, можно добиться того, что первый разряд пройдет во втором такте (деление на два) или в третьем (деление на

четыре) и т.д.

Следовательно, если удается на блок памяти подать одноименные разряды величин, это свидетельствует, что веса этих величин равны единице.

Оценка расхода оборудования. В прототипе использованы 2 матричных умножителя, что требует 2(п(5п+4) элементов И. В предлагаемом устройстве используется последовательный код и для построения устройства необходимо 7() элементов И,

т.е. в 7 лп „ 0,2 п раз меньше.

По быстродействию для вычисления полинома потребуется пять умножений в шесть сложений, т.е. фактически Тпр 11т (время сложения время умножения г ).

В нашем случае для определения старшего разряда потребуется 12,тактов на возведение в квадрат, 4 на блок умножения и возведения в квадрат, т.е. всего 12 и по

такту на считывание из памяти и суммироifiвание, Тпред. 16гт.е. j; -ту 1,4 больше.

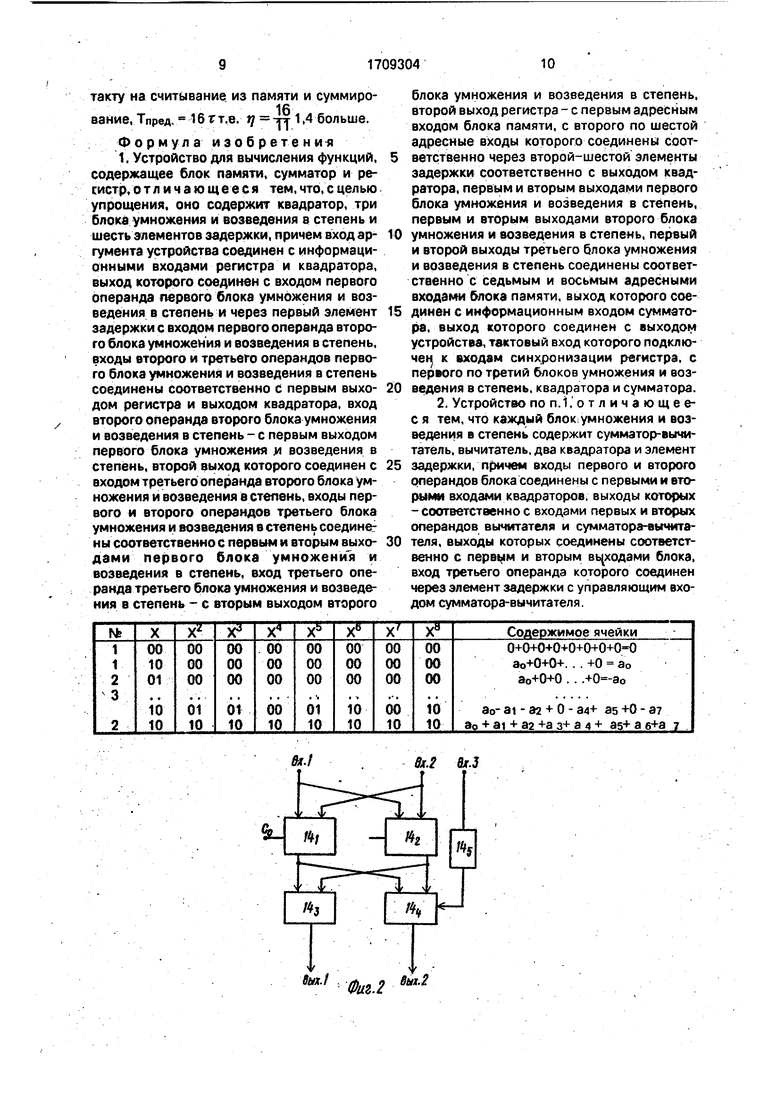

Формула и 3 о б р е те н и я 1. Устройство для вычисления функций, содержащее блок памяти, сумматор и ресистр, отличающееся тем, что, с цел ью упрощения, оно содержит квадратор, три блока умножения и возведения в степень и шесть элементов задержки, причем вход аргумента устройства соединен с информационными входами регистра и квадратора, выход которого соединен с входом первого операнда первого блока умножения и возведения в степень и через первый элемент задержки с входом первого операнда второго блока умножения и возведения в степень, входы второго и третьего операндов первого блока умножения и возведения в степень соединены соответственно С первым выходом регистра и выходом квадратора, вход второго операнда второго блока умножения и возведения в степень - с первым выходом первого блока умножения )л возведения в степень, второй вь1ход которого соединен с входом третьего операнда второго блока умножения и возведения в степень, входы первого и второго операндов третьего блока умножения и возведения а степень соединег ны соответственно с первым и вторым выходами первого блока умножений и возведения в степень, вход третьего операнда третьего блока умножения и возведе ния в степень - с вторым выходом второго

блока умножения и возведения в степень, второй выход регистра - с первым адресным входом блока памяти, с второго по шестой адресные входы которого соединены соответственно через второй-шестой элементы задержки соответственно с выходом квадратора, первым и вторым выходами первого блока умножения и возведения в степень, первым и вторым выходами второго блока

умножения и возведения в степень, и второй выходы третьего блока умножения и возведения в степень соединены соответственно с седьмым и восьмым адресными входами блока памяти, выход которого соединен с информационным входом сумматора, выход которого соединен с выходом устройства, тактовый вход которого подключе к входам синхронизации регистра, с первого по третий блоков умножения и возведения в степень, квадратора и сумматора. 2, Устройство поп.1.отличающеес я тем, что каждый блок;умножения и возведения в степень содержит сумматор-вычитатель, вычитатель, два квадратора и элемент

задержки, причем входы первого и второго операндов блока соединены с первыми и вто(шмт входами квадраторов, выходы которых - соответственно с входами первых и вторых операндов вычитателя и сумматора-вычитателя, выходы которых соединены соответственно с первцм и вторым вь ходами блока, вход третьего операнда которого соединен через элемент задержки с управляющим входом сумматора-вычитателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования | 1981 |

|

SU962926A1 |

| Устройство для выбора частотных диапазонов передачи группового радиосигнала | 1982 |

|

SU1072277A1 |

| Цифровой измеритель симметричных составляющих | 1985 |

|

SU1255964A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU678488A1 |

| Устройство для вычисления многочленов | 1988 |

|

SU1617445A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для возведения в степень | 1978 |

|

SU752334A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

Изобретение относится к области вычислительной техники и может быть использовано в ЭВМ и системах потокового типа. Целью изобретения является упрощение. Эта цель достигается тем, что в устройство, содержащее регистр 1. блок памяти 7, сумматор 8, введены квадратор 2, блоки 4-6 умножения и возведения в квадрат, шесть элементов задержки 3, 9, 10-13. 1 з.п.ф-лы. Зил.i2а•ЧОNOСОо4^>&8Lпарамеаьтгя ВыдалаJпослед. Выдача Фиг. 1

Вых.1

Вых.2

0иг.2

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1990-01-03—Подача