Изобретение отнвсится к радиотехнике и может использоваться в радиолокации.

Целью изобретения является повышение точности установки величины девиации частоты и обеспечение ее регулирования независимо от других параметров линейно- частотно-модулированных (ЛЧМ) сигналов, повышение точности установки средней частоты и обеспечение ее регулировки независимо от других параметров выходных сигналов, а также расширение диапазона регулирования периода ЛЧМ-сигналов.

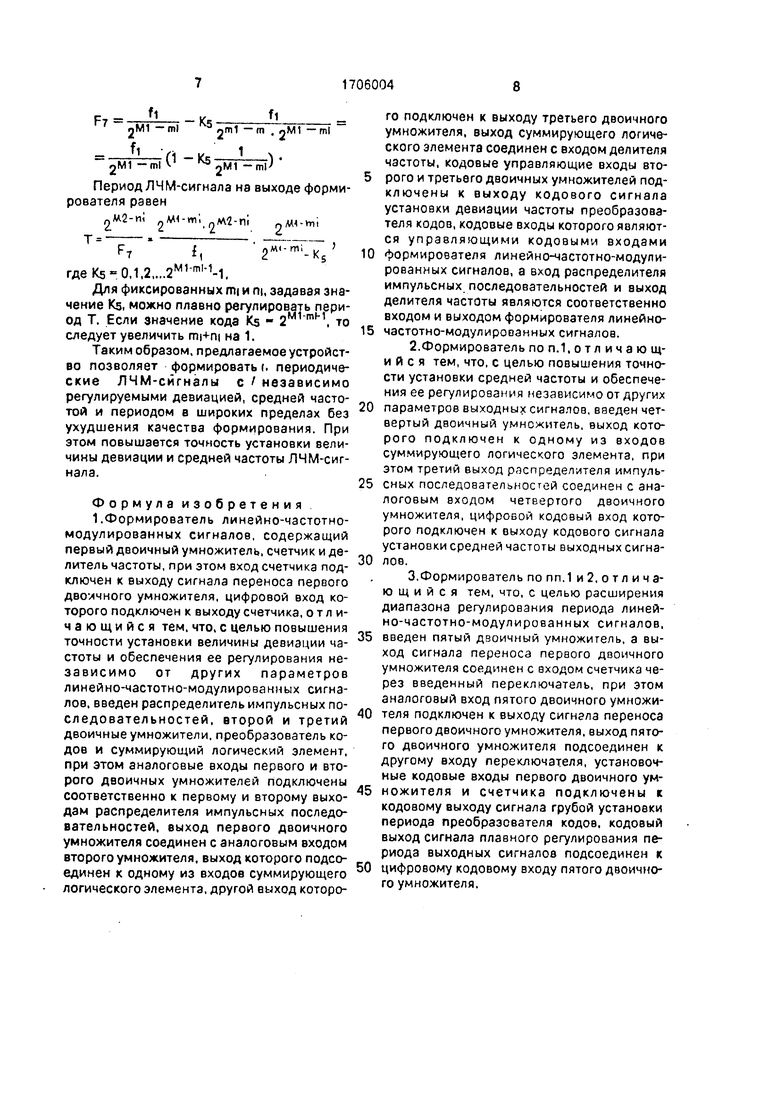

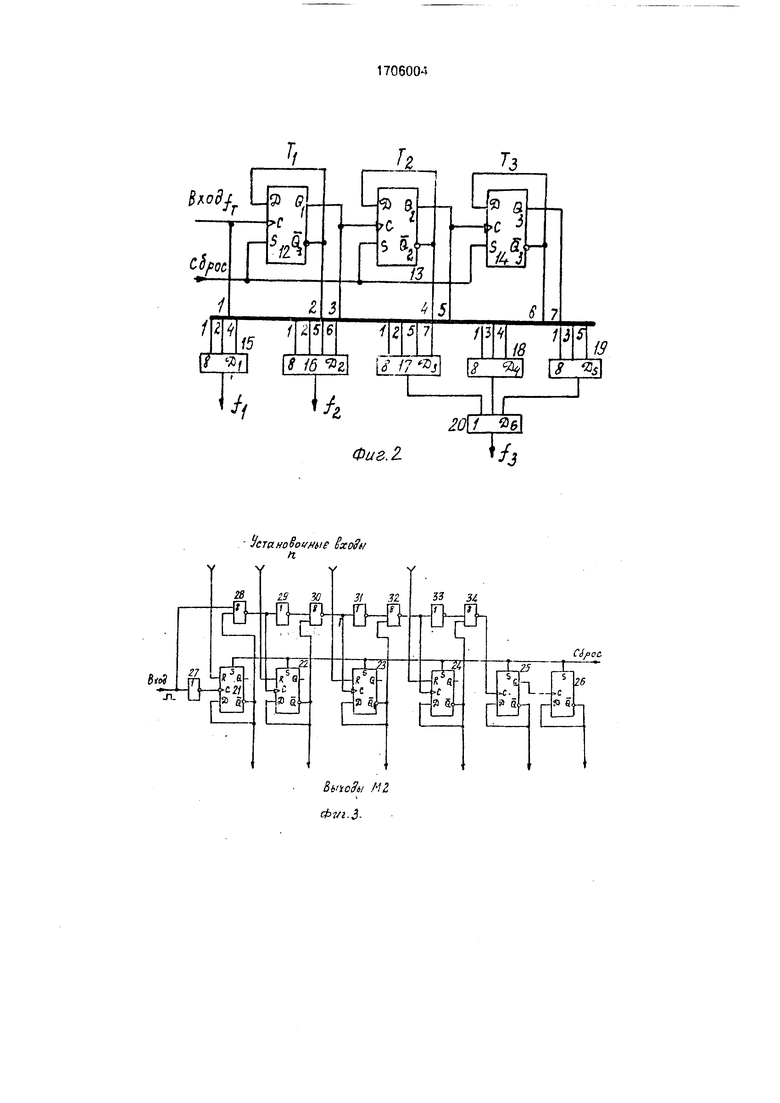

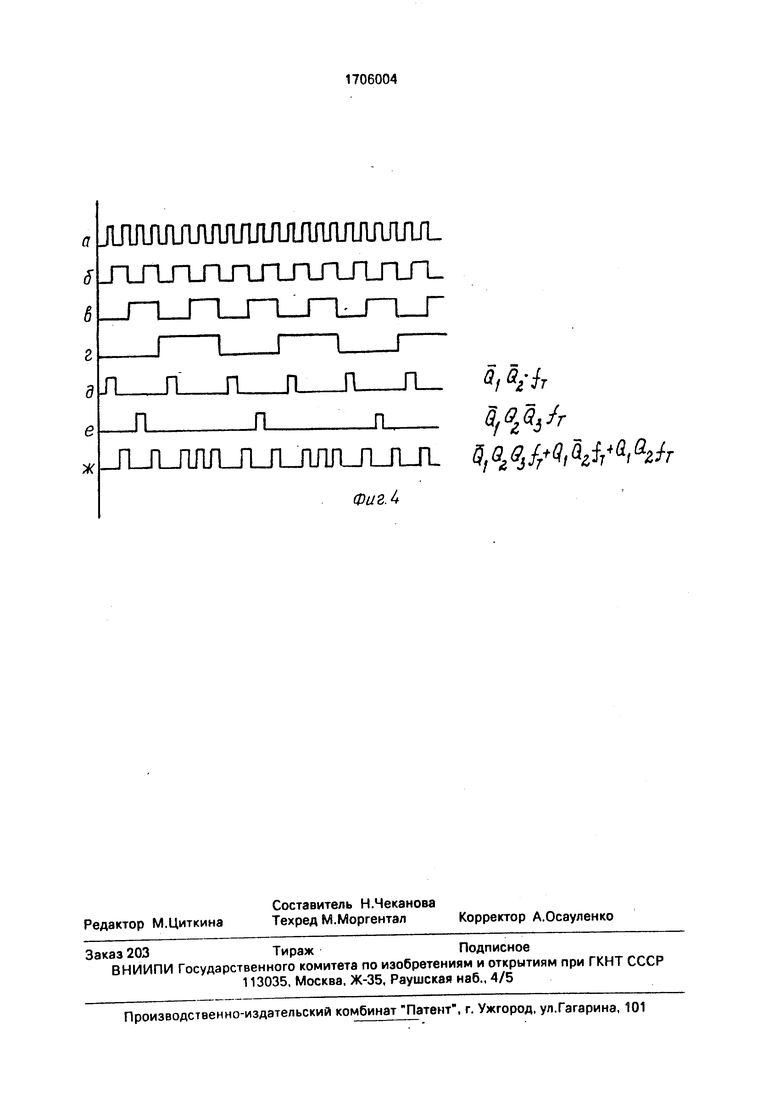

На фиг.1 приведена структурная электрическая схема формирователя линейно-частотно-модулированных сигналов; на фиг.2 - распределитель импульсных последовательностей; на фиг.З -- счетчик; на фиг.4 - диаграммы работы распределителя импульсных последовательностей.

Формирователь ЛЧМ-сигналов (фиг.1) содержит распределитель 1 импульсных последовательностей (РИП), первый - пятый двоичные умножители 2-6, счетчик 7, переключатель 8, преобразователь 9 кодов, суммирующий логический элемент 10, делитель 11 часточм. РИП 1 содержит триггеры 12-14, элементы И 15--19 и элемент ИЛИ 20. Счетчик 7 содержит Д триггеры 21-26, инверторы 27-34.

Фосмировлтель ЛЧМ-сигналов работает следующим образом.

Перед началом работы все триггеры, входящие в состав всех двоичных умножителей 2-6 (фиг.1), счетчика 7 и делителя 11 сбрасываются в начальное состояние. Переключатель 8 находится в положении А. На управляющий вход первого двоичного умножителя 2 подается логический сигнал 1 или О соответственно для растущего или падающего закона ЧМ. На управляющий вход второго двоичного умножителя 3 подается 1, э на управляющий вход третьего двоичного умножителя 4 - О. На первый вход преобразователя 9 кодов поступает код, задающий девиацию частоты Л F. На вход РИП 1 поступают колебания прямоугольной формы с тактовой частотой fT (фиг.4а). На фиг.46,в и г показаны сигналы на выходах См.СЬ.Оз соответственно триггеров 12,13,14, входящих в состав РИП 1. В результате логических операций, выполняемых логическими элементами, входящими в состав РИП 1, на его выходах образуются три импульсных последовательности, положительные импульсы которых не перекры- вйются во времени. В маетности, на первом выходе РИП 1 образуется импульсная последовательность с частотой fi Тт/2 : fT/4 (фиг.4д), на втором выходе образуется импульсная последовательность с частотой f2

fr/22 fr/8 (фиг.4е), на третьем выходе образуется импульсная последовательность с частотой fa -- fT - (М -t f2) 5fT/8. Сигнал о частотой ft с первого выхода РИП

поступаем на аналоговый вход первого двоичного умножителя 2 емкостью М1 двоичных разрядов. С выхода переноса первого двоичною умножителя 2 сигнал с частотой Fn fi/V поступает на вход счетчика 7

емкостью М2 двоичных разрядов, при этом И2 Mi или Мз МН. Счетчик 7 формирует код Ki, линейно изменяющийся от 0 до 2 - 1, Код Кт поступает на цифровой вход первого двоичного умножителя 2, При

формировании сигнала с линейно растущей частотой нп управляющий вход первого двоичного умножителя 2 подано напряжение Г и на его выходе образуется сигнал с частотой Fi Ki fi/2M2, линейно увеличивающийся от 0 до tVfi/2M2. При формировании сигнала с линейно падающей частотой на управляющий вход первого двоичного умножителя 2 подается напряжение О и на его выходе образуется сигнал с частотой FI

fi-Kix xfi/2 , линейно уменьшающейся от fi до fi/2 . Средняя частота формируемого сигнала равна Ficp Fi(1-1/2 )/2.

С выхода первого двоичного умножителя 2 сигнал поступает на аналоговый вход

второго двоичного умножителя 3 емкостью

МЗ двоичных разрядов. Одновременно на

его цифровой вход с первого выхода преобразователя кодов 8 поступает код

К2 0,1,2,...2 , определяющий девиацию

частоты AF. В результате на выходе второго двоичного умножителя 3 образуется сигнал с частотой F2 - К2 Fi/2M3. Девиация частоты этогосигнала равна (M/2 М2)/2МЗ,

ас р е д н я я

р., -к, + - К2 f

- iv. 1/ fчастота1

LL ( - .

0M3 4- 1 k 2м2

0

5

Изменяя величину кода К2, можно регулировать девиацию частоты, однако при этом изменяется средняя частота F2cp. что нежелательно. Для компенсации изменения средней частоты F2Cp импульсная последовательность с частотой f2 fi/2 с второго выхода РИП 1 подается на аналоговый вход третьего двоичного умножителя 4 емкостью Мз двоичных разрядов, на цифровой вход которого поступает код К2, определяющий девиацию частоты, а на управляющий вход подан сигнал О. При этом на выходе третьего двоичного умножителя 4 образуется сигнал с частотой

F,lifi LV

h3 2 ( 2Ш

Сигналы с выходов второго и третьего двоичных умножителей 3,4 поступлю соотсетственно на первый и второй входы суммирующего логического элемента 10. Нэ его выходе образуется сигнал со следующей частотой

F4cp F2cp+F3cp T(1-) +

+Јо

К2ч

щ)

fln

у U

К2 л ,М2 МЗ

2М2+мз эначите,,ьно больше 1,

Поскольку

средняя частота практически постоянна и равна F4cp-fi/2.

Сигнал с выхода суммирующего логического элемента 10 поступает на вход делителя 11с коэффициентом деления N, сглаживающего неравномерность полученной импульсной последовательности. На выходе делителя 11 образуется ЛЧМ-сигнал прямоугольной формы с частотой

F-fi/2- N+ AF/2 и девиацией частоты

UF - Средняя частота этого сигнала практически постоянна и равна FCp - fi/2 N. а период

равен Т

,M1 +M2

Для регулирования средней частоты ЛЧМ-сигнала на второй вход преобразователя 9 кодов от какого-либо устоойства или переключателя подается код средней частоты, который образуется в соответствующий код Кз. Этот код поступает на цифровой вход четвертого двоичного умножителя 5 емкостью Мз двоичных разрядов, на управляющий вход которого подан сигнал 1, На аналоговый вход четвертого ДБОИЧНОГО умножителя 5 с третьего выхода РИП 1 поступает импульсная последовательность с частотой (з. Частота сигнала на выходе четвертого двоичного умножителя 5равна Fs Кз тз/2М4, где Кз - 0,1,2,...2М4-1. Этот сигнал поступает на третий вход суммирующего логического элемента 10, где он складывается с сигналами, поступающими с выходов второго и третьего двоичных умножителей 3,4. Полученный сигнал поступает на делитель 11, на выходе которого (фиг.4ж) образуется ЛЧМ-сигнал со средней частотой

Ffcp V2 N + .

Для регулирования периода формируемого ЛЧМ-сигнала на третий вход преобразователя 9 кодов подается код П, состоящий из Р двоичных разрядов, задающих грубое изменение периода, и 2 разрядов, задающих плавное изменение периода. Код Т| преобразуется в код К4 грубой регулировки периода и код КБ плавной регулировки периода. Код KU поступает на m последних установочных входов первого двоичного умножителя 2 и на п первых установочных входов счетчика 7. С помощью этого кода

регулируется емкость первого двоичного умножителя 2 путем последовательного отключения его триггеров, начиная со старшего разряда, и емкость счетчика 7 путем последовательного отключения его триггеров, начиная с младшего разряда. При этом должно соблюдаться условие (Mrmi)-(M2-ni)-0 либо (Mi-mi)-(M2-ni)- 1, где mi - 0,1,2,.... m - число отключенных

триггеров первого двоичного умножителя 2; m - 0,1,2,..., п - число отключенных триггеров счетчика 7. Значение периода формируемого ЛЧМ-сигнала равно

20

Т

2М1 -ml 2м2 п|

Таким образом, изменяя разрядность MI первого двоичного умножителя 2 и М2 счетчика 7. грубо (с шагом, равным степени двойки) регулируют период формируемого ЛЧМ-сигнала. При формировании ЛЧМ-сигнала происходит ступенчатое увеличение частоты, величина ступенькиAf

А,ft рэвнаД -щ-г:-г а период ступеньки

ЛТ

)М2 - nl

Произведение

Д f Д Т Д В характеризует качество формирования ЛЧМ-сигнала и называется базой скачка. Оно равно 1 либо 2 при любых значениях Mi, Мз и mi, щ, т. е. при регулировке периода качество формирования

ЛЧМ-сигнала не ухудшается. Код К4, определяющий значение периода, содержит m-t-n двоичных разрядов. Количество периодов равно rn+n. Соответствующий код П содержит Р (m+n)}+1 двоичных разрядов.

где ent -операция выделения целой части. Для плавной регулировки периода переключатель 8 устанавливают в положение В. Одновременно с кодом Кз, подаваемым на установочные входы первого двоичного умножителя 2 и счетчика 7, с четвертого выхода преобразователя 9 кодов поступает код КБ на цифровой вход пятого двоичного умножителя б емкостью 2 двоичных разрядов, на аналоговый вход которого поступает сигнал с выхода переноса первого двоичного умножителя 2, На управляющий вход пятого двоичного умножителя 6 поступает О. При этом на его выходе образуется сигнал, частота которого равна

,M1 -ml

- m . «Ml - ml

1

,M1 -ml

0-К5; м г)

Период ЛЧМ-сигнала на выходе формирователя равен

-MI-tTh

,/VM-Hit

«1

-K«

,M1-ml-1

гдеКз-О.и,.. - 1 - - ,

Для фиксированных mi и m, задавая значение Ks, можно плавно регулировать период Т. Если значение кода Ks - , то следует увеличить тн-гн на 1.

Таким образом, предлагаемое устройство позволяет формировать t. периодические ЛЧМ-сйгналы с / независимо регулируемыми девиацией, средней частотой и периодом в широких пределах без ухудшения качества формирования. При этом повышается точность установки величины девиации и средней частоты ЛЧМ-сигнала.

Формула изобретения 1 .Формирователь линейно-чзстотно- модулированных сигналов, содержащий первый двоичный умножитель, счетчик и делитель частоты, при этом вход счетчика подключен к выходу сигнала переноса первого двоичного умножителя, цифровой вход которого подключен к выходу счетчика, отличающийся тем. что, с целью повышения точности установки величины девиации частоты и обеспечения ее регулирования независимо от других параметров линейно-частотно-модулированных сигналов, введен распределитель импульсных последовательностей, второй и третий двоичные умножители, преобразователь кодов и суммирующий логический элемент, при этом аналоговые входы первого и второго двоичных умножителей подключены соответственно к первому и второму выходам распределителя импульсных последовательностей, выход первого двоичного умножителя соединен с аналоговым входом второго умножителя, выход которого подсоединен к одному из входов суммирующего логического элемента, другой выход которого подключен к выходу третьего двоичного умножителя, выход суммирующего логического элемента соединен с входом делителя частоты, кодовые управляющие входы второго и третьего двоичных умножителей под- ключены к выходу кодового сигнала установки девиации частоты преобразователя кодов, кодовые входы которого являются управляющими кодовыми входами

формирователя линейно-частотно-модулированных сигналов, а вход распределителя импульсных последовательностей и выход делителя частоты являются соответственно входом и выходом формирователя линейночастотно-модулированных сигналов.

2.Формирователь по п.1, отличающийся тем, что, с целью повышения точности установки средней частоты и обеспечения ее регулирования независимо от других

параметров выходных сигналов, введен четвертый двоичный умножитель, выход которого подключен к одному из входов суммирующего логического элемента, при этом третий выход распределителя импульсных последовательностей соединен с аналоговым входом четвертого двоичного умножителя, цифровой кодовый вход которого подключен к выходу кодового сигнала установки средней частоты выходных сигналов.

3.Формирователь по пп, 1 и 2, о т л и ч а- ю щ и и с я тем, что, с целью расширения диапазона регулирования периода линейно-частотно-модулированных сигналов,

введен пятый двоичный умножитель, а выход сигнала переноса первого двоичного умножителя соединен с входом счетчика через введенный переключатель, при этом аналоговый вход пятого двоичного умножителя подключен к выходу сигнала переноса первого двоичного умножителя, выход пятого двоичного умножителя подсоединен к другому входу переключателя, установочные кодовые входы первого двоичного умножителя и счетчика подключены к кодовому выходу сигнала грубой установки периода преобразователя кодов, кодовый выход сигнала плавного регулирования периода выходных сигналов подсоединен к

цифровому кодовому входу пятого двоичного умножителя.

Г,

h

r3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения параметров линейно-частотно-модулированных сигналов | 1990 |

|

SU1734033A1 |

| Устройство для телевизионной игры | 1977 |

|

SU736992A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1995 |

|

RU2097829C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1988 |

|

SU1841042A1 |

| Формирователь линейно-частотно-модулированных сигналов | 1984 |

|

SU1241410A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Широтно-импульсный преобразователь | 2018 |

|

RU2683180C1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1990 |

|

SU1841066A2 |

| Устройство формирования линейно-частотно-модулированных сигналов | 1989 |

|

SU1617621A1 |

Изобретение относится к радиотехнике и может использоваться в радиолокации. Целью изобретения является повышение точности установки величины девиации частоты и обеспечение ее регулирования независимо от других параметров линейно-частотно-модулированных (ЛЧМ) сигналов, повышение точности установки средней частоты и обеспечение ее регулировки независимо от других параметров выходных сигналов, а также расширение диапазона регупи- рования периода ЛЧМ-сигналов. Формирователь ЛЧМ содержит распределитель импульсных последовательностей (РИП) 1, первый - пятый двоичные умножители 2-6, счетчик 7, переключатель 8, преоб- разователь 9 кодов, суммирующий логический элемент 10, делитель 11 частоты. Все двоичные умножители упрэвпяются кодовыми сигналами от преобразователя 9 кодов и формируют ЛЧМ-сигналы с заданными параметрами. На выходе РИП формируются импульсные последовательности, поступающие на соответствующие двоичные умножители. Все двоичные умножители управляются кодовыми сигналами от преобразователя 9 и каждый из них обеспечивает установку и регулировку одного из параметров ЛЧМ-сигналов независимо от другого параметра. 2 з.п.ф-лы, 4 ил. 00 t VJ О О о о 4

- Установочные Uxoltt/

n

Bb tcdti MZ cbi/t-3.

JШnШШЛЛJlЛJШLfШЛЛJUШl

5

п

л

я

п

ж

JTJTJTJIHJJL

Фиг. 4

п

, 5;Ь

8fW

WifcQM

| Устройство для формирования линейно переключаемых частот | 1973 |

|

SU599328A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-01-15—Публикация

1989-03-24—Подача