1

(21)4655690/24

(22)27.02.89

(46) 07.01 .91. Бюл. № 1

(72) А.В.Василъкевич и М.Н.Яцимирский

(53)681.333(088.8)

(56)Зарубежная радиоэлектроника, 1987, № 7, с.86, рис.1.

Воробейчик Е.А.Фильтрация изображений при вводе видеоинформации в ЭВМ.-М.: ВИНИТИ, 1984, № 6726, с.3-5, рис.1, 2.

(54)УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОЙ СВЕРТКИ

(57)Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных систем

функционирующих в реальном масштабе времени. Пель изобретения сокращение аппаратурных затрат. Устройство содержит сдвиговые регистры 1 и 2, сумматоры 3-8, умножители 9-11, буферные регистры , вход 18 тактовых импульсов, информационный вход 19 устройства, группу входог 20-22 задания коэффициентов ядра свертки, информационный выход 23 устройства. Устройство позволгет вычислять двумерную свертку исходного массива Ьт с симметричным относи- тельно центра ядром (1, р 1; 3). Организация вычислений в конвейерном режиме обеспечивает высокое быстродействие устройства. 2 ил.

иэ

(S,

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельного вычисления цифровой двумерной свертки | 1986 |

|

SU1416976A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СРЕДНЕГО ЗНАЧЕНИЯ | 1990 |

|

RU2015552C1 |

| Систолический процессор цифровой обработки сигналов | 1987 |

|

SU1471200A1 |

| Устройство для цифровой двумерной свертки | 1985 |

|

SU1264309A1 |

| Устройство для преобразования изображений объектов | 1988 |

|

SU1608712A1 |

| Устройство для преобразования изображений объектов | 1989 |

|

SU1672490A1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1211748A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для вычисления свертки | 1984 |

|

SU1198535A1 |

рэ

Ъ рз

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных систем, функционирующих в реальном масштабе времени.

11ель изобретения - сокращение аппаратурных затрат.

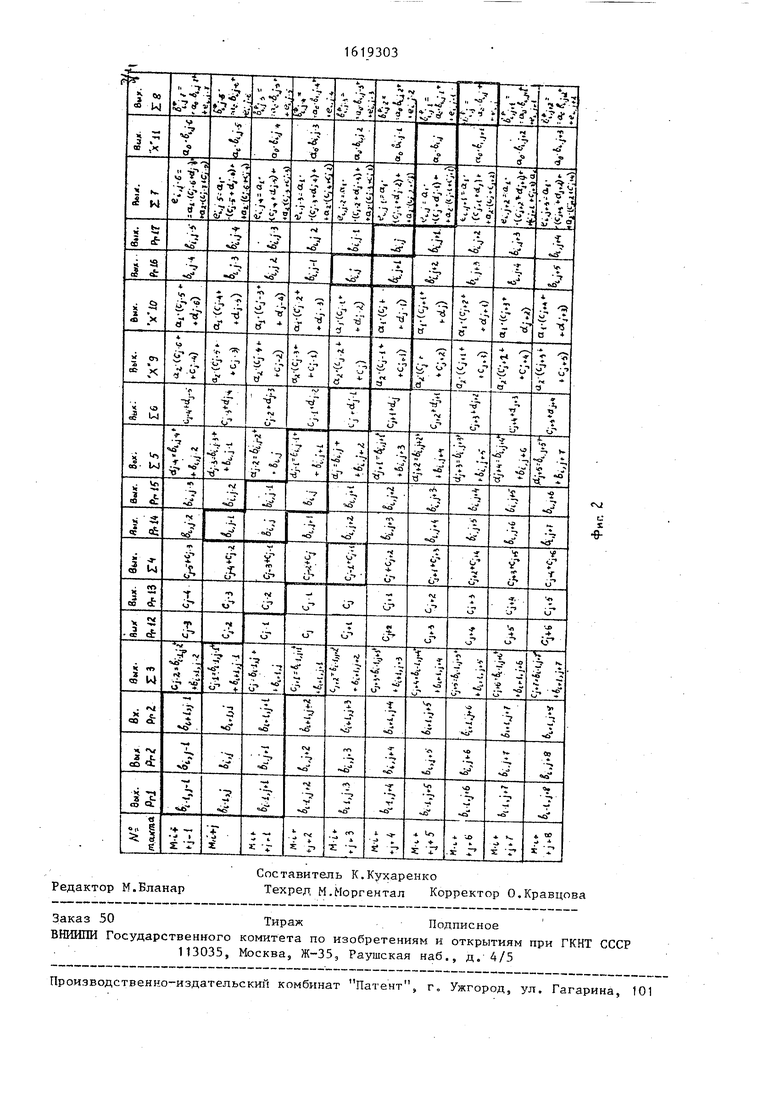

На фиг. 1 изображена схема устройства J на фиг. 2 - временная диа грамма функционирования устройства.

Устройство содержит сдвиговые регистры 1 и 2, сумматоры 3-8, умножители 9-11, буферные регистры 12-17, вход 18 тактовых импульсов, информационный вход 19 устройства, группу входов 20-22 задания-Коэффициентов ядра свертки, информационный выход 23 устройства.

Устройство позволяет вычислять двумерную свертку bj; исходного массива bjj с коэффициентами ядра свертки

е,р.

согласно выражению {

ЪТ. 21 ZI аро, (1)

25

i-e,j-p- ц-, 3

i О, j « Г7м

ричем коэффициенты ядра свертки обадают симметрией относительно центра кна вида

а2 а. аа

а ао

а

г

LЈ

35

40

Краевые эффекты в предлагаемом устройстве на учитываются.

Устройство работает следующим образом.

Отсчеты двумерного массива поступают на информационный вход 19 устройства по строкам и заполняют регистры 1 и 2 сдвига, длина каждого из которых составляет М (М - количество элементов в строке). Начиная с такта 2М+1, когда в регистре 1 сдвига Д5 записаны отсчеты первой строки, а в регистре 2 сдвига отсчеты второй строки, устройство вычисляет точный результат свертки согласно выражению (1).50

Рассмотрим работу устройства в произвольный момент времени, когда в регистр 1 записаны отсчеты (1-1)-й строки, в регистр 2 - отсчеты 1-й строки, а на информационный вход 19 устройства поступают отсчеты (1+1)-й строки.

В этом случае в устройстве обрабатываются отсчеты трех смежных строк

55

5

0

двумерного массива которые поступают в следующей последовательности:

(i-D-я строка: ..., b;Hj(, b;H

bM,+i bi-«,bz bi-«ij+3

i-я строка: ..., Ъ}., , b j(j ,

bi.j4 b J + 2

(i+O-я строка: .... Ь;( , ,

bi+,j-n b«+i,j+2 bvH,j+3 Таким образом, в такте (M i + j-1) на первый вход сумматора 3 с выхода регистра 1 сдвига поступает отсчет Ь,.( г, , а на второй вход сумматора 3 через информационный вход 19 устройства поступает отсчет bft, , на вход регистра 14 с выхода регистра 2 сдвига поступает отсчет (фиг.2).

.

Формирование результата свертки выделено на временной диаграм5

5

0

Д550

55

ме утолщенными линиями.

В такте (M«i + j) с выхода регистра 1 сдвига поступает отсчет Ь,; , с выхода регистра 2 сдвига - отсчет b ,. , по информационному входу 19 поступает отсчет bj+( , на выходе сумматора 3 появляется сумма с: , Ъ ( ,.+ + bi-nj-t, а на выходе регистра 14 - задержанный на такт отсчет Ь,; .

В такте + i + 1) с выхода регистра 1 поступает отсчет b(.|Ij+j, с выхода регистра 2 - отсчет b{ j+, , по информационному входу 19 поступает отсчет b, 4,j4 , на выходе сумматора 3 появляется сумма cj b |, J + + btV , на выходе регистра 12 - задержанная на такт сумма , на выходе регистра 14 - задержанный на такт отсчет b M , на выходе регистра 15 - задержанный на два такта отсчет bij- .

В такте (M i + j+2) на выходе сумматора 3 появляется сумма с . + Ь{( + bj4lt на выходе регистра 12 - задержанная на такт сумма с j, на выходе регистра 13 - задержанная на два такта сумма cj) , на выходе регистра 15 - задержанный на два такта отсчет bjj , а на выходе сумматора 15 появляется сумма dL, bjfj-,+

В такте (M-i + j+З) на выходе сумматора 4 формируется сумма с +

+ CJ-K bM,j-i+ bitt,H+ + binblj , на выходе сумматора 6 формируется

сумма с + dj.., b,.(, + +

+ b,j, + , на выходе регистра

16 появляется задержанный на три такта отсчет bjj .

В такте (W i + j+4) на выходе умножителя 9 формируется произведение а-.Сс, + CJ.J., ), на выходе умножителя 10 - произведение a /Cj + dj(), на выходе регистра 17 появляется задержанный на четыре такта отсчет Ь,-;.

В такте (M i + j+5) на выходе сумматора 7 формируется сумма - e,i - - at(cj + d j, )+ae(cj,+ cj.(), а на выходе умножителя 11 формируется произведение а0- b f(j .

В такте (w.i+j+б) на выходе сумматора ,8 формируется результат свертки для отсчета (i, j) bjj V Ч ч еч + a(bi-M + bui,j + bj,j., + Ь;,.ц )+ а.г(Ьн(, -,+

+ ;+,.+ + bi- .j-n + bUt, J-H )

Одновременно с формированием результата ..свертки bjj происходит формирование промежуточных результатов для вычисления последующих результатов свертки b,(J4(, b}( „

Дальнейшая работа устройства аналогична описанной.

Формула изобретения

Устройство для вычисления двумерной свертки, содержащее .два сдвиговых регистра, шесть сумматоров, шесть буферных регистров и три умножителя, первые информационные входы которых образуют группы входов задания коэффициентов ядра свертки, выход второго сдвигового регистра соединен с информационными входами первого сдвигового регистра и первого буферного регистра, выход которого соединен с информационным входом второго буферного регистра, выход которого соединен с информационным входом третьего буферного регистра, выход первого сумматора соединен с вторым информационным входом первого умножителя, выход которого подключен к первому

0

0

5

0

5

0

5

информационному входу второго сумматора, второй информационный вход которого подключен к выходу второго умножителя, второй информационный вход которого подключен к выходу третьего сумматора, выход третьего умножителя соединен с первым информационным входом четвертого сут-гматора, второй информационный вход которого соединен с выходом второго сумматора, выход четвертого сумматора является информационным выходом устройства,, входы синхронизации сдвиговых регистров, сумматоров, умножителей и буферных регистров объединены и подключены к входу тактовых импульсов устройства, о тличающееся тем,что5 с цепью сокращения аппаратур-- ных затрат, информационный вход устройства соединен с информационным входом второго сдвигового регистра ч первым информационным входом пятеро сумматора, второй информационный вход которого соединен с выхо- цом первого сдвигового регистра, выход пятого сумматора подключен к первому информационному входу первого сумматора и информационному входу четвертого буферного регистра, выход которого подключен к первому информационному входу третьего сумматора н информационному входу пятого буферного регистра, выход которого соединен с вторым информационным входом первого сумматора, выход второго сдвигового регистра соединен с первым информационным входом шестого сумматора, второй информационный вход которого соединен с выходом второго буферного регистра, выход шестого сумматора соединен с вторым информационным входом третьего сумматора, выход третьего буферного регистра соединен с информационным входом шестого буферного регистра, выход которого соединен с вторым входом третьего умножителя.

Авторы

Даты

1991-01-07—Публикация

1989-02-27—Подача