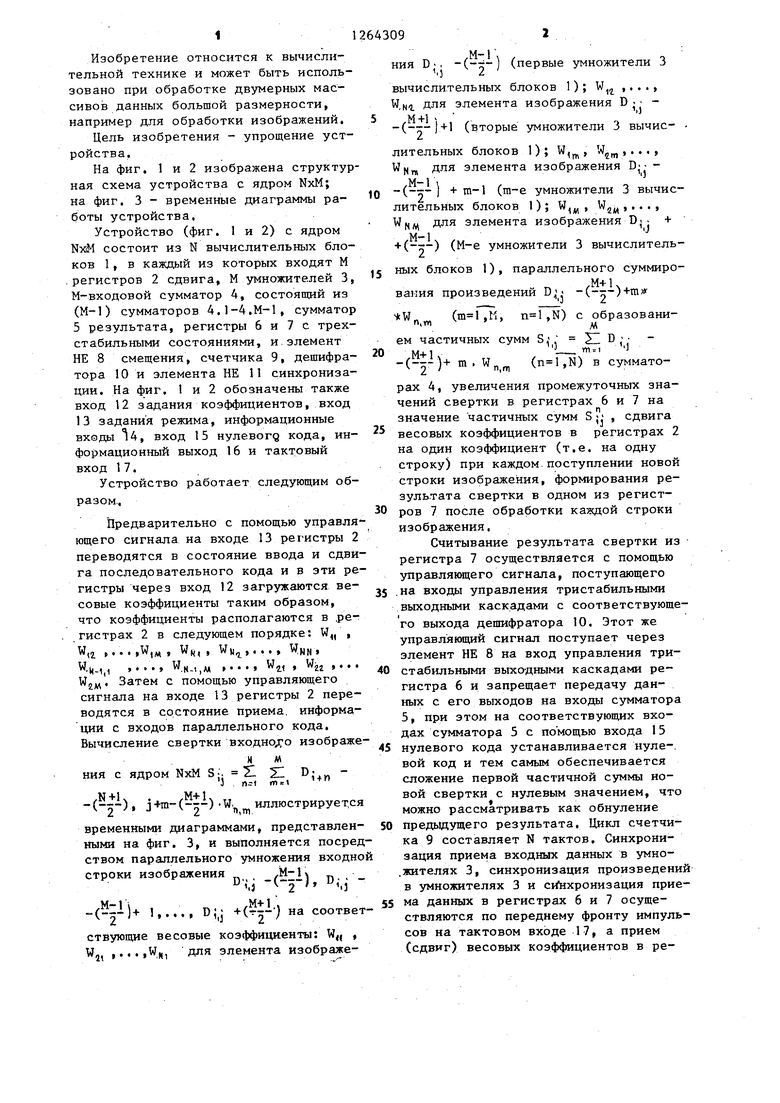

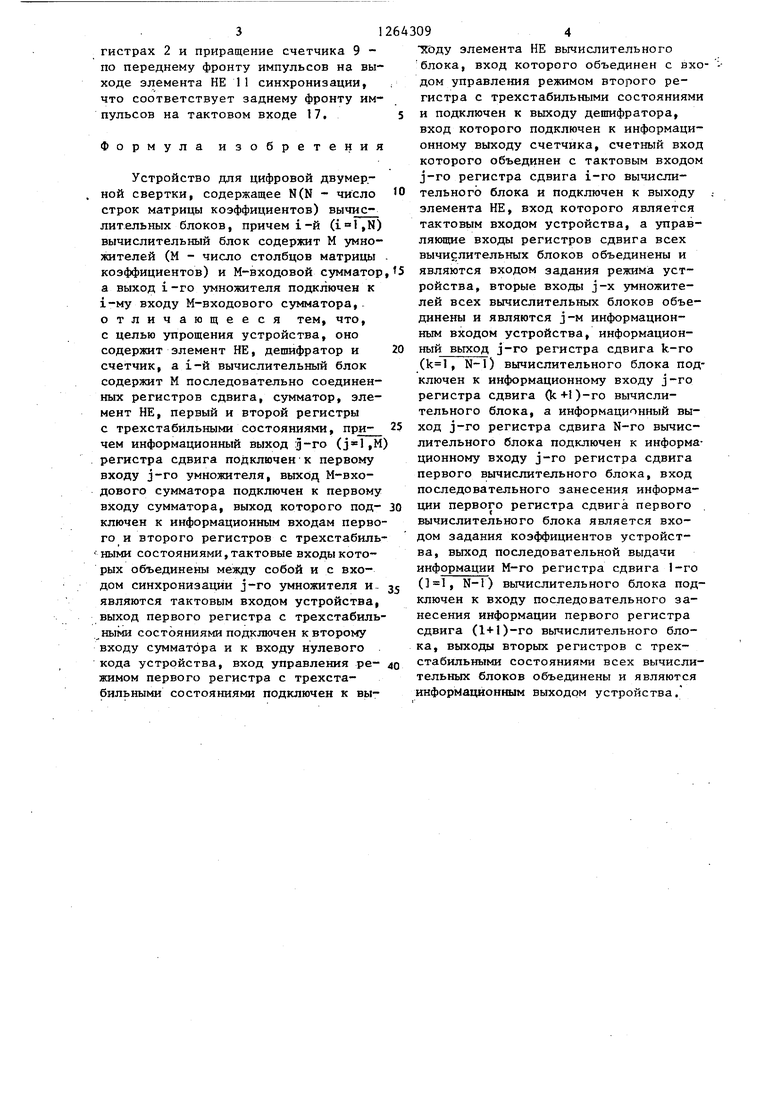

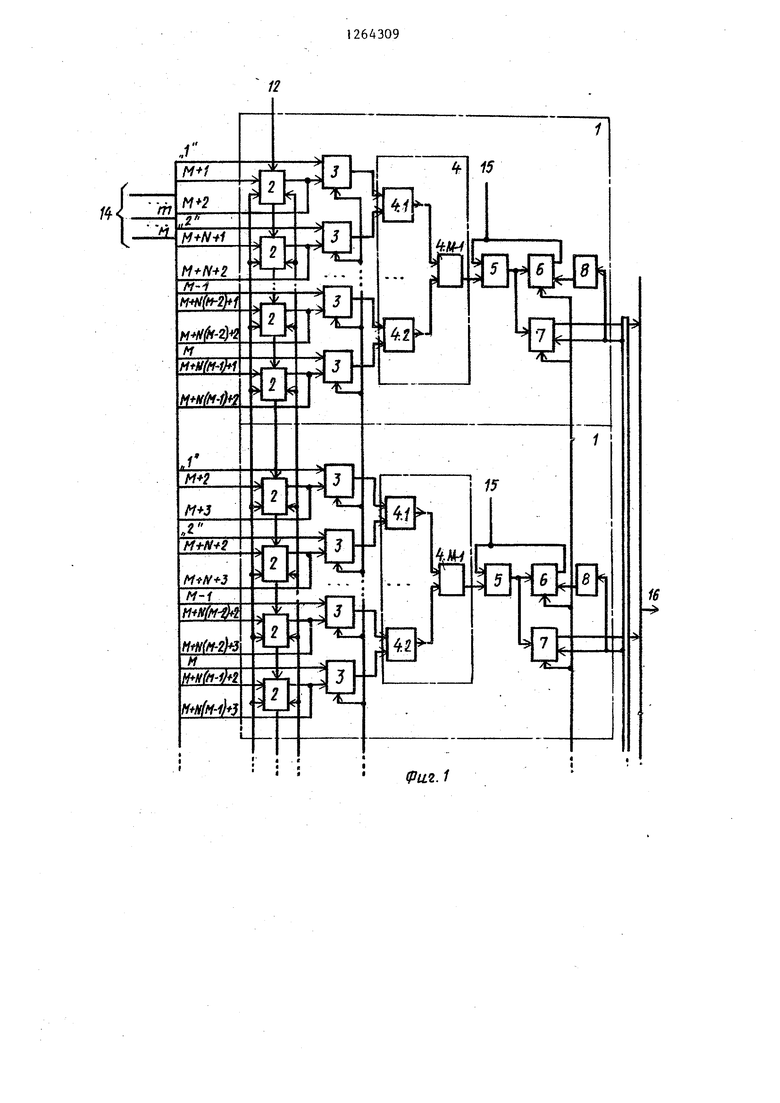

Изобретение относится к вычислительной технике и может быть использовано при обработке двумерных массивов данных большой размерности, например для обработки изображений. Цель изобретения - упрощение устройства. На фиг. 1 и 2 изображена структур ная схема устройства с ядром NxM; на фиг. 3 - временные диаграммы работы устройства. Устройство (фиг. 1 и 2) с ядром N5 состоит из N вычислительных блоков 1, в каждый из которых входят М .регистров 2 сдвига, М умножителей 3, М-входовой сумматор 4, состоящий из (М-1) сумматоров 4.1-4.М-1, сумматор 5 результата, регистры 6 и 7 с трехстабильными состояниями, и.элемент НЕ 8 смещения, счетчика 9, дешифратора 10 и элемента НЕ 11 синхронизации. На фиг. 1 и 2 обозначены также вход 12 задания коэффициентов, вход 13 3 адания режима, информационные входы 4, вход 15 нулевогд кода, информационный выход 16 и тактовый вход 17. Устройство работает следующим образом.. Предварительно с помощью управля ющего сигнала на входе 13 регистры 2 переводятся в состояние ввода и сдви га последовательного кода и в эти ре гистры через вход 12 загружаются весовые коэффициенты таким образом, что коэффициенты располагаются в .регистрах 2 в следующем порядке: W,, , ,.I,)jn , ((I J . W.N.., М гг . Затем с помощью управляющего сигнала на входе 13 регистры 2 переводятся в состояние приема, информации с входов параллельного кода. -,,, Вычисление свертки входного изображе ния с ядром NxM Sj. 51 D; j n-t i . П-I f (o) (o) W иллюстрирует.ся ,iZ n,ni. временными диаграммами, представленными на фиг. 3, и выполняется посред ством параллельного умножения входно строки изображения „ M-li iJ V 2 li М-Г 2 t««« i|j Л2 а о ТВ ствующие весовые коэффициенты: W,, , W,. ,...,W,, для элемента изображе,М-1 ,„ (o) (первые умножители 3 ч 2 вычислительных блоков 1) ; W, ,. , .N для элемента изображения D М+1 ()+1 (вторые умножители 3 вычис- ительных блоков 1); V, W . , для элемента изображения Dj (о 1 + т-1 (га-е умножители 3 вычислительных блоков 1) ; и,„ , Wjj,, t. . , f(/i для элемента изображения DJ - + М-1 +(-г-) (М-е умножители 3 вычислительных блоков 1), параллельного суммиро,М+К вамия произведении D- -C---)+m J (,K. ,N) с образованиМем частичных сумм S; D О vv ч -. m. W (,N) в суммато2 n.rti pax 4, увеличения промежуточных значений свертки в регистрах 6 и 7 на значение частичных сумм S;- , сдвига весовых коэффициентов в регистрах 2 на один коэффициент (т.е. на одну строку) при каждом.поступлении новой строки изображения, формирования результата свертки в одном из регистров 7 после обработки каждой строки изображения. Считывание результата свертки из регистра 7 осуществляется с помощью управляющего сигнала, поступающего на входы управления тристабильными выходными каскадами с соответствующего выхода дещифратора 10. Этот же управляющий сигнал поступает через элемент НЕ 8 на вход управления тристабильными выходными каскадами регистра 6 и запрещает передачу данных с его выходов на входы сумматора 5, при этом на соответствующих входах сумматора 5 с помощью входа 15 нулевого кода устанавливается нуле-. вой код и тем самым обеспечивается сложение первой частичной суммы новой свертки с нулевым значением, что можно рассматривать как обнуление предыдущего результата. Цикл счетчика 9 составляет N тактов. Синхронизация приема входных данных в умножителях 3, синхронизация произведений в умножителях 3 и синхронизация приема данных в регистрах 6 и 7 осуществляются по переднему фронту импульсов на тактовом входе 17, а прием (сдвиг) весовых коэффициентов в регистрах 2 и приращение счетчика 9 по переднему фронту импульсов на выходе элемента НЕ 11 синхронизации, что соответствует заднему фронту импульсов на тактовом входе 17.

Формула изобретения

Устройство для цифровой двумерной свертки, содержащее N(N - число строк матрицы коэффициентов) вычислительных блоков, причем i-и (,N) вычислительный блок содержит М умножителей (М - число столбцов матрицы коэффициентов) и М-входовой сумматор а выход i-го умножителя подключен к i-му входу М-входового сумматора,отличающееся тем, что, с целью упрощения устройства, оно содержит элемент НЕ, дешифратор и счетчик, а i-й вычислительный блок содержит М последовательно соединенных регистров сдвига, сумматор, элемент НЕ, первый и второй регистры с трехстабйльными состояниями, причем информационный выход :д-го (j l,M регистра сдвига подключен к первому входу j-ro умножителя, выход М-входового сумматора подключен к первому входу сумматора, выход которого подключен к информационным входам первого и второго регистров с трехстабиль ными состояниями, тактовые входы которых объединены между собой и с входом синхронизации j-ro умножителя и.. являются тактовым входом устройства, выход первого регистра с трехстабиль ными состояниями подключен к второму входу сумматора и к входу нулевого кода устройства, вход управлеьдая режимом первого регистра с трехстабйльными состояниями подключен к элемента НЕ вычислительного блока, вход которого объединен с входом управления режимом второго регистра с трехстабйльными состояниями и подключен к выходу дешифратора, вход которого подключен к информационному выходу счетчика, счетный вход которого объединен с тактовым входом j-ro регистра сдвига i-ro вычислительного блока и подключен к выходу элемента НЕ, вход которого является тактовым входом устройства, а управляющие входы регистров сдвига всех вычислительных блоков объединены и являются входом задания режима устройства, вторые входы j-x умножителей всех вычислительных блоков объединены и являются J-M информационным входом устройства, информационный выход j-ro регистра сдвига k-ro (, N-l) вычислительного блока подключен к информационному входу j-ro регистра сдвига (k+l)-ro вычислительного блока, а информационный выход j-ro регистра сдвига N-ro вычислительного блока подключен к информационному входу j-ro регистра сдвига первого вычислительного блока, вход последовательного занесения информации первого регистра сдвига первого вычислительного блока является входом задания коэффициентов устройства, выход последовательной выдачи информации М-го регистра сдвига 1-го (1, N-1) вычислительного блока подключен к входу последовательного занесения информации первого регистра сдвига (1+1)-го вычислительного блока, выхода вторых регистров с трехстабйльными состояниями всех вычислительных блоков объединены и являются информационным выходом устройства.

т

ПФиг. 1 9 9uz.Z

tpuz.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельного вычисления цифровой двумерной свертки | 1986 |

|

SU1416976A1 |

| Систолический процессор цифровой обработки сигналов | 1987 |

|

SU1471200A1 |

| Устройство для вычисления двумерной свертки | 1989 |

|

SU1619303A1 |

| Устройство для обработки видеоинформации | 1990 |

|

SU1732354A1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| Устройство для вычисления свертки | 1990 |

|

SU1709342A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1984 |

|

SU1168966A1 |

| Систолический процессор для двумерного дискретного преобразования Фурье | 1988 |

|

SU1608688A1 |

| Процессор для преобразования цифровых сигналов по Хааро-подобным базисам | 1987 |

|

SU1418745A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

Изобретение относится к вычислительной технике и может быть использовано при обработке двумерных массивов данных большой размерности, например для обработки изображений. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что устройство состоит из N вычислительных блоков, счетчика, дешифратора и элемента НЕ, причем каждый выделительный блок содержит М регистров сдвига, М умножителей, М-входовый сумматор, сумматор, элемент НЕ и два регистра с трехстабиль- СО ными состояниями с соответствующими связями. 3 ил.

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Swartzlander Е., Lilbert В., Reed I | |||

| Inner Product Computers | |||

| IEEE Fr | |||

| on Computers, 1978, vol | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1986-10-15—Публикация

1985-05-16—Подача