г-Фя

50-О fO

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на пять | 1989 |

|

SU1698984A2 |

| Преобразователь пачки импульсов в прямоугольный импульс | 1984 |

|

SU1205282A1 |

| Селектор информационных импульсов | 1985 |

|

SU1309289A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1774497A1 |

| Устройство для измерения амплитуды синусоидального напряжения | 1985 |

|

SU1272262A1 |

| Устройство для вычитания частот двух независимых сигналов | 1976 |

|

SU599227A1 |

| Устройство захвата частоты сигнала | 1977 |

|

SU680161A1 |

| Синхронный делитель частоты | 1989 |

|

SU1651374A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Преобразователь интервала времени в цифровой код | 1989 |

|

SU1746533A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения - повышение быстродействия при одновременном повышении помехоустойчивости за счет исключения внецикловых состояний - достигается путем организации новых функциональных связей. Делитель содержит триггеры 1-3, входную шину 4 и вентиль 5. 1 ил.

О 00

Изобретение относитися к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники,

Цель изобретения - повышение быстродействия при одновременном повышении помехоустойчивости за счет исключения внецикловых состояний.

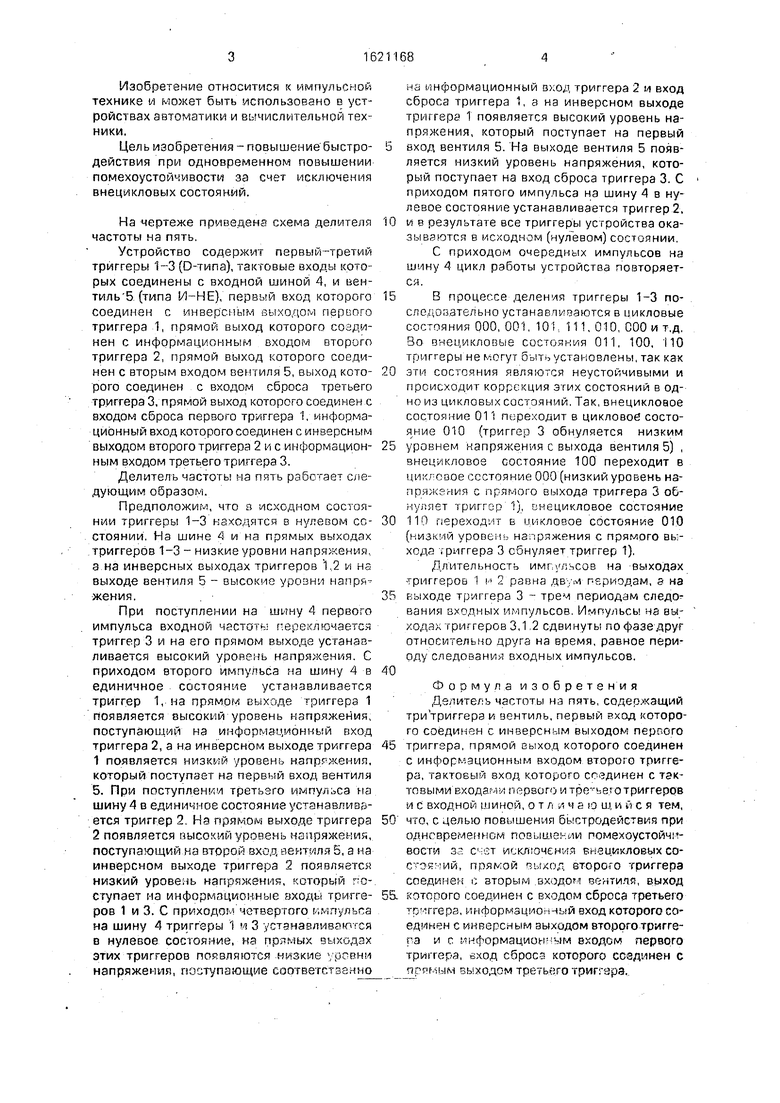

На чертеже приведена схема делителя частоты на пять.

Устройство содержит первый-третий триггеры 1-3 (D-типа), тактовые входы которых соединены с входной шиной 4, и вентиль 5 (типа И-НЕ), первый вход которого соединен с инверсным выходом первого триггера 1, прямой выход которого соэди- нен с информационным входом второго триггера 2, прямой выход которого соединен с вторым входом вентиля 5, выход которого соединен с входом сброса третьего триггера 3, прямой выход которого соединен с входом сброса первого триггера 1, информационный вход которого соединен с инверсным выходом второго триггера 2 и с информационным входом третьего триггера 3.

Делитель частоты ча пять следующим образом.

Предположим, что в исходном состоянии триггеры 1-3 находятся в нулевом состоянии. На шине 4 и на прямых выходах триггеров 1-3 - низкие уровни напряжения, а на инверсных выходах триггеров 1 2 и на выходе вентиля 5 - высокие урозни напряжения.

При поступлении на шину 4 первого импульса входной частоту переключается триггер 3 и на его прямом выходе устанавливается высокий уровень напряжения. С приходом второго импульса на шину 4 в единичное состояние устанавливается триггер 1, на прямом выходе триггера 1 появляется высокий уровень напряжения, поступающий на информационный вход триггера 2, а на инверсном выходе триггера

1появляется низкий /ровень напряжения, который поступает на первый вход вентиля 5. При поступлении третьего импульса на шину 4 в единичное состояние устанавливается триггер 2 Нз прямом выходе триггера

2появляется высокий уровень напряжения, поступающий на второй вход аентмля 5, а на инверсном выходе триггера 2 появляется низкий уровень напряжения, который с- сгупает на информационные входы триггеров 1 и 3. С приходом четвертого -.млульса на шину 4 триггеры 1 ч 3 устанавливайся в нулевое состояние, на прямых выходах этих триггеров появляются низкие 5 осени напряжений, поступающие соответственно

не; информационный вход триггера 2 и вход сброса триггера 1, а на инверсном выходе триггера 1 появляется высокий уровень напряжения, который поступает на первый

вход вентиля 5. На выходе вентиля 5 появляется низкий уровень напряжения, который поступает на вход сброса триггера 3. С приходом пятого импупьса на шину 4 в нулевое состояние устанавливается триггер 2,

0 ив результате все триггеры устройства оказываются в исходном (нулевом) состоянии. С приходом очередных импульсов на шину 4 цикл работы устройства повторяется.

5В процессе деления триггеры 1-3 последовательно устанавливаются в цикловые состояния 000, 001, 101 111, 010, СОО и т.д. Во внецикловые состояния 011, 100, МО триггеры не могут б вп-з установлены, так как

0 эти состояния являются неустойчивыми и происходит коррекция этих состояний в одно из цикловых состояний. Так, внецикловое состояние 011 переходит в цикловоб состояние 010 (триггер 3 обнуляется низким

5 уровнем напряжения с выхода вентиля 5) , внецикловое состояние 100 переходит в цик/твоесостояние 000 (низкий уровень напряжения с прямого выхода триггера 3 обнуляет триггер 1), пнецикловое состояние

0 110 переходит ь ипкловое состояние 010 (низкий ypODti напряжения с прямого вь- хода .риггерэ 3 обнуляет триггер 1).

Длительность имг ,-,сов на выходах триггеров 1 2 равна дв м периодам, s на

5 Е-ыходе триггера 3 - трем периодам следования входных импульсов Импульсы из выходах гритеров 3,1 2 сдвинуты по фазе друг относительно друга на время, равное периоду следования входных импульсов.

0

Фоомула изобретения Делитель частоты на пять, содержащий три триггерэ и вентиль, первый РХОД которого соединен с инверсным выходом перг.ого

5 триггера, прямой вь-ход которого соединен с инфорг . эционным входом второю триггера, тактовый вход которого сгздинен с тактовыми входами пррвого и третьего триггеров и с входной шиной, отлича ю ш и и с я тем,

0 ч го, с целью повышения быстродействия при одновременном повышении помехоустойчивости з с1 ст исключения Внеимклоеых со- , прямой илог, второго триггера соединен i; вторым входом вентиля, выход

| Синхронный делитель частоты сле-дОВАНия иМпульСОВ HA 5 | 1979 |

|

SU797079A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синхронный делитель частоты на пять | 1987 |

|

SU1547056A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Справочник по интегральным микросхемам | |||

| Под ред | |||

| Б.В.Тарабрина | |||

| М.: Энергия, 1980.С.722, рис.5-222. | |||

Авторы

Даты

1991-01-15—Публикация

1988-11-09—Подача