УСТРОЙСТВО для ВЬгаиТАНИЯ ЧАСТОТ ДВУХ

(54) НЕЗАВИСИМЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты импульсов | 1977 |

|

SU698130A2 |

| Синтезатор частот | 1976 |

|

SU799101A1 |

| Устройство генерации импульсов управления шаговым двигателем с электронной коррекцией | 1991 |

|

SU1829022A1 |

| Счетчик импульсов | 1977 |

|

SU784003A1 |

| Частотный компаратор | 1983 |

|

SU1167719A2 |

| Сигнализатор загрузки двигателя | 1990 |

|

SU1795316A1 |

| Частотный компаратор | 1982 |

|

SU1045376A1 |

| Преобразователь интервала времени в цифровой код | 1989 |

|

SU1746533A1 |

| Цифровой фазо-частотный детектор | 1984 |

|

SU1176447A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2250558C1 |

Изобретение относится к импульсной технике.

Известно устройство для вычитания частот, содержащее бистабильный элемент, который за счет использования логических вентилей совпадения модулирует входную информацию упорядоченно во времени. Запоминающая бистабильная схема в сочетании с другими вентилями совпадения определяет, какой из вход,ных сигналов имеет большую частоту, а также разность частот этих сигналов l .

Недостаток схемы - использование принципа частотного компаратора, который даёт большую погрешность.

Наиболее близкое к предлагаемому изобретению устройство для вычитания частот содержит два Зк-триггера, первый вход одного из соторых соединен с выходом первого трехвходового логического элемента И, первый вход i oторого соединен с шиной сигнала первой частоты, второй вход соединен с первым входом первого смесителя, а третий вход подключен к выходу упомянутого tJK-триггвра и первому входу второго смесителя, второй вход которого подключен к выходу второго ЗКтриггера и третьему входу второго

трехвходового логического элемента И, второй вход которого соединен со вторым входом первого смесителя, третий ВХОДвторого трехвходового логического элемента И соединен с шиной сигнала второй частоты, а его выход подключен к первому входу второго ЗКтриггера, причем.вторые входы ЭКтриггеров соединены с шинами инверснь сигналов первой и второй частоты, а выходы смесителей через резисторы подключены к выходу устройства 2j.

Однако такое устройство не обладает достаточной помехоустойчивостью.

Цель изобретения - повьаиение помехоустойчивости .

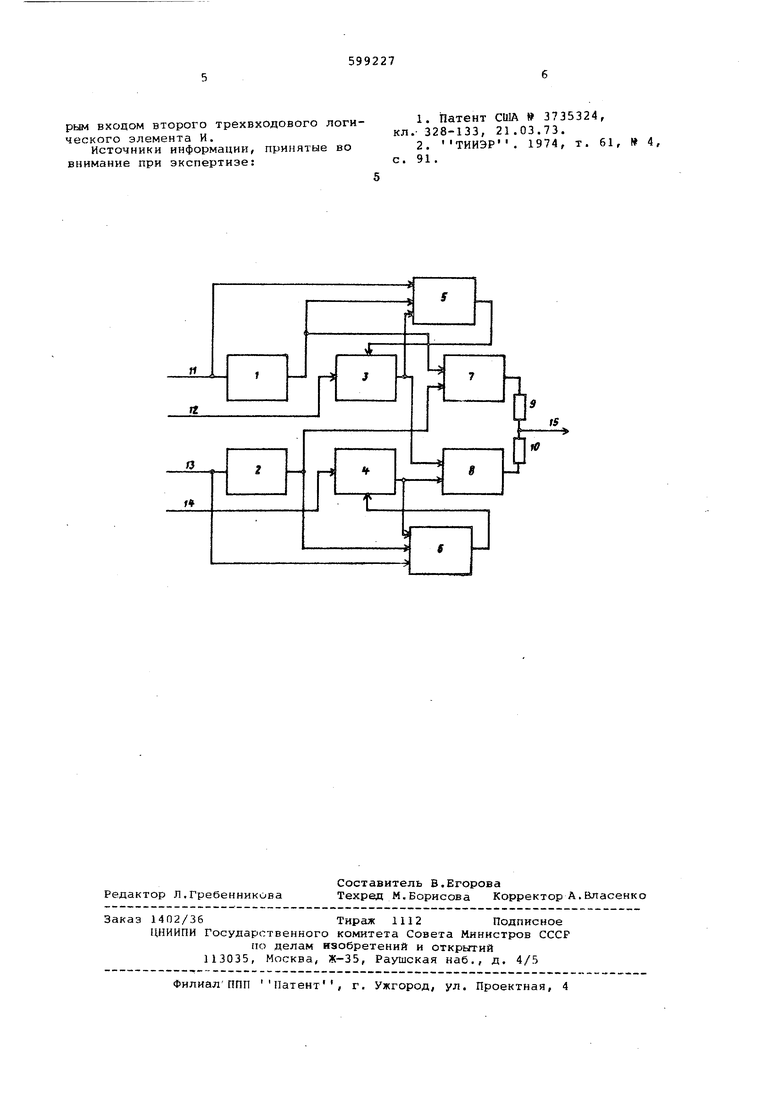

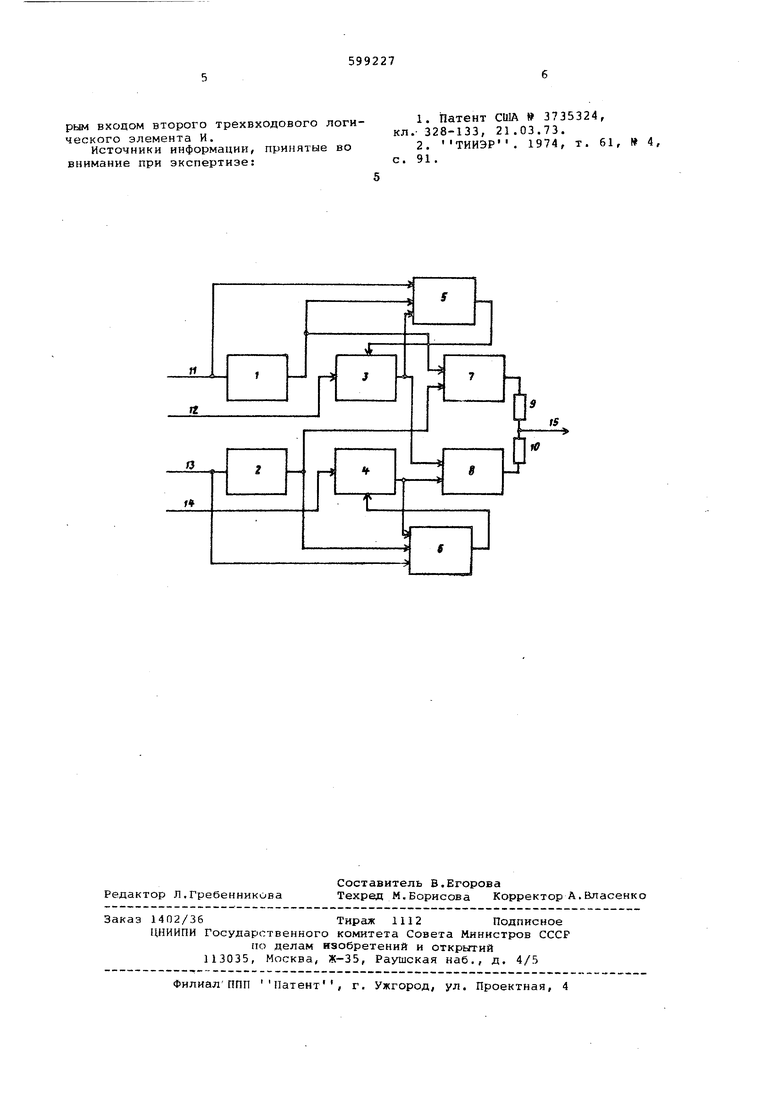

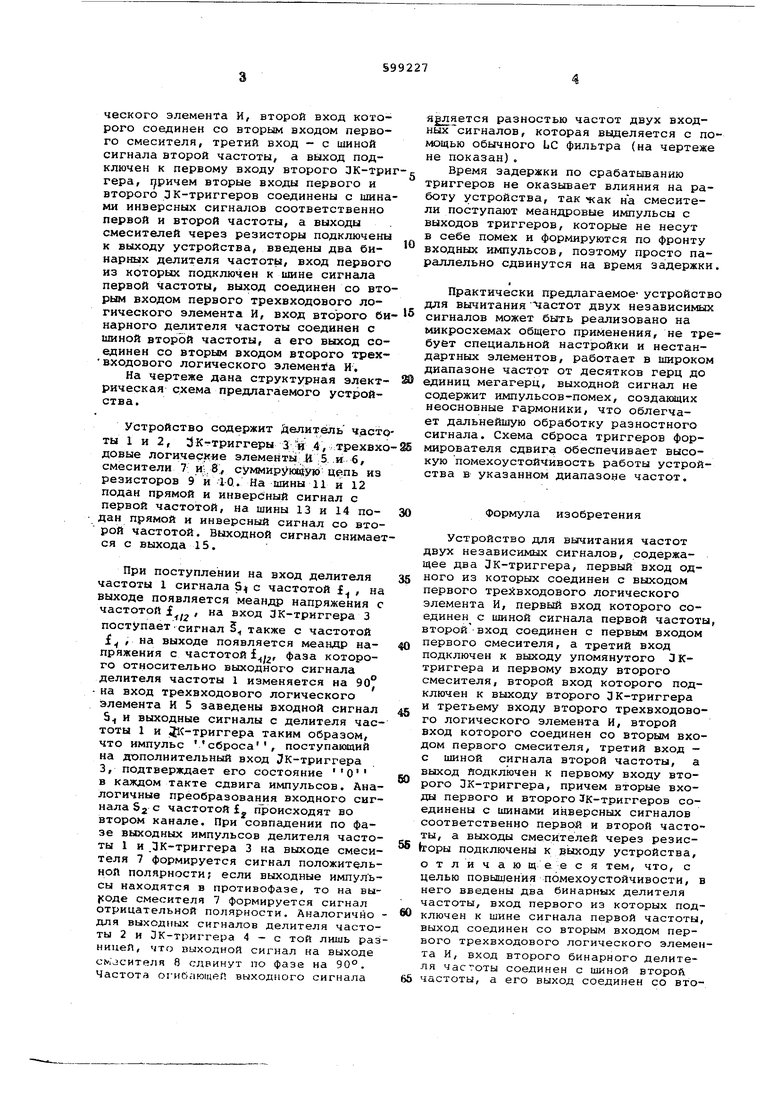

Это достигается тем, что в устройство для вычитания частот, содержащее два Зк-триггера, первый вход одного из которых соединен с выходом первого трехвходового логического элемента И, первый вход которого соединен с шиной сигнала первой частоты, второй вход соединен с первым входом первого смесителя, а третий вход подключен к выходу упомянутого Зк-тригЬера и первому входу второго смесителя, второй вход которого подключен к выходу второго ЗК-триггера и третьему входу второго трехвходового логического элемента И, второй вход которого соединен со вторым входом первого смесителя, третий вход - с шиной сигнала второй частоты, а выход подключен к первому входу второго ЗК-три гера, 1 ричем вторые входы первого и второго ЗК-триггеров соединены с шина ми инверсных сигналов соответственно первой и второй частоты, а выходы смесителей через резисторы подключены к выходу устройства, введены два бинарных делителя частоты, вход первого из которых подключен к шине сигнала первой частоты, выход соединен со вто рым входом первого трехвходового логического элемента И, вход второго би нарного делителя частоты соединен с шиной второй частоты, а его выход соединен со вторым входом второго трехвходового логического элемента И. На чертеже дана структурная электрическая схема предлагаемого устройства. Устройство содержит Делитель часто ты 1 и 2, ЗКг-триггеры 3и 4, трехвхо довые логические элементы .И 5. .и 6, смесители 7 и-. 8,, суммируюадую Цепь из резисторов 9 и 10. На шины 11 и 12 подан прямой и инверсный сигнал с первой частотой, на шины 13 и 14 подан прямой и инверсный сигнал со второй частотой. Выходной сигнал снимает ся с выхода 15. При поступлении на вход делителя частоты 1 сигнала 5 с частотой J. , на выходе появляется меандр напряжения с частотой f , на вход ЗК-триггера 3 поступает сигнал 5 также с частотой f , на выходе появляется меандр напряжения с частотой i.12 Фаза которого относительно выходного сигнала делителя частоты 1 изменяется на 90° на вход трехвходового логического элемента И 5 заведены входной сигнал 5 и выходные сигналы с делителя частоты 1 и ijK-триггера таким образом, что импульс сброса, поступгиощий на дополнительный вход jK-триггера 3, подтверждает его состояние О в каждом такте сдвига импульсов. Аналогичные преобразования входного сигнала Sj с частотой ig п роисходят во втором канале. При совпадении по фазе выходных импульсов делителя частоты 1 и .ЗК-триггера 3 на выходе смесителя 7 формируется сигнал положительной полярности; если выходные импульсы находятся в противофазе, то на вы смесителя 7 формируется сигнал отрицательной полярности. Аналогично для выходных сигналов делителя частоты 2 и ЗК-триггера 4 - с той лишь раз ницеП, что выходной сигнал на выходе cN-ijcHTe/iR 8 сдвинут по фазе на 90°. Частота огиб;1ющеП выходного сигнала является разностью частот двух входых сигналов, которая выделяется с поощью обычного LC фильтра (на чертеже е показан). Время задержки по срабатыванию риггеров не оказывает влияния на раоту устройства, так как на смеситеи поступают меандровые импульсы с ыходов триггеров, которые не несут себе помех и формируются по фронту ходных импульсов, поэтому просто пааллельно сдвинутся на время задержки. Практически предлагаемое- устройство для вычитания Частот двух независимых сигналов может быть реализовано на микросхемах общего применения, не требует специальной настройки и нестандартных элементов, работает в широком диапазоне частот от десятков герц до единиц мегагерц, выходной сигнал не содержит импульсов-помех, создающих неосновные гармоники, что облегчает дальнейшую обработку разностного сигнала. Схема сброса триггеров формиррвателя сдвига обеспечивает высокую помехоустойчивость работы устройства в указанном диапазоне частот. Формула изобретения Устройство для вычитания частот двух независимых сигналов, содержащее два ЛК-триггера, первый вход одного из которых соединен с выходом первого трехвходового логического элемента И, первый вход которого соединен с шиной сигнала первой частоты, второй вход соединен с первым входом первого смесителя, а третий вход подключен к выходу упомянутого Л Ктриггера и первому входу второго смесителя, второй вход которого подключен к выходу второго 3 К-триггера и третьему входу второго трехвходового логического элемента И, второй вход которого соединен со вторым входом первого смесителя, третий вход - с шиной сигнала второй частоты, а выход подключен к первому входу второго ЗК-триггера, причем вторые входы первого и второго ЗК-триггеров соединены с шинами инверсных сигналов соответственно первой и второй частоты, а выходы смесителей через резисЬоры подключены к выходу устройства, отличаю щ е е с я тем, что, с целью повышения помехоустойчивости, в него введены два бинарных делителя частоты, вход первого из которых подключен к шине сигнала первой частоты, выход соединен со вторым входом первого трехвходового логического элемента И, вход второго бинарного делителя частоты соединен с шиной второй частоты, а его выход соединен со вторым входом второго трехвходового логического элемента И.

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1978-03-25—Публикация

1976-10-04—Подача