Изобретение относится к вычислительной технике и может быть использовано в технических средствах отображения графической информации на телевизионном индикаторе, в частности в растровом графическом дисплее.

Целью изобретения является повышение быстродействия устройства.

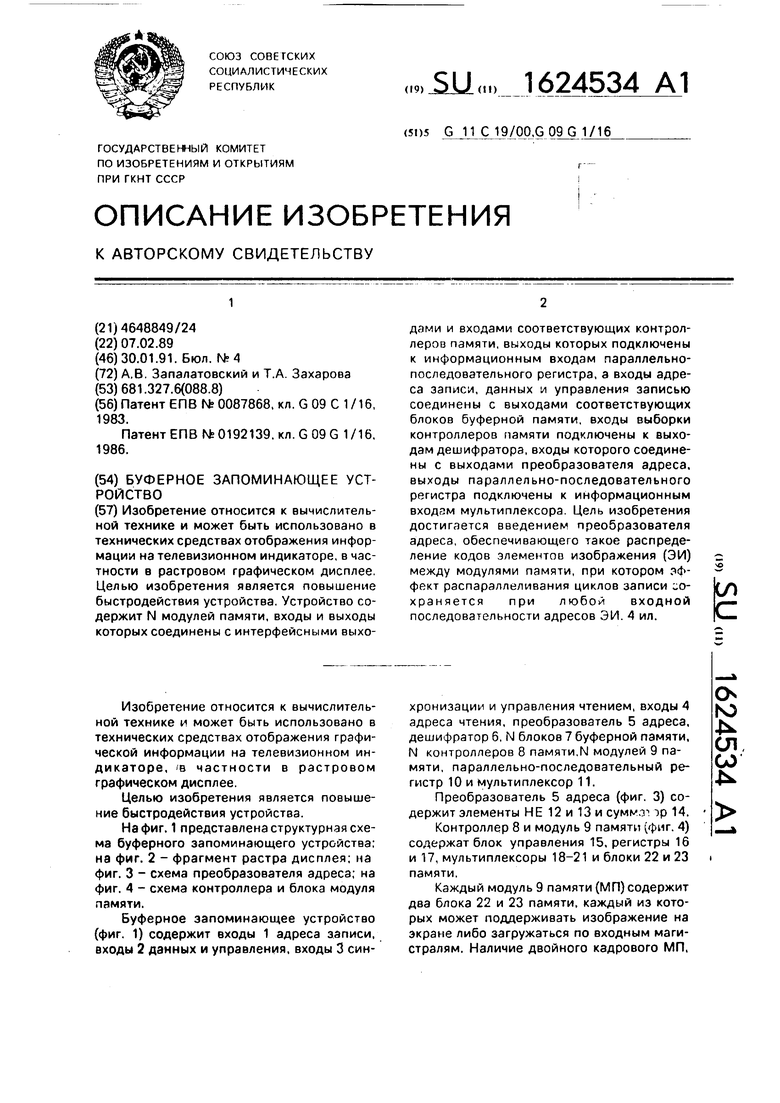

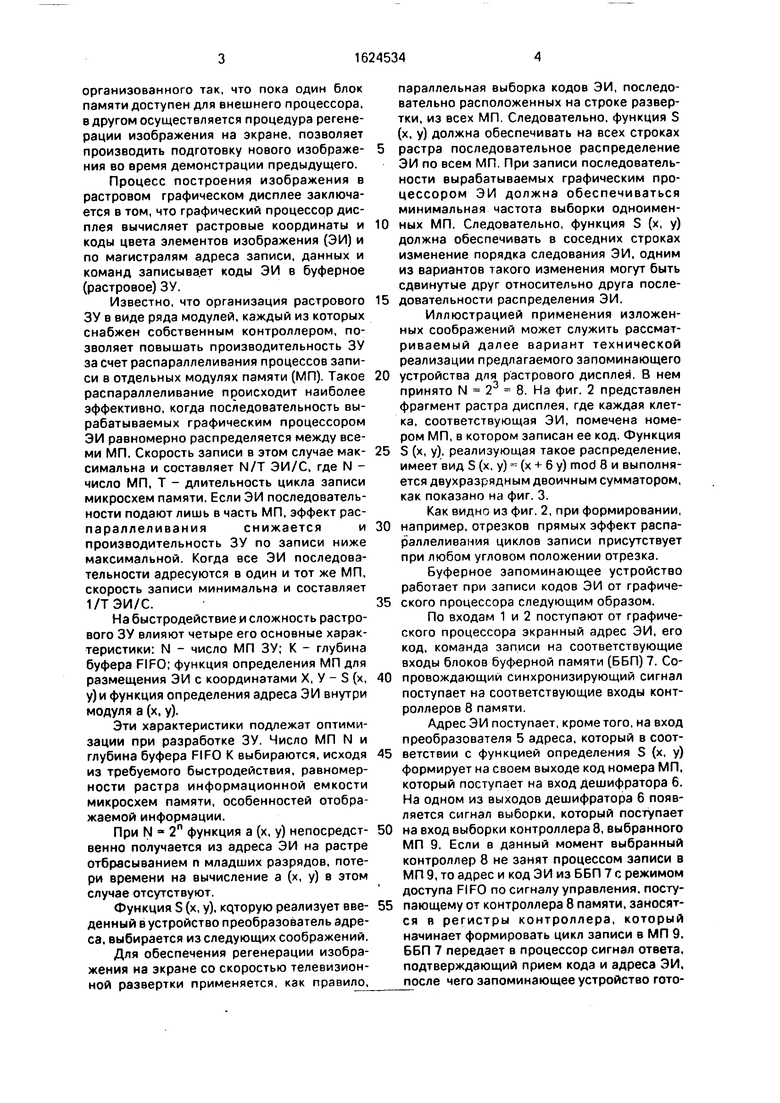

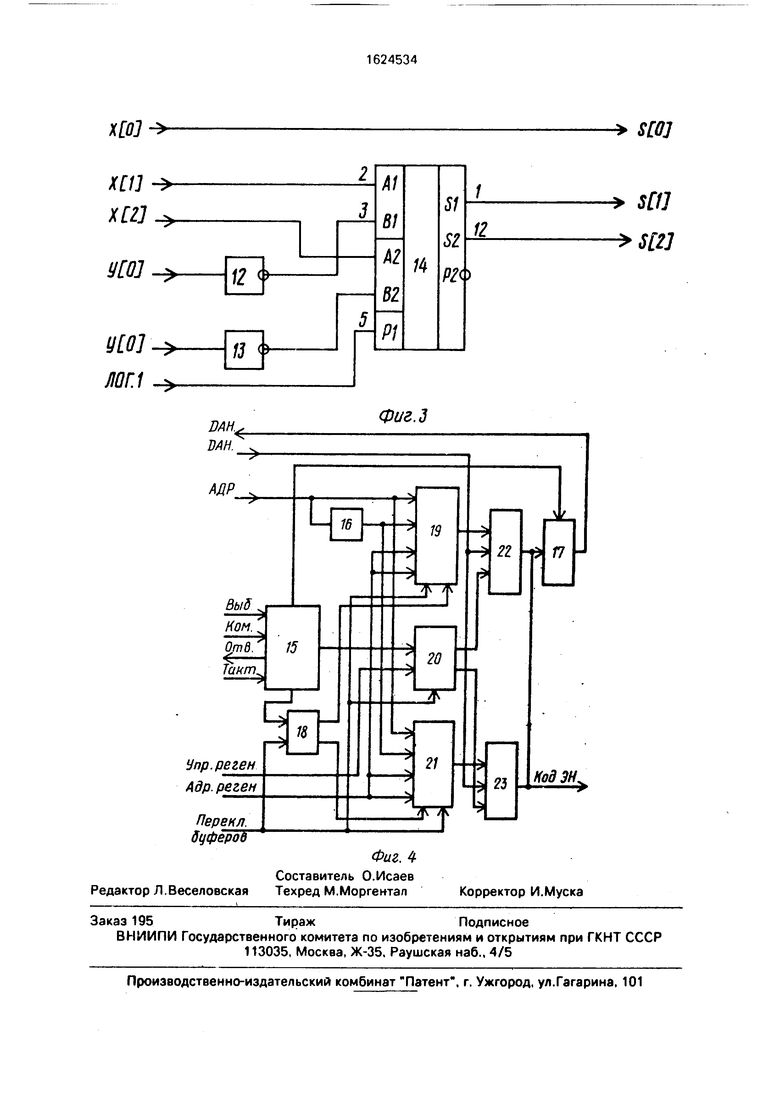

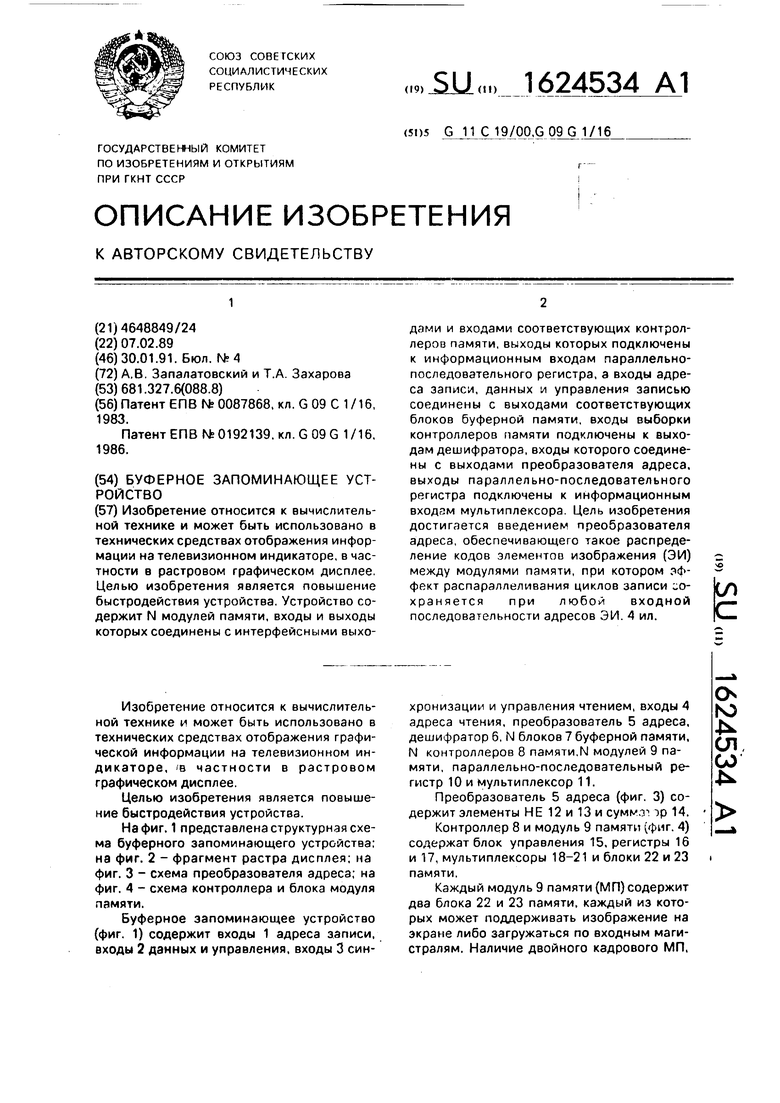

На фиг. 1 представлена структурная схема буферного запоминающего устройства; на фиг. 2 - фрагмент растра дисплея; на фиг. 3 - схема преобразователя адреса; на фиг. 4 - схема контроллера и блока модуля памяти.

Буферное запоминающее устройство (фиг. 1) содержит входы 1 адреса записи, входы 2 данных и управления, входы 3 синхронизации и управления чтением, входы 4 адреса чтения, преобразователь 5 адреса, дешифратор 6, N блоков 7 буферной памяти, N контроллеров 8 памяти.N модулей 9 памяти, параллельно-последовательный регистр 10 и мультиплексор 11.

Преобразователь 5 адреса (фиг. 3) содержит элементы НЕ 12 и 13 и сумма1 эр 14.

Контроллер 8 и модуль 9 памяти (фиг. 4) содержат блок управления 15, регистры 16 и 17, мультиплексоры 18-21 и блоки 22 и 23 памяти.

Каждый модуль 9 памяти (МП) содержит два блока 22 и 23 памяти, каждый из которых может поддерживать изображение на экране либо загружаться по входным магистралям. Наличие двойного кадрового МП,

О

ю ел со

организованного так, что пока один блок памяти доступен для внешнего процессора, в другом осуществляется процедура регенерации изображения на экране, позволяет производить подготовку нового изображения во время демонстрации предыдущего.

Процесс построения изображения в растровом графическом дисплее заключается в том, что графический процессор дисплея вычисляет растровые координаты и коды цвета элементов изображения (ЭЙ) и по магистралям адреса записи, данных и команд записыва.ет коды ЭЙ в буферное (растровое) ЗУ.

Известно, что организация растрового ЗУ в виде ряда модулей, каждый из которых снабжен собственным контроллером, позволяет повышать производительность ЗУ за счет распараллеливания процессов записи в отдельных модулях памяти (МП). Такое распараллеливание происходит наиболее эффективно, когда последовательность вырабатываемых графическим процессором ЭЙ равномерно распределяется между всеми МП. Скорость записи в этом случае максимальна и составляет N/T ЭИ/С, где N - число МП, Т - длительность цикла записи микросхем памяти. Если ЭЙ последовательности подают лишь в часть МП, эффект распараллеливанияснижаетсяипроизводительность ЗУ по записи ниже максимальной. Когда все ЭЙ последовательности адресуются в один и тот же МП, скорость записи минимальна и составляет 1/Т ЭИ/С.

На быстродействие и сложность растрового ЗУ влияют четыре его основные характеристики: N - число МП ЗУ; К - глубина буфера FIFO; функция определения МП для размещения ЭЙ с координатами X, У - S (х, у) и функция определения адреса ЭЙ внутри модуля а (х, у).

Эти характеристики подлежат оптимизации при разработке ЗУ. Число МП N и глубина буфера FIFO К выбираются, исходя из требуемого быстродействия, равномерности растра информационной емкости микросхем памяти, особенностей отображаемой информации.

При N 2 функция а (х, у) непосредственно получается из адреса ЭЙ на растре отбрасыванием п младших разрядов, потери времени на вычисление а (х, у) в этом случае отсутствуют.

Функция S (х, у), кодорую реализует введенный в устройство преобразователь адреса, выбирается из следующих соображений.

Для обеспечения регенерации изображения на экране со скоростью телевизионной развертки применяется, как правило.

параллельная выборка кодов ЭЙ, последовательно расположенных на строке развертки, из всех МП. Следовательно, функция S (х. у) должна обеспечивать на всех строках

растра последовательное распределение ЭЙ по всем МП. При записи последовательности вырабатываемых графическим процессором ЭЙ должна обеспечиваться минимальная частота выборки одноимен0 ных МП. Следовательно, функция S (х, у) должна обеспечивать в соседних строках изменение порядка следования ЭЙ, одним из вариантов такого изменения могут быть сдвинутые друг относительно друга после5 довательности распределения ЭЙ.

Иллюстрацией применения изложенных соображений может служить рассматриваемый далее вариант технической реализации предлагаемого запоминающего

0 устройства для растрового дисплей. В нем принято N 23 8. На фиг. 2 представлен фрагмент растра дисплея, где каждая клетка, соответствующая ЭЙ, помечена номером МП, в котором записан ее код. Функция

5 S (х, у), реализующая такое распределение, имеет вид S (х, у) (х + 6 у) mod 8 и выполняется двухразрядным двоичным сумматором, как показано на фиг. 3.

Как видно из фиг. 2, при формировании,

0 например, отрезков прямых эффект распараллеливания циклов записи присутствует при любом угловом положении отрезка.

Буферное запоминающее устройство работает при записи кодов ЭЙ от графиче5 ского процессора следующим образом.

По входам 1 и 2 поступают от графического процессора экранный адрес ЭЙ, его код, команда записи на соответствующие входы блоков буферной памяти (ББП) 7. Со0 провождающии синхронизирующий сигнал поступает на соответствующие входы контроллеров 8 памяти.

Адрес ЭЙ поступает, кроме того, на вход преобразователя 5 адреса, который в соот5 ветствии с функцией определения S (х, у) формирует на своем выходе код номера МП, который поступает на вход дешифратора 6. На одном из выходов дешифратора 6 появляется сигнал выборки, который поступает

0 на вход выборки контроллера 8, выбранного МП 9. Если в данный момент выбранный контроллер 8 не занят процессом записи в МП 9, то адрес и код ЭЙ из ББП 7 с режимом доступа FIFO по сигналу управления, посту5 пающему от контроллера 8 памяти, заносятся в регистры контроллера, который начинает формировать цикл записи в МП 9. ББП 7 передает в процессор сигнал ответа, подтверждающий прием кода и адреса ЭЙ. после чего запоминающее устройство готово к приему следующего ЭЙ. Если в момент прихода сигнала выборки выбираемый контроллер памяти занят процессором записи в МП 9, то адрес и код ЭЙ записываются в соответствующий ББП 7, который выдает сигнал, подтверждающий прием данных.

В случае, если ББП 7 заполнен полностью, выдача сигнала, подтверждающего прием кода и адреса ЭЙ, задерживается до завершения текущего цикла записи МП 9, после чего в контроллер 8 передаются очередные адрес и код ЭЙ из ББП 7. По окончании этой процедуры ББП 7 может осуществить прием новых адреса и кода ЭЙ по входам 1 и 2 и выдать сигнал, подтверждающий прием адреса и кода ЭЙ.

Запоминающее устройство работает при чтении информации на экран следующим образом.

По входам 4 на вход адреса чтения контроллеров 8 памяти от синхронизатора дисплея поступает адрес чтения данных на экран. По входам 3 на входы контроллеров 8 памяти поступают сигналы синхронизации и управления чтением, под действием которых из всех МП параллельно считываются коды ЭЙ. Считанные коды параллельно заносятся в регистр 10 и затем подвергаются в нем циклическому сдвигу. При этом на выходах разрядов регистра 10, подключенных к входам мультиплексора 11. формируются сдвинутые по фазе последовательности кодов ЭЙ. Мультиплексор 11, управляемый младшими разрядами вертикальной составляющей адреса ЭЙ на экране, передает на выход устройства ту из последовательностей кодов ЭЙ, в которой на данной строке растра скомпенсирован сдвиг, внесенный при записи в МП 9 преобразователем 5 адреса. Таким образом, на

экране ЭЙ отображаются без сдвигов в полном соответствии с их экранными адресами. Формула изобретения Буферное запоминающее устройство,

содержащее N блоков буферной памяти, N модулей памяти, N контроллеров памяти, информационные выходы и входы которых соединены с входами и выходами соответствующих модулей памяти, входы адреса записи, данных и управления записью подключены к выходам соответствующих блоков буферной памяти, информационные входы которых являются входами адреса записи, данных и управления записью устройства, входы синхронизации и управления чтением контроллеров памяти являются одноименными входами устройства и соединены с управляющими входами параллельно-последовательного регистра,

информационные входы которого подключены к информационным выходам контроллеров памяти, входы выборки которых соединены с соответствующими выходами дешифратора, а выходы ответа подключены

к управляющим входам соответствующих блоков буферной памяти, выходы ответа которых являются одноименным выходом устройства, отличающееся тем, что. с целью повышения быстродействия, в устройство введены преобразователь адреса и мультиплексор, причем входы и выходы преобразователя адреса подключены соответственно к входам адреса записи устройства и к входам дешифратора, выходы параллельно-последовательного регистра соединены с информационными входами мультиплексора, выходы которого являются выходами устройства, а управляющие входы подключены к входам адреса чтения контроллеров памяти и являются входами адреса чтения устройства.

1 Мф

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1989 |

|

SU1626262A1 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| Устройство экранной памяти | 1988 |

|

SU1566372A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОГО ПРИЕМА СИГНАЛОВ РАЗЛИЧНЫХ СИСТЕМ СПУТНИКОВОЙ НАВИГАЦИИ | 2015 |

|

RU2611069C1 |

| Устройство для отображения многоугольников на экране растрового графического видеоконтрольного блока | 1987 |

|

SU1534454A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для вывода графической информации | 1990 |

|

SU1833858A1 |

| Генератор изображений | 1988 |

|

SU1522240A1 |

| УСТРОЙСТВО ОБРАБОТКИ ДВУХМЕРНЫХ И ТРЕХМЕРНЫХ ИЗОБРАЖЕНИЙ | 2005 |

|

RU2289161C1 |

Изобретение относится к вычислительной технике и может быть использовано в технических средствах отображения информации на телевизионном индикаторе, в частности в растровом графическом дисплее. Целью изобретения является повышение быстродействия устройства. Устройство содержит N модулей памяти, входы и выходы которых соединены с интерфейсными выходами и входами соответствующих контроллеров памяти, выходы которых подключены к информационным входам параллельно- последовательного регистра, а входы адреса записи, данных и управления записью соединены с выходами соответствующих блоков буферной памяти, входы выборки контроллеров памяти подключены к выходам дешифратора, входы которого соединены с выходами преобразователя адреса, выходы параллельно-последовательного регистра подключены к информационным входам мультиплексора. Цель изобретения достигается введением преобразователя адреса, обеспечивающего такое распределение кодов элементов изображения (ЭЙ) между модулями памяти, при котором эффект распараллеливания циклов записи сохраняется при любой входной последовательности адресов ЭЙ. 4 ил.

frESfr291

xf07-

-

Фиг.З

| 0 |

|

SU87868A1 | |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| ПЫЛЕУЛОВИТЕЛЬ | 0 |

|

SU192139A1 |

| кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1991-01-30—Публикация

1989-02-07—Подача