Изобретение относится к области машинной растровой графики и может быть использовано для заполнения многоугольников, отображаемых на ЭЛТ устройства визуального вывода.

Целью изобретения является повышение быстродействия.устройства за счет увеличения скорости определения границ многоугольников.

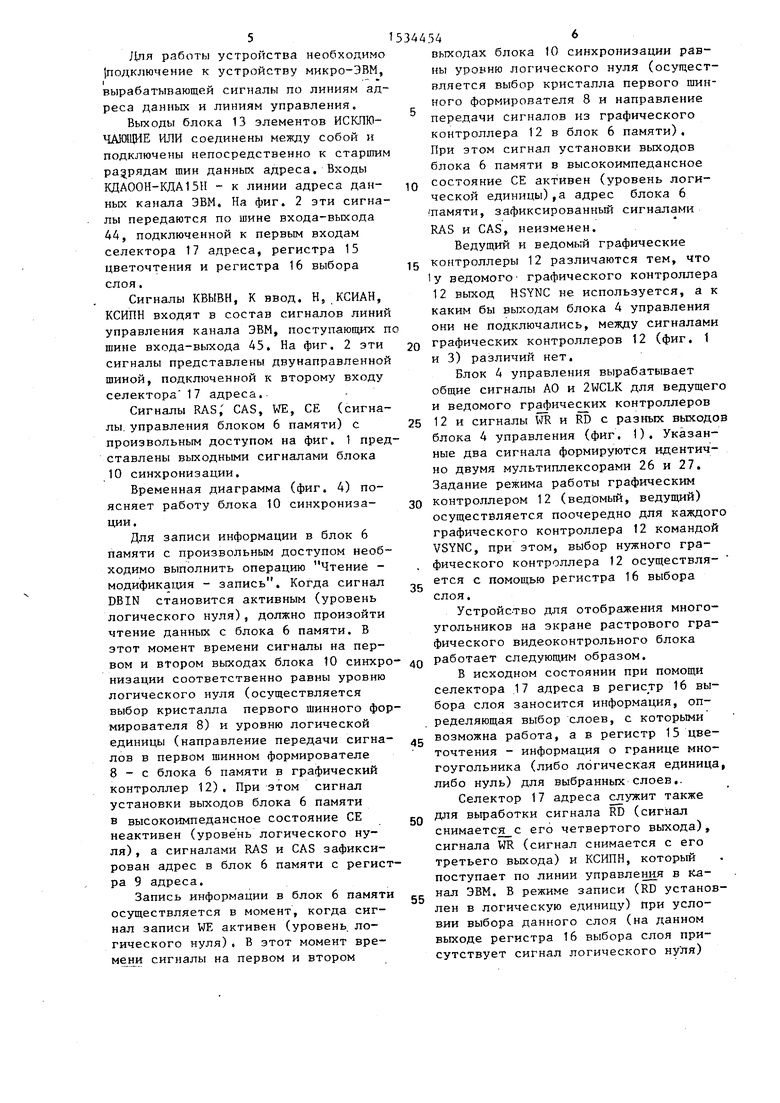

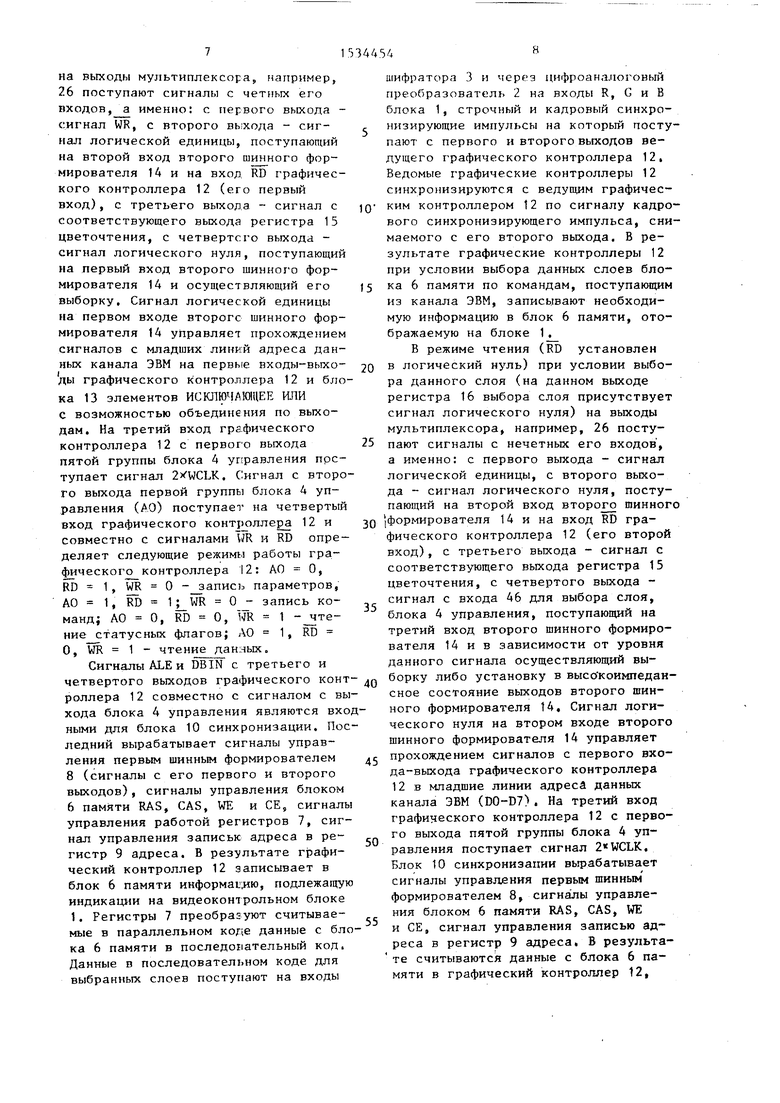

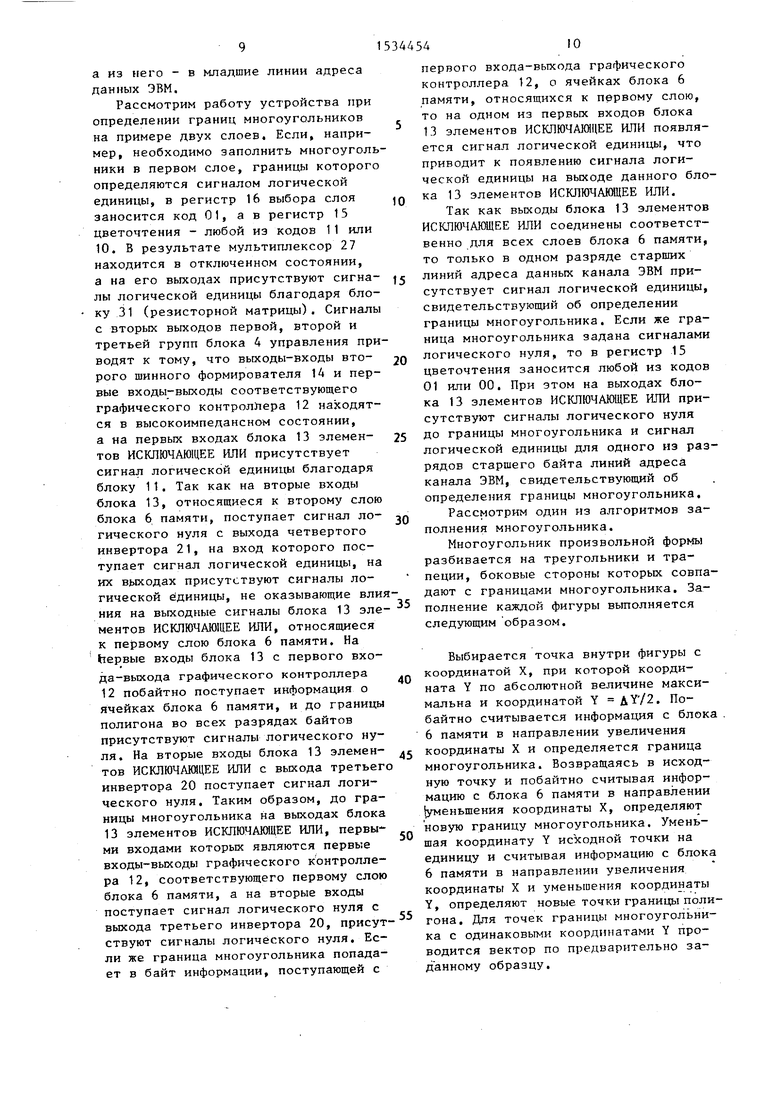

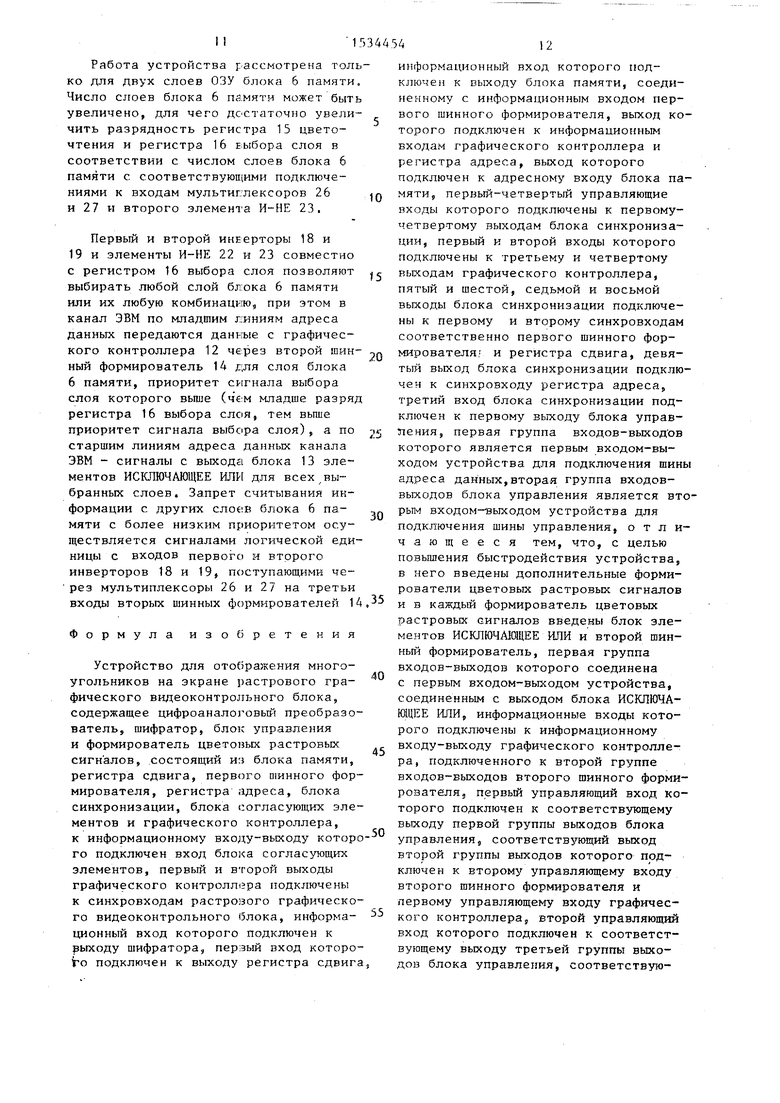

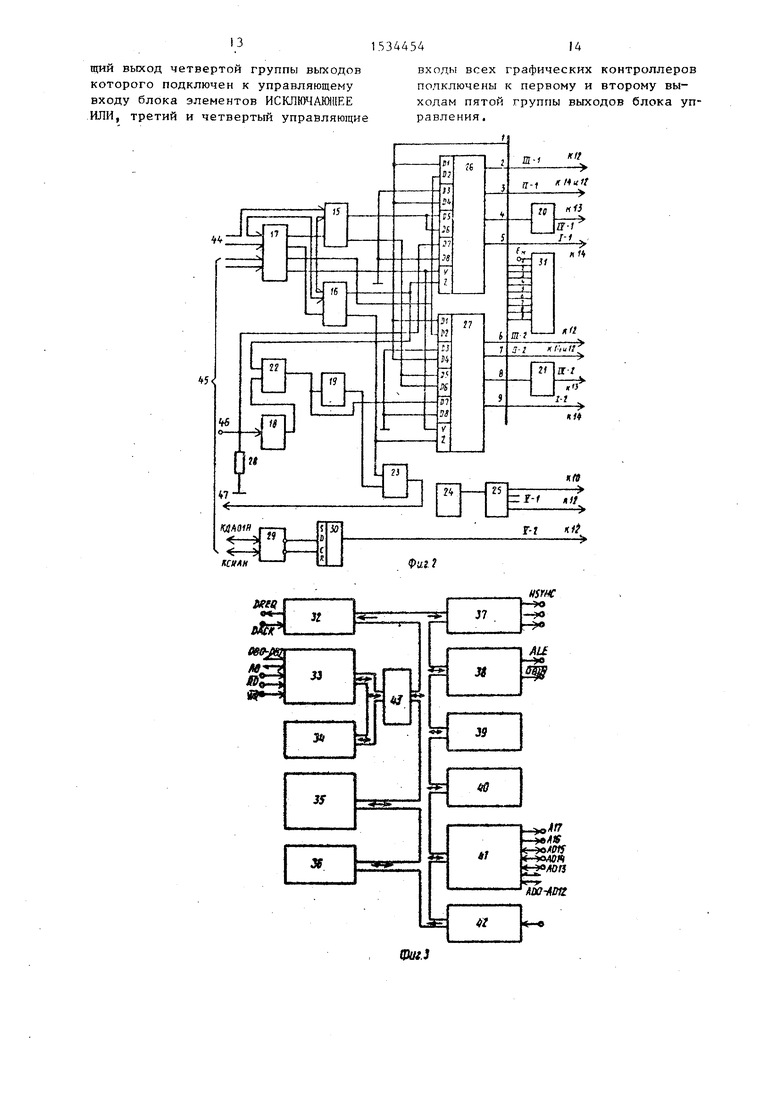

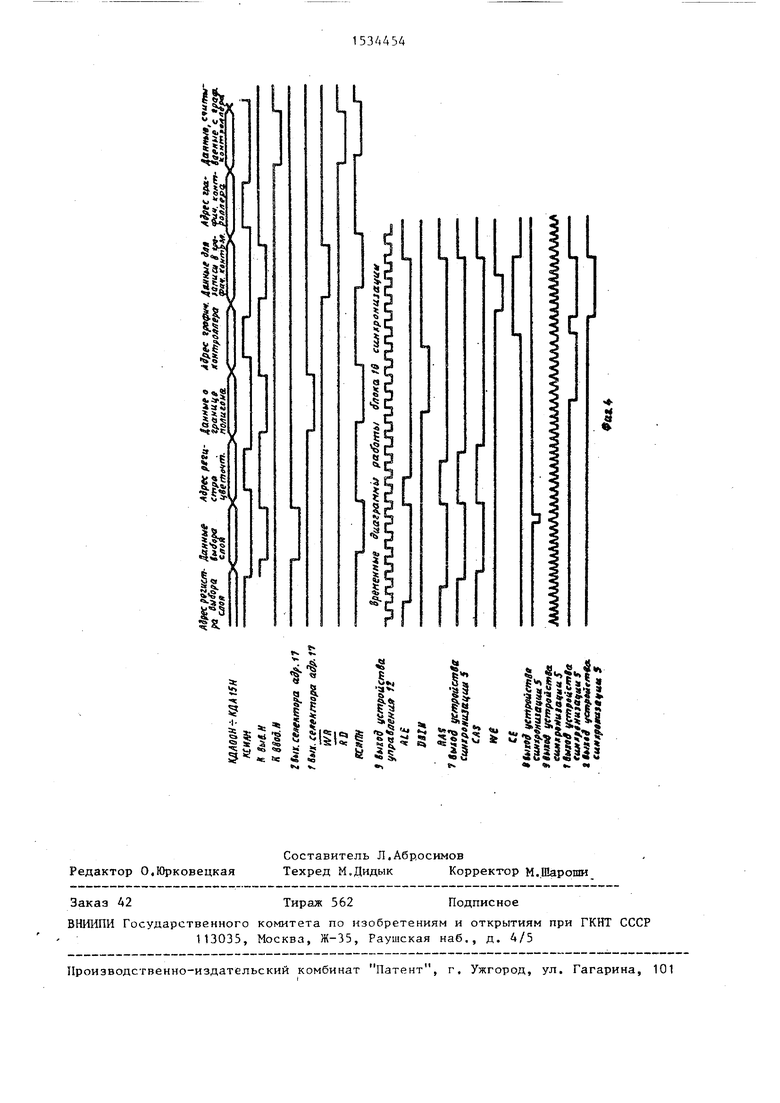

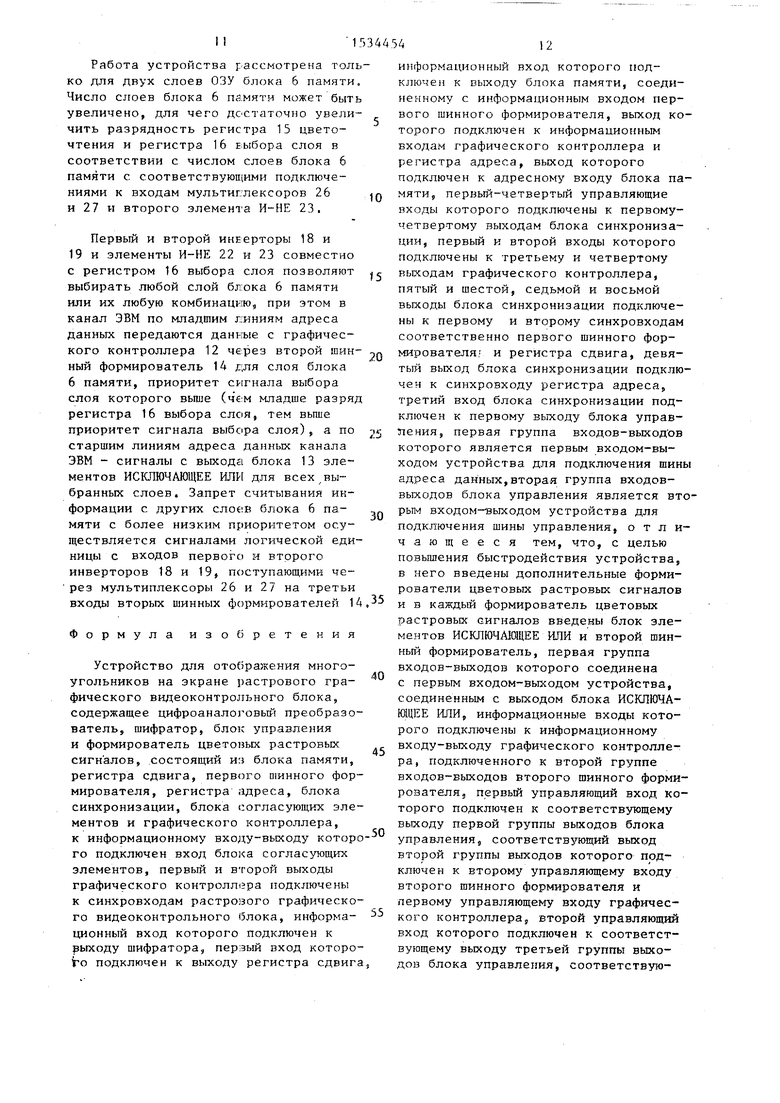

На фиг. 1 приведена схема устрой- ства; на фиг. 2 - схема блока управления; на фиг. 3 приведена схема графического контроллера; на фиг. 4 - временные диаграммы работы селектора адреса и блока синхрони- эацин.

Устройство содержит видеоконтрольный блок 1, цифроаналоговый преобразователь 2, шифратор 3, блок 4 управления, формирователь 5 цветовых растровых сигналов. Формирователь 5 содержит блок 6 памяти, регистр 7 сдвига, первый шинный формирователь 8, регистр 9 адреса, блок 10 синхронизации, блок 11 согласующих эле- ментов, выполненный в виде реэистор- ной матрицы, графический контроллер 12, блок 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛ и второй шинный формирователь 14.

Блок 4 управления содержит регист 15 цветочтения, регистр 16 выбора слоя, селектор 17 адреса, четыре инвертора 18-21, два элемента И-НЕ 22 и 23, генератор 24 импульсов, делитель 25 частоты, два мультиплексора 26 и 27, элемент 28 сопряжения, выполненный в виде резистора, шинный формирователь 29, триггер 30 и блок 31 сопряжения, выполненный в виде ре зисторной матрицы.

Графический контроллер 12 содержи блок 32 управления прямым доступом, интерфейсный блок 33 со статусным регистром, буфер 34 , процессор

.

5

5

35 команд, блок 36 памяти, видеосинх- рогенератор 37, временной генератор 38 памяти, контроллер 39 масштаба, рисующий контроллер 40, контроллер 41 дисплейной памяти с регенерацией, блок 42 управления световым пером и буфер 43.

Первая группа входов-выходов блока 4 управления является первым входом- выходом 44 устройства для подключения к шинам адреса данных канала ЭВМ, вторая группа входов-выходов блока 4 управления является вторым входом-выходом 45 устройства, в состав которой входят вход 46 и выход 47 для выбора слов.

Блок 4 управления имеет 11 выходов (шесть выходов мультиплексоров 26 и 27, два выхода инверторов 20 и 21, два выхода делителя 25 и один выход триггера 10).

По сигналу, сформированному из канального сигнала синхронизации активного устройства (КСИАН) шинным формирователем 29, осуществляется запись сигнала, сформированного шинным формирователем 29 из сигнала КДА01Н в триггере 30. На выходе триггера 30 - сигнал с одиннадцатого выхода блока 4 управления, поступающий на четвертый вход графического контроллера 12 (сигнал АО, фиг, 3), и совместно с сигналами WR и RD определяет следующие режимы работы графического контроллера 12; запись параметров, запись команд, чтение статусных флагов, чтение данных.,

К селектору 17 адреса подключаются входные шины - линии адреса данных канала ЭВМ, а также линии управления канала ЭВМ (кроме КСИПН) и выходная шина - канальный сигнал синхронизации пассивного устройства (КСИПН).

Для работы устройства необходимо (подключение к устройству микро-ЭВМ, вырабатывающей сигналы по линиям адреса данных и линиям управления.

Выходы блока 13 элементов ИСКЛЮЧАЮЩИЕ ИЛИ соединены между собой и подключены непосредственно к старшим разрядам шин данных адреса. Входы КДАООН-КДА15Н - к линии адреса дан- ных канала ЭВМ. На фиг. 2 эти сигналы передаются по шине входа-выхода 44, подключенной к первым входам селектора 17 адреса, регистра 15 цветочтения и регистра 16 выбора слоя.

Сигналы КВЫВН, К ввод. Н, КСИАН, КСИПН входят в состав сигналов линий управления канала ЭВМ, поступающих п шине входа-выхода 45, На фиг. 2 эти сигналы представлены двунаправленной шиной, подключенной к второму входу селектора 17 адреса.

Сигналы RAS, CAS, WE, СЕ (сигналы управления блоком 6 памяти) с произвольным доступом на фиг. 1 представлены выходными сигналами блока 10 синхронизации.

Временная диаграмма (фиг. 4) поясняет работу блока 10 синхрониза- ции.

Для записи информации в блок 6 памяти с произвольным доступом необходимо выполнить операцию Чтение - модификация - запись. Когда сигнал DBIN становится активным (уровень логического нуля), должно произойти чтение данных с блока 6 памяти. В этот момент времени сигналы на первом и втором выходах блока 10 синхро- низации соответственно равны уровню логического нуля (осуществляется выбор кристалла первого Шинного формирователя 8) и уровню логической единицы (направление передачи сигна- лов в первом шинном формирователе 8 - с блока 6 памяти в графический контроллер 12). При этом сигнал установки выходов блока 6 памяти в высокоимпедансное состояние СЕ неактивен (уровень логического нуля) , а сигналами RAS и CAS зафиксирован адрес в блок 6 памяти с регистра 9 адреса.

Запись информации в блок 6 памяти осуществляется в момент, когда сигнал записи WE активен (уровень логического нуля). В этот момент времени сигналы на первом и втором

5

0

5

0

5

выходах блока 10 синхронизации равны уровню логического нуля (осуществляется выбор кристалла первого шинного формирователя 8 и направление передачи сигналов из графического контроллера 12 в блок 6 памяти). При этом сигнал установки выходов блока 6 памяти в высокоимпедансное состояние СЕ активен (уровень логической единицы),а адрес блока 6 памяти, зафиксированный сигналами RAS и CAS, неизменен.

Ведущий и ведомый графические контроллеры 12 различаются тем, что у ведомого графического контроллера 12 выход HSYNC не используется, а к каким бы выходам блока 4 управления они не подключались, между сигналами графических контроллеров 12 (фиг. 1 и 3) различий нет.

Блок 4 управления вырабатывает общие сигналы АО и 2WCLK для ведущего и ведомого графических контроллеров 12 и сигналы WR и RD с разных выходов блока 4 управления (фиг. 1). Указанные два сигнала формируются идентично двумя мультиплексорами 26 и 27. Задание режима работы графическим контроллером 12 (ведомый, ведущий) осуществляется поочередно для каждого графического контроллера 12 командой VSYNC, при этом, выбор нужного графического контроллера 12 осуществляется с помощью регистра 16 выбора слоя.

Устройство для отображения многоугольников на экране растрового графического видеоконтрольного блока работает следующим образом.

В исходном состоянии при помощи селектора 17 адреса в регистр 16 выбора слоя заносится информация, определяющая выбор слоев, с которыми возможна работа, а в регистр 15 цветочтения - информация о границе многоугольника (либо логическая единица, либо нуль) для выбранных слоев.

Селектор 17 адреса служит также для выработки сигнала RD (сигнал снимается с его четвертого выхода), сигнала WR (сигнал снимается с его третьего выхода) и КСИПН, который поступает по линии управления в канал ЭВМ. В режиме записи (RD установлен в логическую единицу) при условии выбора данного слоя (на данном выходе регистра 16 выбора слоя присутствует сигнал логического нуля)

на выходы мультиплексора, например, 26 поступают сигналы с четных его входов,jj именно: с первого выхода - сигнал WR, с второго выхода - сигнал логической единицы, поступающий на второй вход второго шинного формирователя 14 и на вход KD графического контроллера 12 (его первый вход), с третьего выхода - сигнал с соответствующего выхода регистра 15 цветочтения, с четвертого выхода - сигнал логического нуля, поступающий на первый вход второго шинного формирователя 14 и осуществляющий его выборку. Сигнал логической единицы на первом входе второго шинного формирователя 14 управляет прохождением сигналов с младших линий адреса данных канала ЭВМ на первые входы-выходы графического контроллера 12 и блока 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с возможностью объединения по выходам. На третий вход графического контроллера 12 с первого выхода пятой группы блока 4 управления прс- тупает сигнал . Сигнал с второго выхода первой группы блока 4 управления (АО) поступает на четвертый вход графического контроллера 12 и совместно с сигналами WR и RD определяет следующие режимы работы графического контроллера 12: АО О, RD 1, WR 0 - запись параметров, АО 1, RD запись команд; АО О, RD О, WR 1 ние статусных флагов; АО 1, RD О, WR 1 - чтение данных.

Сигналы ALE и DBIN с третьего и четвертого выходов графического конт роллера 12 совместно с сигналом с выхода блока 4 управления являются вхоными для блока 10 синхронизации. Последний вырабатывает сигналы управления первым шинным формирователем 8 (сигналы с его первого и второго выходов), сигналы управления блоком 6 памяти RAS, CAS, WE и СЕ, сигналы управления работой регистров 7, сигнал управления записью адреса в регистр 9 адреса. В результате графический контроллер 12 записывает в блок 6 памяти информацию, подлежащую индикации на видеоконтрольном блоке 1. Регистры 7 преобразуют считываемые в параллельном коде данные с блока 6 памяти в последовательный код. Данные в последовательном коде для выбранных слоев поступают на входы

0

5

0

5

Q 0

5

5

0

5

шифратора 3 и чергч цифроаналогоный преобразователь 2 на входы R, G и В блока 1, строчный и кадровый синхронизирующие импульсы на который поступают с первого и второго выходов ведущего графического контроллера 12, Ведомые графические контроллеры 12 синхронизируются с ведущим графическим контроллером 12 по сигналу кадрового синхронизирующего импульса, снимаемого с его второго выхода. В результате графические контроллеры 12 при условии выбора данных слоев блока 6 памяти по командам, поступающим из канала ЭВМ, записывают необходимую информацию в блок 6 памяти, отображаемую на блоке 1.

В режиме чтения (RD установлен в логический нуль) при условии выбора данного слоя (на данном выходе регистра 16 выбора слоя присутствует сигнал логического нуля) на выходы мультиплексора, например, 26 поступают сигналы с нечетных его входов, а именно: с первого выхода - сигнал логической единицы, с второго выхода - сигнал логического нуля, поступающий на второй вход второго шинного (формирователя 14 и на вход Ш) графического контроллера 12 (его второй вход), с третьего выхода - сигнал с соответствующего выхода регистра 15 цветочтения, с четвертого выхода - сигнал с входа 46 для выбора слоя, блока 4 управления, поступающий на третий вход второго шинного формирователя 14 и в зависимости от уровня данного сигнала осуществляющий выборку либо установку в высокоимпедан- сное состояние выходов второго шинного формирователя 14. Сигнал логического нуля на втором входе второго шинного формирователя 14 управляет прохождением сигналов с первого входа-выхода графического контроллера 12 в младшие линии адреса данных канала ЭВМ (DO-D7). На третий вход графического контроллера t2 с первого выхода пятой группы блока 4 управления поступает сигнал 2«WCLK. Блок 10 синхронизации вырабатывает сигналы управления первым шинным формирователем 8, сигналы управления блоком 6 памяти RAS, CAS, WE и СЕ, сигнал управления записью адреса в регистр 9 адреса. В результа- те считываются данные с блока 6 памяти в графический контроллер 12,

а из него - в младшие линии адреса данных ЭВМ.

Рассмотрим работу устройства при определении границ многоугольников на примере двух слоев, Если, например, необходимо заполнить многоугольники в первом слое, границы которого определяются сигналом логической единицы, в регистр 16 выбора слоя заносится код 01, а в регистр 15 цветочтения - любой из кодов 11 или 10. В результате мультиплексор 27 находится в отключенном состоянии, а на его выходах присутствуют сигналы логической единицы благодаря блоку 31 (резисторной матрицы). Сигналы с вторых выходов первой, второй и третьей групп блока 4 управления приводят к тому, что выходы-входы второго шинного формирователя 14 и первые входы-выходы соответствующего графического контроллера 12 находятся в высокоимпедансном состоянии, а на первых входах блока 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ присутствует сигнал логической единицы благодаря блоку 11. Так как на вторые входы блока 13, относящиеся к второму слою блока 6 памяти, поступает сигнал логического нуля с выхода четвертого инвертора 21, на вход которого поступает сигнал логической единицы, на их выходах присутствуют сигналы логической единицы, не оказывающие влияния на выходные сигналы блока 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, относящиеся к первому слою блока 6 памяти. На Первые входы блока 13 с первого входа-выхода графического контроллера

12побайтно поступает информация о ячейках блока 6 памяти, и до границы полигона во всех разрядах байтов присутствуют сигналы логического нуля. На вторые входы блока 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с выхода третьего инвертора 20 поступает сигнал логического нуля. Таким образом, до границы многоугольника на выходах блока

13элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первыми входами которых являются первые входы-выходы графического контроллера 12, соответствующего первому слою блока 6 памяти, а на вторые входы поступает сигнал логического нуля с выхода третьего инвертора 20, присутствуют сигналы логического нуля. Если же граница многоугольника попадает в байт информации, поступающей с

0

5

0

5

0

5

0

5

0

5

первого входа-выхода графического контроллера 12, о ячейках блока 6 памяти, относящихся к первому слою, то на одном из первых входов блока 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ появляется сигнал логической единицы, что приводит к появлению сигнала логической единицы на выходе данного блока 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Так как выходы блока 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно для всех слоев блока 6 памяти, то только в одном разряде старших линий адреса данных канала ЭВМ присутствует сигнал логической единицы, свидетельствующий об определении границы многоугольника. Если же граница многоугольника задана сигналами логического нуля, то в регистр 15 цветочтения заносится любой из кодов 01 или 00. При этом на выходах блока 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ присутствуют сигналы логического нуля до границы многоугольника и сигнал логической единицы для одного из разрядов старшего байта линий адреса канала ЭВМ, свидетельствующий об определения границы многоугольника.

Рассмотрим один из алгоритмов заполнения многоугольника.

Многоугольник произвольной формы разбивается на треугольники и трапеции, боковые стороны которых совпадают с границами многоугольника. Заполнение каждой фигуры выполняется следующим образом.

Выбирается точка внутри фигуры с координатой X, при которой координата Y по абсолютной величине максимальна и координатой Y ДҐ /2. Побайтно считывается информация с блока 6 памяти в направлении увеличения координаты X и определяется граница многоугольника. Возвращаясь в исходную точку и побайтно считывая информацию с блока 6 памяти в направлении уменьшения координаты X, определяют новую границу многоугольника. Уменьшая координату Y исходной точки на единицу и считывая информацию с блока 6 памяти в направлении увеличения координаты X и уменьшения координаты Y, определяют новые точки границы полигона. Для точек границы многоугольника с одинаковыми координатами Y проводится вектор по предварительно заданному образцу.

Работа устройства рассмотрена только для двух слоев ОЗУ блока 6 памяти. Число слоев блока 6 памяти может быть увеличено, для чего достаточно увеличить разрядность регистра 15 цвето- чтения и регистра 16 выбора слоя в соответствии с числом слоев блока 6 памяти с соответствующими подключениями к входам мультиплексоров 26 и 27 и второго элемента И-НЕ 23.

Первый и второй инверторы 18 и 19 и элементы И-НЕ 22 и 23 совместно с регистром 16 выбора слоя позволяют выбирать любой слой блока 6 памяти или их любую комбинацию, при этом в канал ЭВМ по младшим линиям адреса данных передаются данные с графического контроллера 12 через второй шин- ный формирователь 14 для слоя блока 6 памяти, приоритет сигнала выбора слоя которого выше (чем младше разряд регистра 16 выбора слоя, тем выше приоритет сигнала выбора слоя), а по старшим линиям адреса данных канала ЭВМ - сигналы с выхода блока 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ для всех .выбранных слоев. Запрет считывания информации с других слоев блока 6 па- мяти с более низким приоритетом осуществляется сигналами логической единицы с входов первого и второго инверторов 18 и 19, поступающими через мультиплексоры 26 и 27 на третьи входы вторых шинных формирователей 14

Формула изобретения

Устройство для отображения много

угольников на экране растрового графического видеоконтрольного блока, содержащее цифроаналоговый преобразователь, шифратор, блок управления и формирователь цветовых растровых сигналов, состоящий из блока памяти, регистра сдвига, первого шинного формирователя, регистра адреса, блока синхронизации, блока согласующих элементов и графического контроллера, к информационному входу-выходу которого подключен вход блока согласующих элементов, первый и второй выходы графического контроллера подключены к синхровходам растрового графического видеоконтрольного блока, информа- ционный вход которого подключен к выходу шифратора, первый вход которо- i o подключен к выходу регистра сдвига

,

JQ

с ,„ 25 ,

40

,

50

информационный вход которого подключен к выходу блока памяти, соединенному с информационным входом первого шинного формирователя, выход которого подключен к информационным входам графического контроллера и регистра адреса, выход которого подключен к адресному входу блока памяти, первый-четвертый управляющие входы которого подключены к первому- четвер-тому выходам блока синхронизации, первый и второй входы которого подключены к третьему и четвертому выходам графического контроллера, пятый и шестой, седьмой и восьмой выходы блока синхронизации подключены к первому и второму синхровходам соответственно первого шинного формирователя и регистра сдвига, девятый выход блока синхронизации подкпю- чен к синхровходу регистра адреса, третий вход блока синхронизации подключен к первому выходу блока управления, первая группа входов-выходов которого является первым входом-выходом устройства для подключения шины адреса данных,вторая группа входов- выходов блока управления является вторым входом-выходом устройства для подключения шины управления, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены дополнительные формирователи цветовых растровых сигналов и в каждый формирователь цветовых растровых сигналов введены блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и второй шинный формирователь, первая группа входов-выходов которого соединена с первым входом-выходом устройства, соединенным с выходом блока ИСКЛЮЧАЮЩЕЕ ИЛИ, информационные входы которого подключены к информационному входу-выходу графического контроллера, подключенного к второй группе входов-выходов второго шинного формирователя, первый управляющий вход которого подключен к соответствующему выходу первой группы выходов блока управления, соответствующий выход второй группы выходов которого подключен к второму управляющему входу второго шинного формирователя и первому управляющему входу графического контроллера, второй управляющий вход которого подключен к соответствующему выходу третьей группы выходов блока управления, соответствующий выход четвертой группы выходов которого подключен к управляющему входу блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, третий и четвертый управляющие

входы всех графических контроллеров подключены к первому и второму выходам пятом группы выходов блока управления .

ii 1 I ЫФ & la 5Ыз

| || |t 1ФЙЦ

lhnl F ififiy

i 4 K S 4c«c«c«w

«S.V. «I «k «

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для редактирования и контроля управляющих программ для станков с числовым программным управлением на экране электронно-лучевой трубки | 1986 |

|

SU1451676A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1983 |

|

SU1244704A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для контроля печатных плат | 1986 |

|

SU1472929A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2012 |

|

RU2524852C2 |

| Программируемый контроллер | 1991 |

|

SU1833870A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для отображения графической информации на экране растрового дисплея | 1985 |

|

SU1363179A1 |

Изобретение относится к области машинной растровой графики и может быть использовано для заполнения многоугольников, отображаемых на ЭЛТ устройства визуального вывода. Целью изобретения является повышение быстродействия устройства за счет увеличения скорости определения границ многоугольников. Цель достигается тем, что в устройство, содержащее видеоконтрольный блок 1, цифроаналоговый преобразователь 2, шифратор 3, блок 4 управления, формирователь 5 цветовых растровых сигналов, содержащий блок 6 памяти, регистр 7 сдвига, первый шинный формирователь 8, регистр 9 адреса, блок 10 синхронизации, блок 11 согласующих элементов с их связями, введены дополнтельные формирователи 5 цветовых растровых сигналов и в каждый формирователь 5 введены блок 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и второй шинный формирователь 14 с их связями, что позволяет повысить скорость определения границ многоугольника при его заполнении за счет программно-аппаратного определения границ многоугольников. 4 ил.

| Патент США 4481594, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Пуговица | 0 |

|

SU83A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1990-01-07—Публикация

1987-06-01—Подача