Изобретение относится к вычислительной технике и может быть использовано в растровых дисплеях персональных ЭВМ и графических терминалах

Цель изобретения - повышение быстродействия устройства за счет увеличения скорости модификации битовой карты изображения в памяти и уменьшения среднего времени доступа и экранной памяти .

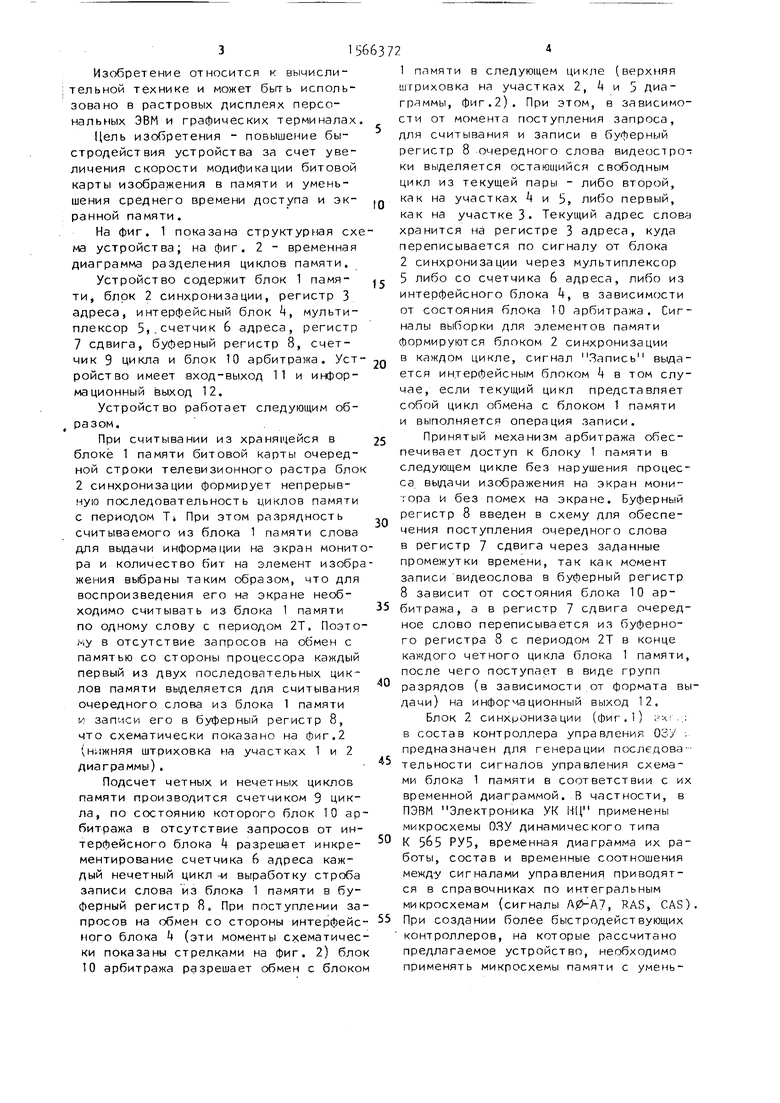

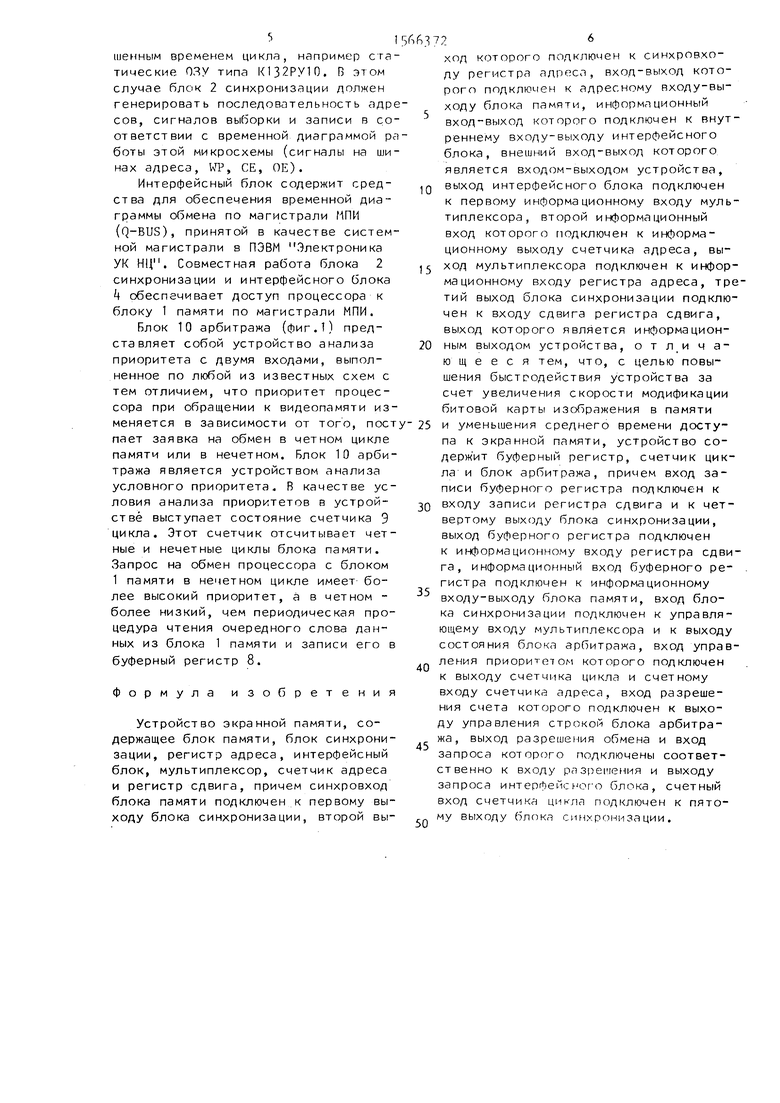

На фиг. 1 показана структурная схема устройства; на фиг. 2 - временная диаграмма разделения циклов памяти. Устройство содержит блок 1 памяти, блок 2 синхронизации, регистр 3 адреса, интерфейсный блок А, мультиплексор 5, счетчик 6 адреса, регистр 7 сдвига, буферный регистр 8, счетчик 9 Цикла и блок 10 арбитража. Устройство имеет вход-выход 11 и информационный выход 12.

Устройство работает следующим образом.

При считывании из хранящейся в блоке 1 памяти битовой карты очередной строки телевизионного растра бло 2 синхронизации формирует непрерывную последовательность циклов памяти с периодом Ti При этом разрядность считываемого из блока 1 памяти слова для выдачи информации на экран монитра и количество бит на элемент изобржения выбраны таким образом, что для воспроизведения его на экране необходимо считывать из блока 1 памяти по одному слову с периодом 2Т. Поэтому в отсутствие запросов на обмен с памятью со стороны процессора каждый первый из двух последовательных циклов памяти выделяется для считывания очередного слова из блока 1 памяти и записи его в буферный регистр 8, что схематически показано на фиг.2 унпжняя штриховка на участках 1 и 2 диаграммы).

Подсчет четных и нечетных циклов памяти производится счетчиком 9 цикла, по состоянию которого блок 10 арбитража в отсутствие запросов от интерфейсного блока k разрешает инкре- ментирование счетчика f адреса каждый нечетный цикл -и выработку строба записи слова из блока 1 памяти в буферный регистр 8. При поступлении запросов на обмен со стороны интерфейс ного блока 1 (эти моменты схематически показаны стрелками на фиг. 2) бло 10 арбитража разрешает обмен с блоко

0

5

0

5

5

0

35

40

45

50

1памяти в следующем цикле (верхняя штриховка на участках 2, 4 и 5 Диаграммы, фиг. 2). При этом, в зависимости от момента поступления запроса, для считывания и записи в буферный регистр 8 очередного слова видеостроки выделяется остающийся свободным цикл из текущей пары - либо второй, как на участках k и 5, либо первый, как на участке 3. Текущий адрес слова хранится на регистре 3 адреса, куда переписывается по сигналу от блока

2синхронизации через мультиплексор 5 либо со счетчика 6 адреса, либо из интерфейсного блока А, в зависимости от состояния блока 10 арбитража. Сигналы выборки для элементов памяти формируются блоком 2 синхронизации

в каждом цикле, сигнал Запись выдается интерфейсным блоком Ц в том случае, если текущий цикл представляет собой цикл обмена с блоком 1 памяти и выполняется операция записи.

Принятый механизм арбитража обеспечивает доступ к блоку 1 памяти в следующем цикле без нарушения процесса выдачи изображения на экран мони- :ора и без помех на экране. Буферный регистр 8 введен в схему для обеспечения поступления очередного слова в регистр 7 сдвига через заданные промежутки времени, так как момент записи видеослова в буферный регистр 8 зависит от состояния блока 10 арбитража, а в регистр 7 сдвига очередное слово переписывается из буферного регистра 8 с периодом 2Т в конце каждого четного цикла блока 1 памяти, после чего поступает в виде групп разрядов (в зависимости от формата выдачи) на информационный выход 12.

Блок 2 синхронизации (фиг.1) . в состав контроллера управления предназначен для генерации поондова тельности сигналов управления схемами блока 1 памяти в соответствии с их временной диаграммой. В частности, в ПЭВМ Электроника УК НЦ применены микросхемы ПЗУ динамического типа К 5б5 РУ5, временная диаграмма их работы, состав и временные соотношения между сигналами управления приводятся в справочниках по интегральным микросхемам (сигналы А0-А7, KAS, CAS). При создании более быстродействующих контроллеров, на которые рассчитано предлагаемое устройство, необходимо применять микросхемы памяти с умень 1

темным временем цикла, например сга- тимеские ОЯУ типа К132РУ10. В этом случае блок 2 синхронизации должен генерировать последовательность адресов, сигналов выборки и записи в соответствии с временной диаграммой работы этой микросхемы (сигналы на шинах адреса, WP, СЕ, ПК).

Интерфейсный блок содержит средства для обеспечения временной диаграммы обмена по магистрали МПИ (Q-BUS), принятой в качестве системной магистрали в ПЭВМ Электроника УК НЦ. Совместная работа блока 2 синхронизации и интерфейсного блока 4 обеспечивает доступ процессора к блоку 1 памяти по магистрали МПИ.

Блок 10 арбитража (фиг . 1) представляет собой устройство анализа приоритета с двумя входами, выполненное по любой из известных схем с тем отличием, что приоритет процессора при обращении к видеопамяти изменяется в зависимости от того, постпает заявка на обмен в четном цикле памяти или в нечетном. Блок 10 арбитража является устройством анализа условного приоритета. В качестве условия анализа приоритетов в устройстве выступает состояние счетчика 3 цикла. Этот счетчик отсчитывает четные и нечетные циклы блока памяти. Запрос на обмен процессора с блоком 1 памяти в нечетном цикле имеет более высокий приоритет, а в четном - более низкий, чем периодическая процедура чтения очередного слова данных из блока 1 памяти и записи его в буферный регистр 8.

Формула изобретения

Устройство экранной памяти, содержащее блок памяти, блок синхронизации, регистр адреса, интерфейсный блок, мультиплексор, счетчик адреса и регистр сдвига, причем синхровход блока памяти подключен к первому выходу блока синхронизации, второй

ход которого подключен к синхровхо- ду регистра адреса, вход-выход которого подключен к адресному входу-выходу блока памяти, информационный вход-выход которого подключен к внутреннему входу-выходу интерфейсного блока, внешний вход-выход которого является входом-выходом устройства,

выход интерфейсного блока подключен к первому информационному входу мультиплексора, второй информационный вход которого подключен к информационному выходу счетчика адреса, выход мультиплексора подключен к информационному входу регистра адреса, третий выход блока синхронизации подключен к входу сдвига регистра сдвига, выход которого является информационным выходом устройства, отличающееся тем, что, с целью повышения быстродействия устройства за счет увеличения скорости модификации битовой карты изображения в памяти

и уменьшения среднего времени доступа к экранной памяти, устройство содержит буферный регистр, счетчик цикла и блок арбитража, причем вход записи буферного регистра подключен к

входу записи регистра сдвига и к четвертому выходу блока синхронизации, выход буферного регистра подключен к информационному входу регистра сдвига, информационный вход буферного регистра подключен к информационному входу-выходу блока памяти, вход блока синхронизации подключен к управляющему входу мультиплексора и к выходу состояния блока арбитража, вход управления приоритетом которого подключен к выходу счетчика цикла и счетному входу счетчика адреса, вход разрешения счета которого подключен к выходу управления строкой блока арбитража, выход разрешения обмена и вход запроса которого подключены соответственно к входу р-кзрепения и выходу запроса интерфейсного блока, счетный вход счетчика цикла подключен к пятому выходу синхронизации.

v W i (V i f

i i

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

Изобретение относится к вычислительной технике и может быть использовано в растровых дисплеях персональных ЭВМ и графических терминалах. Цель изобретения - повышение быстродействия устройства за счет увеличения скорости модификации битовой карты изображения в памяти и уменьшения среднего времени доступа к экранной памяти. Поставленная цель достигается тем, что устройство содержит блок 1 памяти, блок 2 синхронизации, регистр 3 адреса, интерфейсный блок 4, мультиплексор 5, счетчик 6 адреса, регистр 7 сдвига, буферный регистр 8, счетчик 9 цикла, блок 10 арбитража, вход-выход 11, информационный выход 12. 2 ил.

| КОПИРОВАЛЬНЫЙ СТАНОК ДЛЯ ДЕРЕВА | 1925 |

|

SU7220A1 |

| Техническое описание | |||

| Приспособление для направления воды, поступающей к гребным винтам многовинтовых судов | 1926 |

|

SU6384A1 |

| Техническое описание | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СПОСОБ ПОЛУЧЕНИЯ ТВЕРДЫХ ПРОДУКТОВ УПЛОТНЕНИЯ ФОРМАЛЬДЕГИДА С ФЕНОЛАМИ И ДРУГИМИ ВЕЩЕСТВАМИ | 1925 |

|

SU511A1 |

| Техническое описание | |||

| Микропроцессорные средства и системы | |||

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

1990-05-23—Публикация

1988-05-10—Подача