сл

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Программно-управляемый модуль | 1986 |

|

SU1403018A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1367036A1 |

| Частотный модулятор | 1984 |

|

SU1145473A1 |

| Устройство автоматической стабилизации амплитуды видеосигнала | 1990 |

|

SU1757124A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Датчик углового положения,скорости и ускорения вращения вала | 1983 |

|

SU1101740A1 |

| Устройство для программного счета изделий | 1985 |

|

SU1365103A1 |

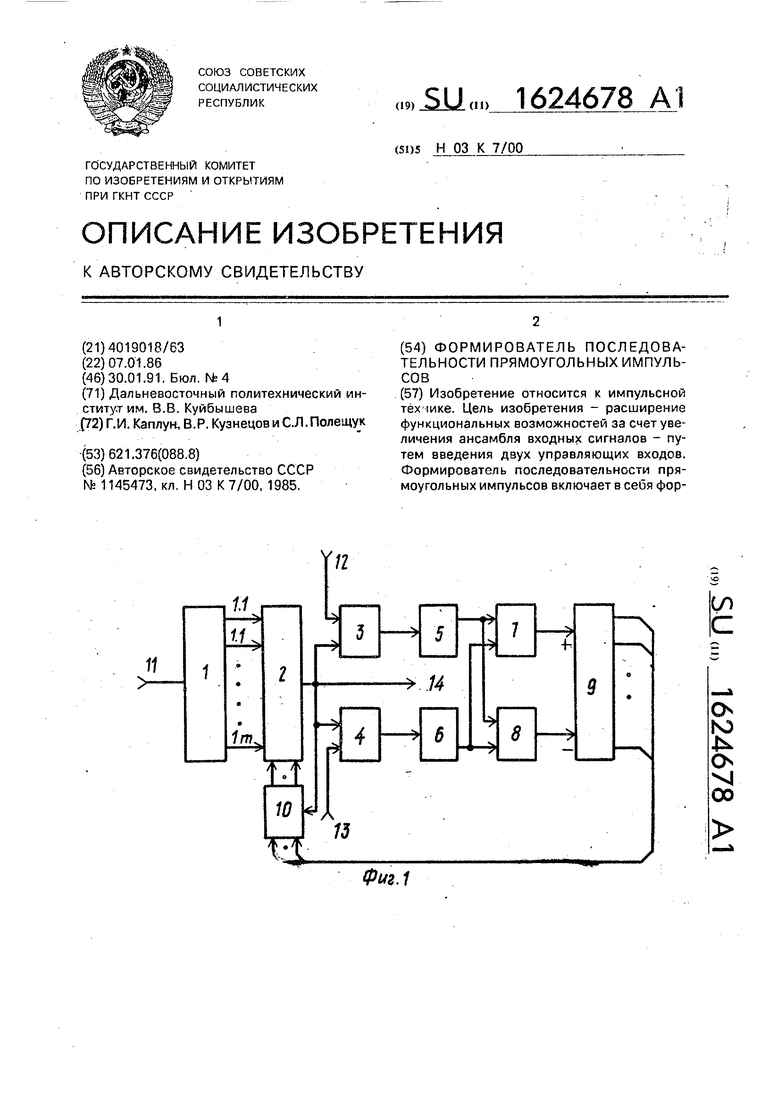

Изобретение относится к импульсной тех ике. Цель изобретения - расширение функциональных возможностей за счет увеличения ансамбля входных сигналов - путем введения двух управляющих входов. Формирователь последовательности прямоугольных импульсов включает в себя фор

О

ю

о XI

00

ФигЛ

мирователь многофазного сигнала, вход которого соединен с первым входом 11 формирователя последовательности прямо- УТР пьных импульсов. На вход 11 подают вх дную последовательность импульсов частоты FBX. Выход формирователя 1 мно- гофрзного сигнала подключен к информаци- ониому входу коммутатора 2, номер последовательности, поступающей на выход коммутатора 2, определяется кодом на его управляющем входе. Каждая последующая последовательность импульсов сдвинута по времени относительно предыдущей на время 1/m- FBX, где т - количество формируемых последовательностей. Выход коммутатора 2 подключен к выходу 14 формирователя последовательности прямоугольных импульсов, и синхронизирующим входам первого 3 и второго 4 триггеров, входу разрешения записи регистра 10. Информационный вход триггера 3(4) соединен

Изобретение относится к импульсной технике и может быть использовано в импульсных устройствах автоматики, системах передачи информации.

Цель изобретения - расширение функ- циональных возможностей за счет увеличения ансамбля входных сигналов путем введения двух управляющих входов,

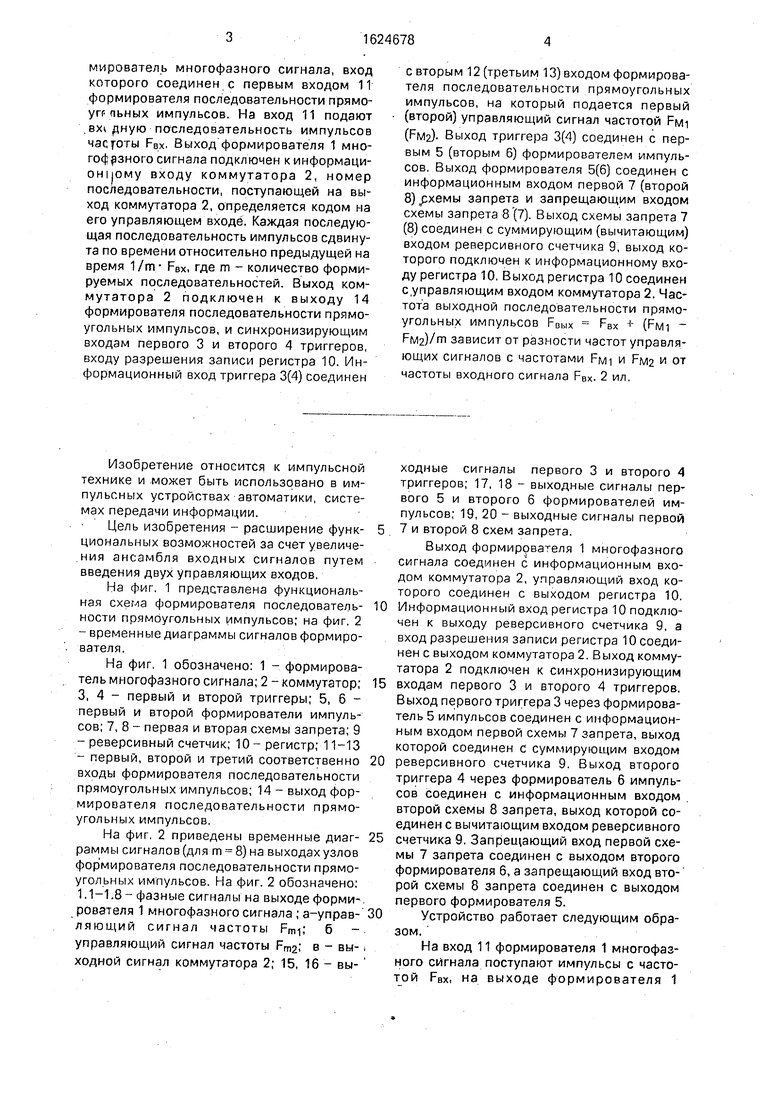

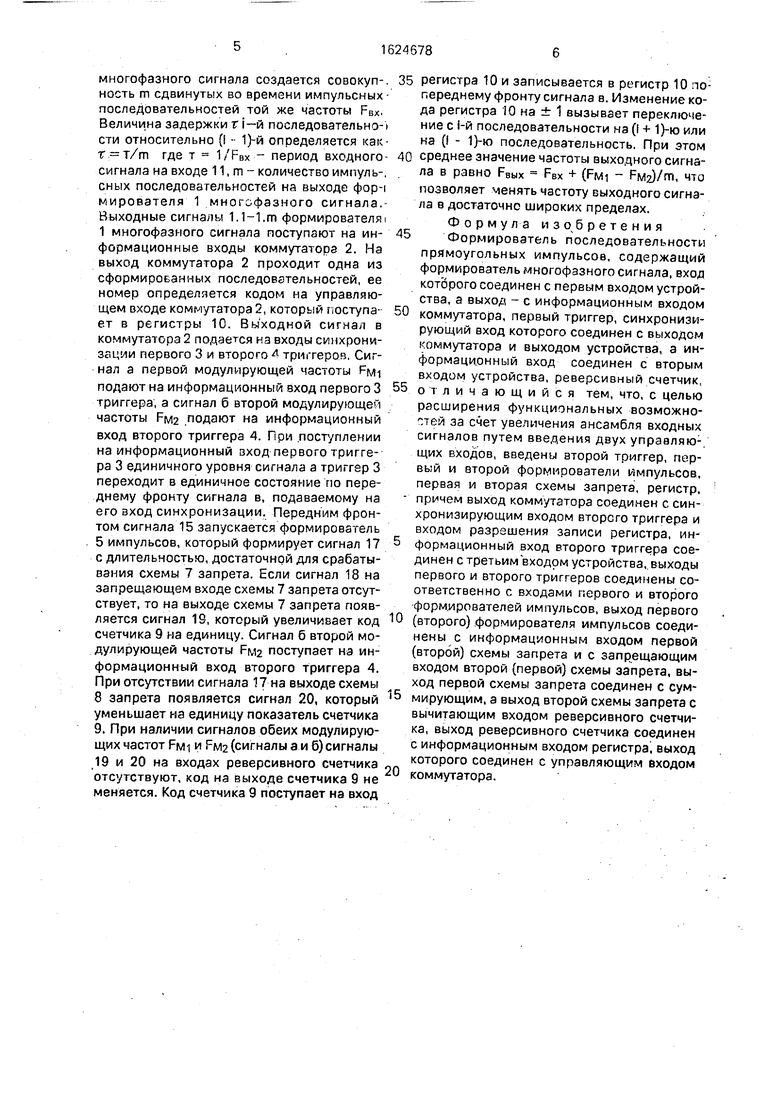

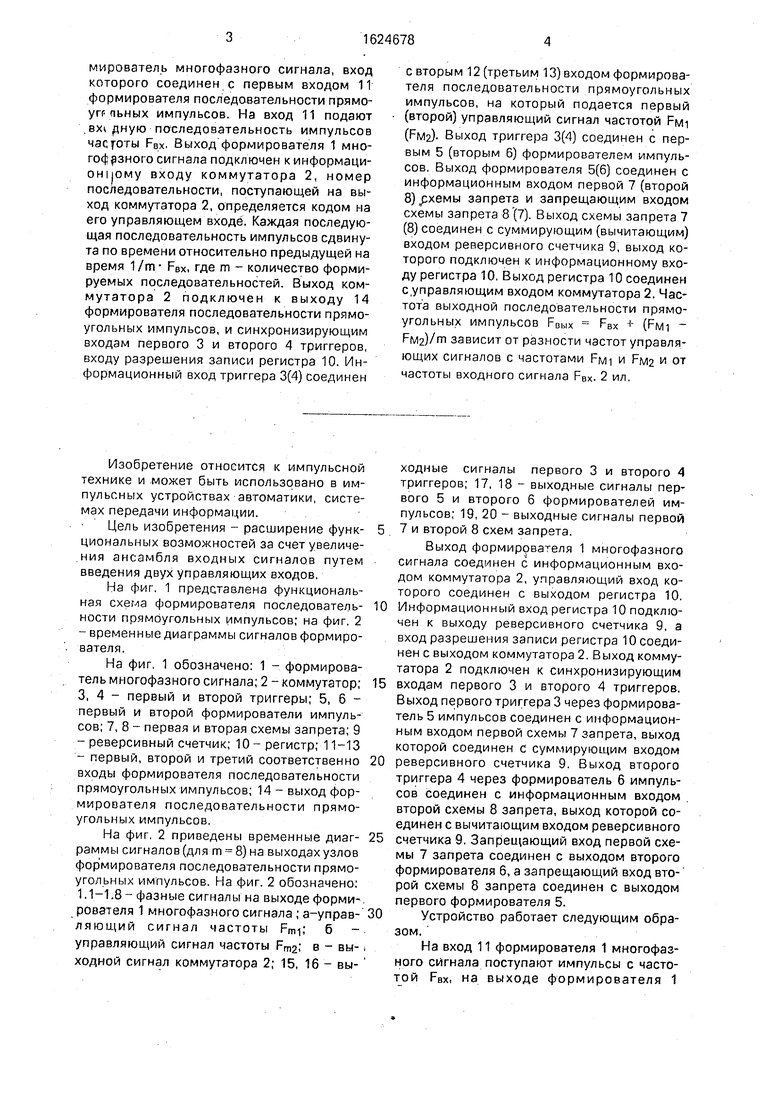

На фиг. 1 представлена функциональная схема формирователя последователь- ности прямоугольных импульсов; на фиг. 2

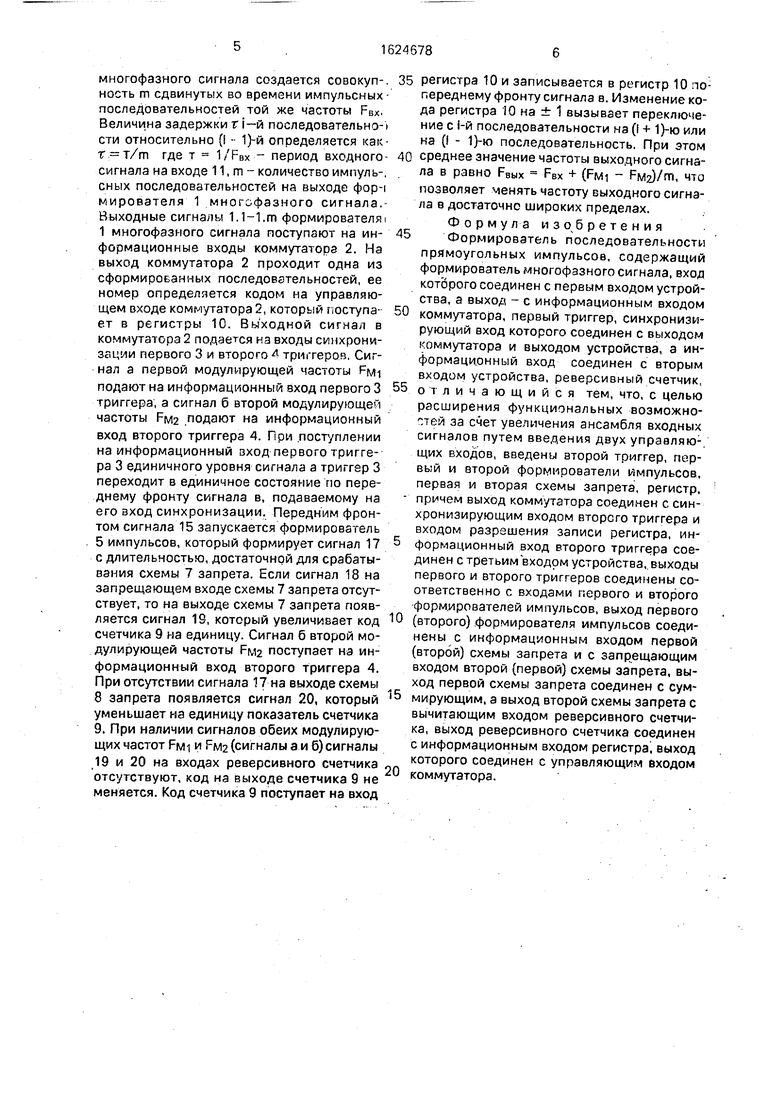

-временные диаграммы сигналов формирователя.

На фиг, 1 обозначено: 1 - формирователь многофазного сигнала; 2 - коммутатор; 3, 4 - первый и второй триггеры; 5, 6 - первый и второй формирователи импульсов; 7, 8 - первая и вторая схемы запрета; 9

-реверсивный счетчик; 10 - регистр; 11-13

-первый, второй и третий соответственно входы формирователя последовательности прямоугольных импульсов; 14 - выход формирователя последовательности прямоугольных импульсов.

На фиг. 2 приведены временные диаг- раммы сигналов (для m 8) на выходах узлов формирователя последовательности прямоугольных импульсов. На фиг. 2 обозначено; 1.1-1.8 - фазные сигналы на выходе формирователя 1 многофазного сигнала ; а-управ- ляющий сигнал частоты Fmi, б - управляющий сигнал частоты fmz в - выходной сигнал коммутатора 2; 15, 16 - выс вторым 12 (третьим 13) входом формирователя последовательности прямоугольных импульсов, на который подается первый (второй) управляющий сигнал частотой FM-I (Рмг)- Выход триггера 3(4) соединен с первым 5 (вторым 6) формирователем импульсов. Выход формирователя 5(6) соединен с информационным входом первой 7 (второй 8) „схемы запрета и запрещающим входом схемы запрета 8 (7). Выход схемы запрета 7 (8) соединен с суммирующим (вычитающим) входом реверсивного счетчика 9, выход которого подключен к информационному входу регистра 10, Выход регистра 10 соединен с .управляющим входом коммутатора 2. Частота выходной последовательности прямоугольных импульсов Рвых FBX + (FMI - FM2) зависит от разности частот управляющих сигналов с частотами FM-I и Рм2 и от частоты входного сигнала FBx. 2 ил.

ходные сигналы первого 3 и второго 4 триггеров; 17, 18 - выходные сигналы первого 5 и второго 6 формирователей импульсов; 19, 20 - выходные сигналы первой 7 и второй 8 схем запрета.

Выход формирователя 1 многофазного сигнала соединен с информационным входом коммутатора 2, управляющий вход которого соединен с выходом регистра 10. Информационный вход регистра 10 подключен к выходу реверсивного счетчика 9, а вход разрешения записи регистра 10 соединен с выходом коммутатора 2. Выход коммутатора 2 подключен к синхронизирующим входам первого 3 и второго 4 триггеров. Выход первого триггера 3 через формирователь 5 импульсов соединен с информационным входом первой схемы 7 запрета, выход которой соединен с суммирующим входом реверсивного счетчика 9. Выход второго триггера 4 через формирователь 6 импульсов соединен с информационным входом второй схемы 8 запрета, выход которой соединен с вычитающим входом реверсивного счетчика 9. Запрещающий вход первой схемы 7 запрета соединен с выходом второго формирователя 6, а запрещающий вход второй схемы 8 запрета соединен с выходом первого формирователя 5.

Устройство работает следующим образом.

На вход 11 формирователя 1 многофазного сигнала поступают импульсы с частотой FBX, на выходе формирователя 1

многофазного сигнала создается совокупность m сдвинутых во времени импульсных последовательностей той же частоты FBx. Величина задержки г i-й последовательности относительно (i - 1)-й определяется как r T/m где т 1/FBx - период входного сигнала на входе 11, m - количество импуль-. сных последовательностей на выходе фор-i мирователя 1 многофазного сигнала.- Выходные сигналы 1..т формирователя 1 многофазного сигнала поступают на ин- формациейные входы коммутатора 2. На выход коммутатора 2 проходит одна из сформироеаниых последовательностей, ее номер определяется кодом на управляющем входе коммутатора 2, который поступа- ет в регистры 10. Выходной сигнал в коммутатора 2 подается на входы синхронизации первого 3 и второго л триггеров. Сигнал а первой модулирующей частоты F(1 подают на информационный вход первого 3 триггера, а сигнал б второй модулирующем частоты Рм2 .п°Дают на информационный вход второго триггера 4. При поступлении на информационный вход первого триггера 3 единичного уровня сигнала а триггер 3 переходит в единичное состояние по переднему фронту сигнала в, подаваемому на его вход синхронизации. Передним фронтом сигнала 15 запускается формирователь 5 импульсов, который формирует сигнал 17 с длительностью, достаточной для срабатывания схемы 7 запрета. Если сигнал 18 на запрещающем входе схемы 7 запрета отсутствует, то на выходе схемы 7 запрета появляется сигнал 19, который увеличивает код счетчика 9 на единицу. Сигнал б второй модулирующей частоты Рм2 поступает на информационный вход второго триггера 4. При отсутствии сигнала 17 на выходе схемы 8 запрета появляется сигнал 20, который уменьшает на единицу показатель счетчика 9. При наличии сигналов обеих модулирующих частот FM-J и FM2 (сигналы а и б) сигналы 19 и 20 на входах реверсивного счетчика отсутствуют, код на выходе счетчика 9 не меняется. Код счетчика 9 поступает на вход

,а

35 40 45 5055 5 0п

15

регистра 10 и записывается в регистр 10 по- переднему фронту сигнала в. Изменение кода регистра 10 на ± 1 вызывает переключение с i-й последовательности на (I + 1)-ю или на (I - 1)-ю последовательность. При этом среднее значение частоты выходного сигнала в равно Рвых FBx + (FMI - Рм2)/пг. что позволяет менять частоту выходного сигнала в достаточно широких пределах. Формула изобретения Формирователь последовательности прямоугольных импульсов, содержащий формирователь многофазного сигнала, вход которого соединен с первым входом устройства, а выход - с информационным входом коммутатора, первый триггер, синхронизирующий вход которого соединен с выходом коммутатора и выходом устройства, а информационный вход соединен с вторым входом устройства, реверсивный счетчик, отличающийся тем, что, с целью расширения функциональных возможностей за счет увеличения ансамбля входных сигналов путем введения двух управляющих входов, введены второй триггер, первый и второй формирователи импульсов, первая и вторая схемы запрета, регистр, причем выход коммутатора соединен с синхронизирующим входом второго триггера и входом разрешения записи регистра, информационный вход второго триггера соединен с третьим входом устройства, выходы первого и второго триггеров соединены соответственно с входами первого и второго формирователей импульсов, выход первого (второго) формирователя импульсов соединены с информационным входом первой (второй) схемы запрета и с запрещающим входом второй (первой) схемы запрета, выход первой схемы запрета соединен с суммирующим, а выход второй схемы запрета с вычитающим входом реверсивного счетчика, выход реверсивного счетчика соединен с информационным входом регистра, выход которого соединен с управляющим входом коммутатора.

J

Lf

Фиг. 2

| Частотный модулятор | 1984 |

|

SU1145473A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-30—Публикация

1986-01-07—Подача