Изобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для синтеза сложных частотно-модулированных сигналов и может быть использовано в системах радиосвязи и телекоммуникациях.

Известны цифровые синтезаторы частотно-модулированных сигналов, содержащие эталонный генератор и блок задержки, блок постоянного запоминания, регистр памяти, делитель с переменным коэффициентом деления, цифровой накопитель, преобразователь кодов, ЦАП, ФНЧ, ждущий мультивибратор, реверсивный счетчик с предварительной установкой, схему сравнения [1].

Наиболее близким техническим решением (прототипом) к предлагаемому является цифровой синтезатор частот, содержащий эталонный генератор, блок задержки, первый блок ПЗУ, первый цифровой накопитель, второй регистр памяти, второй цифровой накопитель, преобразователь кодов, ЦАП, ФНЧ, второй блок ПЗУ и счетчик с предварительной установкой [2].

Однако, известный цифровой синтезатор частот формирует только ЛЧМ-сигнал с заданными свойствами и не позволяет формировать сложные частотно-модулированные сигналы.

Предлагаемый цифровой вычислительный синтезатор формирует сложный частотно-модулированный сигнал, в котором в режиме ЛЧМ можно передавать информацию.

Технический результат – расширение функциональных возможностей ЦВС с возможностью формирования сложных частотно-модулированных сигналов.

Технический результат достигается за счет того, что в цифровой вычислительный синтезатор частотно-модулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок формирования и задержки; первый цифровой накопитель частоты; цифровой накопитель фазы; последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, причем выход ФНЧ является аналоговым выходом цифрового вычислительного синтезатора; последовательно соединенные третий регистр памяти и делитель с переменным коэффициентом деления; выходы блока формирования и задержки подключены с тактовым входам делителя с переменным коэффициентом деления, цифрового накопителя фазы и цифроаналогового преобразователя; выход делителя с переменным коэффициентом деления подключен к тактовому входу первого цифрового накопителя частоты; цифровым входом цифрового вычислительного синтезатора является вход третьего регистра памяти, причем новым является то, что введены два регистра памяти; сумматор; функциональный преобразователь код-синус; причем входы первого и второго регистров памяти являются цифровыми входами ЦВС; выход первого регистра памяти подключен к входу первого цифрового накопителя частоты, а выход второго регистра памяти подключен к входу второго цифрового накопителя частоты; выходы первого и второго цифровых накопителей частоты подключены к соответствующим входам сумматора, выход последнего подсоединен к входу цифрового накопителя фазы; выход цифрового накопителя фазы подключен к входу функционального преобразователя код-синус, выход которого подключен к информационным входам цифроаналогового преобразователя; выход делителя с переменным коэффициентом деления подключен к тактовому входу второго цифрового накопителя частоты.

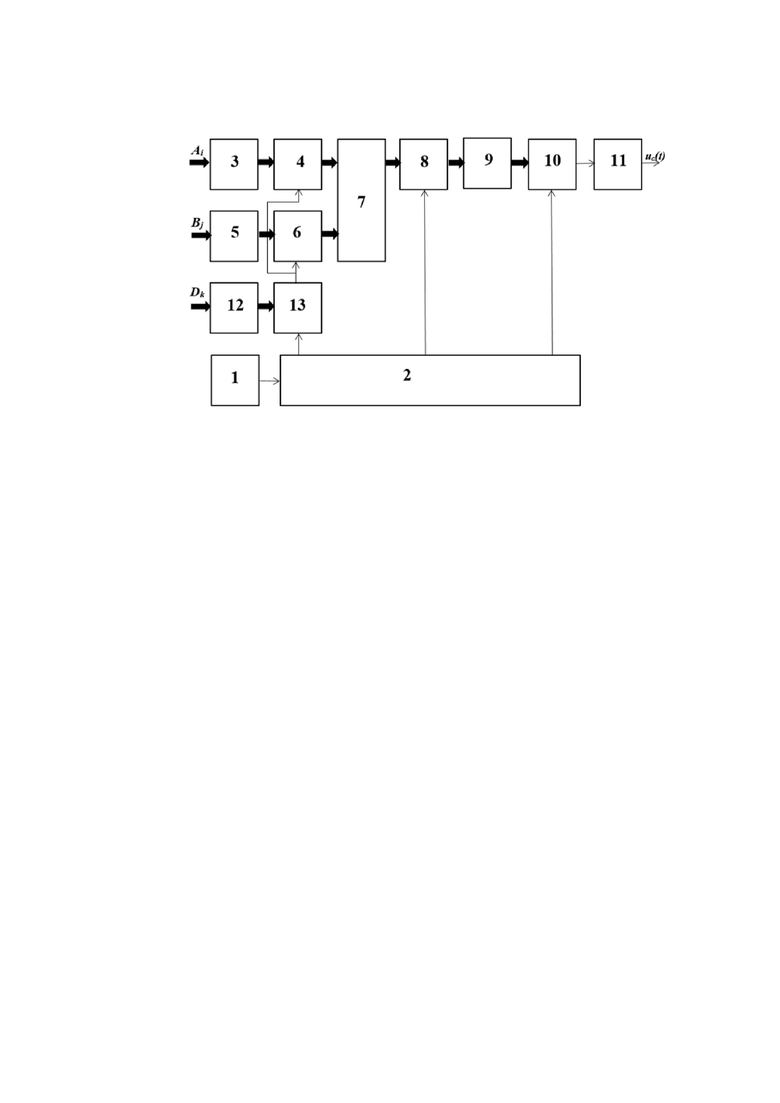

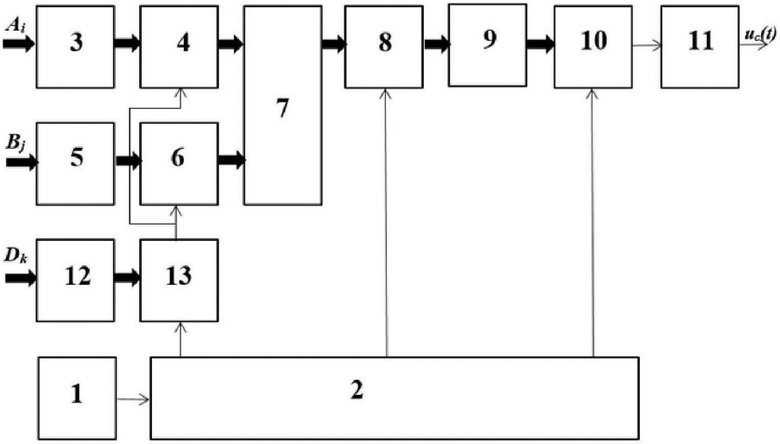

Цифровой вычислительный синтезатор частотно-модулированных сигналов содержит эталонный генератор 1, блок формирования и задержки 2, первый регистр памяти 3, первый цифровой накопитель частоты 4, второй регистр памяти 5, второй цифровой накопитель частоты 6, сумматор 7, цифровой накопитель фазы 8, функциональный преобразователь код-синус 9, цифроаналоговый преобразователь (ЦАП) 10, фильтр низких частот 11, третий регистр памяти 12, делитель с переменным коэффициентом деления 13.

Цифровыми входами цифрового синтезатора являются входы первого, второго и третьего регистров памяти, а его аналоговым выходом – выход ФНЧ.

Изобретение иллюстрируется чертежом.

Цифровой вычислительный синтезатор частотно-модулированных сигналов содержит последовательно соединенные эталонный генератор 1 и блок формирования и задержки 2; последовательно соединенные первый регистр памяти 3, первый цифровой накопитель частоты 4; последовательно соединенные второй регистр памяти 5, второй цифровой накопитель частоты 6, причем выходы первого и второго цифровых накопителей частоты подключены к первому и второму входам сумматора 7; последовательно соединенные сумматор 7, цифровой накопитель фазы 8, функциональный преобразователь код-синус 9, цифроаналоговый преобразователь (ЦАП) 10, фильтр нижних частот (ФНЧ) 11; последовательно соединенные третий регистр памяти 12 и делитель с переменным коэффициентом деления 13, выход которого подсоединен к тактовым входам первого и второго цифровых накопителей частоты; выходы блока формирования и задержки подключены к тактовым входам делителя с переменным коэффициентом деления, цифрового накопителя фазы и ЦАП; цифровыми входами цифрового вычислительного синтезатора являются входы первого, второго и третьего регистров памяти, а его аналоговым выходом – выход ФНЧ.

Цифровой синтезатор работает следующим образом.

Эталонный генератор 1 формирует синусоидальный сигнал опорной частоты, из которого в блоке формирования и задержки 2 формируются последовательности тактовых импульсов формы «меандр», служащие для синхронизации работы основных узлов цифрового синтезатора: делителя с переменным коэффициентом деления, цифрового накопителя фазы и ЦАП.

Пусть в момент t0 на вход первого регистра памяти 3 поступает код начальной частоты Ai, на вход второго регистра памяти 5 – код Bj, а на вход третьего регистра памяти 13 – код Dk.

В момент времени t1 код Ai из первого регистра памяти 3 записывается в первый цифровой накопитель частоты 4, а код Bj – из второго регистра памяти 5 записывается во второй цифровой накопитель частоты 6.

Код Dk из третьего регистра памяти – в делитель с переменным коэффициентом деления.

Далее, с каждым последующим тактовым импульсом, начиная с момента t2, результат суммирования в первом цифровом накопителе частоты 4 будет изменяться по формуле:

S1 = Ai + T, (1)

а результат суммирования во втором цифровом накопителе частоты 6 будет изменяться по формуле:

S2 = Bj + T, (2)

В сумматоре 7 результат описывается следующим выражением:

S3 = Ai + Bj + T (3)

Результат суммирования в цифровом накопителе фазы 8 будет изменяться по формуле:

S4 = (Ci + T)×T/Dk. (4)

где Ci = Ai + Bj

Далее результат суммирования S4 поступает на вход функционального преобразователя 9, где он преобразуется в код sin{(Ci + T)×T/Dk}

Затем код синуса подается на ЦАП 10, где формируется «ступенчатый» частотно-модулированный сигнал, описываемый формулой:

uc(t) = U0 sin [(2π fΣ t + π f ` t2)], (5)

где U0 – амплитуда сигнала,

∆t = T – тактовый интервал,

fΣ – суммарная частота сигнала,

1/Dk = f ` – скорость изменения частоты цифрового вычислительного синтезатора.

Таким образом, первый регистр памяти и первый цифровой накопитель частоты обеспечивают формирование ЛЧМ-сигнала, а второй регистр памяти и второй цифровой накопитель частоты позволяют вводить дополнительную модуляцию частоты для передачи информации.

Третий регистр памяти совместно с делителем с переменным коэффициентом деления обеспечивают необходимую скорость изменения частоты, причем чем меньше значение кода Dk – тем выше скорость перестройки частоты.

Литература

1. Патент РФ № 2204197. МПК H03L 7/18. Цифровой синтезатор частотно- модулированных сигналов/ Рябов И.В., Рябов И.В. Заявл..06.04.2001. Опубл. 10.05.2003. Бюл. № 13. – 5 с.

2. Патент РФ № 2058659. МКИ H03B 19/00. Цифровой синтезатор частот / Рябов И.В., Фищенко П.А. Заявл. 23.09.1993. Опубл. 20.04.1996. Бюл. № 11. – 6 с.

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор с М-образным законом изменения частоты | 2017 |

|

RU2682847C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2566962C1 |

| Цифровой синтезатор фазоманипулированных сигналов | 2019 |

|

RU2701050C1 |

| Цифровой вычислительный синтезатор для адаптивных систем связи с ППРЧ | 2020 |

|

RU2757413C1 |

| Цифровой вычислительный синтезатор с подавлением перекрестных помех | 2019 |

|

RU2726833C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

| Цифровой вычислительный синтезатор двухчастотных сигналов | 2019 |

|

RU2710280C1 |

| Цифровой вычислительный синтезатор двухчастотных частотно-модулированных сигналов | 2024 |

|

RU2826705C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С БЫСТРОЙ ПЕРЕСТРОЙКОЙ ЧАСТОТЫ | 2012 |

|

RU2491710C1 |

Изобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для синтеза сложных частотно-модулированных сигналов и может быть использовано в системах радиосвязи и телекоммуникации. Технический результат – обеспечена возможность при формировании сложных частотно-модулированных сигналов вводить дополнительную модуляцию частоты для передачи информации. Цифровой вычислительный синтезатор частотно-модулированных сигналов содержит эталонный генератор (1), блок формирования и задержки (2), первый регистр памяти (3), первый цифровой накопитель частоты (4), второй регистр памяти (5), второй цифровой накопитель частоты (6), сумматор (7), цифровой накопитель фазы (8), функциональный преобразователь код-синус (9), цифроаналоговый преобразователь (ЦАП) (10), фильтр низких частот (11), третий регистр памяти (12), делитель с переменным коэффициентом деления (13). Цифровыми входами цифрового синтезатора являются входы первого, второго и третьего регистров памяти, а его аналоговым выходом – выход ФНЧ. 1 ил.

Цифровой вычислительный синтезатор (ЦВС) частотно-модулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок формирования и задержки; первый цифровой накопитель частоты; цифровой накопитель фазы; последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, причем выход фильтра нижних частот является аналоговым выходом цифрового вычислительного синтезатора; последовательно соединенные третий регистр памяти и делитель с переменным коэффициентом деления; выходы блока формирования и задержки подключены с тактовым входам делителя с переменным коэффициентом деления, цифрового накопителя фазы и цифроаналогового преобразователя; выход делителя с переменным коэффициентом деления подключен к тактовому входу первого цифрового накопителя частоты; цифровым входом цифрового вычислительного синтезатора является вход третьего регистра памяти, отличающийся тем, что введены два регистра памяти; сумматор; функциональный преобразователь код-синус; причем входы первого и второго регистров памяти являются цифровыми входами ЦВС; выход первого регистра памяти подключен к входу первого цифрового накопителя частоты, а выход второго регистра памяти подключен к входу второго цифрового накопителя частоты; выходы первого и второго цифровых накопителей частоты подключены к соответствующим входам сумматора, выход последнего подсоединен к входу цифрового накопителя фазы; выход цифрового накопителя фазы подключен к входу функционального преобразователя код-синус, выход которого подключен к информационным входам цифроаналогового преобразователя; выход делителя с переменным коэффициентом деления подключен к тактовому входу второго цифрового накопителя частоты.

| Цифровой синтезатор частот с высокой линейностью закона изменения частоты | 2016 |

|

RU2635278C1 |

| Цифровой вычислительный синтезатор с частотной модуляцией | 2016 |

|

RU2628216C1 |

| Цифровой синтезатор с М-образным законом изменения частоты | 2017 |

|

RU2682847C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2566962C1 |

| US 4862109 A1, 29.08.1989 | |||

| US 8384450 B2, 26.02.2013 | |||

| US 4904956 A1, 27.02.1990 | |||

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| RU 2058659 C1, 20.04.1996 | |||

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204197C2 |

Авторы

Даты

2020-04-08—Публикация

2019-09-12—Подача