Изобретение относится к электросвязи и предназначено лля использования в синхронных системах передачи данных.

Цель изобретения - повышение помехоустойчивости цикловой гинхрони- зации.

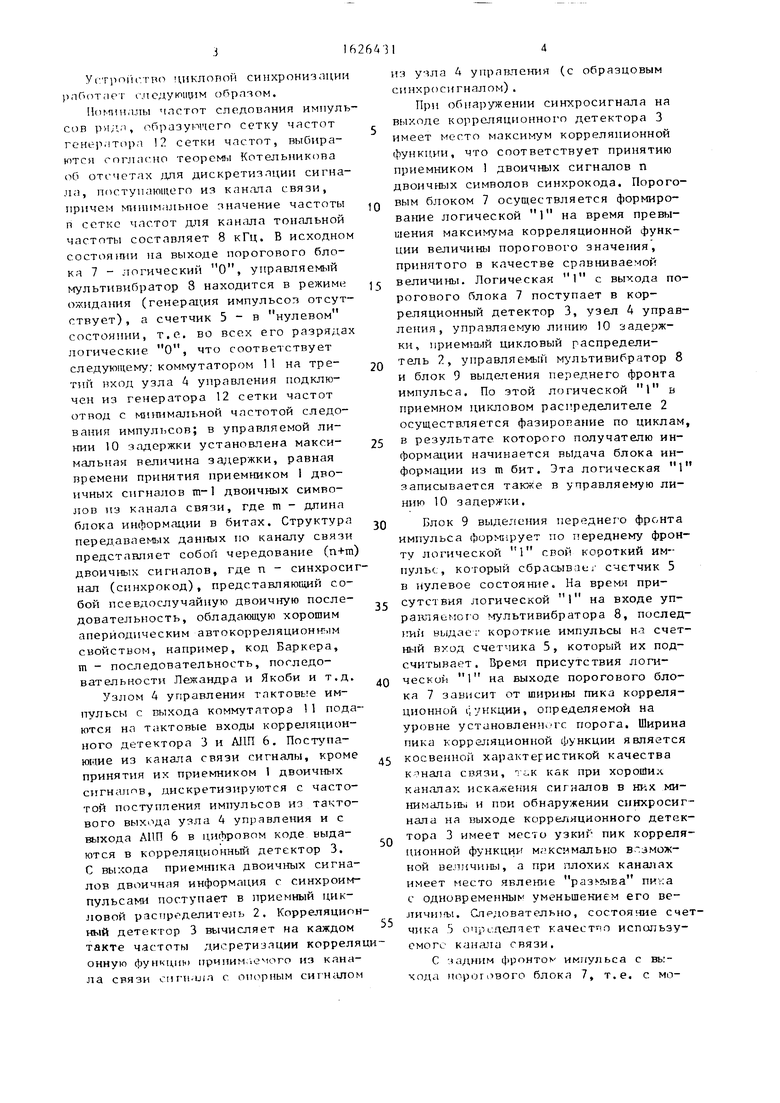

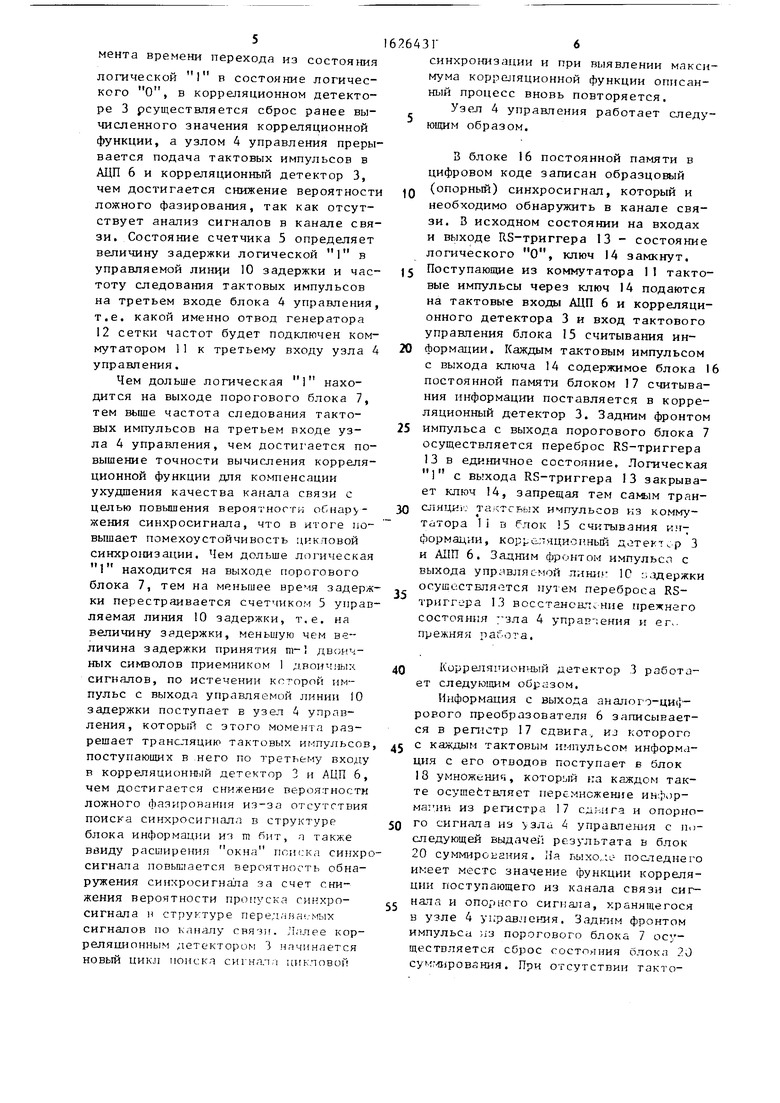

На фиг. 1 представпена структурная электрическая схем i устройства цикловой синхронизации; на Фиг. - схема узла управления; и т Фиг. 3 - схема корреляционного леток гора; на фиг. 4 - схема управляемом шнии задержки .

Устройс1во циклоном синхронизации содержит приемник 1 двоичнн гшналов, присмнли пик p,i( i i еде итель 2, корреляционный детектор 3, узел 4 управления, счетчик 5, аналого-цифровой преобразователь (А1 П) 6, пороговый бло-- 7, управляемый мультивибратор 8, блок 9 выделения переднего фронта импульса, управляемую линию 10 задержки, коммутатор 11 и генератор 12 сетки . V3eji управления содержит RS-трипер 13, ключ 14, блок 15 считывания информации и блок 16 постоянной памяти. Корреляционный детектор содержит регистр 17 сдвига, блок 18 умножения и блок 19 суммирования. %гпраичяемая линия задержки содержит регистр 20 сдвига и коммутатор 21.

О

ю

О5

Јь

00

Устройство цикловой синхронизации работает следующим образом.

Номиналы частот следования импульсов ряда, образующего сетку частот генератора 12 сетки частот, выбираются согласно теоремы Котельникова об отсчетах для дискретизации сигнала, поступающего из канала связи, причем минимальное значение частоты п сетке частот для канала тональной частоты составляет 8 кГц. В исходном состоянии на выходе порогового блока 7 - логический О, управляемый мультивибратор 8 находится в режиме ожидания (генерация импульсов отсутствует) , а счетчик 5 - в нулевом состоянии, т.е. во всех его разрядах логические О, что соответствует следующему; коммутатором 11 на тре- тий вход узла 4 управления подключен из генератора 12 сетки частот отвод с минимальной частотой следования импульсов; в управляемой линии 10 задержки установлена макси- мапьная величина задержки, равная времени принятия приемником 1 двоичных сигналов т-1 двоичных символов из канала связи, где т - длина блока информации в битах. Структура передаваемых данных но каналу связи представляет собой чередование (n+m) двоичных сигналов, где п - синхросигнал (сннхрокод), представляющий собой псевдослучайную двоичную последовательность, обладающую хорошим апериодическим автокорреляционным свойством, например, код Баркера, m - последовательность, последовательности Леэкандра и Якоби и т.д. Узлом 4 управления тактовые импульсы с выхода коммутатора 11 подаются на тактовые входы корреляционного детектора 3 и АПП 6. Поступающие из канала связи сигналы, кроме принятия их приемником 1 двоичных сигналов, дискретиэируготся с частотой поступления импульсов из тактового выхода узла 4 управления и с выхода А11П 6 в цифровом коде выдаются в корреляционный детектор 3. С выхода приемника двоичных сигналов двоичная информация с синхроимпульсами поступает в приемный цикловой распределитель 2. Корреляционный детектор 3 вычисляет на каждом такте частоты дисретизации корреляонную функцию принимаемого из канала связи спгн-ш.ч с опорным сигналом

Q 0 5 5

0

5

0

5

0

из узла 4 управления (с образцовым синхросигналом).

При обнаружении синхросигнала на выходе корреляционного детектора 3 имеет место максимум корреляционной функции, что соответствует принятию приемником 1 двоичных сигналов п двоичных символов синхрокода. Пороговым блоком 7 осуществляется формирование логической на время превышения максимума корреляционной функции величины порогового значения, принятого в качестве сравниваемой величины. Логическая 1 с выхода порогового блока 7 поступает в корреляционный детектор 3, узел 4 управления, управляемую линию 10 задержки, приемный цикловый распределитель 2, управляемый мультивибратор 8 и блок 9 выделения переднего фронта импульса. По этой логической 1 в приемном цикловом распределителе 2 осуществляется фазирование по циклам, в результате которого получателю информации начинается выдача блока информации из m бит. Эта логическая 1 записывается также в управляемую линию 10 задержки.

Блок 9 выделения переднего фронта импульса формирует по переднему фронту логической 1 свой короткий импульс, который сбрасывав/ счетчик 5 в нулевое состояние. На время присутствия логической 1 на входе управляемого мультивибратора 8, последний выдает короткие импульсы на счетный вход счетчика 5, который их подсчитывает. Время присутствия лото- ческой 1 на выходе порогового блока 7 зависит от ширины пика корреляционной функции, определяемой на уровне установленнчтс порога. Ширина пика корреляционной функции является косвенной характеристикой качества канала связи, пч.к как при хороших каналах искажения сигналов в них минимальны и пои обнаружении синхросигнала на выходе корреляционного детектора 3 имеет место узкиг пик корреляционной функции максимально возможной величины, а при плохих каналах имеет место явление размыва с одновременным уменьшением его ве- личи} ы. Следовательно, состояние счетчика 5 определяет качество используемо гс канала связи.

С задним фронтом импульса с выхода порогового блока 7, т.е. с момента времени перехода из состояния

логической I в состояние логического О, в корреляционном детекторе 3 рсуществляется сброс ранее вычисленного значения корреляционной функции, а узлом 4 управления прерывается подача тактовых импульсов в АЦП 6 и корреляционный детектор 3, чем достигается снижение вероятности ложного фазирования, так как отсутствует анализ сигналов в канале связи. Состояние счетчика 5 определяет величину задержки логической 1 в управляемой линией 10 задержки и частоту следования тактовых импульсов на третьем входе блока 4 управления, т.е. какой именно отвод генератора 12 сетки частот будет подключен коммутатором 1 1 к третьему входу узла 4 управления.

Чем дольше логическая находится на выходе порогового блока 7, тем выше частота следования тактовых импульсов на третьем входе узла 4 управления, чем достигается повышение точности вычисления корреляционной функции для компенсации ухудшения качества канала связи с целью повышения вероятности обнар - жения синхросигнала, что в итоге повышает помехоустойчивость циктовой синхронизации. Чем дольше логическая 1 находится на выходе порогового блока 7, тем на меньшее время задержки перестраивается счетчиком 5 управляемая линия 10 задержки, т.е. на величину задержки, меньшую чем величина задержки принятия т-1 двоичных символов приемником 1 двоичных сигналов, по истечении к скорой импульс с выхода управляемой линии 10 задержки поступает в узел 4 управления, который с этого момента разрешает трансляцию тактовых импульсов поступающих в него по третьему входу в корреляционный детектор 3 и АЦП 6, чем достигается снижение вероятности ложного фазирования из-за отсутствия поиска синхросигнала в структуре блока информации ит m бит, п также ввиду расширения окна поиска синхросигнала повышается вероятность обнаружения синхросигнала за счет снижения вероятности пропуска синхросигнала и структуре передана мых сигналов по каналу связи. Л. лее корреляционным детектором 3 начинается новый цикл поиска cm нал i циьповой

2643 Г

синхронизации и при выявлении максимума корреляционной функции описанный процесс вновь повторяется.

Узел 4 управления работает следующим образом.

В блоке 16 постоянной памяти в цифровом коде записан образцовый

,Q (опорный) синхросигнал, который и необходимо обнаружить в канале связи. 3 исходном состоянии на входах и выходе RS-триггера 13 - состояние логического О, ключ 14 замкнут.

15 Поступающие из коммутатора 11 тактовые импульсы через ключ 14 подаются на тактовые входы АЦП 6 и корреляционного детектора 3 и вход тактового управления блока 15 считывания ин20 формации. Каждым тактовым импульсом с выхода ключа 14 содержимое блока 16 постоянной памяти блоком 17 считывания информации поставляется в корреляционный детектор 3. Задним фронтом

25 импульса с выхода порогового блока 7 осуществляется переброс RS-триггера 13 в единичное состояние. Логическая 1 с выхода RS-триггера 13 закрывает ключ 14, запрещая тем самым тран30 СЛЯЦИ1. та -:тсБо х импульсов из комму- титора П в блок 5 считывания информации, корреляционный дотект р 3 и А11П 6. Задним фронтом импульсл с выхода управляемой линж- 1C :.лдержки осуществляется путем переброса RS- тригг ра 1.3 восстанови ние прежнего состояния 4 управления и ег прежняя paf Ora.

35

Корреляционный детектор 3 работает следующим образом.

Информация с выхода аналого-цифрового преобразователя 6 записывается в регистр 17 сдвига, HJ которого

с каждым тактовым импульсом информация с его отводов поступает в блок 13 умножения, который на каждом такте осушестатяет перемножение информации из регистра 17 сдвига и опорного сигнала из злч 4 управления с последующей выдачей результата в блок 20 суммирования. Ня ьыхоле последнего имеет месте значение функции корреляции поступающего из канала связи сигнала и опорного сигнала, хранящегося в узле 4 управления. Задним фронтом импульса из порогового блока 7 осуществляется сброс состояния блока 0 суммирования. При отсутствии тактоних импульсов коррепяционный детектор 3 не работает.

Управляемая линия 10 задержки работает следующим образом.

Импульс (логическая 1) с выходя порогового блока 7 записывается в регистр 20 сдвига, в котором продвигается под воздействием собственных тактовых импульсов. Если на входе управления коммутатора 2 - логические О, то коммутатор 21 последний отвод регистра 20 сдвига проключает на второй вход узла управления 4. Если состояние счетчика 5 отлично от нулевого, то в соответствии с состоянием счетчика 5 коммутатор 21 проключает из К последних отводов регистра 20 сдвига соответствуют™ oi вод на агорой вход узла 4 управления. Максимальное время задержки,, кото- рос определяет длину регистра 20 сдвига, составляет величину, равную времени приема приемником 1 двоичных сигналов т-1 двоичных символов из канала связи.

Частота следования импульсов с выхода управляемого мультивибратора 8 выбирается из условия, что ттпи i тс- альном выдслешш синхросигнал ч , когда функция корреляции имеет максимально возможный максимум, управляемый мультивибратор 8 не должен успеть сформировать передний фронт сюего короткого импульса.

Формул

изобретения

1 . Устройство цикловсй синчрогн- К1ции, содержащее счсгчик и носле- ловатегп но соединенные приемник двоично о спп. -ла, их чд которого является входом устройства, и мрирмный цикловой распределитель, впхоп которого явля -тся вытсоцом устно I ва , а также корреляционный дг ьктор, к первым информационным входам которого п дмт оч°на группа выходов узлг управления, отличающееся тем, что. с целью повышения помехе- устойчивости цикловой синхронизации введены поротовый блок, украпля мнй мультивибратор, управляемая линия задержки, блок выделения передне)о фронта импульса, последовательно соединенные генератор сетки частот, а также аналого-цифровой преобразователь (АЦП), вход кочорото :оедиш н с входом приемника г,ти мнх .я-лов, а выходы ЛИП соединены с вторыми информационными входами корреляционного детектора, к тактовому входу которого и тактовому входу АЦП подключен тактовый выход узла управления, к первому входу которого, а также к входам управляемой линии задержки, управляемого мультивибра- тора, блока выделения переднего фронта импульса, входу управления циклового распределителя и входу сброса корреляционного детектора подключен выход порогового блока, к входу ко

юр о го подключен выход корреляционного детектора, при этом к второму и трет ьему входам узла управления подключены выходы соответственно управляемой линии задержки и коммутатора,

входам управления которого и входам управления управляемой линии задержки подключены выходы счетчика, к счетному входу и входу сброса которого подключены выходы соответственно управляемого мультивибратора и

Глюка выделения переднего фронта импульса,

2. Устройство по п. 1 , о т jj и - чающееся , что узел управ0 лении выполнен в виде последовательно соединенных RS-тритгера и ключа, а также последовательно соединенных блока постоянной памяти и блока счи- т-ыг гния информации, к входу тактово5

0

о - травления которого подключен зыхгп К...Т, , при этом S и Е-входп RS- тилггера и второй вход ключа является -.ответственно первым, вторым и Tpeib-им входами узла управления, ,-j тактовым выходом и группой выходов которого являются выход ключа и выходы блока считывания информации.

3. Устройство по п. 1, о т л и - - . 1 ю ш е е с я тем, ч. о корреляционный детектор выполнен в виде гос- лг,JuaTenbHO соединенных -.егистра сдв 1 га, блока умножения и блока суммирования, выход которого является ,,м корреляционного детектора черимми и вторы,пл инфотмаипинными входами которого являются соответ- ; гвенно вторые ВУОДЫ блока, умножения н мход сдвига, тактовый вхол которого сссдинен с тактовым входом блока умножения и является тактовым входом корреляционного де- тектопа входом сброса которого явля- РПЧ вход сброса блок-, .суммирования.

4. Устройство по п. отличающееся тем, что управляемая линия задержки выполнена в виде регистра сдвига, К последних отводов кото- , рого соединены с входами коммутатора,

входы управления которого являются входами управления управляемой линии задержки, входом и выходом которой являются соответственно вход регистра сдвига и выход коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2002 |

|

RU2229200C2 |

| СИСТЕМА ПЕРЕДАЧИ И ОБРАБОТКИ СИГНАЛОВ О СОСТОЯНИИ ОБЪЕКТОВ | 1994 |

|

RU2087036C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ЦИФРОВЫХ ПОТОКОВ | 1992 |

|

RU2054809C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2000 |

|

RU2168867C1 |

| СИСТЕМА ДУПЛЕКСНОЙ ВЫСОКОСКОРОСТНОЙ КОРОТКОВОЛНОВОЙ РАДИОСВЯЗИ | 2013 |

|

RU2553091C2 |

Изобретение относится к электросвязи. Цель изобретении - повышение помехоустойчивое ги цнклоыи син ронь- зации. содержит приемник 1 двоичных сигналов, приемный цикловой распределитель 2, корреляционный детектор 3, узел 4 управлгния, счетчик 5, АЦП 6, пороговый блок 7, управляемый мультивибратор Я, блок 9 выделения переднего фронта импульса, управляемую линию 10 задержки, коммутатор 11 и г-р 12 сетки частот. 3 данном устр-ве чем дольше логическая 1 находится на выходе порогового блока 7, тем выше частота следования тактовых импульсов на третьем входе узла 4 управления. Этим достигается повышение точности вычисления корреляционной Функции для компенсации ухудшени. качест ва канала связи с целью повышения вероятности обнаружения синхросигнала, что г итоге повышает поме; v устойчивое i цикловой синхронизации. Устр-ьо по пп. 2-4 ф-лы отличается выполньнием узла 4, детектора 3 и линии Ю, даны их ил. 3 т.п. ф-лы, 4 ил. SS 1сл

Фиъ.1

Фиг. 2

f

Фаг. 3

1

го

Риг. Ч

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-02-07—Публикация

1989-04-11—Подача