Изобретение относится к электросвязи и может быть использовано в приемных устройствах синхронизации по циклам систем передачи дискретных сообщений.

В работе [1] на основе критерия максимума апостериорной вероятности получено аналитическое выражение, описывающее оптимальный алгоритм поиска фазы циклового синхросигнала (ЦС) или временного положения ЦС среди информационных символов двоичного потока. В отличии от подобных выражений, полученных в работах [2] и [3], здесь учитывается зависимость необходимой длительности Q интервала анализа принимаемой двоичной последовательности при поиске ЦС, измеряемой в цикловых интервалах (НИ), от параметров ЦС (М, N), отношения апостериорных вероятностей альтернативных гипотез (К) правильного и ложного обнаружения ЦС, определяющего вероятность правильного обнаружения ЦС, вероятности правильного приема синхросимвола (Рп), а также вероятности появления ложного синхросимвола (Рл) на информационной позиции цикла.

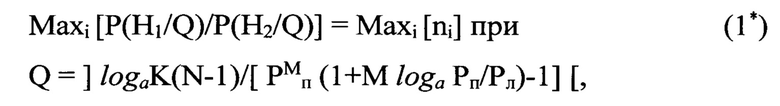

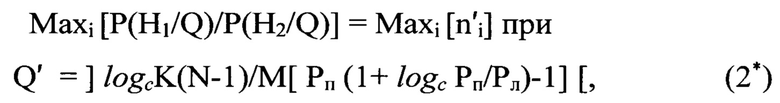

В работе [4] определен минимальный объем анализируемых данных двоичной последовательности Qmin ЦИ при оптимальном алгоритме поиска ЦС, меньше которого не может приниматься решение о временном положении ЦС. При этом определен необходимый объем анализируемых данных (отрезок двоичной последовательности длительностью Q ЦИ), по окончании которого можно принимать решение о временном положении ЦС - фазы ЦС, с требуемой вероятностью правильного обнаружения ЦС, определяемой величиной К. Таким образом, оптимальный алгоритм поиска ЦС, полученный в работе [1] при условии выбора длительности интервала анализа Q=f(K,M,N,Pп,Pл) ЦИ, в конце которого принимают решение о временном положении ЦС, и определяемой по полученной в работе [4] формуле, сокращенно можно записать в виде

где символ] [означает округление до ближайшего целого числа.

Здесь К=P(H1/Q)/P(H2/Q) - отношение апостериорных вероятностей истинности альтернативных гипотез H1 и Н2, где гипотеза Hi означает, что анализируемая i-ая позиция цикла соответствует фазе ЦС; ni - число зарегистрированных откликов - двоичных символов «1», опознавателя синхросигнала на i-ой позиции цикла в течение длительности Q цикловых интервалов анализа; N - число позиций в цикле или длительность цикла - циклового интервала (НИ), в двоичных символах; М - число синхросимволов в сосредоточенной или распределенной по циклу синхрогруппе, регулярное повторение которой через N символов представляет собой ЦС; Рп - вероятность правильного приема синхросимвола (Рп=1-Рос, Рос - вероятность ошибочного приема двоичного символа или вероятность ошибки любого символа принимаемого двоичного сигнала - синхросимвола или информационного символа, кроме того, здесь предполагается, что Рп>0,5); Рл - вероятность появления ложного синхросимвола в группе из М анализируемых опознавателем синхросигнала информационных символов (в большинстве случаев можно считать, что Рл≈0,5); a=(1-РМл)/(1-РМп).

Согласно полученному в работах [1] и [4] оптимальному алгоритму (1*) поиска ЦС принимаемую двоичную последовательность, содержащую цикловой синхросигнал в виде сосредоточенной или распределенной по циклу синхрогруппы из М синхросимволов, периодически повторяемой через N двоичных символов, подают на вход опознавателя синхросигнала (дешифратора синхрогруппы), на выходе которого анализируют двоичную последовательность символов, в которой символ «1» - отклик на правильно принятую синхрогруппу или ложную сихрогруппу из М информационных символов двоичной последовательности, символ «0» - отклик на искаженную синхрогруппу или ложную искаженную синхрогруппу. При этом на каждой из N позиций цикла (соответствующей отклику опознавателя синхросигнала) производят суммирование символов «1» от цикла к циклу в течение следования Q ЦИ анализа, определяемого формулой алгоритма (1*). По окончании Q ЦИ анализа определяют позицию цикла, на которой накоплено откликов больше, чем на любой другой из N-1 позиций цикла, которую считают позицией синхронизма и которая является истинной позицией синхронизма с заданной вероятностью правильного обнаружения ЦС, определяемой величиной К.

Данный алгоритм поиска фазы ЦС можно выполнить различными способами, реализуемых соответствующими устройствами цикловой синхроизации, отличающихся друг от друга степенью соответствия оптимальному алгоритму поиска ЦС. Например, вариант структурой схемы устройства цикловой синхронизации, реализующий один из способов поиска фазы ЦС в соответствии с оптимальным алгоритмом поиска ЦС (1*) при работе в прогнозируемых условиях связи, приведен в [1], который можно изложить в следующем виде.

Способ цикловой синхронизации, в соответствии с которым двоичную последовательность, содержащую цикловой синхросигнал в виде сосредоточенной или распределенной по циклу синхрогруппы из М синхросимволов, периодически повторяемую через N двоичных символов, подают на информационный вход дешифратора синхрогруппы, с выхода которого последовательность откликов - двоичная последовательность символов «1» и «0», подают на первые входы N элементов И, на вторые входы которых с распределителя импульсов, тактовый вход которого объединен с соответствующими входами дешифратора синхрогруппы и счетчика циклов, подают задержанные друг относительно друга на один тактовый интервал соответствующие последовательности цикловых импульсов, при этом формируемые на выходах элементов И последовательности Q1,…,QN одиночных символов «1» подают в блок N счетчиков для подсчета в каждой последовательности количества одиночных символов «1», при этом по окончании счета Q циклов счетчиком циклов на его выходе формируют импульс, с помощью которого результат счета в двоичном коде каждого счетчика блока N счетчиков записывают в решающий узел, в котором производят выбора номера того счетчика в котором накоплено символов «1» больше, чем в любой другом счетчике блока N счетчиков и формируют управляющий сигнал для коммутатора, который обеспечивает подключение на его выход соответствующей последовательности цикловых импульсов, являющейся последовательностью синхронизма, после чего счетчик циклов и все счетчики блока N счетчиков обнуляют и процедуру поиска ЦС повторяют.

Недостатками такого способа поиска ЦС, соответствующего оптимальному алгоритму (1*) поиска ЦС при прогнозируемых условиях связи является:

1. При поиске временного положения ЦС в качестве первичного источника синхроинформации используют отклики дешифратора синхрогруппы, который часто называют опознавателем синхросигнала. В соответствии оптимальным алгоритмом поиска ЦС такие отклики на каждой позиции цикла (соответствующие позициям цикла) суммируют от цикла к циклу для дальнейшего выбора позиции синхронизма. Однако такой дешифратор синхрогруппы реагирует на истинную или ложную синхрогруппу (выдает на его выходе отклик - символ «1») только тогда, когда все М синхросимволов синхрогруппы приняты правильно или происходит ложный набор М информационых символов подобных синхросимволам сихрогруппы, и не реагирует (на выходе - символ «0»), когда хотя бы один синхросимвол истинной синхрогруппы искажен (принят ошибочно) или, когда набор ложной синхрогруппы из информационных символов не происходит, т.е. дешифратор сихрогруппы реагирует на совокупную синхроинформацию от всех М правильно принятых синхросимволов и не учитывает синхроинформацию, содержащуюся в каждом из М синхросимволов синхрогруппы. Однако неполное использование синхроинформации, содержащейся в каждом синхросимволе, приводит к увеличению времени накопления требуемого количества синхроинформации для принятия решения о выборе позиции синхронизма, а соответственно и к увеличению времени поиска ЦС, особенно при плохих условиях связи. Поэтому для сокращения времени поиска ЦС целесообразно накапливать от цикла к циклу на каждой позиции цикла не количество откликов дешифратора синхрогруппы на правильно принятые синхрогруппы и ложные синхрогруппы, а количество символов подобных синхросимволам синхрогруппы на каждой позиции цикла[5].

2. Недостатком такого способа является и то, что он предназначен для работы в канале с постоянными параметрами, когда длительность интервала анализа Q можно заранее определить с учетом прогнозируемых условий связи. При работе в канале с замираниями сигнала такой способ поиска ЦС будет приводить к увеличению вероятности ложного обнаружения ЦС при плохих условиях связи и к увеличению времени поиска ЦС при улучшении условий связи.

Из известных способов цикловой синхронизации наиболее близким по сущности решаемых задач в соответствии с оптимальным алгоритмом поиска ЦС (1*) и большинству совпадающих существенных признаков является способ цикловой синхронизации для сигналов с сосредоточенной или распределенной по циклу синхрогруппой при работе в канале с переменными параметрами, в соответствии с которым двоичная последовательность, содержащая цикловой синхросигнал в виде сосредоточенной или распределенной по циклу синхрогруппы, подают на информационный вход опознавателя синхросигнала, выходной сигнал которого с одноразрядного выхода одновременно подают на первый вход элемента запрета, последовательно соединенного со счетчиком искаженных синхросимволов и блоком выбора порога, и на вход младшего разряда первого входа сумматора, выходной сигнал которого в параллельном n-разрядном двоичном коде подают на сигнальный вход блока регистров сдвига, основной и дополнительный выходы которого подключают соответственно к второму входу сумматора и сигнальному входу решающего узла, тактовый вход которого объединяют с соответствующими входами опознавателя синхросигнала, блока регистров сдвига и формирователя цикловых импульсов, при этом блок регистров сдвига включает в себя n N-разрядных регистров сдвига, у которых раздельно объединяют тактовые входы и входы сброса, которые являются соответственно тактовым входом и входом сброса блока регистров сдвига, а входные и выходные разряды, а также выходы входных разрядов всех n N-разрядных регистров сдвига блока регистров сдвига являются соответственно сигнальным входом, выходом и дополнительным выходом блока регистров сдвига, причем при поступлении каждого тактового импульса на тактовый вход блока регистров сдвига во входные разряды n N-разрядных регистров сдвига этого блока перезаписывают с выхода сумматора в параллельном n-разрядном двоичном коде, результат суммирования символов «1» на соответствующей одной из N позиций цикла с соответствующим порядковым номером i=1,2,…,N, кроме того, последовательность цикловых импульсов с выхода формирователя цикловых импульсов одновременно подают на второй вход элемента запрета и вход счетчика циклов, с помощью которого производят счет S цикловых импульсов после чего импульсный сигнал с его выхода одновременно подают на вход управления блока выбора порога и вход сброса счетчика искаженных синхросигналов, с помощью которого за S циклов подсчитывают количество D одиночных символов «1» с выхода элемента запрета, соответствующих искаженным синхрогруппам, в виде двоичного числа в параллельном коде, которое с выхода счетчика искаженных синхросигналов перезаписывают в блок выбора порога, а счетчики обнуляют для подсчета следующего количества искаженных синхросимволов в течение следующих S циклов, при этом в блоке выбора порога на основе текущей оценки вероятности ошибки синхросимвола в виде Рoc≈D/S, величина которой находится в пределах соответствующего одного из Z интервалов допустимых значений величины Рос, формируют соответствующее пороговое число Gz в параллельном двоичном коде с соответствующим порядковым номером градации порогового числа z=1,2,…,Z, которое с выходе блока выбора порога подают на управляющий вход решающего узла, сигнальным входом которого является первый вход блока вычитания, объединенный с первым входом первого блока сравнения и входом данных блока памяти, выход которого объединен с вторыми входами блока вычитания и первого блока сравнения, в котором производят сравнение двух чисел на его входах при этом, если в соответствующем тактовом интервале число на первом входе первого блока сравнения превышает число на втором его входе, то на выходе первого блока сравнения формируется импульсный сигнал, который подают на вход управления блока памяти, обеспечивая перезапись в него наибольшего числа, поступающего на его вход данных и первые входы первого блока сравнения и блока вычитания, с выхода которого двоичные числа, следующие с частотой тактовых импульсов и соответствующие разности чисел между наибольшим числом с выхода блока памяти и каждым числом, поступающим на первый вход блока вычитания, подают на первый вход второго блока сравнения, в котором двоичные числа, соответствующие разности чисел, сравнивают с пороговым числом, поступающим на второй его вход, являющимся управляющим входом решающего узла, при этом логический уровень с выхода второго блока сравнения подают на вход сброса счетчика сравнения, тактовый вход которого является тактовым входом решающего узла, при этом, если на одной из N позиций цикла результат суммирования символов «1» превысит результат суммирования символов «1» на любой другой позиции цикла не менее чем на пороговое число, то на вход сброса счетчика сравнения подают разрешающий «нулевой» потенциал, и с помощью счетчика сравнения производят счет N-1 тактовых импульсов и на его выходе, являющимся выходом решающего узла, формируют импульсный сигнал синхронизации, который подают на входы сброса блока памяти, блока регистров сдвига и формирователя цикловых импульсов, обнуляя блок памяти блок и регистров сдвига, а также подтверждая или корректируя фазу выходной последовательности цикловых импульсов формирователя цикловых импульсов [6].

Следует отметить следующие недостатки этого способа: 1. Не использованы возможности по сокращению времени поиска ЦС или времени вхождения в синхронизм из-за того, что при поиске временного положения ЦС в качестве первичного источника синхроинформации, которая подвергается обработке, используются отклики опознавателя синхросигнала, а не синхроинформация от каждого синхросимвола каждой синхрогруппы [5].

При суммировании символов подобных синхросимволам синхрогруппы, как рекомендовано в [5], оптимальный алгоритм поиска ЦС (1*) требует уточнения в части длительности Q интервала анализа в цикловых интервалов для достижения требуемого значения отношения апостериорных вероятностей К=P(H1/Q)/P(H2/Q). С учетом полученных в работе [4] аналитических выражений, сокращенно оптимальный алгоритм поиска ЦС в данном случае можно записать в виде

где n'i - число символов подобных синхросимволам синхрогруппы на i-й позиции цикла, каждый из которых регистрируют как синхросимвол «1», в течение длительности Q' цикловых интервалов анализа, в течение которых передано MQ' сихросимволов; с=(1-Рл)/(1-Рп).

При работе в соответствии с алгоритмом (2*) с посимвольной обработкой символов подобных синхросимволам синхрогруппы требуется привести в соответствие и способ цикловой синхронизации максимально приближенный к этому алгоритму.

2. Поскольку согласно данному способу все операции проводят с использованием откликов опознавателя синхросигнала, в том числе, оценки вероятности ошибки синхросимвола Рос, (что требуется в соответствии с оптимальным алгоритмом поиска ЦС (1*)), косвенным экспериментальным способом - путем подсчета количества D искаженных синхргрупп за S циклов (S - общее число переданных синхрогрупп) и определения вероятности (частости) ошибки синхрогруппы Росг=D/S. Такой способ оценки величины Рос≈Росг является не точным, особенно при увеличении количества М синхросимволов в синхрогруппе, что приводит к соответствующей погрешности при выборе длительности интервала анализа Qz, определяемого пороговым числом Gz≈f(Pосг), т.е. Qz≈F(Gz)≈F[f(Pосг)] и нарушению работы согласно алгоритму (1*).

Однако при суммировании символов подобным синхросимволам синхрогруппы и работе в соответствии алгоритмом (2*), появляется возможность более точного определения Рос=D'/MS', где D' - количество искаженных синхросимволов при MS' переданных синхросимволов. При этом расчет длительности Q'z интервала анализа следует производить по другой формуле, соответствующей алгоритму (2*), соответственно и расчет порогового значения G'z=f(Pос) принимает другую величину, которую более точно можно рассчитать, чтобы получить искомую длительность Q'z=F(G'z)=F[f(Poc)] интервала анализа.

3. Поскольку максимальная сумма подсчета откликов опознавателя синхросигнала в параллельном двоичном коде на каждой позиции цикла ограничена разрядностью n параллельных ячеек с идентичными порядковыми номерами разрядов N-разрядных регистров сдвига блока регистров сдвига, то возможны переполнения отдельных n-разрядных чисел, записываемых в параллельные ячейки блока регистров сдвига, что равнозначно обнулению результатов счета откликов в этих ячейках. Такие случаи могут происходить, например, при пропадании сигнала или сравнительно длительном воздействии мощных помех в районе приема сигнала. После восстановления канала связи это может приводить к увеличению времени поиска ЦС, если имел место сбой синхронизма по циклам и увеличению вероятности ложного срабатывания решающего узла.

Этот недостаток будет проявляться и при суммировании символов подобных синхросимволам синхрогруппы при работе согласно алгоритму (2*).

Задачами, на решение которых направлено настоящее изобретение - способ цикловой синхронизации при приеме сигналов с сосредоточенной или распределенной по циклу синхрогруппой, являются:

1. Уменьшение времени поиска ЦС или времени восстановления синхронизма по циклам путем суммирования на каждой позиции цикла не откликов опознавателя синхросигнала, а суммирование всех символов подобных синхросимволам синхрогруппы, используя полную синхроинформацию о каждом синхросимволе синхрогруппы истинным и ложным. При этом поиск временного положения ЦС должен производиться способом, соответствующим оптимальному алгоритму (2*), в соответствии с которым будет достигаться сокращение времени поиска ЦС по отношению с алгоритмом (1*), без ухудшения вероятности ложного обнаружения ЦС.

2. Повышение точности оценки вероятности ошибки синхросимвола Рос экспериментальным способом путем подсчета не количества D искаженных откликов опознавателя синхросигнала в течение S циклов, а количества D' искаженных синхросимволов синхрогрупп в течение S' циклов. В результате более точно можно оценить экспериментальным способом вероятность ошибки синхросимвола по формуле Рос=D'/MS', как требуется при оптимальном алгоритме поиска ЦС (1*) или (2*), а соответственно и выбирать пороговые числа на основе более точного расчета интервала анализа для работы в канале с переменными параметрами связи с обеспечением требуемой помехоустойчивости и исключения ложных обнаружений ЦС в интервалах времени между соседними сбоями синхронизма по циклам.

3. Уменьшение времени поиска ЦС, если имел место сбой синхронизма по циклам, и уменьшение вероятности ложного срабатывания решающего узла после восстановления канала связи при пропадании сигнала или сравнительно длительном воздействии мощных помех в районе приема сигнала за счет обнуления блока памяти решающего узла и блока регистров сдвига при достижении любого результата суммирования на любой из N позиций цикла допустимого значения.

Решение поставленных задач достигается тем, что в известном способе цикловой синхронизации для сигналов с сосредоточенной или распределенной по циклу синхрогруппой, в соответствии с которым двоичную последовательность, содержащую цикловой синхросигнал в виде сосредоточенной или распределенной по циклу синхрогруппы, подают на информационный вход опознавателя синхросигнала, выходной сигнал которого с одноразрядного выхода с порядковым номером r=1 подают на вход младшего разряда с порядковым номером r=1 первого входа сумматора, выходной сигнал которого в параллельном n-разрядном двоичном коде подают на сигнальный вход блока регистров сдвига, основной и дополнительный выходы которого подключают соответственно к второму входу сумматора и сигнальному входу решающего узла, тактовый вход которого объединяют с соответствующими входами опознавателя синхросигнала, блока регистров сдвига и формирователя цикловых импульсов, при этом блок регистров сдвига включает в себя n N-разрядных регистров сдвига, у которых раздельно объединяют тактовые входы и входы сброса, которые являются соответственно тактовым входом и входом сброса блока регистров сдвига, а входные и выходные разряды, а также выходы входных разрядов всех n N-разрядных регистров сдвига блока регистров сдвига являются соответственно сигнальным входом, выходом и дополнительным выходом блока регистров сдвига, причем при поступлении каждого тактового импульса на тактовый вход блока регистров сдвига во входные разряды n N-разрядных регистров сдвига этого блока перезаписывают с выхода сумматора в параллельном n-разрядном двоичном коде, результат суммирования символов «1» на соответствующей одной из N позиций цикла с соответствующим порядковым номером i=1, 2,…, N, кроме того, результаты суммирования символов на каждой из N позиций цикла с дополнительного выхода блока регистров сдвига подают последовательно во времени с частотой следования тактовых импульсов на сигнальный вход решающего узла, сигнальным входом которого является первый вход блока вычитания, объединенный с первым входом первого блока сравнения и входом данных блока памяти, выход которого объединен с вторыми входами блока вычитания и первого блока сравнения, в котором производят сравнение двух чисел на его входах при этом, если в соответствующем тактовом интервале число на первом входе первого блока сравнения превышает число на втором его входе, то на выходе первого блока сравнения формируется импульсный сигнал, который подают на вход управления блока памяти, обеспечивая перезапись в него наибольшего числа, поступающего на его вход данных и первые входы первого блока сравнения и блока вычитания, с выхода которого двоичные числа, следующие с частотой тактовых импульсов и соответствующие разности чисел между наибольшим числом с выхода блока памяти и каждым числом, поступающим на первый вход блока вычитания, подают на первый вход второго блока сравнения, в котором двоичные числа, соответствущие разности чисел, сравнивают с пороговым числом, поступающим на второй его вход, являющимся управляющим входом решающего узла, с выхода блока выбора порога, при этом логический уровень с выхода второго блока сравнения подают на вход сброса счетчика сравнения, тактовый вход которого является тактовым входом решающего узла, при этом, если на одной из N позиций цикла результат суммирования символов «1» превысит результат суммирования символов «1» на любой другой позиции цикла не менее чем на пороговое число, то на вход сброса счетчика сравнения подают разрешающий «нулевой» потенциал, и с помощью счетчика сравнения производят счет N-1 тактовых импульсов и на его выходе, являющимся выходом решающего узла, формируется импульсный сигнал синхронизации, который подают на вход сброса блока формирователя цикловых импульсов, подтверждая или корректируя фазу выходной последовательности цикловых импульсов с выхода формирователя цикловых импульсов, которую подают на вход счетчика циклов и на первый вход элемента запрета с порядковым номером m=1, дополнительно вводят R-1 одноразрядных выходов опознавателя синхросигнала с порядковыми номерами r=2, 3…, R, и М-1 элементов запрета с порядковыми номерами m=2, 3,…, М, где R - минимально необходимое число одноразрядных выходов или число разрядов R-разрядного выхода опознавателя синхросигнала, которое выбирают из условия R=]log2M[, где][ - округление до ближайшего наибольшего целого числа, М - число синхросимволов в сосредоточенной или распределенной по циклу синхрогруппе двоичного сигнала на информационном входе опознавателя синхросигнала, следующих во времени друг за другом с условными порядковыми номерами m=1, 2, …, М, и длительностью цикла или периодом повторения синхрогрупп среди информационных символов равным Тц=N двоичных символов, причем дополнительные разрядные выходы опознавателя синхросигнала с порядковыми номерами r=2, 3, …, R подключают к соответствующим разрядным входам с таким же порядковыми номерами r=2, 3, …, R первого входа сумматора, первые входы М-1 элементов запрета с порядковыми номерами m=2, 3, …, М объединяют и подключают дополнительно к первому входу элемента запрета с порядковым номером m=1, а вторые входы М элементов запрета с порядковыми номерами m=1, 2, …, М подключают к соответствующим дополнительным выходам опознавателя синхросигнала с такими же порядковыми номерами m=1, 2, …, М, кроме того, дополнительно вводят сумматор искаженных синхросимволов синхрогруппы, накапливающий сумматор, второй блок памяти, первый элемент задержки, второй элемент задержки, дешифратор переполнения и элемент ИЛИ.

В режиме синхронизма по циклам каждый цикловой импульс с выхода формирователя цикловых импульсов должен совпадать во времени с соответствующими М синхросимволами каждой преобразованной синхрогруппы, поступающих одновременно с М дополнительных выходов опознавателя синхросигнала с порядковыми номерами m=1,2,…,М, при этом, если во входном двоичном сигнале нет искаженных сихросимволов синхрогрупп, то во время действия каждого циклового импульса на первых входах М элементов запрета, на вторые входы этих элементов запрета одновременно подают М синхросимволов «1» с соответствующих М дополнительных выходов опознавателя синхросигнала, а с выходов М элементов запрета на соответствующие одноразрядные входы сумматора искаженных синхросимволов синхрогруппы подают М символов «0», что означает, что ошибок синхросимволов синхрогруппы нет, соответственно на выходе этого сумматора формируют в двоичном коде «нулевое» число, в противоположном случае, когда во входном двоичном сигнале все М сихросимволов каждой синхрогруппы искажены, то во время действия каждого циклового импульса на первых входах М элементов запрета, на вторые входы этих элементов запрета одновременно подают М синхросимволов «0» с соответствующих М дополнительных выходов опознавателя синхросигнала, а с выходов М элементов запрета подают на соответствующие одноразрядные входы сумматора искаженных синхросимволов синхрогруп синхросимволы «1», что означает, что все синхросимволы синхрогруппы искажены, соответственно на выходе этого сумматора результат суммирования символов «1» на его входах представляют, в данном случае, в виде числа М в параллельном двоичном коде, которое подают синхронно с соответствующим цикловых импульсом формирователя цикловых импульсов на сигнальный вход накапливающего сумматора, с помощью которого производят суммирование искаженных синхросимволов синхрогрупп от цикла к циклу в течение S' циклов, подсчитываемых счетчиком циклов, по окончании которых на его выходе формируется импульс, который подают на управляющий вход второго блока памяти, обеспечивая перезапись и запоминание нового результата счета D' искаженных синхросимволов с выхода накапливающего сумматора, подключенного к входу данных второго блока памяти, кроме того, импульс с выхода счетчика циклов подают через первый элемент задержки на вход сброса накапливающего сумматора, обнуляя его содержимое, и счет искаженных синхросимволов синхрогрупп накапливающим сумматором, на вход синхронизации которого подают цикловые импульсы с выхода формирователя цикловых импульсов через второй элемент задержки, повторяют в течение следующих S' циклов, при этом записываемый во второй блок памяти текущий результат счета искаженных синхросимволов в течение каждых S' циклов, подают на сигнальный вход блока выбора порога, в котором по измеренной величине оценки вероятности ошибки синхросимвола Рос=D'/MS', величина которой находится в пределах соответствующего одного из Z интервалов допустимых значений величины Рос, формируют соответствующее пороговое число G'z в параллельном двоичном коде с соответствующим порядковым номером градации порогового числа z=1,2,…,Z, которое с выходе блока выбора порога подают на управляющий вход решающего узла в котором для исключения переполнения каких либо разрядов N-разрядных регистров сдвига с идентичными порядковыми номерами блока регистров сдвига, к выходу первого блока памяти дополнительно подключают дешифратор переполнения, на выходе которого при записи в первый блок памяти критического двоичного числа А=В-М, где В - максимально возможное n-разрядное двоичное число, формируется перепад напряжения, который подают на вход элемента ИЛИ, на другой вход которого подают импульсный сигнал синхронизации с выхода счетчика сравнения, при этом выход элемента ИЛИ подключают к входу сброса первого блока памяти, являющимся дополнительным выходом решающего узла, и входу сброса блока регистров сдвига, обеспечивая обнуление первого блока памяти и блока регистров сдвига при поступлении любого сигнала на соответствующий вход элемента ИЛИ.

В опознавателе синхросигнала для приема двоичного сигнала с сосредоточенной синхрогруппой из М синхросимволов с условными порядковыми номерами m=1,2,…,М и длительностью цикла или периодом повторения синхрогруппы равным Тц=N двоичных символов, используют М-разрядный регистр сдвига, в котором количество разрядов М с порядковыми номерами m=1,2,…,М, соответствующими порядку следования разрядов от старшего (выходного) разряда - при m=1, к младшему (входному) разряду - при m=М, который является информационным входом опознавателя синхросигнала, тактовым входом которого является тактовый вход М-разрядного регистра сдвига, выходы разрядов которого с порядковыми номерами m=1,2,…,М подключают к соответствующим входам преобразователя синхрогруппы, выходы которого с порядковыми номерами m=1, 2, …, М, являющиеся дополнительными выходами опознавателя синхросигнала с такими же порядковыми номерами m=1, 2, …, М, дополнительно подключают к соответствующим одноразрядным входам сумматора символов подобных синхросимволам синхрогруппы, выход которого является R-разрядным цифровым выходом опознавателя синхросигнала, состоящего из R одноразрядных выходов с порядковыми номерами r=1, 2, …, R.

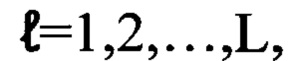

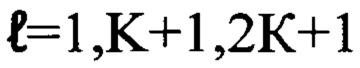

В опознавателе синхросигнала для приема двоичного сигнала с равномерно распределенной по циклу синхрогруппой из М синхросимволов с условными порядковыми номерами m=1, 2, …, М и длительностью цикла или периодом повторения синхрогруппы Тц=N=МТс двоичных символов, где Тс=К-период следования синхросимволов среди информационных символов равный K двоичных символов, используют L-разрядный регистр сдвига, в котором количество L=K(M-1)+1 разрядов с порядковыми номерами  соответствующих порядку следования разрядов от старшего (выходного) разряда - при m=1, к младшему (входному) разряду - при m=L, который является информационным входом опознавателя синхросигнала, тактовым входом которого является тактовый вход L-разрядного регистра сдвига, выходы М разрядов которого с порядковыми номерами

соответствующих порядку следования разрядов от старшего (выходного) разряда - при m=1, к младшему (входному) разряду - при m=L, который является информационным входом опознавателя синхросигнала, тактовым входом которого является тактовый вход L-разрядного регистра сдвига, выходы М разрядов которого с порядковыми номерами  при М=3 или

при М=3 или  (М-1)K+1 при М>3 подключают к соответствующим входам преобразователя синхрогруппы, выходы которого с порядковыми номерами m=1,2,…,М, являющиеся дополнительными выходами опознавателя синхросигнала с такими же порядковыми номерами m=1, 2, …, М, дополнительно подключают к соответствующим одноразрядным входам сумматора символов подобных синхросимволам синхрогруппы, выход которого является R-разрядным цифровым выходом опознавателя синхросигнала, состоящего из R одноразрядных выходов с порядковыми номерами r=1, 2, …, R.

(М-1)K+1 при М>3 подключают к соответствующим входам преобразователя синхрогруппы, выходы которого с порядковыми номерами m=1,2,…,М, являющиеся дополнительными выходами опознавателя синхросигнала с такими же порядковыми номерами m=1, 2, …, М, дополнительно подключают к соответствующим одноразрядным входам сумматора символов подобных синхросимволам синхрогруппы, выход которого является R-разрядным цифровым выходом опознавателя синхросигнала, состоящего из R одноразрядных выходов с порядковыми номерами r=1, 2, …, R.

Сопоставительный анализ с прототипом показывает, что введение существенных отличительных признаков составляет новизну и позволяет, как будет показано ниже, решить поставленные задачи.

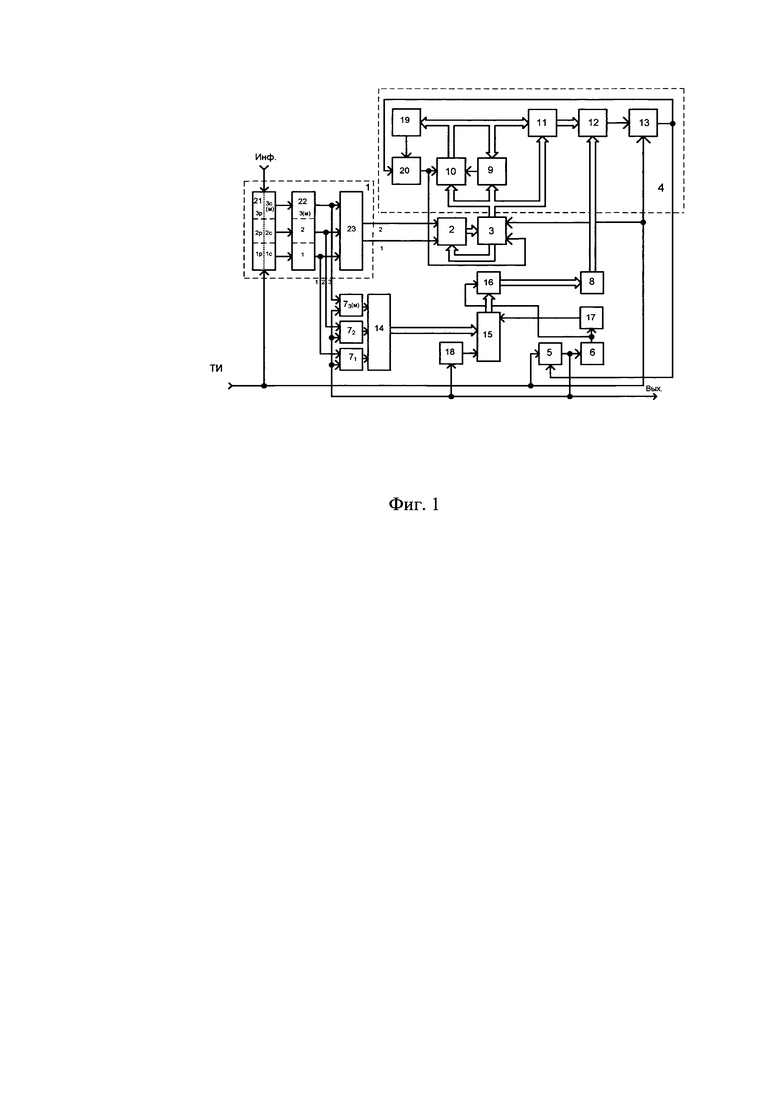

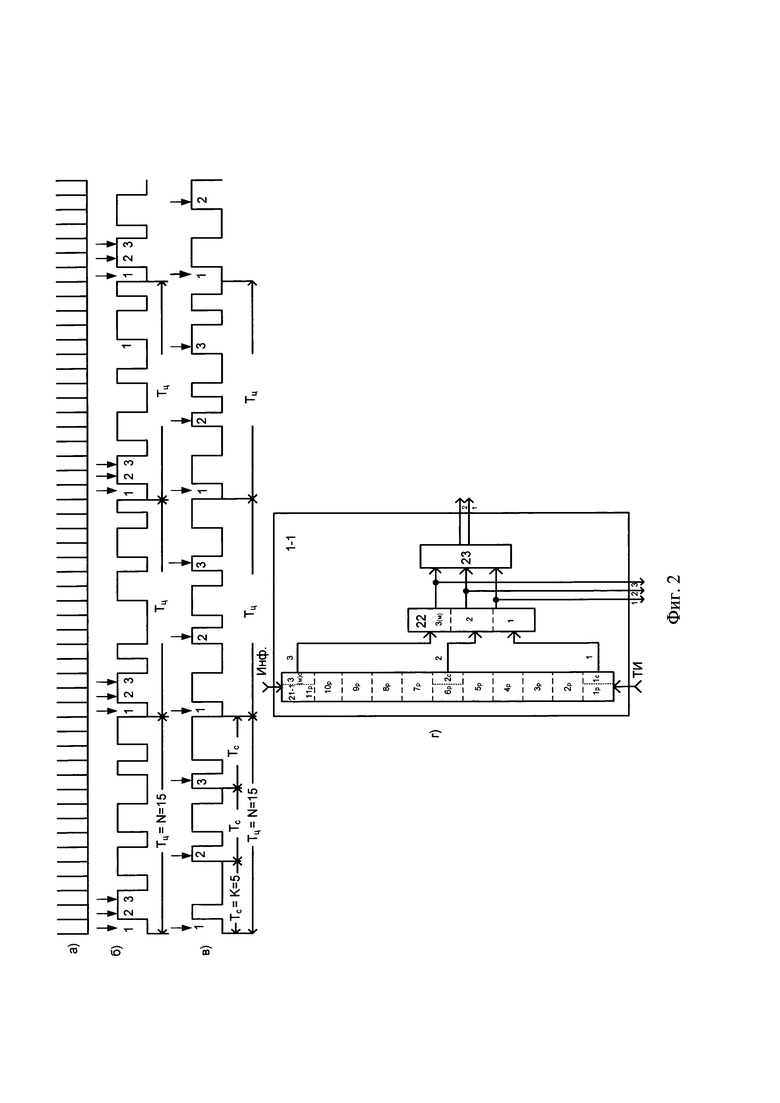

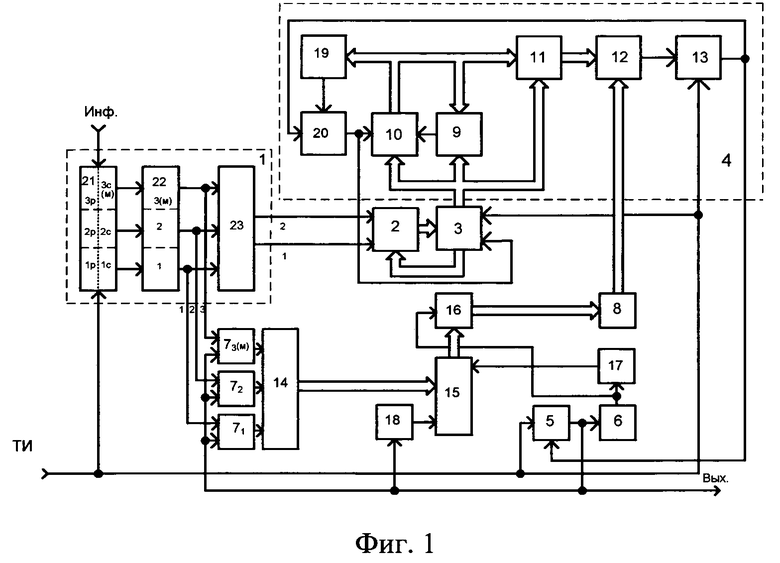

Рассмотрим эффективность предлагаемого изобретения на примере функционирования устройства цикловой синхронизации, схема электрическая структурная которого приведена на фиг. 1 с опознавателем синхросигнала в составе для приема двоичного сигнала с сосредоточенной синхрогруппой при М=3, Тц=N=15. На фиг. 2 г приведена схема электрическая структурная опознавателя синхросигнала для приема двоичного сигнала с распределенной по циклу синхрогруппой при М=3, Тц=N=MTc=15, Тс=К=5. На фиг. 2а,б,в приведены временные диаграммы входных сигналов устройства: а) - тактовых импульсов; б) - сигнала с сосредоточенной синхрогруппой; в) - сигнала с равномерно распределенной по циклу синхрогруппой.

Устройство цикловой синхронизации для сигнала с сосредоточенной синхрогруппой содержит опознаватель 1 синхросигнала, сумматор 2, блок 3 регистров сдвига, решающий узел 4, формирователь 5 цикловых импульсов, счетчик 6 циклов, М=3 элементов 71,72,73 запрета с порядковым номером m=1,2,3 и блок 8 выбора порога, причем информационным и тактовым входами устройства являются соответственно информационный и тактовый входы опознавателя 1 синхросигнала, R=2 разрядных выходов которого с порядковыми номерами разрядных выходов r=1,2, составляющих R-разрядный выход, подключены к соответствующим разрядным входам с такими же порядковыми номерами разрядных входов первого входа сумматора 2, выход которого подключен к сигнальному входу блока 3 регистров сдвига, основной и дополнительный выходы которого подключены соответственно к второму входу сумматора 2 и сигнальному входу решающего узла 4, тактовый вход которого объединен с соответствующими входами опознавателя 1 синхросигнала, блока 3 регистров сдвига, и формирователя 5 цикловых импульсов.

Здесь R=2 - минимально необходимое число одноразрядных выходов или число разрядов R-разрядного выхода опознавателя 1 синхросигнала, количество разрядов которого выбирается из условия R=]log2M[, где][ - округление до ближайшего наибольшего целого числа, М=3 - число синхросимволов в сосредоточенной или распределенной по циклу синхрогруппе двоичного сигнала на информационном входе устройства, следующих во времени друг за другом с условными порядковыми номерами m=1,2,3 и длительностью цикла или периодом повторения синхрогрупп среди информационных символов равным Тц=N двоичных символов и равным количеству N=15 разрядов каждого регистра сдвига блока 3 регистров сдвига.

Выход формирователя 5 цикловых импульсов, являющийся выходом устройства, объединен с входом счетчика 6 циклов и первыми входами М=3 элементов 71,72,73 запрета с порядковыми номерами m=1, 2, 3, вторые входы которых подключены к соответствующим дополнительным выходами опознавателя синхросигнала с таким же порядковым номерами m=1, 2, 3, при этом вход сброса формирователя 5 цикловых импульсов подключен к выходу решающего узла 4, управляющий вход которого подключен к выходу блока 8 выбора порога.

Решающий узел 4 состоит из первого блока 9 сравнения, первого блока 10 памяти, блока 11 вычитания, второго блока 12 сравнения и счетчика 13 сравнения, причем выход первого блока 9 сравнения, подключен к входу управления первого блока 10 памяти, выход которого объединен с входом дешифратора 19 переполнения и первыми входами первого блока 9 сравнения и первого блока 11 вычитания, выход которого подключен к первому входу второго блока 12 сравнения, выход которого подключен к входу сброса счетчика 13 сравнения, выход которого, являющийся выходом решающего узла 4, дополнительно подключен к первому входу элемента 20 ИЛИ, второй вход которого подключен к выходу дешифратора 19 переполнения, а выход элемента 20 ИЛИ, являющийся дополнительным выходом решающего узла 4, объединен с входами сброса первого блока 10 памяти и блока 3 регистров сдвига, причем сигнальным, управляющим и тактовым входами решающего узла 4 являются соответственно вход данных первого блока 10 памяти, объединенного с вторыми входами первого блока 9 сравнения, и блока 11 вычитания, второй вход второго блока 12 сравнения и тактовый вход счетчика 13 сравнения.

Кроме того, устройство содержит сумматор 14 искаженных синхросимволов синхрогруппы, накапливающий сумматор 15, второй блок 16 памяти, первый элемент 17 задержки и второй элемент 18 задержки, при этом выходы М=3 элементов 71,72,73 запрета с порядковыми номерами m=1,2,3 подключены к соответствующим одноразрядным входам сумматора 14 искаженных синхросимволов сихрогруппы, выход которого подключен к сигнальному входу накапливающего сумматора 15, вход сброса и вход синхронизации которого подключены соответственно к выходу счетчика 6 циклов через первый элемент 17 задержки и дополнительно к выходу формирователя цикловых 5 импульсов через второй элемент 18 задержки, а выход накапливающего сумматора 15 подключен к входу данных второго блока 16 памяти, выход и вход управления которого подключены соответственно к сигнальному входу блока 8 выбора порога и дополнительно к выходу счетчика 6 циклов.

Опознаватель 1 синхросигнала для приема двоичного сигнала с сосредоточенной синхрогруппой из М=3 синхросимволов с условными порядковыми номерами m=1, 2, 3 и длительностью цикла или периодом повторения синхрогруппы равным Тц=N=15 двоичных символов, содержит М-разрядный регистр 21 сдвига, в котором количество разрядов М=3 с порядковыми номерами m=1,2,3, соответствующими порядку следования разрядов от старшего (выходного) разряда - при m=1, к младшему (входному) разряду - при m=3, который является информационным входом опознавателя 1 синхросигнала, тактовым входом которого является тактовый вход М-разрядного регистра сдвига, выходы разрядов которого с порядковыми номерами m=1, 2, 3 подключены к соответствующим входам преобразователя 22 синхрогруппы, выходы которого с порядковыми номерами m=1, 2, 3, являющиеся дополнительными выходами опознавателя 1 синхросигнала с такими же порядковым номерами m=1, 2, 3, дополнительно подключены к соответствующим одноразрядным входам сумматора 23 символов подобных синхросимволам синхрогруппы, выход которого является R-разрядным цифровым выходом опознавателя 1 синхросигнала, состоящего из R=2 одноразрядных выходов с порядковыми номерами r=1, 2.

Опознаватель 1-1 синхросигнала для приема двоичного сигнала с равномерно распределенной по циклу синхрогруппой из М=3 синхросимволов с условными порядковыми номерами m=1, 2, 3 и длительностью цикла или периодом повторения синхрогруппы Тц=N=МТс=15 двоичных символов, где Тс=К - период следования синхросимволов среди информационных символов равный K=5 двоичных символов, содержит L-разрядный регистр 21-1 сдвига, в котором количество L=K(M-1)+1=11 разрядов с порядковыми номерами  соответствующих порядку следования разрядов от старшего (выходного) разряда - при m=1, к младшему (входному) разряду - при m=11, который является информационным входом опознавателя 1-1 синхросигнала, тактовым входом которого является тактовый вход L-разрядного регистра сдвига, выходы М=3 разрядов которого с порядковыми номерами

соответствующих порядку следования разрядов от старшего (выходного) разряда - при m=1, к младшему (входному) разряду - при m=11, который является информационным входом опознавателя 1-1 синхросигнала, тактовым входом которого является тактовый вход L-разрядного регистра сдвига, выходы М=3 разрядов которого с порядковыми номерами  подключены к соответствующим входам преобразователя синхрогруппы, выходы которого с порядковыми номерами m=1, 2, 3, являющиеся дополнительными выходами опознавателя 1-1 синхросигнала с такими же порядковым номерами m=1, 2, 3, дополнительно подключены к соответствующим одноразрядным входам сумматора 23 символов подобных синхросимволам синхрогруппы, выход которого является R-разрядным цифровым выходом опознавателя синхросигнала, состоящего из R=2 одноразрядных выходов с порядковыми номерами r=1, 2.

подключены к соответствующим входам преобразователя синхрогруппы, выходы которого с порядковыми номерами m=1, 2, 3, являющиеся дополнительными выходами опознавателя 1-1 синхросигнала с такими же порядковым номерами m=1, 2, 3, дополнительно подключены к соответствующим одноразрядным входам сумматора 23 символов подобных синхросимволам синхрогруппы, выход которого является R-разрядным цифровым выходом опознавателя синхросигнала, состоящего из R=2 одноразрядных выходов с порядковыми номерами r=1, 2.

Устройство цикловой синхронизации работает следующим образом.

Если входной двоичный сигнал содержит цикловой синхросигнал в виде сосредоточенной синхрогруппы из М=3 синхросимволов, периодически повторяемой среди информационных символов с периодом повторения Тц=N=15 двоичных символов (фиг. 2б), то в составе устройства цикловой синхронизации должен использоваться опознаватель синхросигнала, которой входит в устройство, приведенное на фиг. 1. Здесь с опознаватель 1 синхросингала, содержит М-разрядный регистр 21 сдвига, в котором количество разрядов М=3 с порядковыми номерами m=1,2,3, соответствующими порядку следования разрядов от старшего (выходного) разряда - при m=1 к младшему (входному) разряду - при m=3, вход которого является информационным входом опознавателя 1 синхросигнала и устройства в целом,

Под воздействием тактовых импульсов (фиг. 2а) входная последовательность двоичных символов (фиг. 2б) продвигается по разрядам М-разрядного регистра 21 сдвига. В данном случае сосредоточенная синхрогруппа из М=3 синхросимволов представляет собой комбинацию синхросимволов вида «011». В тактовых интервалах, совпадающих во времени с цикловыми импульсами с выхода формирователя 5 цикловых импульсов эта синхрогруппа каждого цикла располагается в соответствующих разрядах М-разрядного регистра 21 сдвига с порядковыми номерами m=1, 2, 3, выходы которых подключены к соответствующим входам преобразователя 22 синхрогруппы, который обеспечивает преобразование известной комбинации из М=3 синхросимволов «011» в комбинацию М=3 «единичных» синхросимволов «111» с помощью соответствующих логических элементов преобразователя 22 синхрогруппы: одного логического элемента с функцией отрицания - НЕ и двух логических элементов каждый с функцией повторения или двойного отрицания - НЕ-НЕ [7].

Одноразрядные выходы преобразователя 22 синхрогруппы, являющиеся дополнительными выходами опознавателя 1 синхросигнала с порядковыми номерами m=1, 2, 3, дополнительно подключены к соответствующим одноразрядным входам сумматора 23 символов подобных синхросимволам синхрогруппы. Сумматор 23 производит подсчет символов «1» на его входах и выдает результат суммирования на цифровой выход опознавателя 1 синхросигнала в двоичном коде. Для представления максимального десятичного числа М=3 двоичным кодом требуется R=2 разряда или два одноразрядных выхода опознавателя 1 синхросигнала, выбираемого из соотношения R=]log2M[, где][ - округление до ближайшего наибольшего целого числа. Сумматор 23 представляет собой комбинационный сумматор параллельного действия [7], выход которого является R-разрядным цифровым выходом опознавателя 1 синхросигнала, состоящего из R=2 одноразрядных выходов с порядковыми номерами r=1, 2.

Если принимаемый двоичный сигнал содержит распределенную по циклу синхрогруппу, периодически повторяемую среди информационных символов (фиг. 2в), то в составе устройства, приведенного на фиг. 1, должен использоваться другой вариант исполнения опознавателя 1-1 синхросигнала (фиг. 2г), содержащий L-разрядный регистр 21-1 сдвига, в котором количество L=K(M-1)+1=11 разрядов с порядковыми номерами  соответствующих порядку следования разрядов от старшего (выходного) разряда - при

соответствующих порядку следования разрядов от старшего (выходного) разряда - при  к младшему (входному) разряду - при

к младшему (входному) разряду - при  =11, вход которого является информационным входом опознавателя 1 синхросигнала и устройства в целом.

=11, вход которого является информационным входом опознавателя 1 синхросигнала и устройства в целом.

Под воздействием тактовых импульсов (фиг. 2а) последовательность двоичных символов продвигается по разрядам L-разрядного регистра 21-1 сдвига. В данном случае распределенная по циклу синхрогруппа также состоит из М=3 синхросимволов и представляет собой комбинацию синхросимволов вида «011» с условными порядковыми номерами m=1, 2, 3. В тактовых интервалах, совпадающих во времени с цикловыми импульсами с выхода формирователя 5 цикловых импульсов эта синхрогруппа каждого цикла располагается в соответствующих разрядах L-разрядного регистра сдвига 21-1 с порядковыми номерами  =1,K+1,2К+1=1, 6, 11, выходы которых подключены к входам соответствующих логических элементам, составляющих преобразователь 22 синхрогруппы, который обеспечивает преобразование известной комбинации из М=3 синхросимволов «011» в комбинацию «единичных» синхросимволов «111» с помощью соответствующих М=3 логических элементов преобразователя 22 синхрогруппы: одного логического элемента с функцией отрицания - НЕ и двух логических элементов каждый с функцией повторения или двойного отрицания - НЕ-НЕ.

=1,K+1,2К+1=1, 6, 11, выходы которых подключены к входам соответствующих логических элементам, составляющих преобразователь 22 синхрогруппы, который обеспечивает преобразование известной комбинации из М=3 синхросимволов «011» в комбинацию «единичных» синхросимволов «111» с помощью соответствующих М=3 логических элементов преобразователя 22 синхрогруппы: одного логического элемента с функцией отрицания - НЕ и двух логических элементов каждый с функцией повторения или двойного отрицания - НЕ-НЕ.

Одноразрядные выходы преобразователя 22 синхрогруппы, являющиеся дополнительными выходами опознавателя 1-1 синхросигнала с соответствующими порядковыми номерами m=1, 2, 3, дополнительно подключены к соответствующим одноразрядным входам сумматора 23 символов подобных синхросимволам синхрогруппы. Сумматор 23 производит подсчет символов «1» на его входах и представляет собой комбинационный сумматор параллельного действия [7], выход которого является R-разрядным цифровым выходом опознавателя 1 синхросигнала, состоящего из R=2 одноразрядных выходов с порядковыми номерами r=1, 2.

Таким образом, работа опознавателей 1 и 1-1 синхросигналов аналогична и заключается в подсчете символов подобных синхросимволам синхрогруппы сосредоточенной либо распределенной.

В любой проектируемой либо действующей системе связи может использован только один выбранный при проектировании вид циклового синхросигнала, поэтому в устройстве цикловой синхронизации (фиг. 1) должен использован либо опознаватель 1 синхросигнала, либо опознаватель 1-1 синхросигнала. С учетом этого любой вариант исполнения опознавателя 1 или 1-1 синхросигнала, построенный по приведенным на фиг. 1 и фиг. 2г структурам для соответствующего сигнала - с сосредоточенной или распределенной по циклу синхрогруппой с любыми одинаковыми параметрами М, R, Тц=N=МТс, совместим со всеми взаимодействующими функциональными элементами в составе устройства синхронизации по циклам, приведенного на фиг. 1.

Результаты суммирования символов подобных синхросимволам синхрогруппы с цифрового выхода опознавателя 1 или 1-1 синхросигнала подаются на первый вход сумматора 2. На второй вход сумматора 2 с выхода блока 3 регистров сдвига подаются с тактовой частотой следования двоичные n-разрядные двоичные числа в параллельном коде.

Сумматор 2 представляет собой параллельный комбинационный сумматор [7], у которого два младших разрядных входа (R=2) первого слагаемого и n разрядных входов второго слагаемого являются соответственно первым и вторым входами сумматора 2, при этом другие n-2 разрядные входы первого входа подключены к источнику «нулевого» уровня.

Блок 3 регистров сдвига включает в себя n N-разрядных регистров сдвига, у которых раздельно объединены тактовые входы и входы сброса. При этом объединенные тактовые входы и объединенные входы сброса регистров сдвига в составе блока 3 регистров сдвига являются соответственно тактовым входом и входом сброса блока 3 регистров сдвига, а входы первых разрядов, выходы последних разрядов и выходы первых разрядов всех n регистров сдвига являются соответственно сигнальным входом, выходом и дополнительным выходом блока 3 регистров сдвига.

Таким образом, результат счета символов подобных синхросимволам синхрогруппы на выходе опознавателя 1 или 1-1 синхросигнала, имеющий место в i-ом тактовом интервале, складывается в сумматоре 2 с результатом предыдущего счета символов подобных синхросимволам на i-й позиции цикла, поступающим с выхода блока 3 регистров сдвига, и новый результат счета таких символов, больший на М≤3 прежнего, записывается в виде n-разрядного двоичного числа в первые ячейки (разряды) регистров сдвига блока 3 регистров сдвига.

При этом двоичное число, записанное до этого в первые ячейки блока 3 регистров сдвига, а также все остальные числа, хранящиеся в последующих однотипных ячейках, параллельно сдвигаются на один разряд, и с выхода блока 3 регистров сдвига на второй вход сумматора 2 поступает уже следующий результат счета символов - на (i+1)-й позиции цикла, который перезаписывается в первые ячейки блока 3 регистров сдвига, а остальные числа, хранящиеся в однотипных ячейках блока 3 регистров сдвига, сдвигаются на один разряд и т.д. т.е. блок 3 регистров сдвига обеспечивает запоминание результатов счета символов подобных синхросимволам на каждой позиции цикла в течение длительности цикла. При этом величина n определяет емкость памяти результатов счета.

Одновременно результаты счета символов подобных синхросимволам на каждой из позиций цикла с дополнительного выхода блока 3 регистров сдвига последовательно поступают на сигнальный вход решающего узла 4. В решающем узле 4, например, а i-м тактовом интервале, двоичное число в параллельном коде, представляющее собой текущий результат счета символов подобных синхросимволам на i-й позиции цикла, одновременно подается на соответствующие входы первого блока 9 сравнения, первого блока 10 памяти и первого блока 11 вычитания. В первом блоке 9 сравнения входное число сравнивается с двоичным числом, хранящимся в первом блоке 10 памяти и, если оно превышает число первого блока 10 памяти, то на выходе первого блока 9 сравнения формируется импульс, который, поступая на вход управления первого блока 10 памяти, обеспечивает стирание прежнего и запись нового (входного) числа. После этого на входах первого блока 9 сравнения оказываются равные двоичные числа. Если же входное число равно или меньше числа, хранящегося в первом блоке 10 памяти, то содержимого последнего не изменяется.

Таким образом, в первый блок 10 памяти перезаписывается наибольший текущий результат счета символов подобных синхросимволам на какой-либо позиции цикла, который далее сравнивается с результатами счета на последующих позициях цикла. Получающаяся разность (между числом первого блока 10 памяти и входным числом) на выходе блока 11 вычитания в виде двоичного числа в параллельном коде сравнивается во втором блоке 12 сравнения с пороговым числом G'z, поступающем на второй его вход (являющийся управляющимся входом решающего узла 4) с выхода блока 8 выбора порога. При этом, если число с выхода блока 11 вычитания меньше порогового числа G'z, то с выхода второго блока 12 сравнения на вход сброса счетчика 13 сравнения поступает «единичный» (запрещающий) потенциал, который устанавливает и удерживает его в «нулевом» состоянии. В противоположном случае, когда в i-м тактовом интервале число с выхода блока 11 вычитания равно или больше число G'z, то с выхода второго блока 12 сравнения поступает «нулевой» (разрешающий) потенциал, и счетчик 13 сравнения производит счет одного тактового импульса, поступающего на его тактовый вход, являющийся тактовым входом решающего узла 4. При этом, если наибольшее двоичное число, записанное в первый блок 10 памяти, в каком-либо j-м тактовом интервале и соответствующее результату накопления на j-й позиции цикла, будет превышать на величину равную или большую порогового числа G'z каждое из N-1 последующих чисел, поступающих друг за другом с дополнительного выхода блока 3 регистров сдвига, то счетчик 13 сравнения произведет счет следующих подряд N-1 тактовых импульсов, после чего на его выходе формируется импульсный сигнал синхронизации. Этот сигнал подается на вход сброса формирователя 5 цикловых импульсов и на первый вход элемента ИЛИ 20, выход которого является дополнительным выходом решающего узла 4 и объединен со входами сброса первого блока 10 памяти и блока 3 регистров сдвига. В результате действия импульсного сигнала синхронизации производится обнуление первого блока 10 памяти и блока 3 регистров сдвига и производится фазирование формирователя 5 цикловых импульсов. Далее процесс поиска циклового синхросигнала повторяется, при этом, если сбоя синхронизма по циклам не происходило, то сигнал синхронизации с выхода решающего узла 4, будет подтверждать цикловую фазу выходного сигнала. Поскольку количество n регистров сдвига в блоке 3 регистров сдвига ограничено, то возможно переполнение разрядных ячеек памяти блока 3 регистров сдвига при суммировании символов подобных синхросимволам. В результате алгоритм работы устройства может нарушаться и возрастает вероятность ложного срабатывания решающего узла 4. Для исключения таких ситуаций к выходу первого блока 10 памяти подключен дешифратор 19 переполнения, который при записи в первый блок 10 памяти критического двоичного числа А=В-М, где В - максимально возможное n-разрядное двоичное число, формирует перепад напряжения, который поступает на второй вход элемента ИЛИ 20, обнуляя первый блока 10 памяти и блок 3 регистров сдвига.

Процесс формирования пороговых чисел блоком 8 выбора порога для решающего узла 3 производится следующим образом.

На вторые входы элементов 71,72,73 запрета поступают двоичные элементы с М=3 выходов с порядковыми номерами m=1, 2, 3 преобразователя 22 синхрогруппы, являющихся соответствующими выходами опознавателя 1 или 1-1 синхросигнала, а на первые входы этих элементов запрета - последовательность импульсов с выхода формирователя 5 цикловых импульсов. В результате на выход каждого элемента запрета пройдет только тот символ с соответствующего выхода преобразователя 22 синхрогруппы, причем с инверсией, который во времени совпадает с «единичным» импульсом (одиночным символом «1») формирователя 5 цикловых импульсов. Таким образом, если, например, в разряды регистра 21 сдвига опознавателя 1 синхросигнала поступит М=3 правильно принятых синхросимволов синхрогруппы и в момент продвижения первого символа «0» синхрогруппы «011» (фиг. 2б) в разряд регистра 21 сдвига с порядковым номером m=1 одновременно поступит «единичный» импульс формирователя 5 цикловых импульсов, то на выходе каждого из М=3 элементов 71,72,73 запрета появится символ «0» (ошибок в синхрогруппе нет). Если все М символов синхрогруппы искажены, т.е. в разрядах регистра 21 сдвига располагается синхрогруппа «100», на соответствующих выходах преобразователя 22 синхрогруппы появится синхрогруппа «000», то на выходе каждого из М элементов запрета появится символ «1» (три ошибки в синхрогруппе). В общем случае, при каждом поступлении циклового импульса на выходах М элементов запрета могут фиксироваться от 0 до М=3 «единичных» символов (ошибок синхросимволов) в зависимости от вероятности ошибки двоичного символа принимаемого сигнала. Причем в интервалах между цикловыми импульсами, каждый длительностью N-1=14 символов «0», на выходах элементов 71, 72, 73 запрета будет периодически фиксироваться N-1=14 символов «0».

Аналогичные операции производятся и в регистре 21-1 сдвига и преобразователе 22 синхрогруппы опознавателя 1-1 синхросигнала (фиг. 2г).

Выходы элементов 71, 72, 73 подключены к соответствующим одноразрядным входам сумматора 14 искаженных синхросимволов синхрогруппы, который производит подсчет искаженных синхросимволов (символов «1» на входах сумматора) в двоичном коде. Сумматор 14 представляет собой комбинационный сумматор параллельного действия [7]. Выход сумматора 14 искаженных синхросимволов синхрогруппы подключен к сигнальному входу накапливающего сумматора 15, подсчитывающего общее число искаженных синхросимволов различных синхрогрупп. Подсчитывая число D' искаженных синхросимволов в течение времени счета довольно большого числа цикловых импульсов S', можно с определенной степенью точности периодически определять вероятность (частость) ошибочного приема синхросимвола по формуле Рос=D'/MS', т.е. производить текущую оценку степени искажений принимаемого сигнала. При этом счетчик 6 циклов посчитывает общее число S' цикловых импульсов, в течение которых передано MS' синхросимволов. Коэффициент счета (емкость) счетчика 8 циклов выбирается равной величине S', поэтому после счета каждых S' цикловых импульсов на его выходе формируется одиночный импульс, после чего он сбрасывается в «нуль». С помощью этого импульса во второй блок 16 памяти записывается результат счета D' искаженных синхросимволов накапливающим сумматором 15, вместо хранившегося в нем прежнего двоичного числа, записанного после окончания счета предыдущих S' цикловых импульсов. С некоторой задержкой, определяемой первым элементом задержки 17, сбрасывается в «нуль» накапливающий сумматор 15 и процесс анализа качества принимаемого сигнала в течение следования последующих S цикловых импульсов повторяется.

На сигнальный вход накапливающего сумматора 15 цифровые данные поступают синхронно с импульсами формирователя 5 цикловых импульсов. Поэтому для обеспечения накапливающим сумматором 15 надежного последовательного суммирования чисел в двоичном коде, на его вход синхронизации должны подаваться импульсы с выхода формирователя 5 цикловых импульсов с некоторой задержкой [7], определяемой вторым элементом задержки 18.

Блок 8 выбора порога в зависимости от значения записанного в второй блок 16 памяти двоичного числа D' производит выбор определенного двоичного порогового числа G'z в зависимости от условий связи, которое с его выхода в параллельном коде подается на управляющий вход решающего узла 4.

Таким образом, в течение времени счета каждых S' циклов в решающий узел 4 подается определенное пороговое число G'z, которое может принимать в каждом конкретном случае одно из z=1, 2, …, Z дискретных значений (градаций) в зависимости от качества принимаемого сигнала, определяемого величиной ошибки синхросимвола Рос. Необходимое число градаций Z порогового числа G'z выбирается из расчета поддержания вероятности ложного срабатывания решающего узла 4 (ложного обнаружения цикловой фазы сигнала в течение среднего интервала времени между двумя соседними сбоями синхронизма по циклам) при различных изменениях величины Рос При этом закон формирования конкретных значений пороговых чисел G'z блоком 8 выбора порога символически можно записать

где F - заранее выбранное правило для блока 8 выбора порога, по которому величина Рос≈D'/MS', принимающей значения в пределах z-го интервала измерений, приводится в соответствии вполне определенное значение порогового числа G'z;

Az и Bz - соответственно нижняя и верхняя границы величины Рос для z-го интервала.

Соответственно требуемая помехоустойчивость устройства, которая определяется вероятностью ложного срабатывания, обеспечивается выбором закона формирования пороговых чисел G'z для блока 8 выбора порога по соответствующим измеренным значениям величины Рос, попадающим в пределы какого-либо z-го интервала с границами Az и Bz, по принципу: чем больше величина Рос, тем большим должно быть пороговое число G'z.

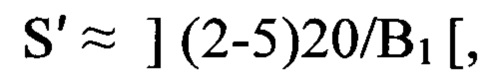

Величина S', определяющая коэффициент счета счетчика 6 циклов, должна выбираться, с одной стороны, достаточно большой, для того, чтобы обеспечить требуемую точность оценки вероятности ошибки Рос синхросигнала, с другой стороны - достаточно малой, чтобы обеспечить измерение величины Рос в пределах между двумя сбоями синхронизма по циклам и слежение за изменениями условий связи. Если считать, что сбои синхронизма по циклам происходят через интервалы времени, намного превышающие время счета S' цикловых импульсов (что имеет место на практике), то величина S' может быть выбрана в следующем виде [6]

где B1 - верхняя граница величины Рос в пределах первого интервала измерений, который соответствует наименьшему пороговому числу G'z;

][ - означает округление до ближайшего целого числа.

Для определения эффективности предлагаемого способа поиска временного положения циклового синхросигнала (ЦС) или цикловой фазы сигнала требуется выяснить, что лучше с точки зрения уменьшения времени поиска ЦС:

- либо в качестве первичного источника синхроинформации использовать отклики опознавателя синхросигнала (ОС), который, как и во многих других устройствах цикловой синхронизации, выполняет функцию дешифратора синхрогруппы (ДС) из М синхросимволов [3] и производить их накопление в соответствии алгоритмом работы устройств, основанном на полученном ранее оптимальном алгоритме поиска временного положения ЦС (1*);

- либо использовать синхроинформацию, содержащуюся непосредственно в принимаемой двоичной последовательности и при этом производить суммирование не откликов ДС от каждой позиции цикла, а синхросимволов синхрогрупп (истинных или ложных), поступающих на вход ОС, согласно алгоритму (2*).

Эту операцию можно производить с помощью ОС, структурная схема которого приведена на фиг. 1 (ОС 1) или на фиг. 2г (ОС 1-1), каждый из которых будем называть сумматором символов подобных синхросимволам синхрогруппы (СС). При этом с выхода СС синхроинформация на каждой анализируемой позиции цикла снимается не в виде двоичных символов «1» и «0» (откликов), как с одноразрядного выхода ДС (ОС), а в виде результатов суммирования символов подобных сихросимволам синхрогруппы.

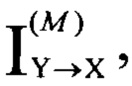

Для решения поставленной задачи необходимо определить количество информации, получаемое как от каждого отклика ДС, так и непосредственно от синхросимволов синхрогруппы и далее произвести сравнение по времени накопления одного и того же количества синхроинформации при указанных двух способах накопления откликов ДС и символов подобных синхросимволов синхрогрупп, как выполнено в работе [5].

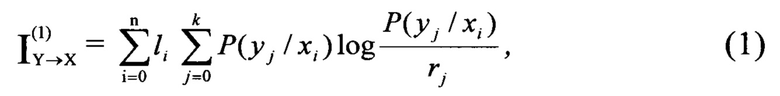

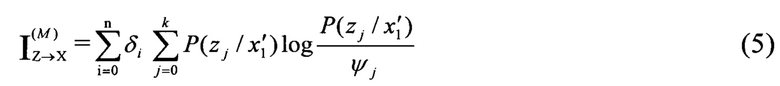

Для решения поставленной задачи следует определить количество информации, поступающей на вход ДС при дешифрации М синхросимволов и количество информации, получаемой при этом на его выходе. Рассмотрим три системы, которые условно обозначим X, Y и Z Пусть система X является источником передачи символов, а системы Y и Z - соответственно демодулятор и демодулятор с ДС. При этом будем производить наблюдение за системой X через системы Y и Z отдельно. Для определения количества информации  содержащейся в системе Y относительно системы X, состоящую из источника информации X при приеме М символов, можно определить сначала количество информации, содержащейся в каждом приятом символе

содержащейся в системе Y относительно системы X, состоящую из источника информации X при приеме М символов, можно определить сначала количество информации, содержащейся в каждом приятом символе  и, воспользовавшись свойством аддитивности информации [10], определить величину

и, воспользовавшись свойством аддитивности информации [10], определить величину  . По общему определению количества информации [8] имеем

. По общему определению количества информации [8] имеем

где  и rj - безусловные вероятности того, что системы X и Y принимают состояния xi и yj соответственно; Р (yj/xi) условная вероятность того, что система Y будет находиться в состоянии yj, если система X приняла состояние xi. Предположим, что система X приняла вполне определенное состояние x1, например, передан первый символ синхрогруппы - «1». Тогда в формуле (1) индекс суммирования i принимает только одно значение i=1, соответственно безусловная вероятность передачи синхросимвола i1=1.

и rj - безусловные вероятности того, что системы X и Y принимают состояния xi и yj соответственно; Р (yj/xi) условная вероятность того, что система Y будет находиться в состоянии yj, если система X приняла состояние xi. Предположим, что система X приняла вполне определенное состояние x1, например, передан первый символ синхрогруппы - «1». Тогда в формуле (1) индекс суммирования i принимает только одно значение i=1, соответственно безусловная вероятность передачи синхросимвола i1=1.

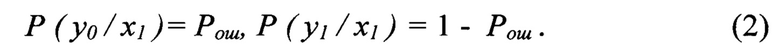

Система Y может принимать два значения - y1 (принят символ «1») и у0 (принят символ «0»), при этом r1=r0=0.5, а возможные значения условных вероятностей в формуле (1) будут иметь вид

С учетом (2) формула (1) преобразуется к виду

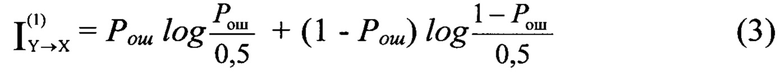

Если последующий передаваемый символ должен принимать противоположное значение - «0» в соответствии со структурой синхросигнала, то нетрудно показать, что количество информации, получаемой системой Y, будет также определяться выражением (3), т.е. количество информации, содержащейся в каждом принимаемом синхросимволе, не зависит от того, какое конкретное значение принимает каждый синхросимвол в синхрогруппе.

С учетом (3) общее количество информации, получаемое системой Y при приеме синхрогруппы, будет равно

Воспользовавшись формулой (1), определим теперь количество информации

содержащейся в системе Z, о состоянии системы X:

содержащейся в системе Z, о состоянии системы X:

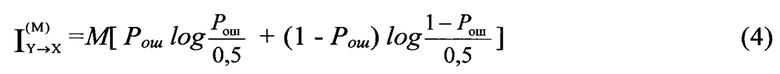

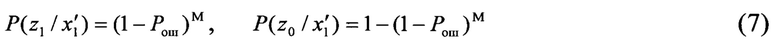

В данном случае также предположим, что система X прияла вполне определенное состояние х'1 (передана последовательность М сихросимволов), при этом i=1, а безусловная вероятность δi=1. Система Z может принимать также два состояния - z1 («единичный» отклик ДС) и z0 («нулевой» отклик ДС), а безусловные вероятности нахождения системы Z в этих состояниях будут равны

Возможные значения условных вероятностей в формуле (5) можно записать в виде

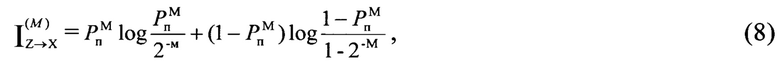

С учетом (6) и (7) выражение (5) будет иметь вид

где Рп=1-Рош.

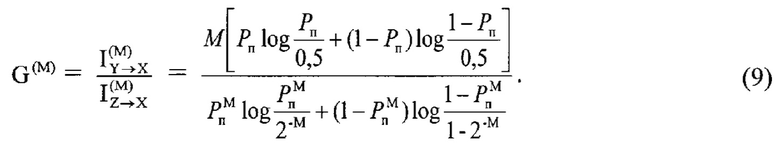

Для определения выигрыша G(M) по количеству синхроинформации, получаемой системой Y по отношению к системе Z при приеме М символов при каком-либо значении величины Рп>0,5, достаточно найти отношение величин  определяемых формулами (4) и (8)

определяемых формулами (4) и (8)

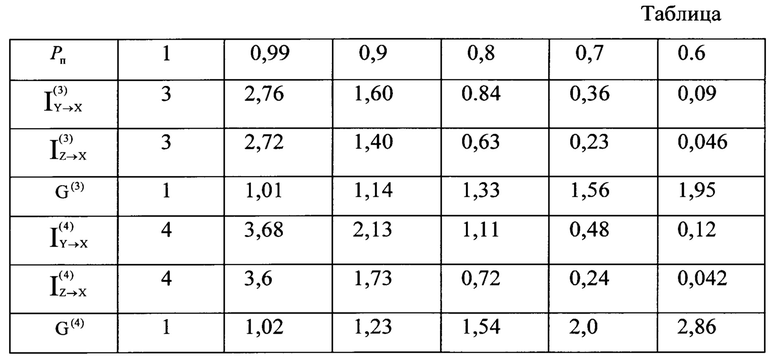

Для примера в таблице приведены результаты расчета величин  (в двоичных единицах) и G(M) (в разах) по формулам (4), (8) и (9) соответственно при различных Рп и при M1=3 и М2=4.

(в двоичных единицах) и G(M) (в разах) по формулам (4), (8) и (9) соответственно при различных Рп и при M1=3 и М2=4.

Из анализа данных таблицы следует, что при  т.е. при хороших условиях связи системы Y и Z эквиваленты в части получаемых сведений о переданном синхросигнале. Однако с уменьшением Рп в системе Z происходит более быстрое «разрушение» синхроинформации, чем в системе Y, т.е. при использовании в качестве первичного источника синхроинформации откликов ДС для обнаружения временного положения ЦС, теряется определенное количество информации, имеющейся на приемной стороне (в системе Y). Причем эти потери тем значительнее, чем хуже условия связи и чем больше синхросимволов М в синхрогруппе.

т.е. при хороших условиях связи системы Y и Z эквиваленты в части получаемых сведений о переданном синхросигнале. Однако с уменьшением Рп в системе Z происходит более быстрое «разрушение» синхроинформации, чем в системе Y, т.е. при использовании в качестве первичного источника синхроинформации откликов ДС для обнаружения временного положения ЦС, теряется определенное количество информации, имеющейся на приемной стороне (в системе Y). Причем эти потери тем значительнее, чем хуже условия связи и чем больше синхросимволов М в синхрогруппе.

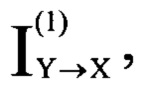

Оптимальный алгоритм поиска ЦС (1*) предполагает суммирование откликов ДС от одних и тех же позиций цикла, т.е. фактически синхроинформация, содержащаяся в откликах ДС, от цикла к циклу суммируется. Используя свойство аддитивности информации [8], можно поставить вопрос: какое количество циклов или цикловых интервалов (ЦИ) Qz необходимо проанализировать ДС на одной и той же позиции цикла, чтобы получить требуемое количество информации, например, равное величине R (в двоичных единицах). Очевидно, что величина Qz будет равна

Если суммирование синхроинформации от цикла к циклу производить в системе Y т.е. от каждого синхросимвола синхрогруппы, т.е. в соответствии с алгоритмом (2*), то для получения того же количества информации о системе X при тех же условиях связи число ЦИ анализа будет равно

Если выигрыш по времени накопления заданного количества синхроинформации в системе Y по отношению к системе Z или выигрыш по времени поиска ЦС (при рассматриваемых способах суммирования синхроинформации) представить в виде отношения величин Qz/QY, то значение этого выигрыша будет полностью будет полостью соответствовать выражению (9)

Таким образом, для определения выигрыша по времени поиска ЦС при конкретном значении Рп>0,5 в случае, когда в качестве источника синхроинфмации не отклики ДС, а символов подобных синхросимволам синхрогруппы, достаточно определить значения величин

В заключении следует отметить, что реализация предлагаемого изобретения - способа цикловой синхронизации для сигналов с сосредоточенной или распределенной по циклу синхрогруппой, при сравнении его с реализацией известного способа - прототипа, в котором в качестве первичного источника синхроинформации, используются отклики опознавателя (дешифратора) синхросигнала, позволяет достичь следующих преимуществ при работе в канале с переменными параметрами:

1. Уменьшение времени поиска ЦС или времени восстановления синхронизма по циклам путем суммирования на каждой позиции цикла не откликов опознавателя синхросигнала, а суммирование всех символов подобных синхросимволам синхрогруппы, используя полную синхроинформацию о каждом синхросимволе синхрогруппы истинным и ложным [5]. При этом поиск временного положения ЦС производится способом, соответствующим оптимальному алгоритму (2*), в соответствии с которым достигается сокращение времени поиска ЦС по отношению с алгоритмом (1*), без ухудшения вероятности ложного обнаружения ЦС.

2. Повышение точности оценки вероятности ошибки синхросимвола Рос экспериментальным способом путем подсчета не количества D искаженных откликов опознавателя синхросигнала в течение S циклов, а количества D' искаженных синхросимволов синхрогрупп в течение S' циклов.. В результате более точно можно оценить экспериментальным способом вероятность ошибки синхросимвола по формуле Рос=D'/MS', как требуется при оптимальном алгоритме поиска ЦС (1*) или (2*), а соответственно и выбирать пороговые числа на основе более точного расчета интервала анализа для работы в канале с переменными параметрами связи с обеспечением требуемой помехоустойчивости и исключения ложных обнаружений ЦС в интервалах времени между соседними сбоями синхронизма по циклам.

3. Уменьшение времени поиска ЦС, если имел место сбой синхронизма по циклам, и уменьшение вероятности ложного срабатывания решающего узла после восстановления канала связи из-за пропадания сигнала или сравнительно длительном воздействии мощных помех в районе приема сигнала за счет обнуления блока памяти решающего узла и блока регистров сдвига при достижении любого результата суммирования на любой из N позиций цикла допустимого значения.

Литература

1. Шадрин Б. Г. Оптимизация алгоритма поиска циклового синхросигнала Техника средств связи. Сер. ТРС, 1983, вып. 10(31), с. 120-125.

2. Кислюк Л.Д. Оптимизация инерционных устройств кадровой синхронизации - Вопросы радиоэлектроники. Сер. ТРС, 1972, вып. 3 с. 35-42.

3. Колтунов М.Н., Коновалов Г.В., Лангуров З.И. Синхронизация по циклам в цифровых системах связи. - М.: Связь, 1980. - 152.

4. Шадрин Б. Г. О необходимом объеме анализируемых данных при оптимальном алгоритме поиска фазы циклового синхросигнала - Техника средств связи. Сер. ТРС, 1984, вып. 10, с. 47-49.

5. Шадрин Б.Г. Сравнительный анализ двух способов накопления синхроинформации при оптимальном алгоритме поиска синхросигнала -Техника средств связи. Сер. ТРС, 1984, вып. 10, с. 43-46.

6. Описание изобретения к авторскому свидетельству СССР №1172052 H04L 7/08 - Устройство для синхронизации по циклам, Опубл. 07.08.1985, Бюл. №29/ Шадрин Б.Г.

7. Соловьев Г.Н. Арифметические устройства ЭВМ. - М.: Энергия, 1978. - 176 с.

8.. Ветцель Е.С.Теория вероятностей. - М.: Наука, 1969. - 576 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ С ПОВЫШЕННОЙ ПОМЕХОУСТОЙЧИВОСТЬЮ | 2020 |

|

RU2752003C1 |

| СПОСОБ ПРИЕМА СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ В УСТРОЙСТВАХ ПРИЕМА СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2020 |

|

RU2747777C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

Изобретение относится к области электросвязи. Техническим результатом является уменьшение времени поиска циклового синхросигнала ЦС и повышение точности его обнаружения. Поиск ЦС или восстановление синхронизма по циклам выполняют путем суммирования на каждой позиции цикла не откликов опознавателя синхросигнала, а суммирования всех символов, подобных синхросимволам синхрогруппы, используя полную синхроинформацию о каждом синхросимволе синхрогруппы, истинном и ложном. Повышение точности оценки вероятности ошибки синхросимвола Рос экспериментальным способом достигается путем подсчета не количества D искаженных откликов опознавателя синхросигнала в течение S циклов, а количества D’ искаженных синхросимволов синхрогрупп в течение S’ циклов. Уменьшение времени поиска ЦС, если имел место сбой синхронизма по циклам, и уменьшение вероятности ложного срабатывания решающего узла после восстановления канала связи при пропадании сигнала или сравнительно длительном воздействии мощных помех в районе приема сигнала достигается за счет обнуления блока памяти решающего узла и блока регистров сдвига при достижении любого результата суммирования на любой из N позиций цикла допустимого значения. 2 з.п. ф-лы, 2 ил.