Изобретение относится к технике цифровой обработки сигналов и может быть использовано в электро и радиосвязи для обнаружения гармонических составляющих дельта-модулированных сигналов.

Целью изобретения является повышение помехозащищенности и точности обнаружения.

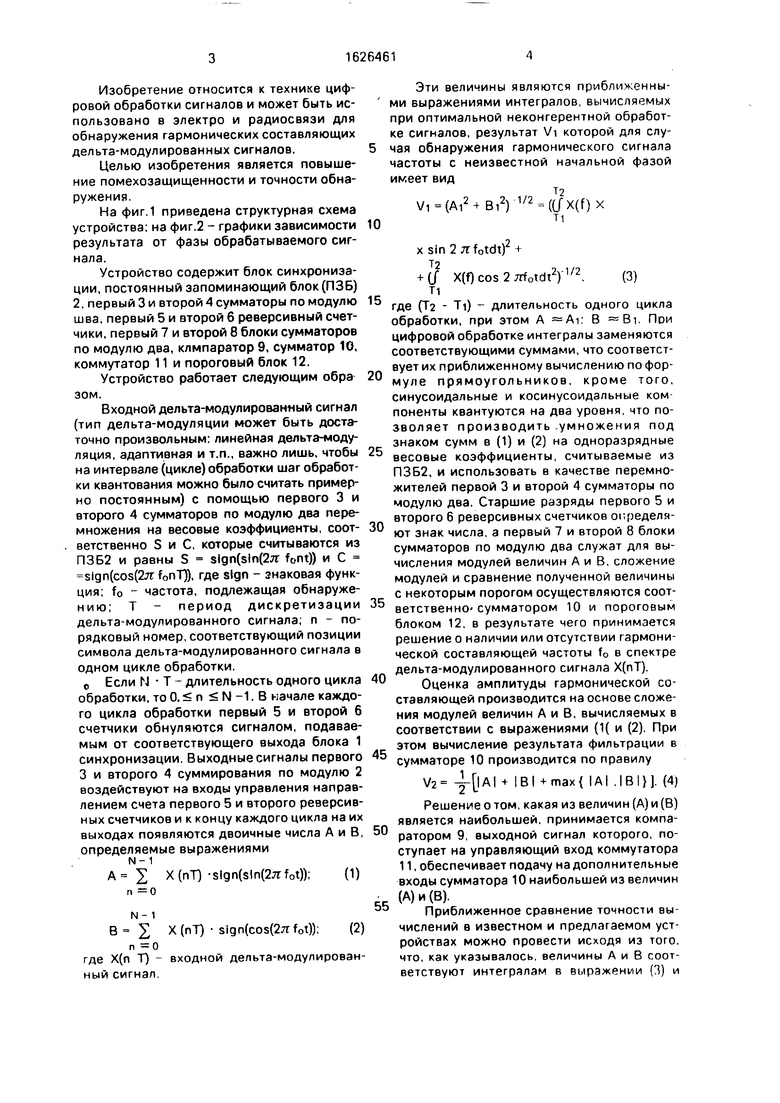

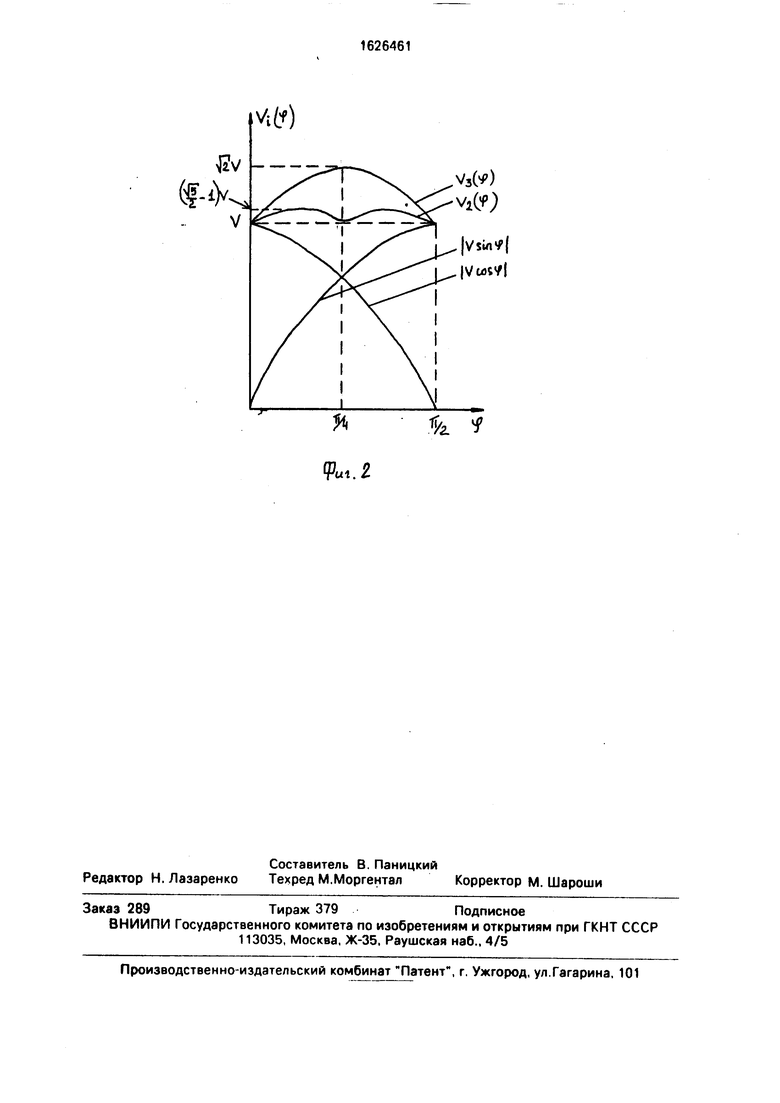

На фиг.1 приведена структурная схема устройства; на фиг.2 - графики зависимости результата от фазы обрабатываемого сигнала.

Устройство содержит блок синхронизации, постоянный запоминающий блок (ПЗБ) 2,первыйЗи второй 4 сумматоры по модулю шва, первый 5 и второй 6 реверсивный счетчики, первый 7 и второй 8 блоки сумматоров по модулю два, клмпаратор 9, сумматор 10, коммутатор 11 и пороговый блок 12.

Устройство работает следующим обра зом.

Входной дельта-модулированный сигнал (тип дельта-модуляции может быть достаточно произвольным: линейная дельта-модуляция, адаптивная и т.п., важно лишь, чтобы на интервале (цикле) обработки шаг обработки квантования можно было считать примерно постоянным) с помощью первого 3 и второго 4 сумматоров по модулю два перемножения на весовые коэффициенты, соответственно S и С, которые считываются из ПЗБ2 и равны S sign(sln(2jr font)) и С slgn(cos(2jr f0nT)), где sign - знаковая функция; f0 - частота, подлежащая обнаружению; Т - период дискретизации дельта-модулированного сигнала; п - порядковый номер, соответствующий позиции символа дельта-модулированного сигнала в одном цикле обработки. 0 Если N -Т - длительность одного цикла обработки, то 0. n N -1. В начале каждого цикла обработки первый 5 и второй 6 счетчики обнуляются сигналом, подаваемым от соответствующего выхода блока 1 синхронизации. Выходные сигналы первого 3 и второго 4 суммирования по модулю 2 воздействуют на входы управления направлением счета первого 5 и второго реверсивных счетчиков и к концу каждого цикла на их выходах появляются двоичные числа А и В, определяемые выражениями

N-1

А- Ј X(nT)-slgn(sln(2;rfot));

(D

п 0

N- 1

Х(пТ) sign(cos(2ttf0t)); (2)

п 0 где Х(п Т) - входной дельта-модулированный сигнал.

Эти величины являются приближенными выражениями интегралов, вычисляемых при оптимальной неконгерентной обработке сигналов, результат Vi которой для слу- чая обнаружения гармонического сигнала частоты с неизвестной начальной фазой имеет вид

Т2

Vi(Ai + В Г)

2 1/2

(Cfx(f)x

Т1

0

5

0

0

5

0

5

(3)

х sin 2 я fotdt)2 +

Т2

+ (/ X(f)cos2 otdt2y1/2. П

где (Та - Ti) - длительность одного цикла обработки, при этом A Ai: В Bi. Пои цифровой обработке интегралы заменяются соответствующими суммами, что соответствует их приближенному вычислению по фор- муле прямоугольников, кроме того, синусоидальные и косинусоидальные ком поненты квантуются на два уровня, что позволяет производить .умножения под знаком сумм в (1) и (2) на одноразрядные весовые коэффициенты, считываемые из ПЗБ2, и использовать в качестве перемножителей первой 3 и второй 4 сумматоры по модулю два. Старшие разряды первого 5 и второго 6 реверсивных счетчиков определяют знак числа, а первый 7 и второй 8 блоки сумматоров по модулю два служат для вычисления модулей величин А и В, сложение модулей и сравнение полученной величины с некоторым порогом осуществляются соот- ветственно-сумматором 10 и пороговым блоком 12. в результате чего принимается решение о наличии или отсутствии гармонической составляющей частоты f0 в спектре дельта-модулированного сигнала Х(пТ).

Оценка амплитуды гармонической составляющей производится на основе сложения модулей величин А и В, вычисляемых в соответствии с выражениями (1( и (2). При этом вычисление результата фильтрации в сумматоре 10 производится по правилу

V2 + IB +max{ IAI ,IBI}. (4)

Решение о том, какая из величин (А) и (В) является наибольшей, принимается компаратором 9, выходной сигнал которого, поступает на управляющий вход коммутатора 11, обеспечивает подачу на дополнительные входы сумматора 10 наибольшей из величин (А) и (В).

Приближенное сравнение точности вычислений в известном и предлагаемом устройствах можно провести исходя из того, что, как указывалось, величины А и В соответствуют интегралам в выражении (3) и

приближенный анализ точности вычислений может быть произведен в области непрерывного времени t.

Подставляя гармонический сигнал X(t) V sirt(2;rf + р) в подинтегральные функции равенства (3) после взятия интегралов, получаем

AI А -г-- (sin Дои - slnp); (5) Bi B -Ј cos p- cos (ДшТ +);(6)

где расстройка относительно частоты, фаза сигнала X(t) при

А V В V sin f и результаты V вычислений, проводимых в известном (Уз) и предлагаемом (V2) устройствах производятся по правилам

V3 V(lcos (f + lsiny |);(7)

V2 j lcosp I + Isinp I +

+ max {Icos p,s ntpty(8)

На фиг.2 приведены зависимости /з( р) и /2(р), где в обоих вариантах сохраняется некоторая зависимость от фазы р. Макси- йальная относительная погрешность вычис- лений для известного устройства составляет V2 1 0,414, в предлагаеVQ

мом устойстве «j - 1 0,115 (экстремум о

находится для /2 подставкой корня уравнеd V

- О в выражение (8), т.е. точность

ния

d p

вычислений в предлагаемом устройстве повышена примерно в 4 раза.

Формула изобретения

Цифровой обнаружит ель гармонических составляющих дельта-модулировэнных сигналов, содержащий последовательно содиненные блок синхронизации и посто- янной запоминающий блок, первый и второй выходы которого соединены соответственно с первыми входами первого и второго сумматоров по модуля два. вторые входы которых являются входом цифрового обнаружителя, последовательно соединенные сумматор, к входам которого подключены выходы первого и второго блоков

сумматоров по модулю 2, и пороговый блок, первый и второй реверсивные счетчики, соответственно объединенные входы сброса и синхронизации которых подключены соответственно к второму и третьему выходам

блока синхронизации, а выходы первого и второго сумматоров по модулю два подключены соответственно к входам управления первого и второго реверсивных счетчиков, выходы старших разрядов которых соединены соответственно с первыми входами первого и второго блоков сумматоров по модулю 2, причем вторые входы первого блока сумматоров по модклю 2 соединены с соответствующими выходами младших разрядов первого реверсивного счетчика, а вторые входы второго блока сумматоров по модулю 2 соединены с соответствующими выходами младших разрядов второго реверсивного счетчика, отличающийся тем,

что, с целью повышения помехозащищенности и точности обранужения. введены последовательно соединенные компаратор, входы которого соединены с выходами первого и второго блоков сумматоров по модулю 2, и коммутатор, выходы которого соединены с дополнительными входами сумматороа. входы которого объединены с информационными входами коммутатора.

V3()

v4cp;

|Vsin {

%.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многочастотный приемник сигналов адаптивной дельта-модуляции | 1989 |

|

SU1626442A1 |

| Цифровой приемник дельта-модулированных сигналов | 1989 |

|

SU1732499A1 |

| Цифровой приемник дельта-модулированных сигналов многочастотных кодов | 1989 |

|

SU1683181A1 |

| Электропривод переменного тока | 1988 |

|

SU1577060A1 |

| Измеритель частоты вращения вала | 1989 |

|

SU1673983A1 |

| МНОГОЧАСТОТНЫЙ ПРИЕМНИК ДЕЛЬТА-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1993 |

|

RU2090981C1 |

| Групповой цифровой приемник многочастотного кода с адаптивной дельта-модуляцией | 1988 |

|

SU1640742A1 |

| Дельта-декодер | 1986 |

|

SU1432779A1 |

| Интеллектуальный счетчик электрической энергии | 2021 |

|

RU2786977C2 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1830632A1 |

Изобретение относится к технике цифровой обработки сигналов и может быть использовано в электро- и радиосвязи для обнаружения гармонических составляющих дельта-модулированных сигналов. Целью изобретения является повышение помехозащищенности и точности обнаружения. Устройство содержит блок 1 синхронизации, постоянный запоминающий блок 2, первый 3 и второй 4 сумматоры по модулю два, первый 5 и второй 6 реверсивные счетчики, первый 7 и второй 8 блоки сумматоров по модулю два, компаратор 9, сумматор 10, коммутатор 11 и пороговый блок 12. Поставленная цель достигаемся введением компаратора 9 и коммутатора 11, обеспечивающих подключение к дополнительным входам сумматора 10 выходов первого 7 или второго 8 блока сумматоров по модулю два в зависимости от их наибольшего значения. 2 ил. Ј

Put. 2

| Брунченко А.В | |||

| Цифровые обнаружители гармонических составляющих для сигналов с адаптивной дельта-модуляцией, - Электросвязь, 1987, № 10, с | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1991-02-07—Публикация

1989-02-20—Подача