Вход

сл

с

Изобретение относится к цифровым приемникам многочастотных кодов с адаптивной дельта-модуляцией. Цель - повышение помехоустойчивости, точности и упрощение устройства. Цель достигается совместным использованием последовательной обработки сигналов при помощи коммутатора 2 адресов и блока 3 оперативной памяти, управляемых задающим генератором 1. Квадратурный прием осуществляется в решающих блоках 5, опорные сигналы которых хранятся в блоке 4 памяти квадратурных компонент. Помехоустойчивость и точность приема обеспечиваются путем формирования адаптивного порога в регистре 10, дешифраторе 11 минимального уровня и формирователе 12 адаптивного порога, 1 ил.

V

ВыхЛ

о

|Ьь

О VI

ND

Изобретение относится к электросвязи и может быть использовано для приема сигналов в каналах тональной частоты.

Цель изобретения - повышение помехоустойчивости и точности приема и упрощение устройства.

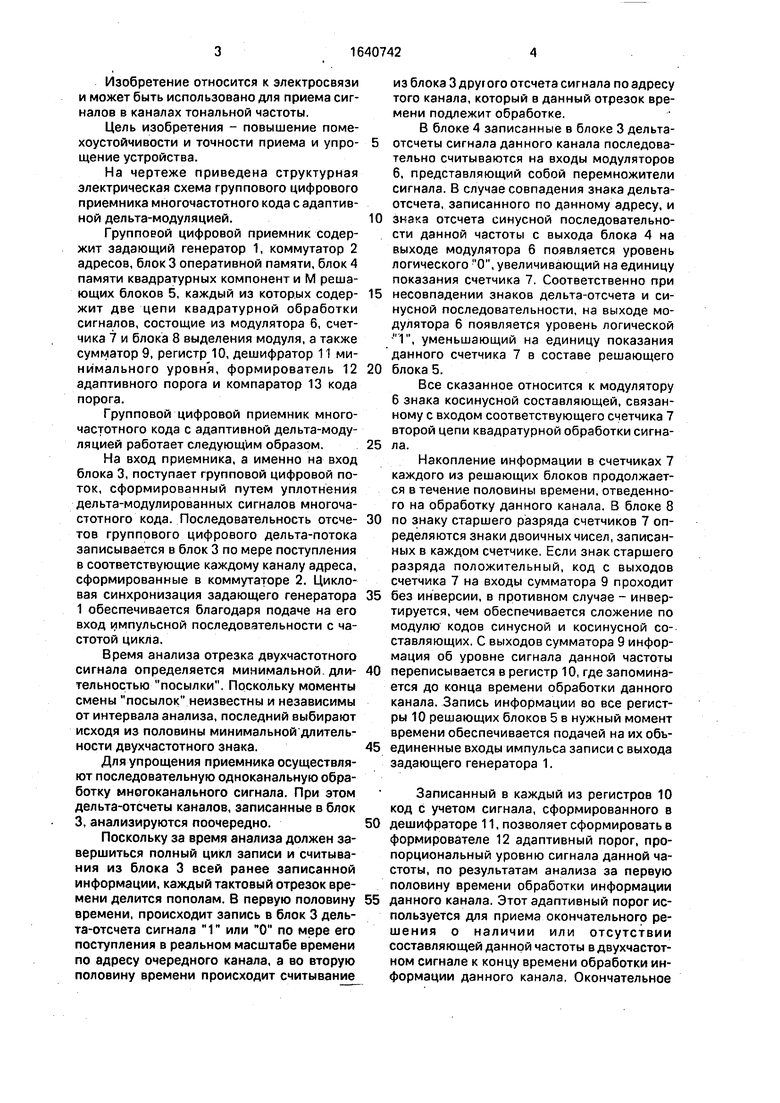

На чертеже приведена структурная электрическая схема группового цифрового приемника многочастотного кода с адаптивной дельта-модуляцией.

Групповой цифровой приемник содержит задающий генератор 1, коммутатор 2 адресов, блок 3 оперативной памяти, блок 4 памяти квадратурных компонент и М решающих блоков 5, каждый из которых содержит две цепи квадратурной обработки сигналов, состощие из модулятора 6, счетчика 7 и блока 8 выделения модуля, а также сумматор 9, регистр 10, дешифратор 11 минимального уровня, формирователь 12 адаптивного порога и компаратор 13 кода порога.

Групповой цифровой приемник многочастотного кода с адаптивной дельта-модуляцией работает следующим образом.

На вход приемника, а именно на вход блока 3, поступает групповой цифровой поток, сформированный путем уплотнения дельта-модулированных сигналов многочастотного кода. Последовательность отсчетов группового цифрового дельта-потока записывается в блок 3 по мере поступления в соответствующие каждому каналу адреса, сформированные в коммутаторе 2. Цикловая синхронизация задающего генератора 1 обеспечивается благодаря подаче на его вход импульсной последовательности с частотой цикла.

Время анализа отрезка двухчастотного сигнала определяется минимальной длительностью посылки. Поскольку моменты смены посылок неизвестны и независимы от интервала анализа, последний выбирают исходя из половины минимальной длительности двухчастотного знака.

Для упрощения приемника осуществляют последовательную одноканальную обработку многоканального сигнала. При этом дельта-отсчеты каналов, записанные в блок 3, анализируются поочередно.

Поскольку за время анализа должен завершиться полный цикл записи и считывания из блока 3 всей ранее записанной информации, каждый тактовый отрезок времени делится пополам. В первую половину времени, происходит запись в блок 3 дельта-отсчета сигнала 1 или О по мере его поступления в реальном масштабе времени по адресу очередного канала, а во вторую половину времени происходит считывание

из блока 3 другого отсчета сигнала по адресу того канала, который в данный отрезок времени подлежит обработке.

В блоке 4 записанные в блоке 3 дельтаотсчеты сигнала данного канала последовательно считываются на входы модуляторов 6, представляющий собой перемножители сигнала. В случае совпадения знака дельта- отсчета, записанного по данному адресу, и

знака отсчета синусной последовательности данной частоты с выхода блока 4 на выходе модулятора б появляется уровень логического О, увеличивающий на единицу показания счетчика 7. Соответственно при

несовпадении знаков дельта-отсчета и синусной последовательности, на выходе модулятора 6 появляется уровень логической , уменьшающий на единицу показания данного счетчика 7 в составе решающего

блока 5.

Все сказанное относится к модулятору 6 знака косинусной составляющей, связанному с входом соответствующего счетчика 7 второй цепи квадратурной обработки сигнала.

Накопление информации в счетчиках 7 каждого из решающих блоков продолжается в течение половины времени, отведенного на обработку данного канала. В блоке 8

по знаку старшего разряда счетчиков 7 определяются знаки двоичных чисел, записанных в каждом счетчике. Если знак старшего разряда положительный, код с выходов счетчика 7 на входы сумматора 9 проходит

без инверсии, в противном случае - инвертируется, чем обеспечивается сложение по модулю кодов синусной и косинусной составляющих. С выходов сумматора 9 информация об уровне сигнала данной частоты

переписывается в регистр 10, где запоминается до конца времени обработки данного канала. Запись информации во все регистры 10 решающих блоков 5 в нужный момент времени обеспечивается подачей на их объединенные входы импульса записи с выхода задающего генератора 1.

Записанный в каждый из регистров 10 код с учетом сигнала, сформированного в

дешифраторе 11, позволяет сформировать в формирователе 12 адаптивный порог, пропорциональный уровню сигнала данной частоты, по результатам анализа за первую половину времени обработки информации

данного канала. Этот адаптивный порог используется для приема окончательного решения о наличии или отсутствии составляющей данной частоты в двухчастот- ном сигнале к концу времени обработки информации данного канала. Окончательное

решение о приеме посылки кода принимается в компараторах 13 решающих блоков 5. Формула изобретения Групповой цифровой приемник многочастотного кода с адаптивной дельта-модуляцией, содержащий задающий генератор, блок памяти квадратурных компонентов и М решающих блоков, каждый из которых содержит две цепи квадратурной обработки сигналов, состоящих из последовательно соединенных модулятора, счетчика и блока вычисления модуля, выходы блоков вычисления модуля цепей синусной и косинусной обработки сигналов подключены к входам сумматора, выходы которого подключены к первым входам компаратора кода порога, выход которого является выходом решающего блока, первыми и вторыми входами которого являются первые входы модуляторов каждой из цепей, вторые входы которых являются соответственно третьим и четвертым входами решающего блока, установочным входом которого являются объединенные установочные входы счетчиков, подключенные к установочному выходу задающего генератора, а первые и вторые входы всех решающих блоков подключены к соответствующим 2М выходам блока памяти квадратурных компонент, отличающийся тем, что, с целью повышения

помехоустойчивости и точности приема и- упрощения устройства, введены коммутатор адресов и блок оперативной памяти, а в каждый из М решающих блоков введены

регистр, дешифратор минимального уровня и формирователь адаптивного порога, причем адресные выходы задающего генератора подключены к попарно объединенным входам блока памяти квадратурны} компонент и коммутатора адресов, выходы которого подключены к адресным входам блока оперативной памяти, выход которого подключен к объединенным третьим и четвертым, входам всех решающих блоков,

тактовые входы задающего генератора, блока памяти квадратурных компонент, коммутатора адресов и блока оперативной памяти объединены, а управляющий выход задающего генератора подключен к входам записи всех решающих блоков, в которых он является входом записи регистра, входы которого подключены к выходам сумматора, выходы регистра подключены к попарно объединенным входам формирователя

адаптивного порога и дешифратора минимального уровня, выход которого подключен к управляющему входу формирователя адаптивного порога, выходы которого подключены к вторым входам компаратора кода

порога.

| Брунченко А.В., Охинченко Е.П | |||

| Цифровые обнаружители гармонических составляющих для.сигналов с адаптивной дельта-модуляцией | |||

| - Электросвязь, 1987, № 10. |

Авторы

Даты

1991-04-07—Публикация

1988-12-21—Подача