;/

f

,. ,...-. ,,-.

{ Ф у Jk

32

JM

| название | год | авторы | номер документа |

|---|---|---|---|

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| Кодек системы связи | 1983 |

|

SU1150770A1 |

| Устройство связи с дельта-модуляцией | 1983 |

|

SU1095395A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Дельта-демодулятор | 1984 |

|

SU1269270A1 |

| Многоканальная кодоимпульсная система телесигнализации | 1986 |

|

SU1325544A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

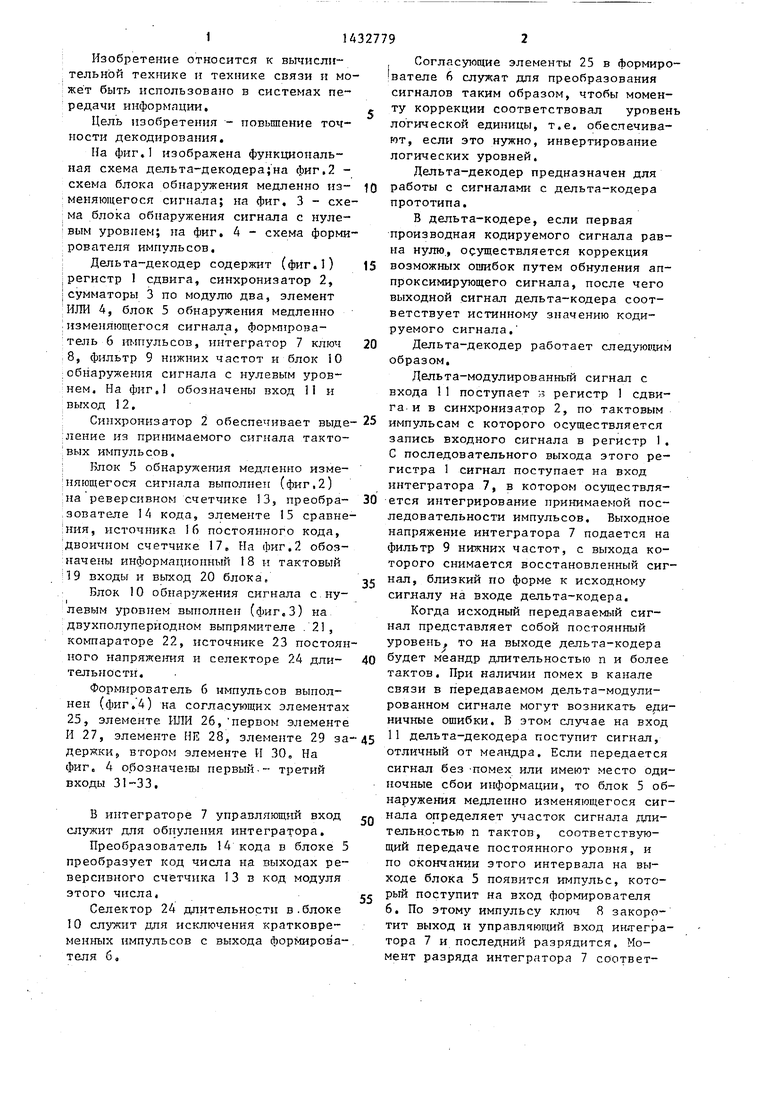

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи информации позволяет повысить точность декодирования. Дельта-декодер содержит регистр I сдвига, синхронизатор 2, сумматоры 3 по модулю два, формирователь 6 импульсов, интегратор 7, ключ 8 и фильтр 9 нижних частот. Благодаря введению элемента ИЛИ 4, блока 5 обнаружения медленно изменяющегося сигнала и блока 10 обнаружения сигнала с нулевым уровнем коррекция в дельта-декодере обеспечивается даже при наличии единичных сбоев в дельта-модулированном сигнале. 3 з.п. ф-лы, 4 ил.

Изобретение относится к вьпшсли- тельной технике и технике связи п мо :жет быть использовано в системах передачи информации.

Цель изобретения - повышение точности декодирования.

На фиг,1 изображена функциональная схема дельта-декодера;на фиг,2 - схема блока обнаружения медленно изменяющегося сигнала; на фиг, 3 - схема блока обнаружения сигнала с нуле- вым уровнем; на фиг, 4 - схема форми :рователя имнульсов, ; Дельта-декодер содержит (фиг,1) I регистр 1 сдвига, синхронизатор 2, I сумматоры 3 по модулю два, элемент I ИЛИ 4, блок 5 обнаружения медленно I изменяющегося сигнала, формирова- ;тель б т-1пульсов, интегратор 7 ключ .8, фильтр 9 нижних частот и блок 10 ;обнаружения сигнала с нулевым уровнем. На фиг, обозначены вход 11 и выход 12,

Синхронизатор 2 обеспечивает выде- 25 импульсам с которого осуществляется

:ление из принимаемого сигнала такто- ;вых импульсов.

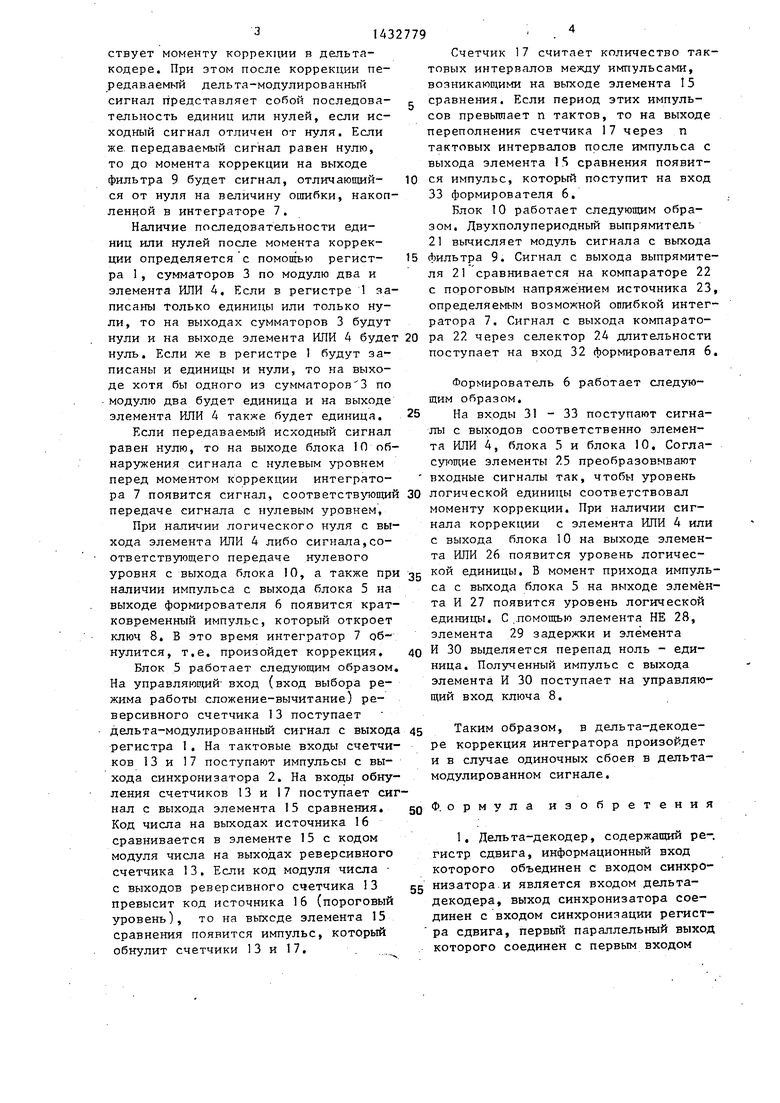

Блок 5 обнаружеттоя медленно изме- ;няющегося сигнала выполнен (фиг,2) ;На реверсивном счетчике 13, преобра- :3ователе 14 кода, элементе 15 сравне- ;ния, источника 16 постоянного кода, двоичном счетчике 17, На фиг,2 обозначены информационный 18 и тактовый 19 входы и выход 20 блока.

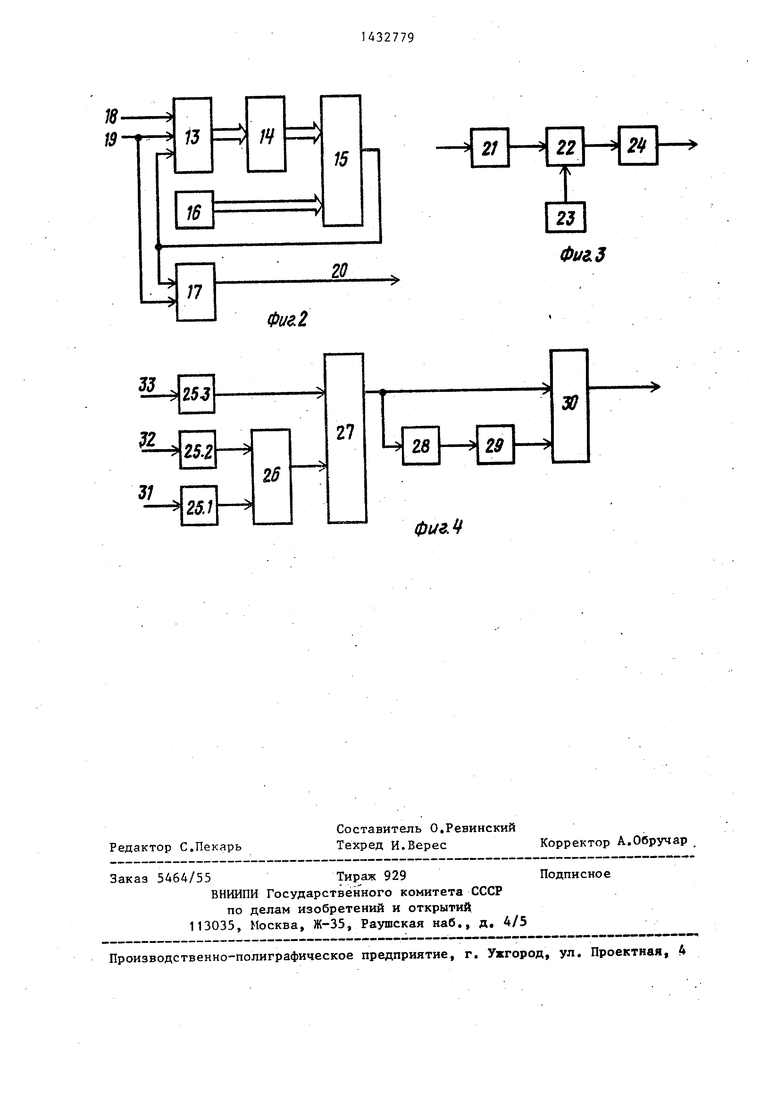

Блок 10 обнаружения сигнала с нулевым уровнем выполнен (фиг.З) на двухполупериодном выпрямителе .21, компараторе 22, источнике 23 постоянного напряже1тая и селекторе 24 дли- тельност.

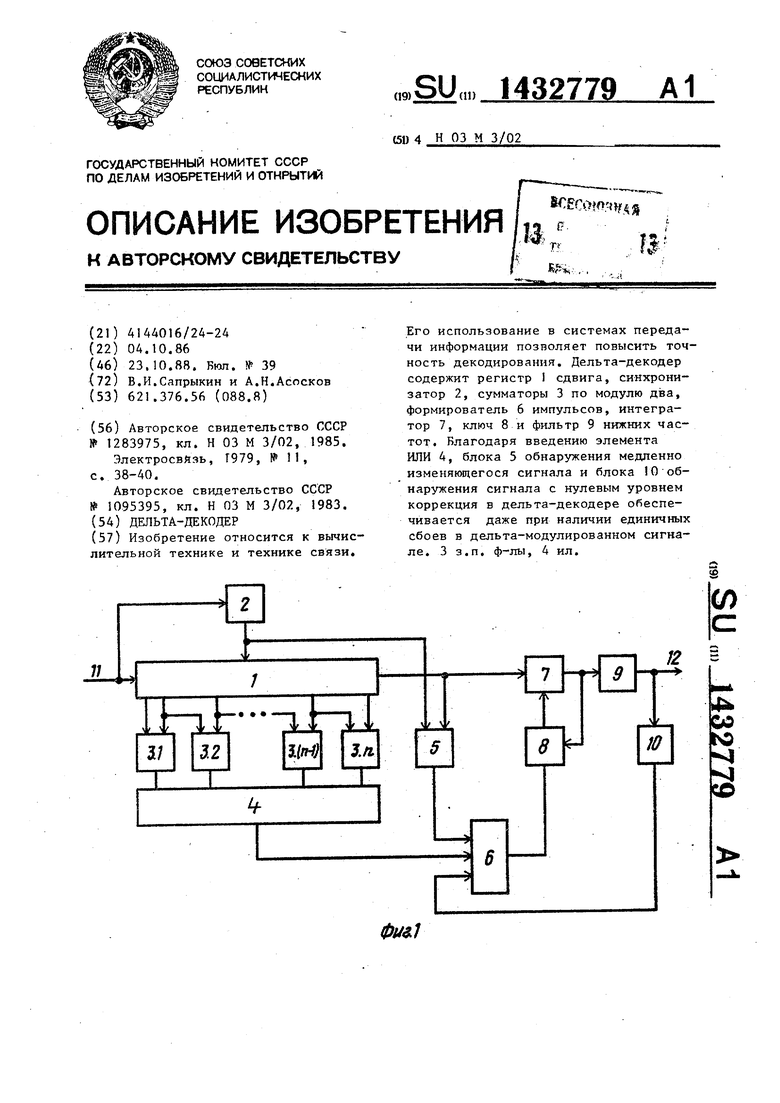

Формирователь б импульсов выполнен (фиг.4) на согласующих элементах 25, элементе ИЛИ 26, первом элементе

30

35

40

запись входного сигнала в регистр 1 С последовательного выхода этого регистра 1 сигнал поступает на вход интегратора 7, в котором осуществляется интегрирование принимаемой последовательности импульсов. Выходное напряжение интегратора 7 подается на фильтр 9 нижних частот, с выхода которого снимается восстановленный сиг нал, близкий по форме к исходному сигналу на входе дельта-кодера.

Когда исходный передаваемый сигнал представляет собой постоянный уровень, то на выходе дельта-кодера будет меандр длительностью п и более тактов. При наличии помех в канале связи в передаваемом дельта-модули- рованном сигнале могут возникать еди ничные ошибки, Б этом случае на вход

И 27, элементе НЕ 28, элементе 29 за-45 дельта-декодера поступит сигнал, деркки, втором элементе И 30„ На фиг, 4 обозначены первый-- третий входы 31-33,

отличный от меандра. Если передается сигнал без Помех или имеют место оди ночные сбои информации, то блок 5 об наружения медленно изменяющегося сиг нала определяет участок сигнала дпи- тельностью п тактов, соответствующий передаче постоянного уровня, и по окончании этого интервала на выходе блока 5 появится И1-1пульс, который поступит на вход формирователя 6, По этому импульсу ключ 8 закоротит выход и управляющий вход ин.тегра тора 7 и последний разрядится. Момент разряда интегратора 7 соответВ интеграторе 7 управляющий вход служит для обнуления интегратора.

Преобразователь 14 кода в блоке 5 преобразует код числа на выходах реверсивного счетчика 13 в код модуля этого числа.

Селектор 24 длительности в.блоке 10 служит для исключения кратковременных импульсов с выхода формирователя 6,

, Согласующие элементы 25 в формирователе 6 служат для преобразования сигналов таким образом, чтобы момен- ту коррекции соответствовал уровень логической единицы, т.е, обеспечивают, если это нужно, инвертирование логических уровней.

Дельта-декодер предназначен для работы с сигналамк с дельта-кодера прототипа,

В дельта-кодере, если первая производная кодируемого сигнала равна нулю, осуществляется коррекция возможных ошибок путем обнуления аппроксимирующего сигнала, после чего выходной сигнал дельта-кодера соответствует истинному значению кодируемого сигнала,

Дельта-декодер работает следуювшм образом,

Дельта-модулированный сигнал с входа 1 1 поступает :.з регистр 1 сдвига и в синхронизатор 2, по тактовым

импульсам с которого осуществляется

0

5

0

запись входного сигнала в регистр 1, С последовательного выхода этого регистра 1 сигнал поступает на вход интегратора 7, в котором осуществляется интегрирование принимаемой последовательности импульсов. Выходное напряжение интегратора 7 подается на фильтр 9 нижних частот, с выхода которого снимается восстановленный сигнал, близкий по форме к исходному сигналу на входе дельта-кодера.

Когда исходный передаваемый сигнал представляет собой постоянный уровень, то на выходе дельта-кодера будет меандр длительностью п и более тактов. При наличии помех в канале связи в передаваемом дельта-модули- рованном сигнале могут возникать единичные ошибки, Б этом случае на вход

дельта-декодера поступит сигнал,

отличный от меандра. Если передается сигнал без Помех или имеют место одиночные сбои информации, то блок 5 обнаружения медленно изменяющегося сигнала определяет участок сигнала дпи- тельностью п тактов, соответствующий передаче постоянного уровня, и по окончании этого интервала на выходе блока 5 появится И1-1пульс, который поступит на вход формирователя 6, По этому импульсу ключ 8 закоротит выход и управляющий вход ин.тегра- тора 7 и последний разрядится. Момент разряда интегратора 7 соответствует моменту коррекции в дельта- кодере. При этом после коррекции передаваемый дельта-модулированнъш сигнал представляет собой последовательность единиц или нулей, если исходный сигнал отличен от нуля. Если же передаваемый сигнал равен нулю, то до момента коррекции на выходе фильтра 9 будет сигнал, отличающийся от нуля на величину ошибки, накопленной в интеграторе 7.

Наличие последовательности единиц или нулей после момента коррекции определяется с помощью регистра 1 , сумматоров 3 по модулю два и элемента ИЛИ 4. Если в регистре 1 записаны только единицы или только нули, то на выходах сумматоров 3 будут

нули и на выходе элемента ИЛИ 4 будет 20 ра 22 через селектор 24 длительности

нуль. Если же в регистре 1 будут записаны и единицы и нули, то на выходе хотя бы одного из сумматоров 3 по модулю два будет единица и на выходе элемента ИЛИ 4 также будет единица.

Если передаваемый исходный сигнал равен нулю, то на выходе блока 1 Г) обнаружения сигнала с нулевым уровнем перед моментом коррекции интегратопоступает на вход 32 формирователя 6.

Формирователь 6 работает следующим образом.

25

На входы 31 - 33 поступают сигналы с выходов соответственно элемента ИЛИ 4, блока 5 и блока 10. Согласующие элементы 25 преобразовывают входные сигналы так, чтобы уровень ра 7 появится сигнал, соответств топхий 30 логической единицы соответствовал передаче сигнала с нулевым уровнем, моменту коррекции. При наличии сиг- При наличии логического нуля с вы- нала коррекции с элемента ИЛИ 4 или

хода элемента ИЛИ 4 либо сигнала,соответствующего передаче нулевого уровня с выхода блока 10, а также при наличии импульса с выхода блока 5 на выходе формирователя 6 появится кратковременный импульс, который откроет ключ 8. В это время интегратор 7 об- нулится, т.е. произойдет коррекция.

Блок 5 работает следующим образом. На управляющий вход (вход выбора режима работы сложение-вычитание) реверсивного счетчика I3 поступает дельта-модулированньй сигнал с выхода регистра I. На тактовые входы счетчиков 13 и 17 поступают импульсы с выхода синхронизатора 2. На входы обнуления счетчиков 13 и 17 поступает сиг

нал с выхода элемента 15 сравнения. Код числа на выходах источника I6 сравнивается в элементе 15 с кодом модуля числа на выходах реверсивного счетчика 13. Если код модуля числа - с выходов реверсивного счетчика 13 превысит код источника 16 (пороговый уровень), то на выходе элемента 15 сравнения появится импульс, который обнулит счетчики 13 и 17.

Счетчик 17 считает количество тактовых интервалов между импульсами, возникаюпдими на выходе элемента 15

сравнения. Если период этих импульсов превьппает п тактов, то на выходе переполнения счетчика 17 через п тактовых интервалов после импульса с выхода элемента 15 сравнения появится импульс, который поступит на вход 33 формирователя 6.

Блок 10 работает следующим образом. Двухполупериодный выпрямитель 21 вычисляет модуль сигнала с выхода

фильтра 9. Сигнал с выхода выпрямителя 21 сравнивается на компараторе 22 с пороговым напряжением источника 23, oпpeдeляe ы возможной опгибкой интегратора 7. Сигнал с выхода компаратопоступает на вход 32 формирователя 6.

Формирователь 6 работает следующим образом.

25

30

с выхода блока 10 на выходе элемента ИЛИ 26 появится уровень логической единицы. В момент прихода импульса с выхода блока 5 на выходе элемента И 27 появится уровень логической единицы. С.ломощью элемента НЕ 28, элемента 29 задержки и элемента

т - /

И 30 выделяется перепад ноль - единица. Полученный импульс с выхода элемента И 30 поступает на управляющий вход ключа 8.

45 Таким образом, в дельта-декодере коррекция интегратора произойдет и в случае одиночных сбоев в дельта- модулированном сигнале.

50

Ф. ормула изобретения

1, Дельта-декодер, содержащий ре-. гистр сдвига, информационный вход которого объединен с входом синхро- 55 низатора и является входом дельта- декодера, выход синхронизатора соединен с входом синхронизации регист- ра сдвига, первый параллельный выход которого соединен с первым входом

первого сумматора по модулю два, i-й параллельный выход регистра сдви- га (г 2,п, -п - число тактов за время анализа входного сигнала) сб.- динен с первым входом г-го и вторым .входом ()-ro сумматоров по модутпо два, (ri+1)-параллельный выход регистра сдвига соединен с вторым входом Iп-го сумматора по модулю два,интег- ;ратор, выход Которого подключен к информационному входу ключа и входу : фильтра нижних частот, выход которо- ; го является выходом дельта-декодера, ; формирователь импульаов, выход кото- ; рого соединен с управляющим входом ; ключа, выход которого подключен к управляющему входу интегратора, о т- л и ч а ю щ и и с я тем, что, с целью ловьшения точности декодирова- : ния, в дельта-декодер введены элемент ИЛИ, блок обнаружения сигнала с нулевым уровнем и блок обнаружегшя медленно изменяющегося сигнала, информационный вход которого объединен с информационным входом интегра- : тора и подключен к последовательному : выходу регистра сдвига, тактовый I вход блока обнарз ения медленно из- 1 меняющегося сигнала подключен к вы- ; ходу синхронизатора, вход Гхпока об- наружения сигнала с нулевым уровнем : подключен к выходу фильтра нижних : частот, выходы первого - п-го сум- . маторов по модулю два соединены с входами элемента ИЛИ, выход которого и выходы блока обнаружения медленно изменяющегося сигнала и блока обнаружения сигнала с нулевым уровнем подключены соответственно к первому - - третьему входам формирователя импульсов,2. Дельта-декодер по п . 1 , о т л и- чающийся тем, что блок обнаружения сигнала с медленно изменяющимся, уровнем выполнен на реверсивт ном счетчике, преобразователе кода, элементе сравнения, источнике постоянного кода и двоичном счетчике, счетный вход которого объединен со счет143,27796

HiiiM входом реверсивного счетчика и является тактовым входом блока, управляющий вход реверсивного счетчика явJ. ляется информационным входом блока, выходы реверсивного счетчика через преобразователь кода, подключены к первым входам элемента сравнения, выходы источника постоянного кода соедиig иены с вторыми входами элемента сравнения, выход которого подключен к входам обнуления реверсивного счетчика и двоичного счетчика, выход переполнения которого является выходом

15 блока,

25 напряжения подключены соответственно к первому и второму входам компаратора, выход которого соединен с входом селектора длительности, выход которого является выходом блока,

30 4,Дельта-декодер по п,1, о т л и- ч а.ющийся тем, что формирова- тапь импульсов выполнен на элементах И, элементе ИЛИ, последовательно соединенных элементе НЕ и элементе

35 задержки, первом - третьем согласующих, элементах, входы которьгх являются соответственно первым - третьим входами формирователя, выходы первого, второго и третьего согласующих

40 элементов соединены соответственно с первым входом первого элемента И и с первым и вторым входами элемента ИЛИ, выход которого подключен к второму входу первого элемента И, выход

45 которого соединен с первым входом второго элемента И и входом элемента НЕ, выход элемента задержки подключен к второму входу второго элемента И, выход которого является выходом фор50 мирователя.

| Авторское свидетельство СССР № 1283975, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Злектросвйзь, Г979, №11, с | |||

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

| Устройство связи с дельта-модуляцией | 1983 |

|

SU1095395A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-23—Публикация

1986-10-04—Подача