о

00

00

Ј

со

А

Изобретение относится к электросвязи и может быть использовано в системах передачи сигналов многочастотными кодами 2 из б (2 из 0).

Цель изобретения -- повышение достоверности приема путем устранения ложных срабатываний.

На фиг.1 приведена структурная электрическая схема предложенного приемника; на фиг.2 -- структурная электрическая схема анализатора числа срабатываний; на фиг.З и 4 - представлены диаграммы работы приемника.

Цифровой приемник дельта-модул и DO- ванных сигналов многочастотных кодов содержит блок 1 синхронизации, первые, второе третье и четвертое оперативные запоминающие устройства ОЗУ 2,3,Л и 5, постоянное запоминающее устройство ПЗУ б, рзверсизный счетчик 7, лвомчн jfl счетчик О, дешифратор 9, блок 10 стробирования, элемент ИЛИ 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, блок, 13 объединения, блок 14 сравнения, счетчик 15 числа срабатываний, регистр 16, анализатор 17 числа срабатываний и блок 18 фиксации результата.

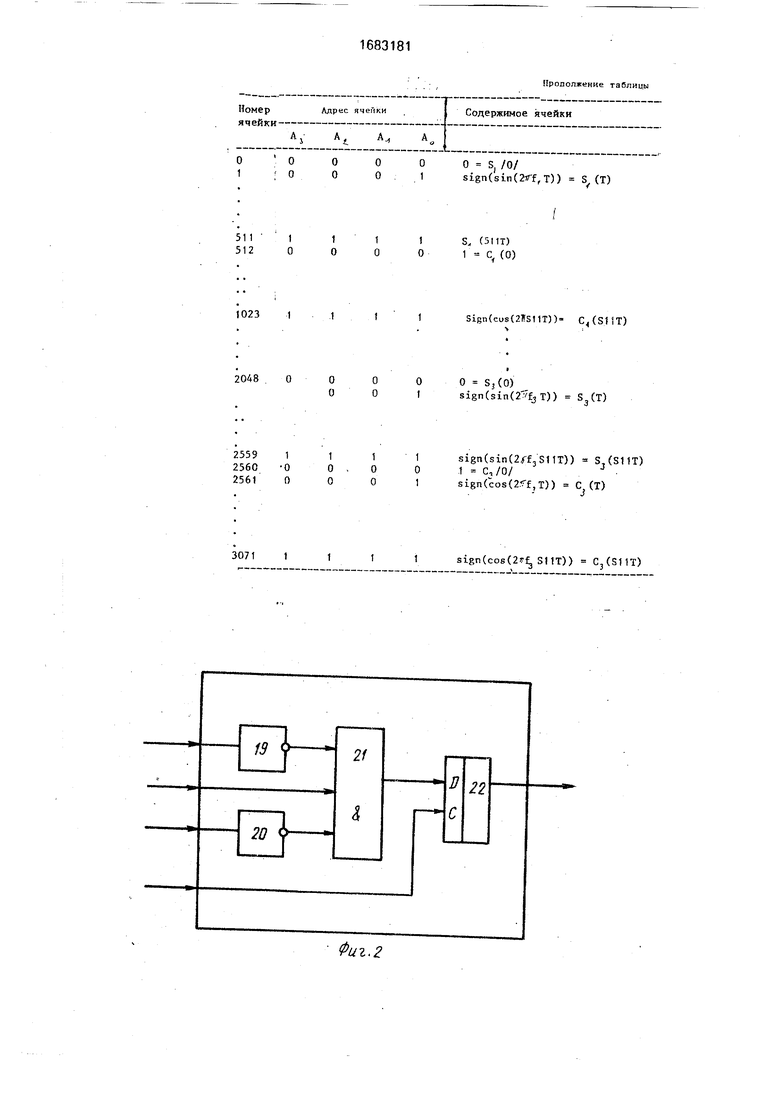

Анализатор числа срабатываний содержит первый и второй инверторы 19 и 20, элемент И 21 и Д-триггер 22.

Приемник работает следующим образом.

Сигналы многочастотного кода 2 из 6 (2 из 8), преобразованные в цифровую форму на базе дельта-модуляции с инерционным компанированием (адаптивной дельта-модуляции АДМ) поступают параллельно,на информационные входы первого и второго ОЗУ 2 и 3. Длительность одного символа х(пТ) АДМ - сигнала (фиг.35) равна периоду T-f 10 соответствующей тактовой частоты f0 (fo показана на фиг.За). Сигналы x(nT), f о (фиг.За.б) показаны в увеличенном масштабе.

Обработка последовательности х(пТ) ведется циклами, по N символов в каждом цикле (например, можно принять N-512, что при кГц соответствует длительности Тц одного цикла обработки 1 б мс). Для обеспечения работы в реальном масштабе временя ОЗУ 2,3 работают 53 противофазе - если в 1-м цикле Тц запись текущей информации производится в ОЗУ 2, то в этом же цикле из ОЗУ 3 производится считывание информации, накопленной в нем в (1-1)- -м цикле и наоборот. Такой режим обеспечивается подачей не ОЗУ 2,3 соответствующих сигналов от второй и третьей групп адресных выходов блока 1 синхронизации (его структура будет рассмотрена позднее). Для примера на фиг.З в,г показаны наиболее

высокочастотные адресные сигналы для ОЗУ 2,3 - А12 (фиг.З г.) и Ai3 (фиг.Зе) соответственно, и наиболее низкочастотные - АК2 (фиг.Зв) и АкЗ (фиг.Зд), а также сигнал (W/R)2 (фиг.Зж)управления режимом записи - считывания для ОЗУ 2 (0 - запись, 1 - считывание).

В рассмотренном варианте предусмотрена обработка потока х(пТ) в восьми частотных каналах. При этом за время одного 1-го цикла Тц обработки из ОЗУ 2 (или ОЗУ 3) 16 раз подряд производится считывание бит сигнала х(пТ), поступивших на

вход устройства в предыдущем (1-1)-м цикле. Структура сигналов на выходе ОЗУ 2,3 показана на фиг.3з,и. Прием одной частотной составляющей производится за время (1/8) Тц, за это время указанные бит считываются

из соответствующего ОЗУ 2 или 3 раза подряд и поступают на согласованный фильтр (коррелятор), построенный на ПЗУ 6, элементе 12 ИСКЛЮЧАЮЩЕЕ ИЛИ, двоичном 8 и реверсивном 7 счетчике и дешифраторе

9. Работа корреляционного фильтра при приеме одной частотной составляющей заключается в вычислении величины

N -1 3(5 Fi l2 x(nT)(2jrflnT)l +

n 0

N -1

+I2 x(nT)slgn(cos(2rcflnT)i (1)

где FI - результат обработки в f-м частотном канале. В равенстве (1) подразумевается, что величины х (пТ), sign (.) (знак числа) принимают значение ± I. На практике отрицательные значения отображаются яогиче- ским нулем и равенство (1) приводится к виду

45

Fi l 2 x(nTXjjSi(nT)(nT)g)

©S,(nT)}l-H21{(rtT)(i)

50

@Ci(nT)(nT)©Ci(nT)}l (2)

где f - операция ИСКЛЮЧАЮЩЕЕ ИЛИ (реализуется на элементе 12), a Sf(nT), Cs(nT) - последовательности значений соответствующих знаковых функций в(1), в который отрицательные значения отображаются логическим нулем. Далее равенство (2) приводится к виду

Fi 2 I N/2- Sci I + I N/2- Ceil (3) где

Sci 2 О Т )i (nTУ (4)

n 0

cci NE1 ( т} iЈ)Q (rnr} (5)

n 0

Значения Si, Ci для каждой частоты fi хранятся в ПЗУ 6. Ниже приводится пример размещения информации в ПЗУ 6. При частоте дискретизации д ел ьта-мо дули ро ванного сигнала х(пТ)32 гКц и длительности цикла обработки 16 мс в каждом цикле обрабатывается N-512 бит сигнала х(пТ), и для каждой выделяемой частотной составляющей fi в ПЗУ 6 должно в соответствии с выражением (1) хранится 512x2 в однобитных весовых коэффициентов, соответствующих величинам sign sin ( 2 л fi nT) и sign cos (2 n fi nT).

При количестве выделяемых частот fi, равном, например, 8, требуемый обьем ПЗУ 6 равен таким образом 512x2x8 7 кБайт.

В приведенной таблице дано содержимое тех ячеек ПЗУ, в которых хранятся весовые коэффициенты, обеспечивающие прием частот fi, fa (интервалы tg - tio и tn - 112 на фиг.Зн). Для остальных частот ячейки ПЗУ 6 заполняются аналогичным образом. Нулевые и отрицательные значения знаковых функций sign(.) задаются, как уже отмечалось, логическими нулями. В соответствии с вычислениями по равенству (3) в начале каждого интервала (1/8) Тц (фиг.Зз), в котором производится прием одной частоты (например, пусть на интервале tg - tio (фиг.Зн)) производится прием частоты fi (в реверсивный счетчик 7 записывается число N, а двоичный счетчик 8 обнуляется. Сигналы Уз, Uj разрешающие обнуление и установку и формируемые в блоке 1 синхронизации, показаны на фиг.З к;л, соответственно. На элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12 в первой половине интервала tg - tio из ПЗУ 6 считываются значения Si(nT), а во второй Ci(nT), и в течение каждой половины указанного интервала считываются N значений сигнала х(пТ), накопленные за предыдущий цикл Тц,

В каждом такте работы счетчиков 7,8 разрешается лишь в том случае, если выходной сигнал элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 равен нулю, то есть когда значения х(пТ) и S i (nT)/ или Ci (nT)/ одинаковы. При это-M в начале первой половины интервала из ПЗУ 6 считываются значения Si (nT), a реверсивный счетчик 7 работает на вычитание тактовых импульсов, что продолжается

до тех пор, пока на выходе двоичного счетчика 8 не появится число N/2, после чего сработает дешифратор 9 и направление счета меняется на прямое. В начале второй 5 половины интервала tg - tio двоичный счетчик 8 снова обнуляется сигналом Уз (фиг.Зк) и реверсивный счетчик 7 снова начинает работать на вычитание до тех пор, пока на выходе двоичного счетчика 8 не накопится 10 число IS1/2, после чего направление счета меняется на прямое. Такой алгоритм работы обеспечивает формирование на выходе реверсивного счетчика 7 к концу интервала tg - tio величины FJ /2, где Fi определяется

5 равенством (3) (при ).

Результат обработки на интервале tg - Но фиксируется в блоке 10 стробирования, на который подается сигнал U4 (фиг.Зм) от блока 1 синхронизации, стробированиеосу0 ществляется передним фронтом этого сигнала. Очевидно что для того, чтобы избежать сбоев импульсы Ui (фиг.Зл) разрешения установки реверсивного счетчика 7 должны быть слегка задержаны относительно пере5 дних фронтов сигнала Щ (фиг.Зм). Таким образом, результат обработки на частоте fi, проведенный на интервале tg - tio. присутствует на выходе блока 10 стробирования в течение следующего интервала tio - tn

0 (фиг.Зн). Аналогично производится обработка отрезка сигнала х (пТ) и в других частотных каналах с той разницей, что на интервале tio - tit из ПЗУ 6 считываются весовые коэффициенты SafnT), C2(nT) для

5 следующей частоты f2, на интервале tn - ti2 для частоты f 3 т.д. Все результаты обработки за один цикл Тц по всем частотам записываются в одно из ОЗУ 4 и 5, которые также, как и ОЗУ 2,3 работают в противофа0 зе - если в i-м цикле осуществляется запись в ОЗУ 4, то из ОЗУ 5 производится считывание, и наоборот.

Выходные сигналы ОЗУ 2,3 поступают на блок 13 объединения, с выхода которого

5 информация теперь считывается непрерывно в каждом цикле, либо из ОЗУ 4 либо из ОЗУ 5 (для ОЗУ 2,3 аналогичную функцию выполнял элемент ИЛИ 11). Считывание производится с существенно более высокой

0 частотой, чем запись. За время (фиг.4а), равное длительности одного символа сигнала х(пТ) на входе устройства, через блок 13 объединения от одного из ОЗУ 4 и 5 последовательно считываются результаты

5 обработки (Ui3, фиг.4б) на всех частотах, то же повторяется и в следующих интервалах , таким образом в течение одного цикла Тц результаты обработки на всех частотах в предыдущем цикле Тц считываются раз подряд. Наиболее высокочастотный адресный сигнал, подаваемый на то из ОЗУ 4 и 5, из которого в данном цикле производится считывание, показан на фиг.4в (сигнал частоты 4fo). В каждом интервале f o (фиг.4а) в течение одного цикла Тц от шестой группы адресных выходов блока 1 синхронизации на блок 14 сравнения поступают двоичные числа, соответствующие определенным значениям порогов Pi срабатывания, с нарастанием от минимальных значений в начале цикла Тц к максимальным значениям в конце цикла, которые сравниваются в блоке 14 с результатами фильтрации на различных частотах (Uia, фиг.4б), поступающим в каждом интервале fо 1 с выхода блока 13 объединения. В результате сравнения формируются однобитные значения (0 или 1), говорящие о наличии или отсутствии срабатывания в каком-либо частотном канале при данном значении порога Р. Подсчет числа срабатываний на каждом временном интервале fo (фиг.4а) производится счетчиком 15, обнуляемым в начале каждого интервала fo короткими импульсами. Us (фиг.4д), поступающими с пятого тактового выхода блока 1 синхронизации, Счет производится по передним фронтам сигнала 1)б (фиг,4е), подаваемого на тактовый вход счетчика 15 числа срабатываний от шестого тактового выхода блока 1 синхронизации, и происходит лишь в тех случаях, когда на его вход разрешения счета подается высокий уровень сигнала с выхода блока 14 сравнения в текуа м интервале

At 1/8 fo 1 (фиг,4г). Также передними фронтами сигнала Ue (фиг,4е) выходная информация блока 14 сравнения на каждом интервале f0 (фиг.4а) последовательно вписывается в регистр 16, на выходе которого к концу каждого интервала fo (фиг,4а) будет s параллельном позиционном коде появляться информация о количестве и номере частотных каналов, в которых произошло срабатывание (прием частоты) при текущем значении порога. Выходной сигнал счетчика 15 числа срабатываний поступает на информационный вход анализатора 17 числа срабатываний, тактируемым сигналом U (фиг.4ж) подается с седьмого выхода блока 1 синхронизации. К концу интервала (фиг,4а) единица появится нз выходе элемента 21 И только в том случае, если на вход анализатора 17 поступает число 2 (010 в двоичной форме), и только в этом случае сработа ет Д-триггер 22, например, ка интервале Ti количество срабатываний (сигнал DM, фиг.4г) равнялось трем на частотах f 1, f 4, s), поэтому к моменту ti стробирова- ния число на выходе счетчика 15 равняется

трем (001), на выходе элемента И 21 нулевой сигнал и Д-триггер 22 остается в нулевом состоянии. На интервале Т2 (фиг.4е) на блок 14 сравнения от шестой группы выходов

блока 1 синхронизации поступает новое значение порога Р, большее, чем на интервале Ti, и срабатывание на частоте, имевшей наиболее низкий уровень изтрех(1 i,f 4,fs), устраняется. В результате к моменту t2

0 (фмг.4ж) на выходе счетчика 15 срабатываний присутствует число 2 (010) и Д-триггер 22 устанавливается в единичное состояние. К этому же моменту информация о номерах двух сработавших частот (f 1, fa) в виде пози5 цмонного кода присутствует на выходе регистра 16, откуда она переписывается в блок 18 фиксации результата передним фронтом выходного сигнала .4з) анализатора 17 числа срабатываний, где и удерживается

0 до окончания текущего цикла обработки Тц. В начале каждого последующего цикла Тц блок 18 фиксации результата обнуляется коротким импульсом с восьмого тактового выхода блока 1 синхронизации. Таким

5 образом в каждом цикле обработки Тц на выходе устройства (на выходе блока 18 фиксации результата) появляется информация о срабатывании на двух частотных составляющих входного сигнала, имеющих наиболь0 шие уровни по сравнению с другими. Формула изобретения Цифровой приемник дельта-модулиро- ванных сигналов многочастотных кодов, содержащий блок синхронизации, вторая и

5 третья группы адресных выходов которого соединены с адресными входами соответственно первого и второго оперативных запоминающих устройств, выходы которых подключены через элементы ИЛИ к первому

0 входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу постоянного запоминающего устройства, вход которого соединен с первой группой адрес- гшх выходов блока синхронизации, первый

5 тактовый выход которого соединен s входом начальной установки реверсивного счьтчи- ка, вход разрешения счета которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к выходу разрешения счета двоично0 го счетчика, вход установки нуля которого подключен к третьему тактовому выходу блока синхронизации, второй тактовый выход которого соединен с тактовым входом даоичного счетчика и с тактовым входом ре5 версивного счетчика, вход направления счета которого подключен к аыходу дешифратора, входы которого подключены к соответствующим выходам двоичного счетчика, при этом информационные входы первого и второго оперативных запоминающих устройств объединены и являются входом приемника, отличающийся тем, что, с целью повышения достоверности приема путем устранения ложных срабатываний, в него введены третье и четвертое оператив- ные запоминающие устройства, блок объединения, блок сравнения, счетчик числа срабатываний, анализатор числа срабатываний, регистр, блок фиксации результата и блок стробирования, выходы которого сое- динены с попарно объединенными информационными входами третьего и четвертого оперативных запоминающих устройств, выходы которых попарно объединены и подключены ко входам блока обьединения, выходы которого подключены к информационным входам блока сравнения, выход которого соединен со входом разрешения счета счетчика числа срабатываний и информационным входом регистра, выходы кото- рого соединены с информационными входами блока фиксации результата, первый тактовый вход которого подключен к восьмому тактовому выходу блока синхронизации, пятый тактовый выход которого соединен со входом установки нуля счетчика числа срабатываний, выходы которого подключены к информационному входу анализатора числа срабатываний, тактовый вход которого подключен к седьмому тактовому выходу блока синхронизации, шестой тактовый выход которого соединен с тактовым входом счетчика числа срабатываний и с тактовым входом регистра,четвертая, пятая и шестая группы адресных выходов блока синхронизации соединены с адресными входами соответственно третьего оперативного запоминающего устройства, четвертого оперативного запоминающего устройства и блока сравнения, четвертый тактовый выход . блока синхронизации соединен с тактовым входом блока стробирования, информационные входы которого подключены к .с;..... реверсивного счетчика, при этом выход анализатора числа срабатываний соединен со вторым тактовым входом блока фиксации результата, выходы которого являются выходами приемника.

Изобретение относится к электросвязи. Цель изобретения - повышение достоверности приема путем устранения ложных срабатываний. Цифровой приемник дельта- модулированных сигналов многочастотных кодов содержит блок 1 синхронизации, четыре оперативных запоминающих устройства 2,3,4 и 5, постоянное запоминающее устройство 6, реверсивный и двоичный счетчики 7 и 8, дешифратор 9, блок 10 стро- бирования, элемент ИЛИ 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, блок 13 объединения, блок 14 сравнения, счетчик 15 числа срабатывания, регистр 16, анализатор 17 числа срабатываний и блок 18 фиксации результата. Цель достигается последовательным перебором пороговых значений, начиная от минимального, соответствующего нижней границе рабочего диапазона уровней, с последующим сравнением пороговых значений с предварительно запомненными результатами согласованной фильтрации в каждом частотном канале в предыдущем цикле обработки. 4 ил СГ с

О О

О

О

о о

о о

1 о о

1

о о

j-.

Фиг.2

| Цифровой многочастотный приемник сигналов адаптивной дельта-модуляции | 1988 |

|

SU1598214A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-10-07—Публикация

1989-10-12—Подача