Ш1

N3 30

N5 О

tc

Изобретение относится к импульсной и вычислительной технике и может использоваться при построении счетчиков в системах слежения, регистрации событий, цифровой обработки данных

Целью изобретения является повышение быстродействия устройства,,

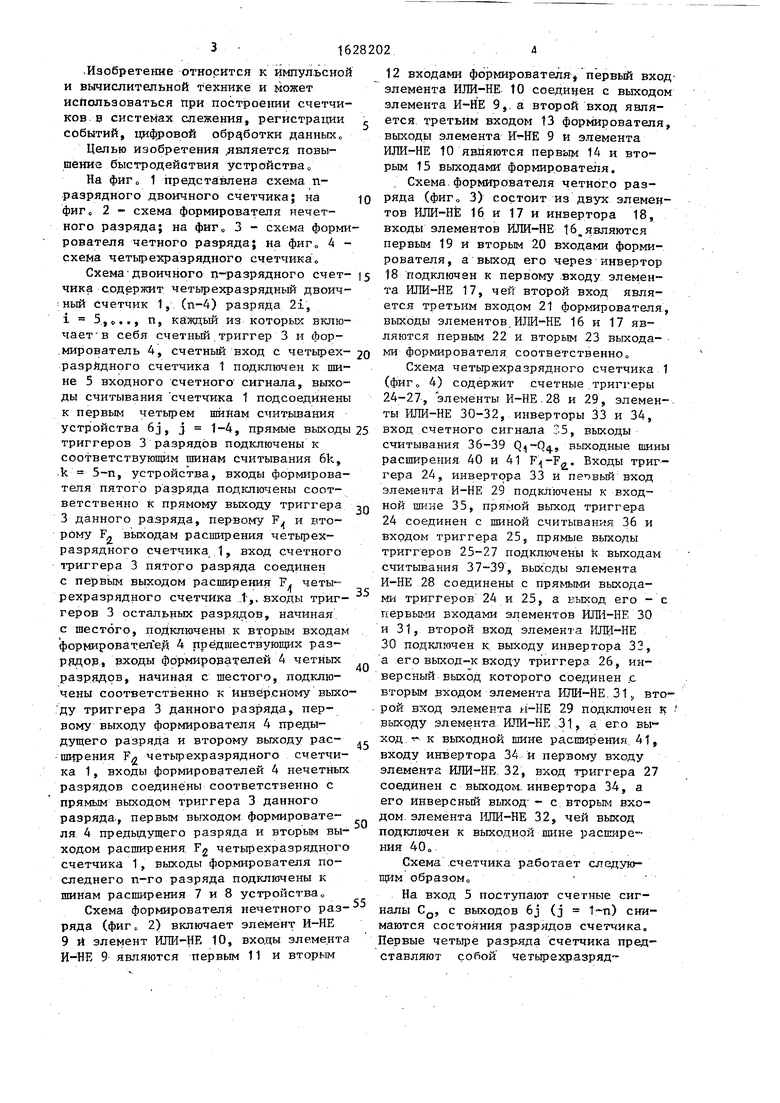

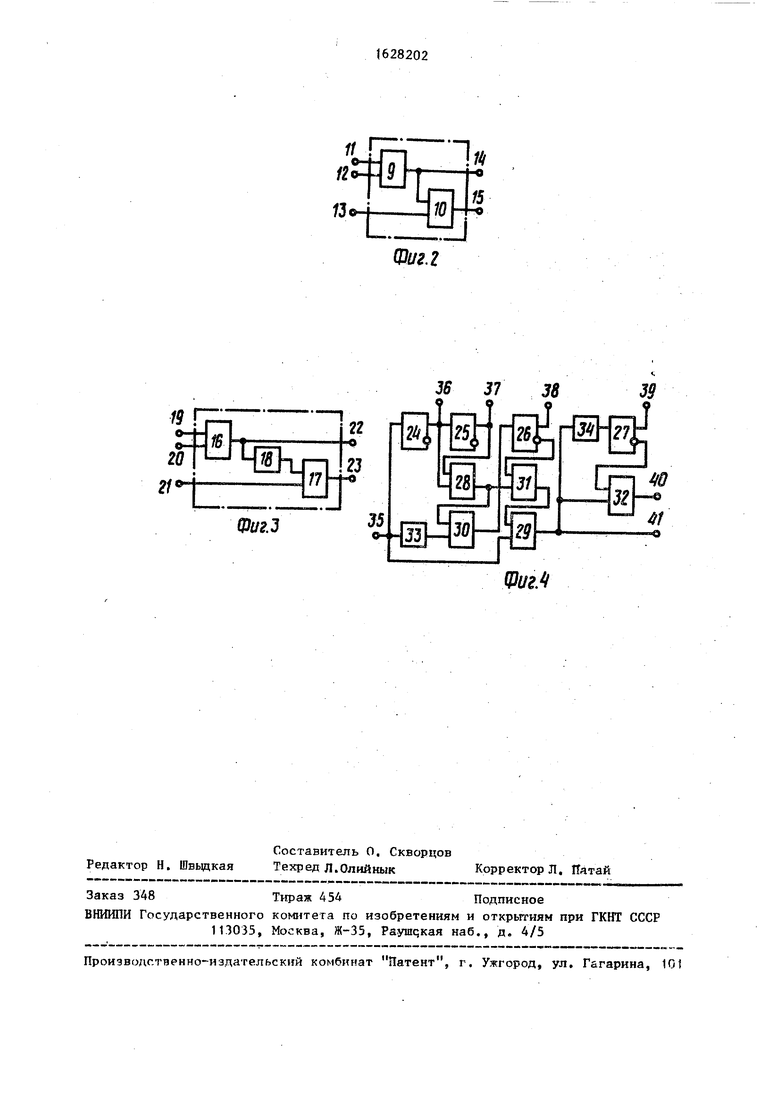

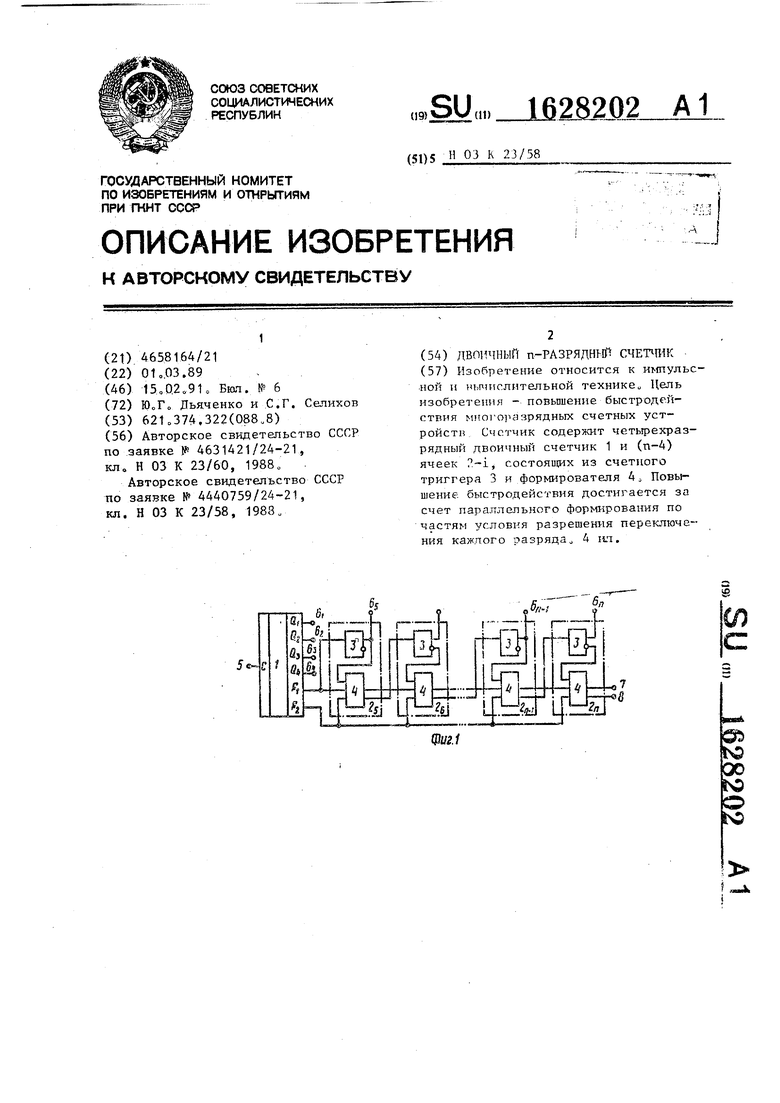

На фиг о 1 представлена схема п- разрядного двоичного счетчика; на фиг о 2 - схема формирователя нечетного разряда; на фиг, 3 - схема формирователя четного разряда; на фиг0 4 - схема четырехразрядного счетчика.

Схема двоичного n-разрядного счет- чика содержит четырехразрядный двоичный счетчик 1, (п-4) разряда 21, i 5,0,., п, каждый из которых включает в себя счетный триггер 3 и cbop- мирователь 4, счетный вход с четырех- разрядного счетчика 1 подключен к шине 5 входного счетного сигнала, выходы считывания счетчика 1 подсоединены к первым четырем шинам считывания устройства 6j, д 1-4, прямые выходы триггеров 3 разрядов подключены к соответствующим шинам считывания 6k, k 5-n, устройства, входы формирователя пятого разряда подключены соответственно к прямому выходу триггера 3 данного разряда, первому F и второму FЈ выходам расширения четырехразрядного счетчика 1, вход счетного триггера 3 пятого разряда соединен с первым выходом расширения F, четырехразрядного счетчика 1,, входы триггеров 3 остальных разрядов, начиная с шестого, подключены к вторым входам формирователе 4 предшествующих разрядов, входы формирователей 4 четных разрядов, начиная с шестого, подключены соответственно к инверсному выходу триггера 3 данного разряда, первому выходу формирователя 4 предыдущего разряда и второму выходу рас- ширения Fg четырехразрядного счетчика 1, входы формирователей 4 нечетных разрядов соединены соответственно с прямым выходом триггера 3 данного разряда, первым выходом формировате ля 4 предыдущего разряда и вторым выходом расширения F2 четырехразрядного счетчика 1, выходы формирователя последнего n-го разряда подключены к шинам расширения 7 и 8 устройства„

Схема формирователя нечетного разряда (фиг0 2) включает элемент И-НЕ 9 и элемент ИЛИ-НЕ 10, входы элемента И-НЕ 9 являются первым 11 и вторим

12 входами формирователяt первый вход элемента ИЛИ-НЕ tO соединен с выходом элемента И-НЕ 9, а второй вход является третьим входом t3 формирователя, выходы элемента И-НЕ 9 и элемента ИЛИ-НЕ 10 являются первым 14 и вторым 15 выходами формирователя.

Схема формирователя четного разряда (фиг„ 3) состоит из двух элементов ИЛИ-НЕ 16 и 17 и инвертора 18, входы элементов ИЛИ-НЕ t6,являются первым 19 и вторым 20 входами формирователя, а выход его через инвертор 18 подключен к первому входу элемента ИЛИ-НЕ 17, чей второй вход является третьим входом 21 формирователя, выходы элементов ИЛИ-НЕ 16 и 17 являются первым 22 и вторым 23 выходами формирователя соответственное,

Схема четырехразрядного счетчика 1 (фиг о 4) содержит счетные триггеры 24-27, элементы И-НЕ 28 и 29, элементы ИЛИ-НЕ 30-32, инверторы 33 и 34, вход счетного сигнала 5, выходы считывания 36-39 ., выходные шины расширения 40 и 41 ,. Входы триггера 24, инвертора 33 и первый вход элемента И-НЕ 29 подключены к входной шине 35, прямой выход триггера 24 соединен с шиной считывания; 36 и входом триггера 25, прямые выходы триггеров 25-27 подключены к выходам считывания 37-39, выходы элемента И-НЕ 28 соединены с прямыми выходами триггеров 24 и 25, а гыход его - с первыми входами элементов ИЛИ-HF 30 и 31, второй вход элемента ИЛИ-НЕ 30 подключен к выходу инвертора 33, а его выход-к входу триггера 26, инверсный выход которого соединен с вторым входом элемента ИЛИ-НЕ 31v второй вход элемента я-НЕ 29 подключен к выходу элемента ИЛИ-НЕ 31, а его выход к выходной шине расширения 41, входу инвертора 34 и первому входу элемента ИЛИ-НЕ 32, вход триггера 27 соединен с выходом, инвертора 34, а его инверсный выход - с вторым входом элемента ИЛИ-НЕ 32, чей выход подключен к выходной шике расширения 40 0

Схема счетчика работает следующим образом

На вход 5 поступают счетные сигналы CQ, с выходов 6j (j ) снимаются состояния разрядов счетчика. Первые четыре разряда счетчика представляют собой четырехразряд™

ный счетчик произвольной организации, реализующий также функции расширения:

C0Q(,

из

1

C0Q,QjQv возможностей

реализаций

такого четырехразрядного счетчика представлена на фиг„ 4„

Счетный сигнал для триггера 3 пятого разряда формируется прямым выходом триггера четвертого разряда , счетчика 1, а счетный сигнал для триггера 3 некоторого m-го разряда, начиная с шестого, формируется сигналом С0 при наличии разрешающего условия, определяемого состояниями предыдущих разрядов счетчика: 0 j 1,

1 - 1 , 000, ГО- 1 „

Формула изобретения

Двоичный n-разрядный счетчик, содержащий четырехразрядный двоичный счетчик и (п-4) ячеек, каждая из которых состоит из счетного триггера и Лормирователя, счетный вход четырехразрядного счетчика подключен к шине входного счетного сигнала, а выходы считывания подключены к первым четырем шинам считывания п-разрядного счетчика, последующие шины считывания счетчика подключены к прямым выходам триггеров ячеек, вторые входы формирователей всех разрядов, начиная с шестого, подключены к первому выходу формирователя предыдущего разряда, второй вход формирователя пятого разряда соединен с первым выходом расширения четырехразрядного счетчика, третьи входы формирователей всех разрядов подключены к второму выходу расширения четырехразрядного счетчика, вторые выходы формирователей всех разрядов по (п-О-й включительно соединены со счетными входами триггеров последующих разряд, выходы формирователя n-го разряда подключены к шинам первого и второго выходов расширения

устройства соответственно, отличающийся тем, что, с целью повышения быстродействия двоичного n-разрядного счетчика, в него введены новые конструктивные связи, формирователь каждого нечетного разряда, начиная с пятого, содержит элементы Й-НЕ и ИЛИ-НЕ, входы элемента И-НЕ являются первым и вторым входами формирователя, а его выход соединен

0 с первым входом элемента ИЛИ-НЕ, второй вход которого является третьим входом формирователя, выходы элементов И-НЕ и ИЛИ-НЕ являются первым и вторым выходами формирователя соот5 ветственно, формирователь каждого четного разряда содержит два элемента ИЛИ-НЕ и инвертор, входы первого элемента ИЛИ-НЕ являются первым и вторым входами Аормирователя, а выход

0 его - первым выходом формирователя, инвертор включен между выходом первого и первым входом второго элементов ИЛИ-НЕ, второй вход второго элемента ИЛИ-НЕ является третьим входом формирователя, а его выход - вторым выходом формироватРЛя, счетный вход триггера пятого разряда соединен с первым выходом расширения четырехразрядного счетчика, первые входы форQ мирователей подключены в нечетных разрядах к прямому выходу триггера данного разряда, а в четных разрядах - к инверсному выходу триггера данного разряда

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный @ -разрядный реверсивный счетчик | 1989 |

|

SU1684928A2 |

| Двоичный счетчик | 1990 |

|

SU1713101A1 |

| Двоичный реверсивный счетчик | 1990 |

|

SU1758873A1 |

| Двоичный счетчик | 1988 |

|

SU1529444A1 |

| Четырехразрядный двоичный счетчик | 1988 |

|

SU1598171A1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| Генератор тестовой последовательности | 1980 |

|

SU944096A1 |

| Устройство для генерирования функционально изменяющихся напряжений | 1979 |

|

SU903916A1 |

| Устройство для контроля работы @ -разрядного счетчика | 1982 |

|

SU1167727A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

Изобретение относится к импульсной и вычислительной технике,, Цель изобретения - повышение быстродействия многоразрядных счетных устройств Счетчик содержит четырехразрядный двоичный счетчик 1 и (п-4) ячеек ч-i 1, состоящих из счетного триггера 3 и формирователя 4, Повышение быстродействия достигается за счет параплельного формирования по частям условия разрешения переключения каждого разряда„ 4 ил.

(Риг. 2

36 37

| Авторское свидетельство СССР по заявке Р 4631421/24-21, кл„ Н 03 К 23/60, 19880 Авторское свидетельство СССР по заявке № 4440759/24-21, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-15—Публикация

1989-03-01—Подача