Изобретение относится к импульсной и вычислительной технике и может использоваться при построении счетных, регистрирующих устройств, систем цифровой обработки информации.

Целью изобретения является расширение области применения за счет увеличения емкости.

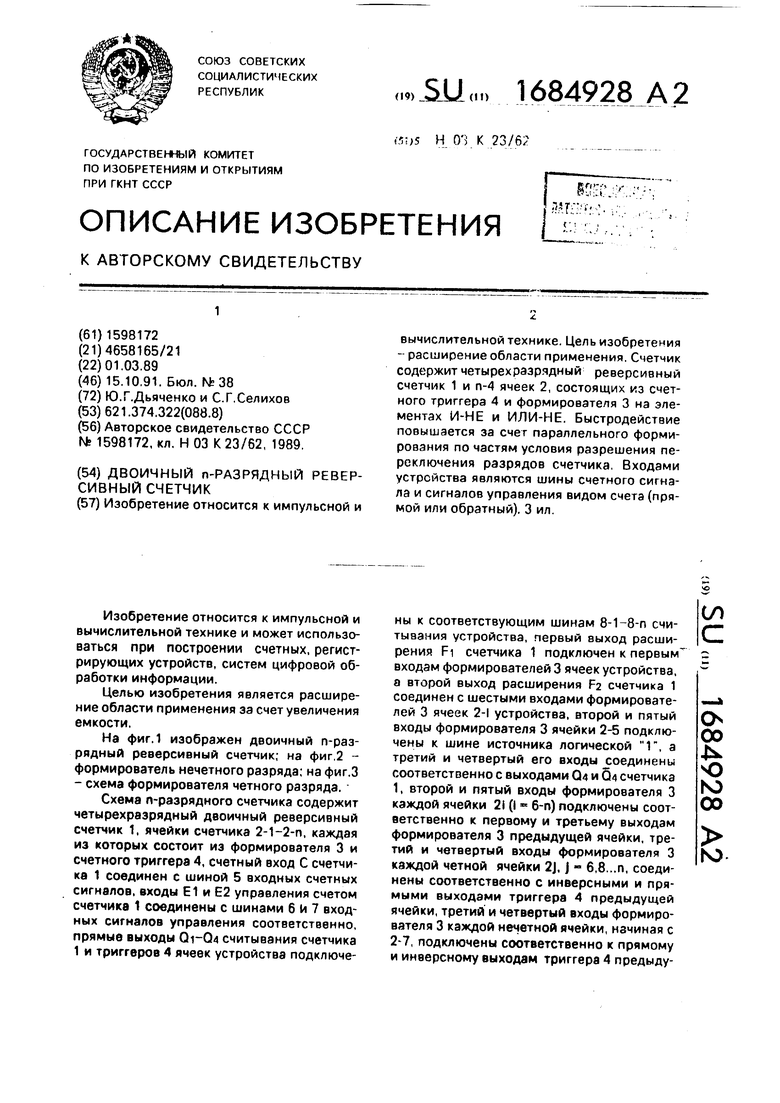

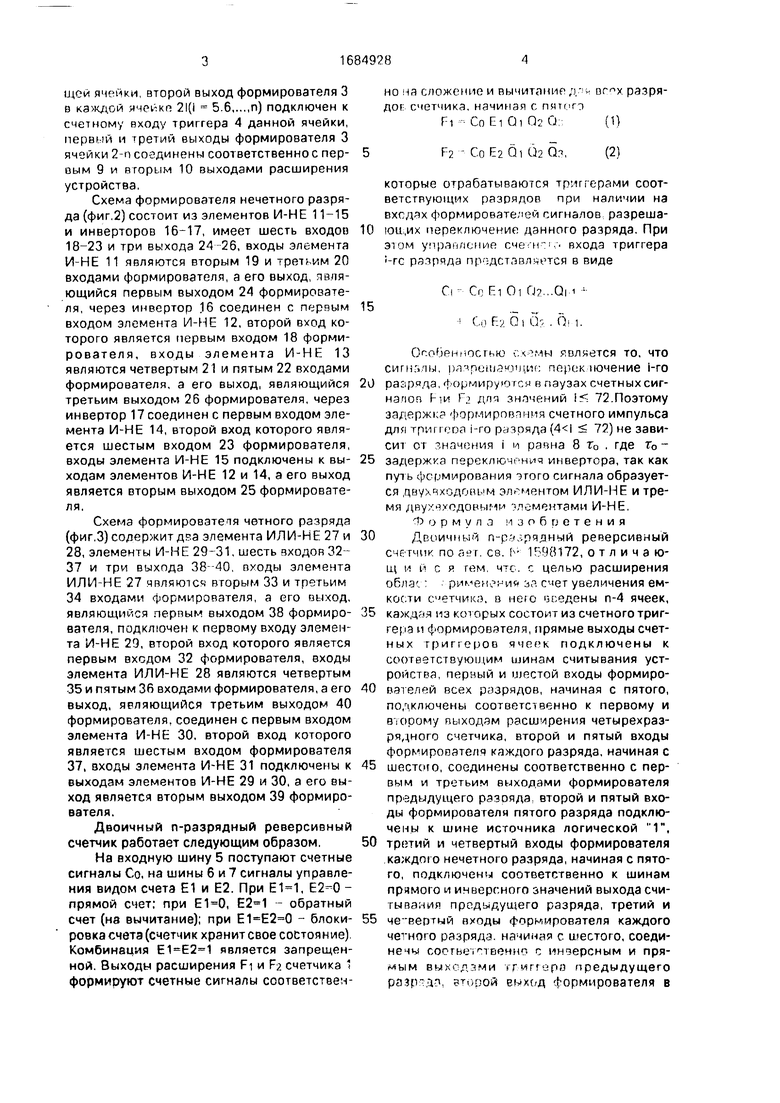

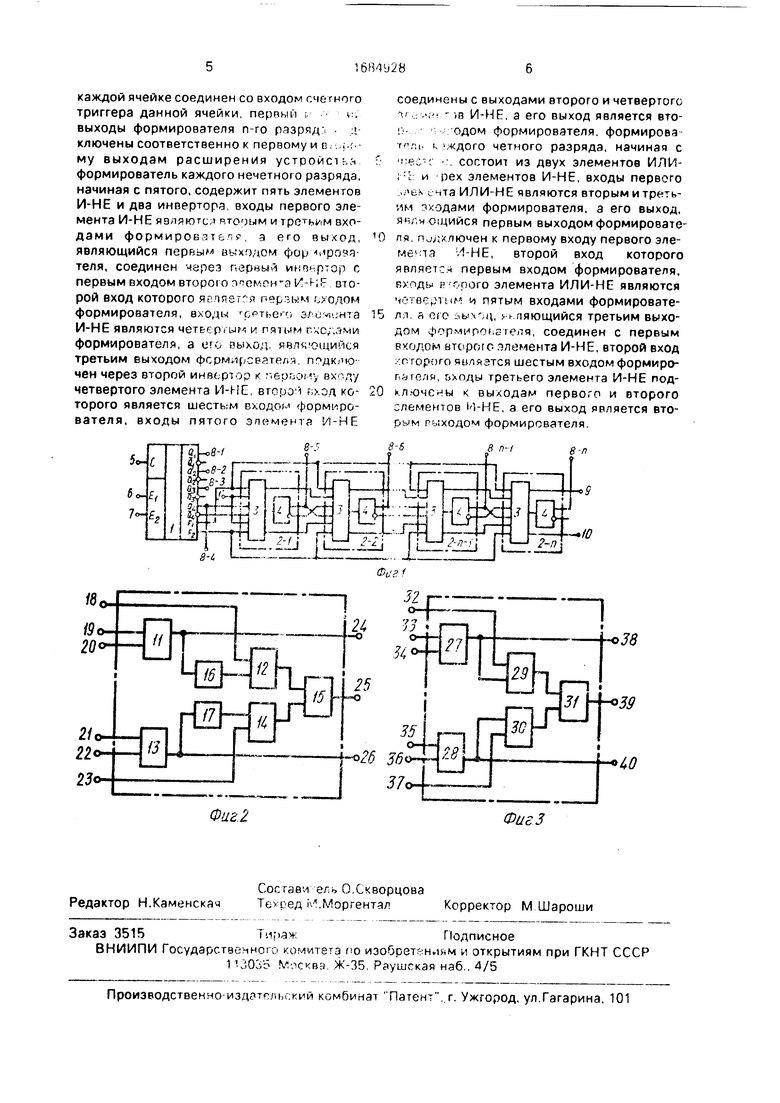

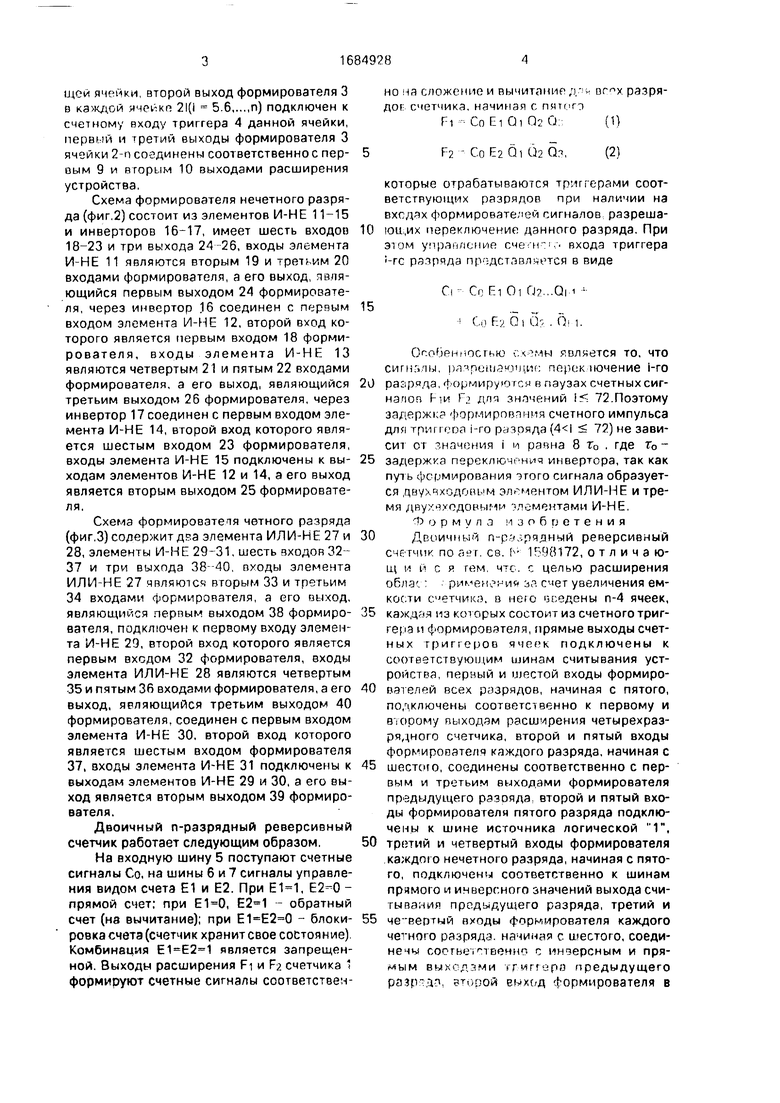

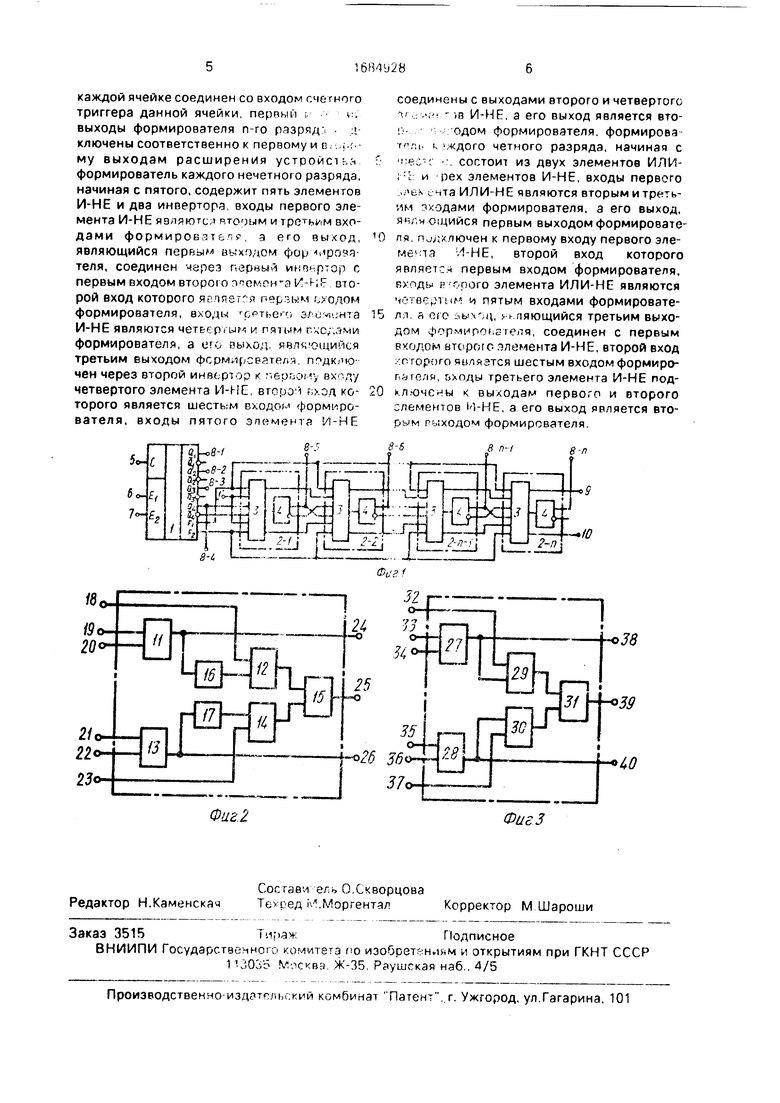

На фиг.1 изображен двоичный п-раз- рядный реверсивный счетчик; на фиг.2 - формирователь нечетного разряда; на фиг.З - схема формирователя четного разряда.

Схема n-разрядного счетчика содержит четырехразрядный двоичный реверсивный счетчик 1, ячейки счетчика 2-1-2-п, каждая из которых состоит из формирователя 3 и счетного триггера 4, счетный вход С счетчике 1 соединен с шиной 5 входных счетных сигналов, входы Е1 и Е2 управления счетом счетчика 1 соединены с шинами 6 и 7 входных сигналов управления соответственно, прямые выходы Qt-См считывания счетчика 1 и триггеров 4 ячеек устройства подключены к соответствующим шинам 8-1-8-п считывания устройства, первый выход расширения FI счетчика 1 подключен к первым входам формирователей 3 ячеек устройства, а второй выход расширения F2 счетчика 1 соединен с шестыми входами формирователей 3 ячеек 2-1 устройства, второй и пятый входы формирователя 3 ячейки 2-5 подключены к шине источника логической 1, а третий и четвертый его входы соединены соответственно с выходами См и См счетчика 1, второй и пятый входы формирователя 3 каждой ячейки 21 (I б-п) подключены соответственно к первому и третьему выходам формирователя 3 предыдущей ячейки, третий и четвертый входы формирователя 3 каждой четной ячейки 2J, j - 6,8...n, соединены соответственно с инверсными и прямыми выходами триггера 4 предыдущей ячейки, третий и четвертый входы формирователя 3 каждой нечетной ячейки, начиная с 2-7, подключены соответственно к прямому и инверсному выходам триггера 4 предыдусо С

О 00

4

ю ю со

го

щей ячейки, второй выход формирователя 3

в каждой ячейке 2I(I 5.6п) подключен к

счетному входу триггера 4 данной ячейки, первмй и третий выходы формирователя 3 ячейки 2-п соединены соответственно с первым 9 и вторым 10 выходами расширения устройства,

Схема формирователя нечетного разряда (фиг,2) состоит из элементов И-НЕ 11-15 и инверторов 16-17, имеет шесть входов 18-23 и три выхода 24-26, входы элемента И-НЕ 11 являются вторым 19 и третьим 20 входами формирователя, а его выход, лапя- ющийся первым выходом 24 формирователя, через инвертор .16 соединен с первым входом элемента И-НЕ 12, второй вход которого является первым входом 18 формирователя, входы элемента И-НЕ 13 являются четвертым 21 и пятым 22 входами формирователя, а его выход, являющийся третьим выходом 26 формирователя, через инвертор 17 соединен с первым входом элемента И-НЕ 14, второй вход которого является шестым входом 23 формирователя, входы элемента И-НЕ 15 подключены к выходам элементов И-НЕ 12 и 14, а его выход является вторым выходом 25 формирователя.

Схема формировэтетя четного разряда (фиг.З) содержит два элемента ИЛИ-НЕ 27 и 28, элементы И-НЕ 29-31, шесть входов 32- 37 и три выхода 38-40, входы элемента ИЛИ-НЕ 27 чвляклсч вторым 33 и третьим

34входами формирователя, а его выход, являющийся первым выходом 38 формирователя, подключен к первому входу элемента И-НЕ 29, второй вход которого является первым входом 32 формирователя, входы элемента ИЛИ-НЕ 28 являются четвертым

35и пятым 36 входами формирователя, а его выход, являющийся третьим выходом 40 формирователя, соединен с первым входом элемента И-НЕ 30, второй вход которого является шестым входом формирователя 37, входы элемента И-НЕ 31 подключены к выходам элементов И-НЕ 29 и 30, а его выход является вторым выходом 39 формирователя.

Двоичный n-разрядный реверсивный счетчик работает следующим образом,

На входную шину 5 поступают счетные сигналы Со, на шины 6 и 7 сигналы управления видом счета Е1 и Е2. При , - прямой счет; при , - обратный счет (на вычитание); при - блокировка счета (счетчик хранит свое состояние) Комбинация йвляется запрещенной. Выходы расширения FI и Рг счетчика 1 формируют счетные сигналы соответственно чя сложенней вычитание,Vv разря- до( счетчика, начиная с пятого

Fi CoEiQiOaQ(П

- Со Еа См Q2 Cb,

(2}

которые отрабатываются триггерами соответствующих разрядов при наличии на вхсдях формирователей сигналов разреша- юи.их переключение данного разряда. При этом умранление счеоп.. входа триггера -гс разряда представляется в виде

15

Ci - Со Гц см о ..QI 1

(,, F.v См СЬ . QI 1.

Ог-.оЬримосгню v, является то. что cum. iiu, пачгилиаю цис переключение 1-го

разряда, формируются в паузах счетныхсиг- нагюп Ни Г для значений 15. 72.Поэтому задержка формирования счетного импульса для триггера 1-го рсоряда ( 7) не зависит or значения i и равна 8 Т0 . где ть задержка переключения инвертора, так как путь формирования этого сигнала образуется двухчходовым элементом ИЛИ-НЕ и тремя двуу-эуодокыми элементами И-НЕ. Формула изобретения

Двоичный п-р орядный реверсивный счетчик по aer. ce. h- 1f:48172, отличаю- щ и и с я тем, чт. с целью расширения облз . римеис и за счет увеличения емкости сиетчик;5, в нею чседены п-4 ячеек,

каждая из кот орых состоит из счетного триггера и Формирователя, прямые выходы счетных триггеров подключены к соответствующим шинам считывания устройства, первый и шестой входы формиропат елей всех разрядов, начиная с пятого, подключены соответственно к первому и второму пыходам расширения четырехразрядного счетчика, второй и пятый входы формирователя каждого разряда, начиная с

шестого, соединены соответственно с первым и третьим выходами формирователя предыдущего разояда второй и пятый входы формирователя пятого разряда подключены к шине источника логической 1,

третий и четвертый входы формирователя каждою нечетного разряда, начиная с пятого, подключены соответственно к шинам прямого и инверсного значений выхода считывания предыдущего разряда, третий и

че вертый входы формирователя каждого четного разряда, начиная с шестого, соединены cocrbeiri вечно с инзерсным и прямым выходами сгиггиро предыдущего . т,,рой выход формирователя в

каждой ячейке соединен со входом счетного триггера данной ячейки, первый .,v,

выходы формирователя n-го разряд . д- ключены соответственно к первому и с. ...- му выходам расширения устройств формирователь каждого нечетного разряда, начиная с пятого, содержит пять элементов И-НЕ и два инвертора, входы первого элемента И-НЕ яв/тяютс, Р,ТОЧЫМ и третьим входами формировать 9 , а его выход, являющийся первым выходом фор мрозя- теля, соединен через парный с первым входом второю И-KF ото- рой вход которого ярчяег-р первым одом формирователя, входы гсртье - - И-НЕ являются четБер.ык v. пятым г.хс;.ами формирователя, а его выход, явл« Ощийея третьим выходом Фсрмирсеателч п°дк. ЧО- чен через второй инвертор к перьому вхп/v/ четвертого элемента И-НЕ, второй F.XOA которого является шестым входом формирователя, входы пятого элемента И-НЕ

О

соединены с выходами второго и четвертого v .-, -,в И-НЕ, а его выход является вто- г-одом формирователя, формировэтт. 1- k ждого четного разряда, начиная с ( . состоит из двух элементов ИЛИ- и рех элементов И-НЕ, входы первого ..ь. .нта ИЛИ-НЕ являются вторым и треть- ям ходами формирователя, а его выход, ячу-,я оидийся первым выходом формирователя, исключен к первому входу первого эле- И-НЕ, второй вход которого являете первым входом формирователя, входы Р орого элемента ИЛИ-НЕ являются четвсршм ч пятым входами формирователя s ic ,t, я пяющийся третьим выходом формиро., соединен с первым входом второго элемента И-НЕ, второй вход /огорого чиляэтся шестым входом формиро- пйгеяя, ьходы третьего элемента И-НЕ под- ключс- ы к выходам первого и второго слементов И-НЕ, а его выход является вторым р ходом формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный п-разрядный счетчик | 1989 |

|

SU1628202A1 |

| Двоичный реверсивный счетчик | 1990 |

|

SU1758873A1 |

| Двоичный счетчик | 1990 |

|

SU1713101A1 |

| Двоичный счетчик | 1988 |

|

SU1529444A1 |

| Дешифратор времяимпульсных кодов | 1991 |

|

SU1807562A1 |

| Голографическое постоянное запоминающее устройство со сменным носителем голограмм | 1990 |

|

SU1691889A1 |

| Четырехразрядный двоичный счетчик | 1988 |

|

SU1598171A1 |

| Формирователь последовательности кодов | 1974 |

|

SU526870A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1522271A1 |

| Многоразрядный счетчик | 1984 |

|

SU1225012A1 |

Изобретение относится к импульсной и вычислительной технике. Цель изобретения - расширение области применения. Счетчик содержит четырехразрядный реверсивный счетчик 1 и п-4 ячеек 2, состоящих из счетного триггера 4 и формирователя 3 на элементах И-НЕ и ИЛИ-НЕ. Быстродействие повышается за счет параллельного формирования по частям условия разрешения переключения разрядов счетчика. Входами устройства являются шины счетного сигнала и сигналов управления видом счета (прямой или обратный). 3 ил.

Штгад ц

f-W f-I i l-H ., ;

Bi 1 ,- ; -- Ш - 1гд L-rt

, i-ц )4±z7ZIi LT

в л-/

в-л

| Четырехразрядный двоичный реверсивный счетчик | 1988 |

|

SU1598172A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-10-15—Публикация

1989-03-01—Подача