Изобретение относится к импульсной и вы ислительной технике и может использоваться при построении счетчиков в системах слежения, регистрации событий, цифровой обработки данных.

Известен двоичный счетчик, содержащий инвертор и п разрядов, каждый из которых состоит из счетного триггера и формирователя.

Недостаток известного устройства низкое быстродействие.

Наиболее близким к предлагаемому решению по технической сущности является двоичный п-разрядный счетчик, содержащий четырехразрядный счетчик и (п-4) ячейки, каждая из которых состоит из счетного триггера и формирователя.

Недостаток - низкое быстродействие.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в двоичном счетчике, содержащем четырехразрядный двоичный счетчик и (п-4) ячеек, каждая из которых состоит из счетного триггера и формирователя, причем счетный вход четырехразрядного счетчика подключен к шине входного счетного сигнала, а выходы считывания его и прямые выходу триггеров ячеек подключены к соответствующим выходам считывания устройства, формирователь каждого нечетного разряда, начиная с пятого, содержит элементы И-НЕ и ИЛИ-НЕ, входы элемента И-НЕ являются первым и вторым входами формирователя, а его выход - первым выходом формирователя, первый вход элемента ИЛИ-НЕ соединен с выходом элемента И-НЕ, второй вход является третьим входом формирователя, а выход его - вторым выходом формирователя, формирователь каждого четного разряда начиная с шестого, содержит два элемента ИЛИ-НЕ и инвертор, входы первого элемента ИЛИ-НЕ являют.ся первым и вторым входами формирователя, а выход его является первым выходом формирователя и через инвертор подключен к первому входу второго элеплента ИЛИ-НЕ, второй вход которого явдяется третьим входом формирователя, а выход - вторым выходом формирователя, счетный вход триггера пятого разряда соединен с выходом переполнения четырехразрядного счетчика, а первый вход формирователя пятого разряда подключен к прямому выходу триггера пятого разряда, счетный вход триггера каждого разряда, начиная с шестого подключенк второму выходу формирователя предыдущего разряда1 пёрвь й и второй входы формирователей, четных разрядов.

начиная с шестого, подключены соответственно к инверсному выходу триггера данного разряда и пер&ому выходу формирователя предыдущего разряда, первый и

второй входы формирователей нечетных разрядов, начиная с седьмого, подключены соответственно к прямому выходу триггера данного разряда и первому выходу формирователя предыдущего разряда,

0 первый и второй выходы формирователя последнего п-го разряда подключены к первой и второй шинам расширения устройства соответственно, введены инвертор и новые конструктивные связи, вход

5 инвертора подключен к выходу переполнения четырехразрядного счетчика, а выхрд его - к третьим входам формирователей всех разрядов, начиная с пятого, второй вход формирователя пятого разряда соеди0 йен с источником Лог.1.

Известно использование инверторов в счетчиках. Однако использование инвертора в даннам счетчике позволяет достичь эффекта, выраженного целью изобретения.

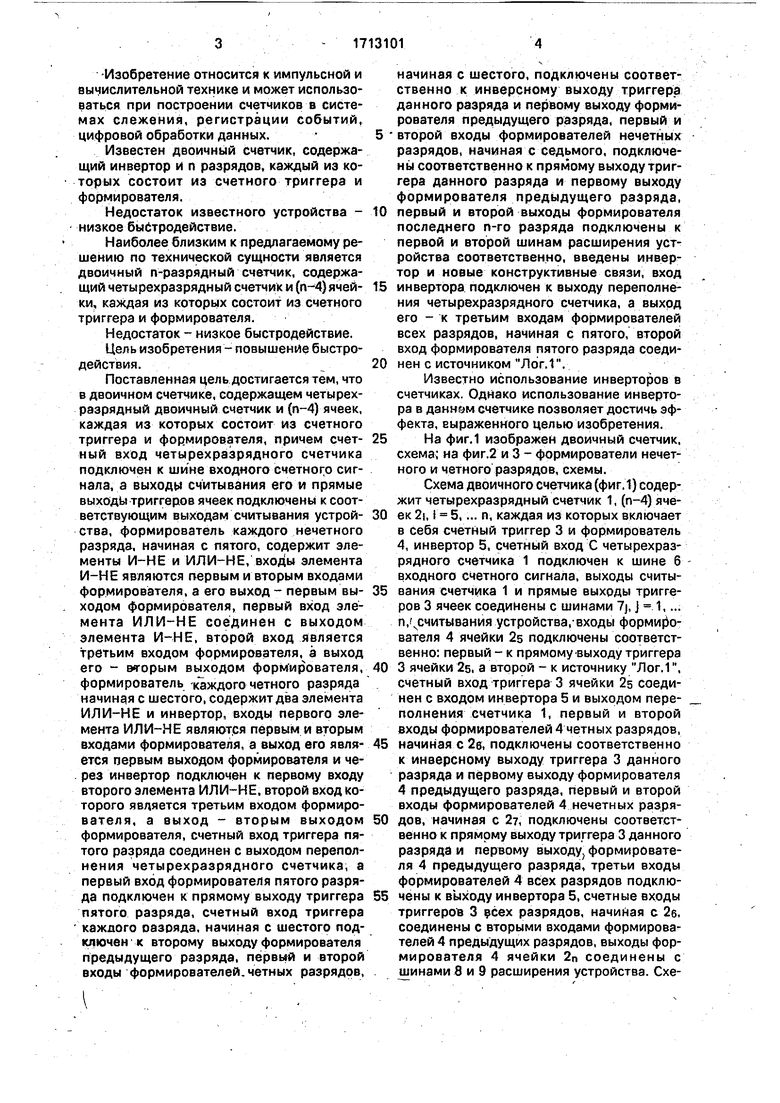

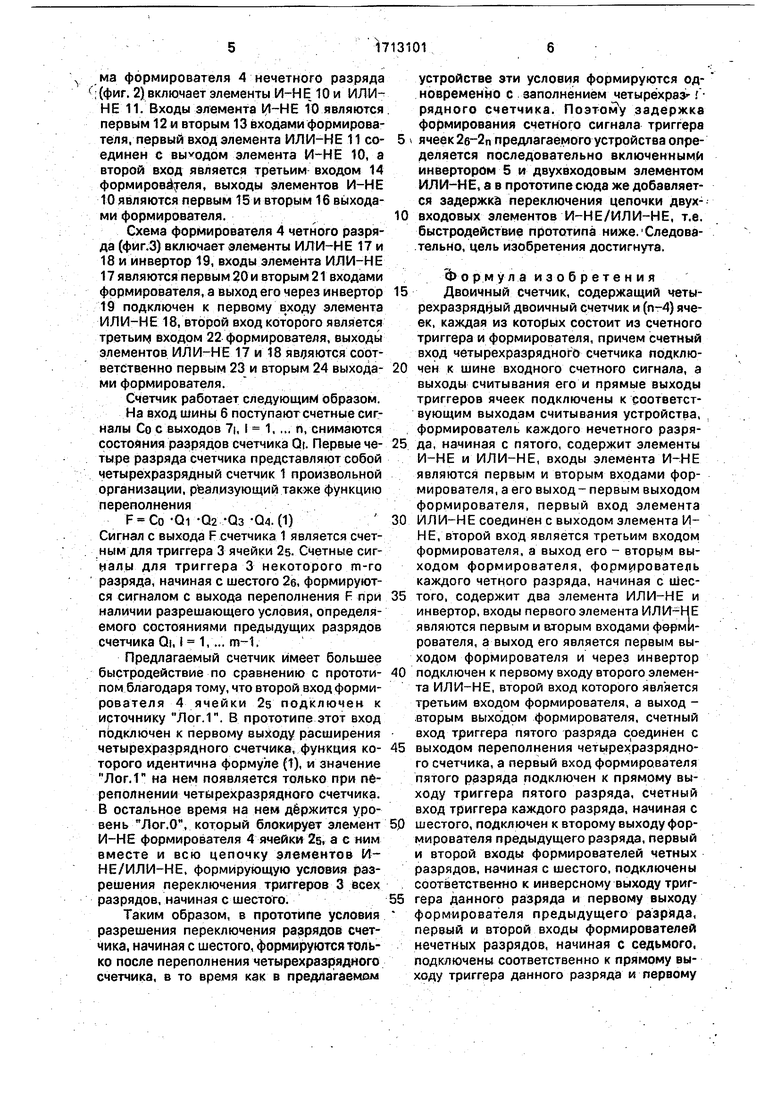

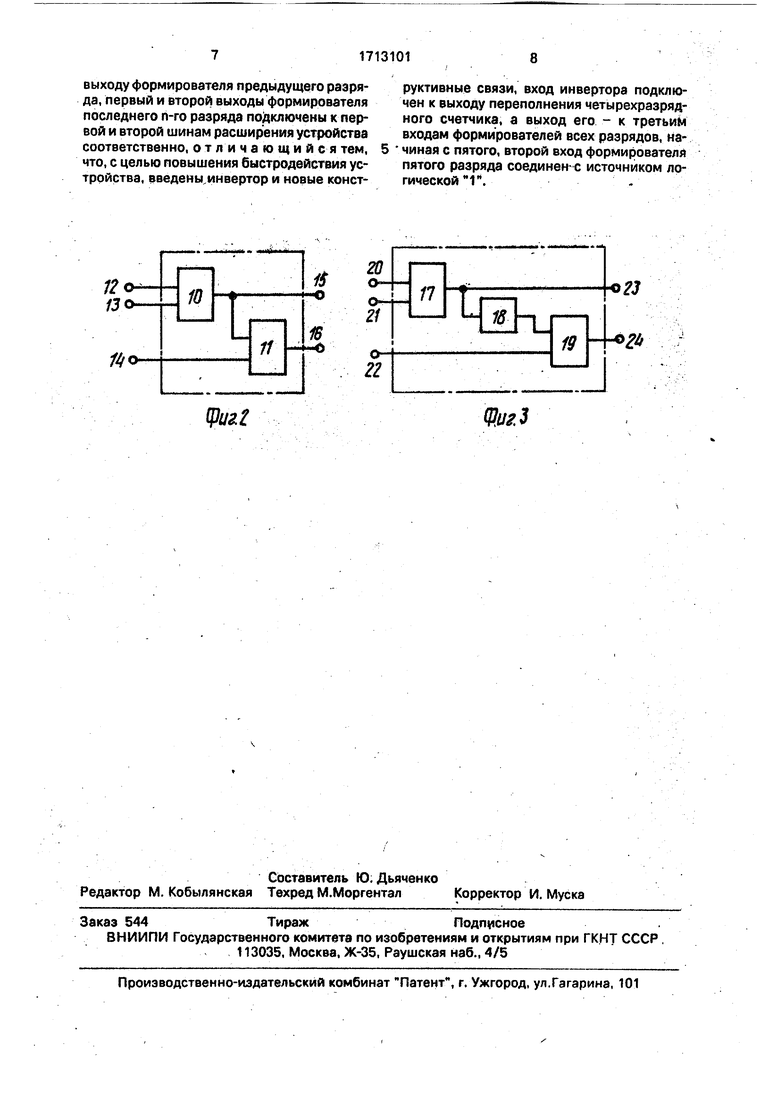

5 На фиг.1 изображен двоичный счетчик, схемам на фиг.2 и 3 - формирователи нечетного и четного разрядов, схемы.

Схема двоичного счетчика (фиг. 1) содержит четырехразрядный счетчик 1, (п-4) ячеек 2|, I 5,... п, каждая из которых включает в себя счетный триггер 3 и формирователь 4, инвертор 5, счетный вход С четырехразрядного счетчика 1 подключен к шине б входного счетного сигнала, выходы считывания счетчика 1 и прямые выходы триггеров 3 ячеек соединены с шинами 7j, 1,... п, считывания устройства,-входы формирователя 4 ячейки 25 подключены соответственно: первый - к прямому-выходу триггера

0 3 ячейки 25, а второй - к источнику Лог.1, счетный вход триггера 3 ячейки 25 соединен с входом инвертора 5 и выходом переполнения счетчика 1, первый и второй входы формирователей 4 четных разрядов,

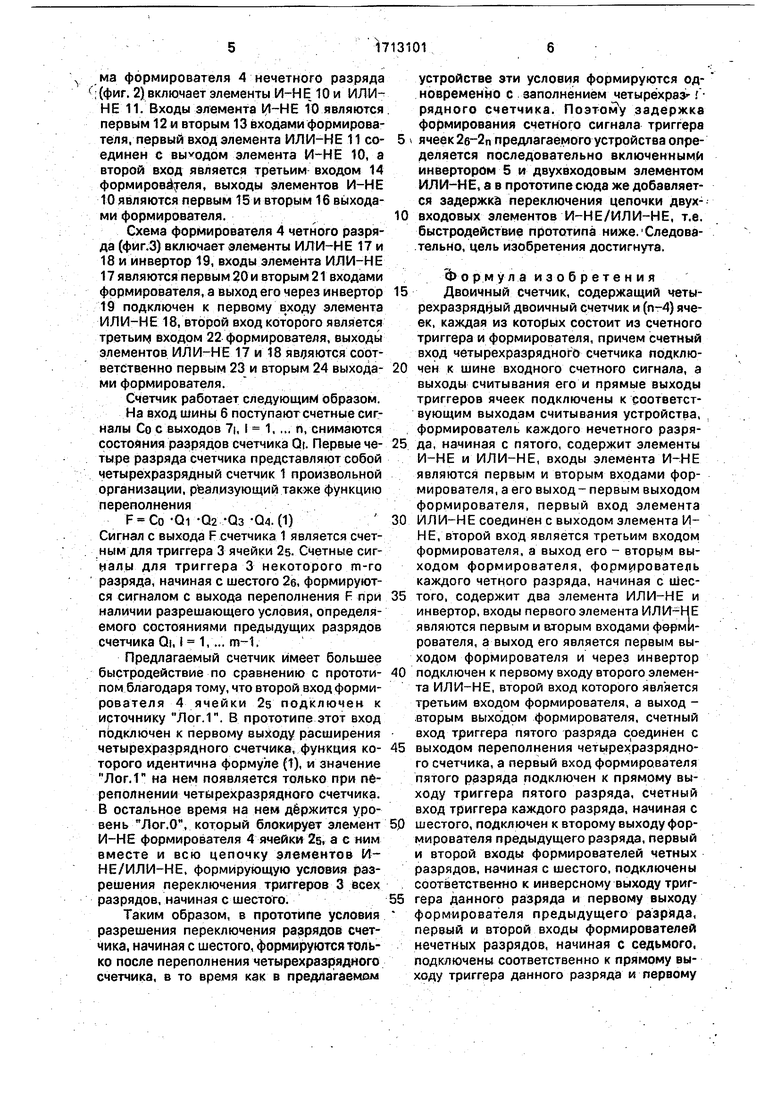

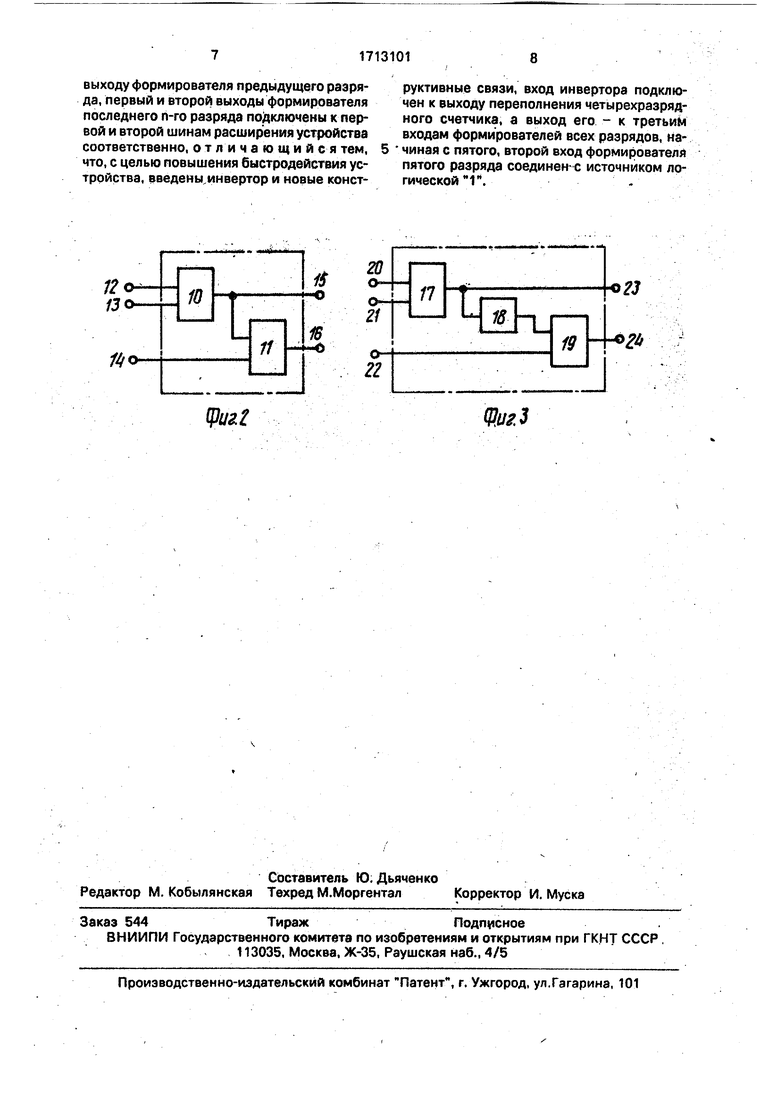

5 начиная с 2б, подключены соответственно к инверсному выходу триггера 3 данного разряда и первому выходу формирователя 4 предыдущего разряда, первый и второй входы формирователей 4 нечетных разрядов, начиная с 2, подключены соответственно к прямому выходу триггера 3 данного разряда и первому выходу формирователя 4 предыдущего разряда, третьи входы формирователей 4 всех разрядов подключены к выходу инвертора 5, счетные входы триггеров 3 сех разрядов, начиная с 2б, соединены с вторыми входами формирователей 4 предыдущих разрядов, выходы формирователя 4 ячейки 2п соединены с шинами 8 и 9 расширения устройства. Схе ма формирователя 4 нечетного разряда : (фиг. 2) включает элементы И-Н Е 10 и ИЛИНЕ 11. Входы элемента И-НЕ 10 являются первым 12 и вторым 13 входами формирователя, первый вход элемента ИЛИ-НЕ 11 соединен с выходом элемента И-НЕ 10, а второй вход является третьим входом 14 формиров еля. выходы элементов И-НЕ 10 являются первым 15 и вторым 16 выходами формирователя. Схема формирователя 4 четного разряда (фйг.З) включает элементы ИЛИ-НЕ 17 и 18и инвертор 19, входы элемента ИЛИ-НЕ 17 являются первым 20 и вторым 21 входами формирователя, а выход его через инвертор 19подключен к первому выходу элемента ИЛИ-НЕ 18, второй вход которого является третьиг входом 22 формирователя, выходы элементов ИЛИ-НЕ 17 и 18 яв/ яются соответственно первым 23 и вторым 24 выходами формирователя. Счетчик работает следующим образом. На вход шины 6 поступают счетные сигналы Со с выходов 7|, I 1, ,.. h, снимаются состояния разрядов счетчика Qi. Первые четыре разряда счетчика представляют собой четырехразрядный счетчик 1 произвольной организации, р)еализующий также функцию переполнения F Co -Qi -02 Q3 -04. (1) Сигнал с выхода F счетчика 1 является счет. ным для триггера 3 ячейки 25. Счетные сигналы для триггера 3 некоторого т-го разряда, начиная с шестого 2б, формируются сигналом С выхода переполнения F при наличии разрешающего условия, определяемого состояниями предыдущих разрядов счетчика Qi, I 1,... т-1. Предлагаемый счетчик имеет большее быстродействие по сравнению с прототипом благодаря тому, что второй вход формирователя 4 ячейки 25 подключен к ИСТОЧНИКУ Лог.1. В прототипе этот вход пЬдключен к первому выходу расширения четырехразрядного счетчика, функция которого идентична формуле (1), и значение Лог.1 на нем появляется только при переполнении четырехразрядного счетчика. В остальное время на нем держится уровень Лог.О, который блокирует элемент И-НЕ формирователя 4 ячейки 2$, а с ним вместе и всю цепочку элементов ИНЕ/ИЛИ-НЕ, формирующую условия разрешения переключения триггеров 3 всех разрядов, начиная с шестого. Таким образом, в прототипе условия разрешения переключения разрядов счетчика, начиная с шестого, формируются только после переполнения четь(рехраз|)ядного счетчика, в то время как в предлагаемом устройстве эти условия формируются одновременно с заполнением четырёхраз. рядного счетчика. Поэтому задержка формирования счетного сигнала триггера ячеек 2б-2п предлагаемого устройства определяется последовательно включенными инвертором 5 и двухвходовым элементом ИЛИ-НЕ, а в прототипе сюда же добавляется задержка переключения цепочки двухвходовых элементов И-НЕ/ИЛ И-НЕ, т.е. быстродействие прототипа ниже. Следова.тельно, цель изобретения достигнута. Формул а изо б рете н ия Двоичный счетчик, содержащий четырехразрядчый двоичный счетчик и (п-4) ячеек, каждая из которых состоит из счетного триггера и формирователя, причем счетный вход четырехразрядного счетчика подключен к шине входного счетного сигнала, а выходы считывания его и прямые выходы триггеров ячеек подключены к соответствующим выходам считывания устройства, , формирователь каждого нечетного разряда, начиная с пятого, содержит элементы И-НЕ и ИЛИ-НЕ, входы элемента И-НЕ являются первым и вторым входами формирователя, а его выход-первым выходом формирователя, первый вход элемента ИЛИ-НЕ соединен с выходом элемента ИНЕ, второй вход является третьим входом формирователя, а выход его - вторым выходом формирователя, форм1 роватедь каждого четного разряда, начиная с Шестого, содержит два элемента ИЛИ-НЕ и инвертор, входы первого элемента ИЛИ-НЕ являются первым и вторым входами формирователя, а выход его является первым выходом формирователя и через инвертор подключен к первому входу второго элемента ИЛИ-НЕ, второй вход которого является третьим входом формирователя, а выход .вторым выходом формирователя, счетный вход триггера пятого разряда соединен с выходом переполнения четьфехразрядного счетчика, а первый вход формирователя пятого разряда подключен к прямому выходу триггера пятого разряда, счетный вход триггера каждого разряда, начиная с шестого, подключен к второму выходу формирователя предыдущего разряда, первый и второй входы формирователей четных разрядов, начиная с шестого, подключены соответственно к инверсному выходу триггера данного разряда и первому выходу формирователя предыдущего разряда, первый и второй входы формирователей нечетных разрядов, начиная с седьмого, подключены соответственно к прямому выходу триггера данного разряда и первому

выходу формирователя предыдущего разряда, первый и второй выходы формирователя последнего п-го разряда подключены к первой и второй шинам расширения устройства соответственно, отличающийся тем, что, с целью повышения быстродействия устройства, введеиы инвертор и новые конструктивные связи, вход инвертора подключен к выходу переполнения четырехразрядного счетчика, а выход его - к третьим входам формирователей всех разрядов. Начиная с пятого, второй вход формирователя пятого разряда соединен источником логической 1..

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный реверсивный счетчик | 1990 |

|

SU1758873A1 |

| Двоичный @ -разрядный реверсивный счетчик | 1989 |

|

SU1684928A2 |

| Двоичный п-разрядный счетчик | 1989 |

|

SU1628202A1 |

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1231613A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1462374A1 |

| Дешифратор времяимпульсных кодов | 1991 |

|

SU1807562A1 |

| Двоичный счетчик | 1988 |

|

SU1529444A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2006 |

|

RU2319192C2 |

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2002 |

|

RU2232412C1 |

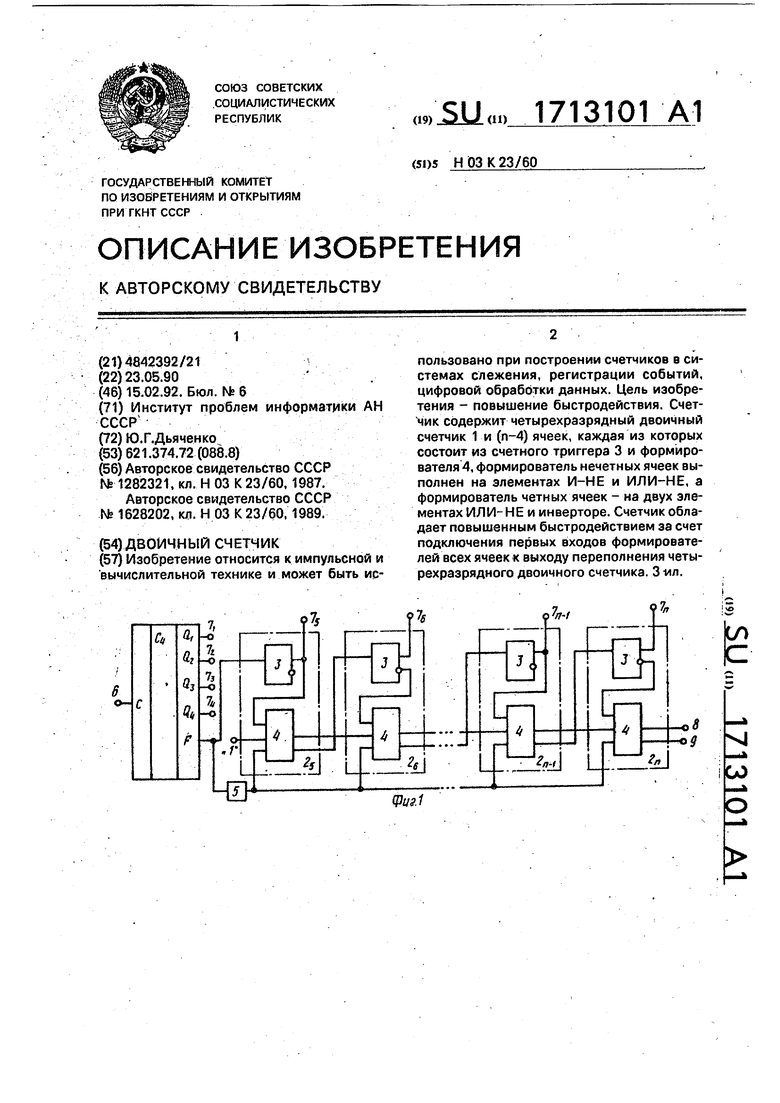

Изобретение относится к импульсной и 'вычислительной технике и может быть использовано при построении счетчиков в системах слежения, регистрации событий, цифровой обработки данных. Цель изобретения - повышение быстродействия. Счет- 'чик содержит четырехразрядный двоичный счетчик 1 и (п-4) ячеек, каждая из которых состоит из счетного триггера 3 и формирователя 4. формирователь нечетных ячеек выполнен на элементах И-НЕ и ИЛИ-НЕ. а формирователь четных ячеек - на двух зле- ментах ИЛИ-НЕ и инверторе. Счетчик обладает повышенным быстродействием за счет подключения первых входов формирователей всех ячеек к выходу переполнения четырехразрядного двоичного счетчика. 3 -ил.O'ff'l\^e>&feCPUf.l^ со о

№

teJ

| Двоичный счетчик | 1984 |

|

SU1282321A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1992-02-15—Публикация

1990-05-23—Подача